Optimization of Contact Resistance and DC Characteristics for AlGaN/GaN HEMTs Utilizing Sub-10 nm Nanohole Etching

Abstract

1. Introduction

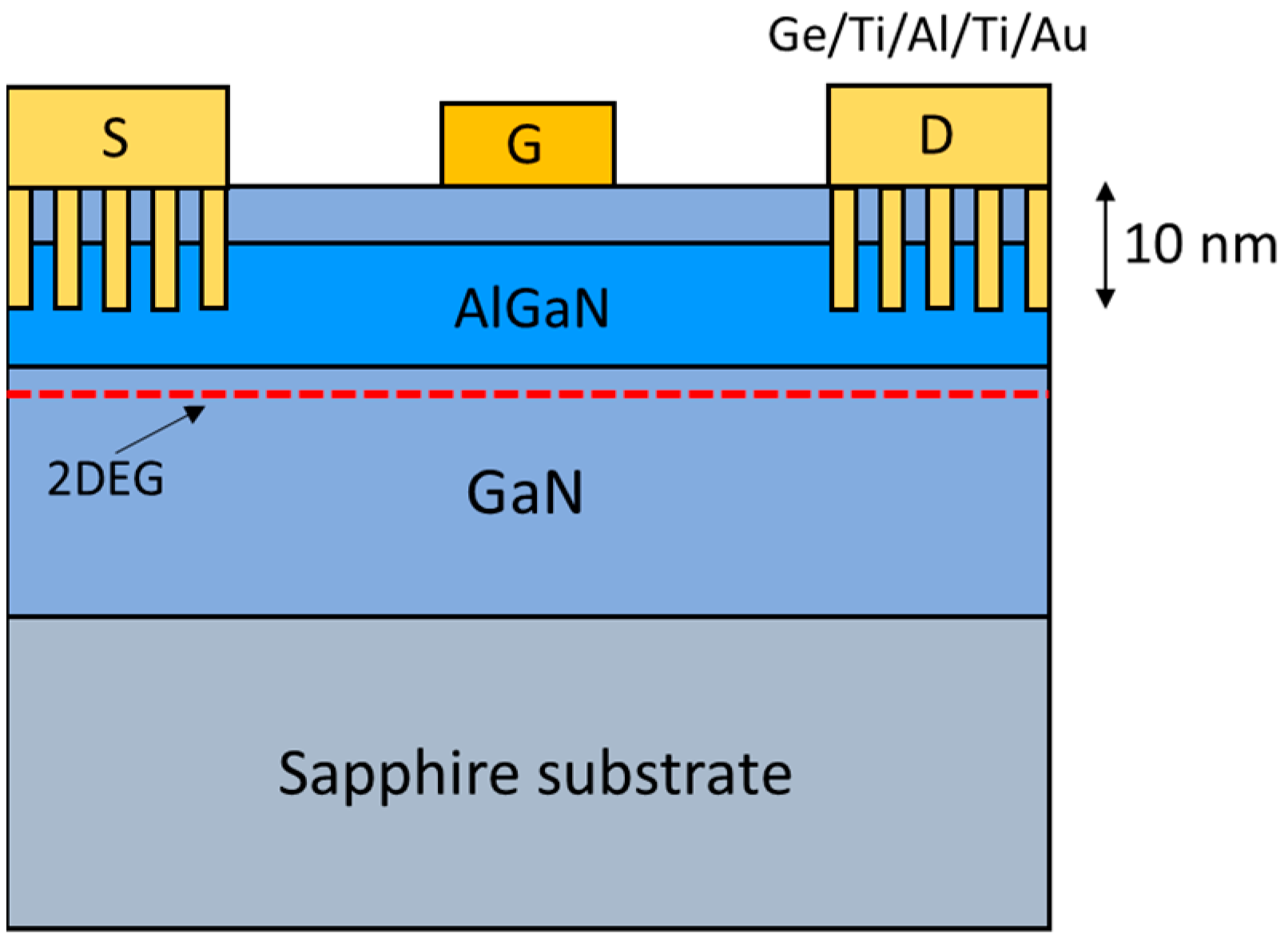

2. Materials and Methods

3. Results and Discussion

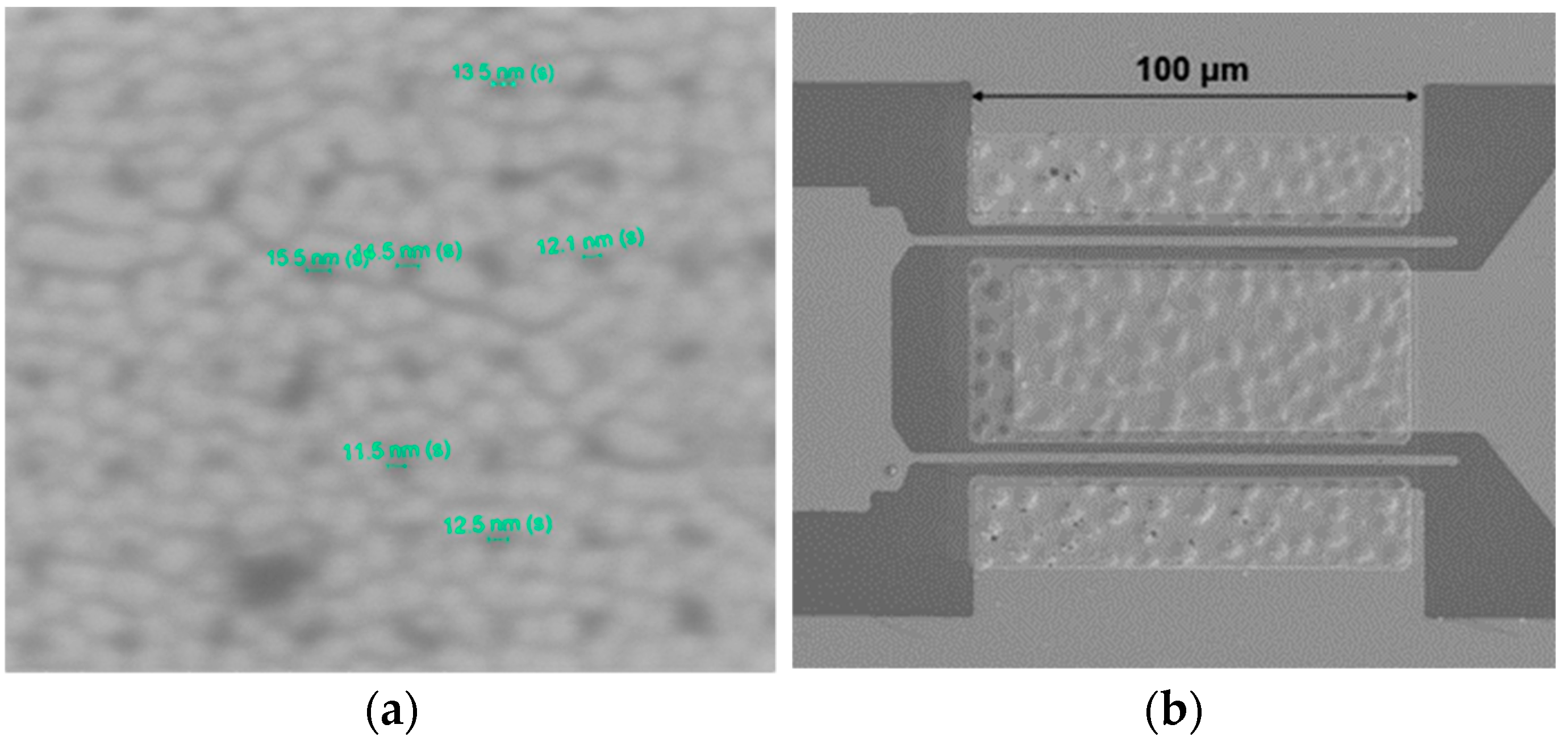

3.1. Sub-10 nm Nanohole Patterns

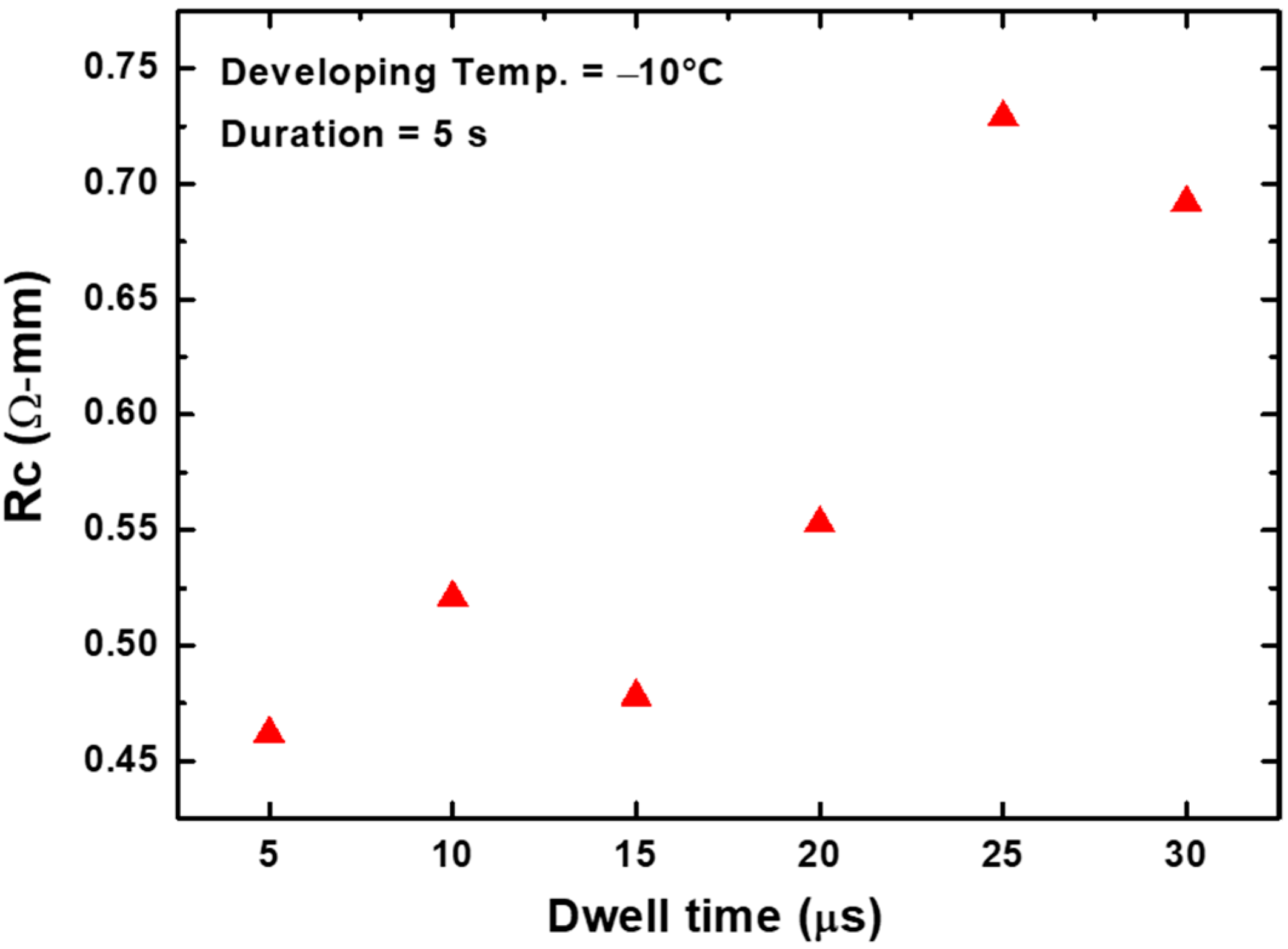

3.2. Contact Resistance Evaluation with TLM Measurement

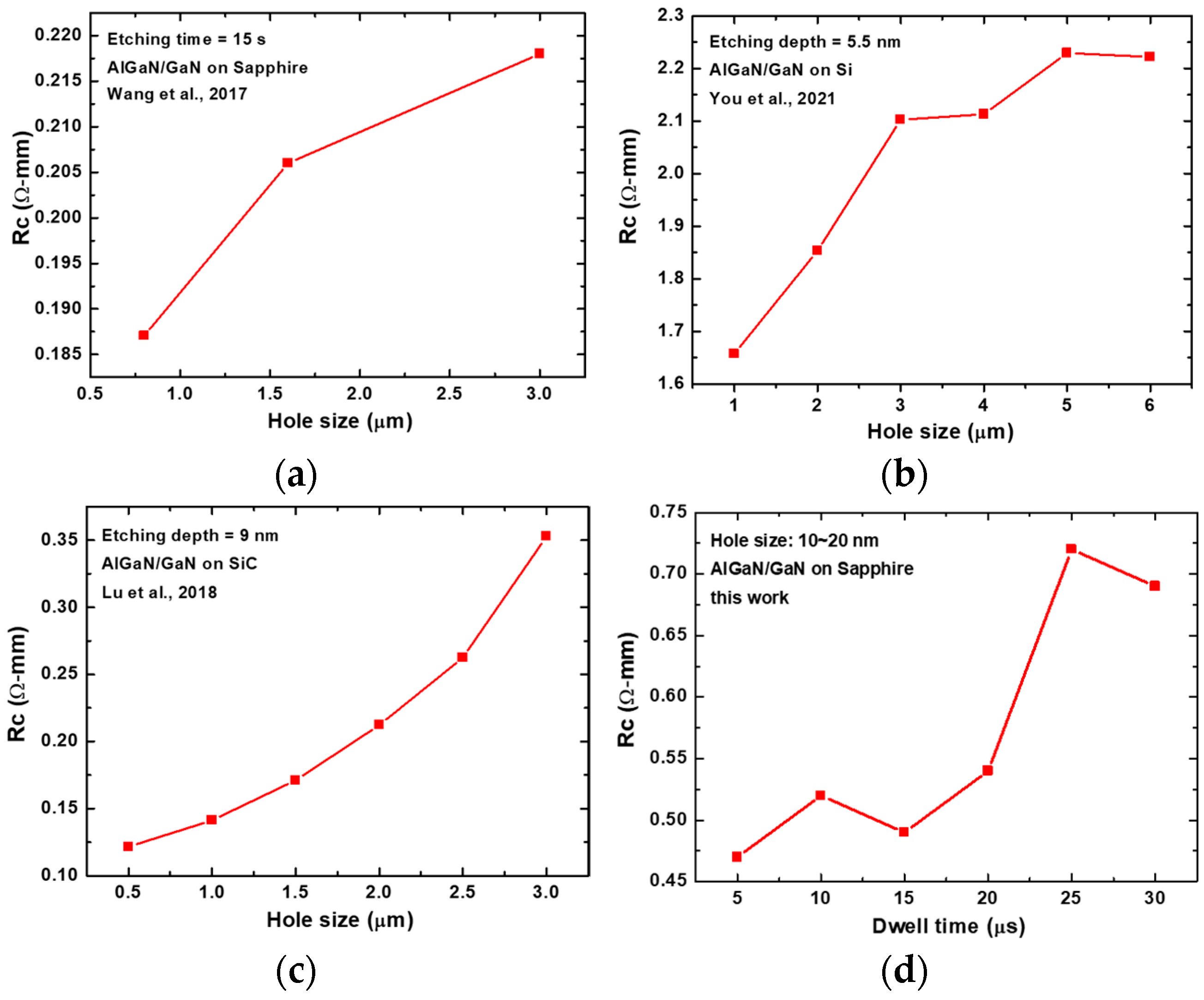

3.3. Effect of Etching Holes on Different Substrate Materials

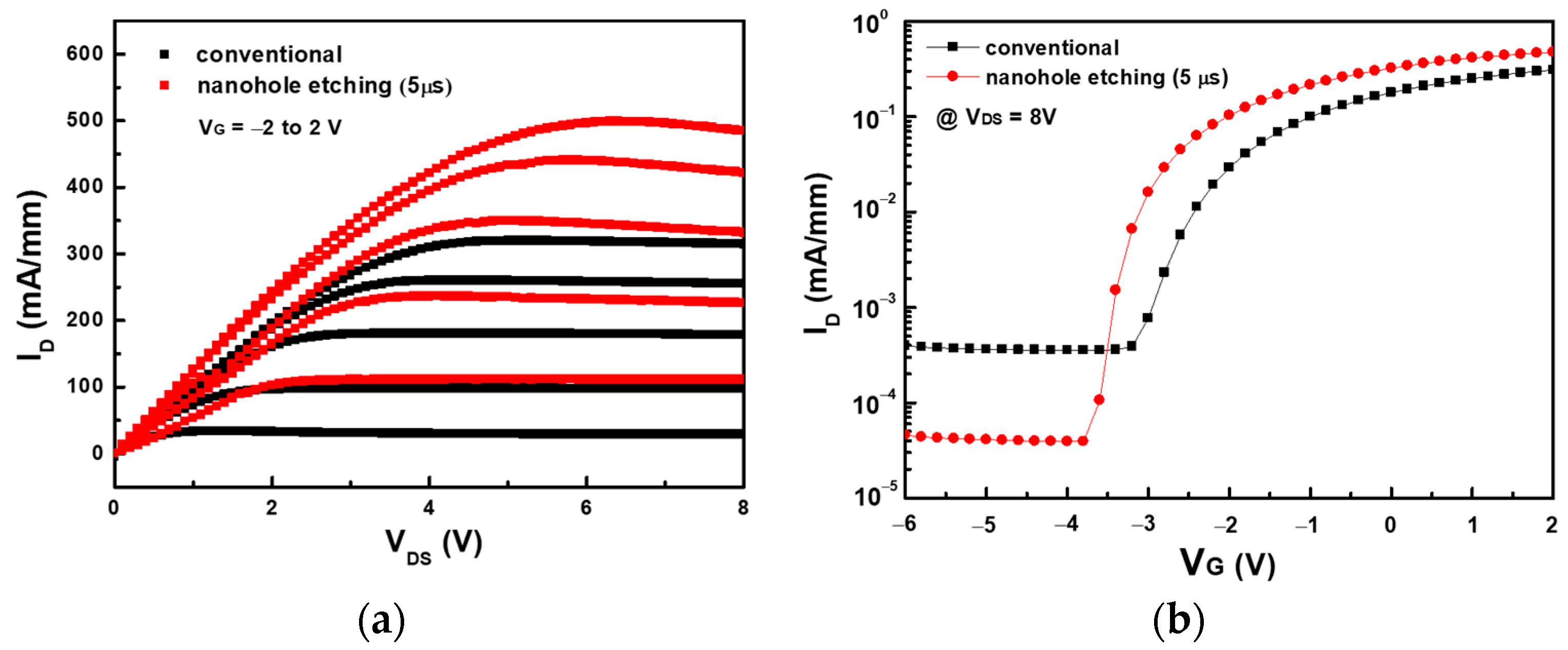

3.4. DC Characteristics of AlGaN/GaN HEMTs Utilizing Sub-10 nm Nanohole Etching

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Haziq, M.; Falina, S.; Manaf, A.A.; Kawarada, H.; Syamsul, M. Challenges and Opportunities for High-Power and High-Frequency AlGaN/GaN High-Electron-Mobility Transistor (HEMT) Applications: A Review. Micromachines 2022, 13, 2133. [Google Scholar] [CrossRef] [PubMed]

- Ambacher, O.; Foutz, B.; Smart, J.; Shealy, J.R.; Weimann, N.G.; Chu, K.; Murphy, M.; Sierakowski, A.J.; Schaff, W.J.; Eastman, L.F.; et al. Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures. J. Appl. Phys. 2000, 87, 334. [Google Scholar] [CrossRef]

- Hsu, C.-W.; Lin, Y.-C.; Lee, M.-W.; Chang, E.-Y. Investigation of the Effect of Different SiNx Thicknesses on the Characteristics of AlGaN/GaN High-Electron-Mobility Transistors in Ka-Band. Electronics 2023, 12, 4336. [Google Scholar] [CrossRef]

- Jones, E.A.; Wang, F.; Costinett, D. Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 707–719. [Google Scholar] [CrossRef]

- Nakatani, K.; Yamaguchi, Y.; Komatsuzaki, Y.; Sakata, S. A Ka-Band High Efficiency Doherty Power Amplifier MMIC using GaN-HEMT for 5G Application. In Proceedings of the 2018 IEEE MTT-S International Microwave Workshop Series on 5G Hardware and System Technologies (IMWS-5G), Dublin, Ireland, 30–31 August 2018. [Google Scholar]

- Weng, Y.-C.; Lin, Y.-C.; Hsu, H.-T.; Kao, M.-L.; Huang, H.-Y.; Ueda, D.; Ha, M.-T.-H.; Yang, C.-Y.; Maa, J.-S.; Chang, E.-Y.; et al. A Novel GaN:C Millimeter-Wave HEMT with AlGaN Electron-Blocking Layer. Materials 2022, 15, 703. [Google Scholar] [CrossRef] [PubMed]

- Saito, W.; Kuraguchi, M.; Takada, Y.; Tsuda, K.; Omura, I.; Ogura, T. High breakdown Voltage undoped AlGaN-GaN power HEMT on sapphire substrate and its demonstration for DC-DC converter application. IEEE Trans. Electron Devices 2004, 51, 1913–1917. [Google Scholar] [CrossRef]

- Mohanbabu, M.; Mohankumar, N.; Godwin Raj, D.; Sarkar, P.; Saha, S.K. Efficient III-Nitride MIS-HEMT devices with high-κ gate dielectric for high-power switching boost converter circuits. Superlattices Microstruct. 2017, 103, 270–284. [Google Scholar] [CrossRef]

- Zhou, Y.; Mi, M.; Yang, M.; Han, Y.; Wang, P.; Chen, Y.; Liu, J.; Gong, C.; Lu, Y.; Zhang, M.; et al. High performance millimeter-wave InAlN/GaN HEMT for low voltage RF applications via regrown Ohmic contact with contact ledge structure. Appl. Phys. Lett. 2022, 120, 062104. [Google Scholar] [CrossRef]

- Yadav, Y.K.; Upadhyay, B.B.; Meer, M.; Ganguly, S.; Saha, D. Reduced Contact Resistance and Improved Transistor Performance by Surface Plasma Treatment on Ohmic Regions in AlGaN/GaN HEMT Heterostructures. Phys. Status Solidi A 2018, 215, 1700656. [Google Scholar] [CrossRef]

- Chung, J.W.; Hoke, W.E.; Chumbes, E.M.; Palacios, T. AlGaN/GaN HEMT with 300-GHz. IEEE Electron Dev. Lett. 2010, 31, 195–197. [Google Scholar] [CrossRef]

- Saito, W.; Takada, Y.; Kuraguchi, M.; Tsuda, K.; Omura, I. Recessed-gate structure approach toward normally off high-Voltage AlGaN/GaN HEMT for power electronics applications. IEEE Trans. Electron Devices 2006, 53, 356–362. [Google Scholar] [CrossRef]

- Bright, A.N.; Thomas, P.J.; Weyland, M.; Tricker, D.M.; Humphreys, C.J.; Davies, R. Correlation of contact resistance with microstructure for Au/Ni/Al/Ti/AlGaN/GaN ohmic contacts using transmission electron microscopy. J. Appl. Phys. 2001, 89, 3143–3150. [Google Scholar] [CrossRef]

- Bardwell, J.A.; Sproule, G.I.; Liu, Y.; Tang, H.; Webb, J.B.; Fraser, J.; Marshall, P. Comparison of two different Ti/Al/Ti/Au ohmic metallization schemes for AlGaN/GaN. J. Vac. Sci. Technol. B 2002, 20, 1444–1447. [Google Scholar] [CrossRef]

- Selvanathan, D.; Zhou, L.; Kumar, V.; Adesida, I. Low Resistance Ti/Al/Mo/Au Ohmic Contacts for AlGaN/GaN Heterostructure Field Effect Transistors. Phys. Status Solidi (A) 2002, 194, 583–586. [Google Scholar] [CrossRef]

- Yadav, Y.K.; Upadhyay, B.B.; Meer, M.; Bhardwaj, N.; Ganguly, S.; Saha, D. Ti/Au/Al/Ni/Au Low Contact Resistance and Sharp Edge Acuity for Highly Scalable AlGaN/GaN HEMTs. IEEE Electron Device Lett. 2019, 40, 67–70. [Google Scholar] [CrossRef]

- Nguyen, C.; Shah, P.; Leong, E.; Derenge, M.; Jones, K. Si implant-assisted Ohmic contacts to GaN. Solid-State Electron. 2010, 54, 1227–1231. [Google Scholar] [CrossRef][Green Version]

- Yue, Y.; Hu, Z.; Guo, J.; Sensale-Rodriguez, B.; Li, G.; Wang, R.; Faria, F.; Fang, T.; Song, B.; Gao, X.; et al. InAlN/AlN/GaN HEMTs with Regrown Ohmic Contacts and fT of 370 GHz. IEEE Electron Dev. Lett. 2012, 33, 988–990. [Google Scholar] [CrossRef]

- Takei, Y.; Kamiya, M.; Tsutsui, K.; Saito, W.; Kakushima, K.; Wakabayashi, H.; Kataoka, Y.; Iwai, H. Reduction of contact resistance on AlGaN/GaN HEMT structures introducing uneven AlGaN layers. Phys. Status Solidi A 2015, 212, 1104–1109. [Google Scholar] [CrossRef]

- Takei, Y.; Tsutsui, K.; Saito, W.; Kakushima, K.; Wakabayashi, H.; Iwai, H. Dependence of ohmic contact properties on AlGaN layer thickness for AlGaN/GaN high-electron-mobility transistors. Jpn. J. Appl. Phys. 2016, 55, 040306. [Google Scholar] [CrossRef]

- Gudkov, A.G.; Shashurin, V.D.; Vyuginov, V.N.; Tikhomirov, V.G.; Vidyakin, S.I.; Agasieva, S.V.; Gorlacheva, E.N.; Chizhikov, S.V. The Influence of AlGaN Barrier-Layer Thickness on the GaN HEMT Parameters for Space Applications. In Proceedings of the Scientific-Practical Conference “Research and Development—2016”, Moscow, Russia, 14–15 December 2016. [Google Scholar]

- Wang, C.; Zhao, M.D.; He, Y.L.; Zheng, X.F.; Wei, X.X.; Mao, W.; Ma, X.H.; Zhang, J.C.; Hao, Y. Optimization of ohmic contact for AlGaNGaN HEMT by introducing patterned etching in ohmic area. Solid-State Electron. 2017, 129, 114–119. [Google Scholar] [CrossRef]

- Benakaprasad, B.; Eblabla, A.M.; Li, X.; Crawford, K.G.; Elgaid, K. Optimization of Ohmic Contact for AlGaN/GaN HEMT on Low-Resistivity Silicon. IEEE Trans. Electron Devices 2020, 67, 863–868. [Google Scholar] [CrossRef]

- You, X.R.; Chen, C.W.; Tzou, J.; Hsin, Y.M. Study of Au-Based and Au-Free Ohmic Contacts in AlGaN/GaN HEMTs by Recessed Patterns. ECS J. Solid State Sci. Technol. 2021, 10, 075006. [Google Scholar] [CrossRef]

- Lee, M.-W.; Chuang, C.-W.; Gamiz, F.; Chang, E.-Y.; Lin, Y.-C. Improvement of AlGaN/GaN High-Electron-Mobility Transistor Radio Frequency Performance Using Ohmic Etching Patterns for Ka-Band Applications. Micromachines 2024, 15, 81. [Google Scholar] [CrossRef] [PubMed]

- Yu, C.H.; Luo, Q.Z.; Luo, X.D.; Liu, P.S. Donor-Like Surface Traps on Two-Dimensional Electron Gas and Current Collapse of AlGaN/GaN HEMTs. Sci. World J. 2013, 2013, 931980. [Google Scholar] [CrossRef] [PubMed]

- Marino, F.A.; Ferry, D.K. Effects of threading dislocations on AlGaN/GaN high-electron mobility transistors. IEEE Trans. Electron Devices 2010, 57, 353–360. [Google Scholar] [CrossRef]

- Chang, L.C.; Nien, C.; Ye, J.H.; Chung, C.H.; Su, V.C.; Wu, C.H.; Kuan, C.H. A comprehensive model for sub-10 nm electron beam patterning through the short-time and cold development. Nanotechnology 2017, 28, 425301. [Google Scholar] [CrossRef] [PubMed]

- Yang, J.; Liu, K.; Chen, X.; Shen, D. Recent advances in optoelectronic and microelectronic devices based on ultrawide-bandgap semiconductors. Prog. Quantum Electron. 2022, 83, 100397. [Google Scholar] [CrossRef]

- Bruni, F.J. Crystal growth of sapphire for substrates for high-brightness, light emitting diodes. Cryst. Res. Technol. 2015, 50, 133–142. [Google Scholar] [CrossRef]

- Gao, J.; Hao, M.; Li, W.; Xu, Z.; Mandal, S.; Nemanich, R.; Chowdhury, S. Al2O3 Insertion Layer for Improved PEALD SiO2/(Al)GaN Interfaces. Phys. Status Solidi A 2018, 215, 1700498. [Google Scholar] [CrossRef]

- Liao, W.-C.; Chiang, C.-T.; Chyi, J.-I.; Hsin, Y.-M. Reduced Interface States of Atomic-Layer-Deposited Al2O3/AlGaN/GaN Heterostructure Containing In Situ Grown AlN/GaN Cap Layer and Subjected to Thermal Oxidation. J. Electrochem. Soc. 2015, 162, E160–E165. [Google Scholar] [CrossRef]

- Kordoš, P.; Stoklas, R.; Gregušová, D.; Novák, J. Characterization of AlGaN/GaN metal-oxide-semiconductor field-effect transistors by frequency dependent conductance analysis. Appl. Phys. Lett. 2009, 94, 2235. [Google Scholar] [CrossRef]

- Duffy, S.J.; Benbakhti, B.; Mattalah, M.; Zhang, W.; Bouchilaoun, M.; Boucherta, M.; Kalna, K.; Bourzgui, N.; Maher, H.; Soltani, A. Low Source/Drain Contact Resistance for AlGaN/GaN HEMTs with High Al Concentration and Si-HP [111] Substrate. ECS J. Solid State Sci. Technol. 2017, 6, S3040–S3043. [Google Scholar] [CrossRef]

- Lu, Y.; Ma, X.; Yang, L.; Hou, B.; Mi, M.; Zhang, M.; Zheng, J.; Zhang, H.; Hao, Y. High RF Performance AlGaN/GaN HEMT Fabricated by Recess-Arrayed Ohmic Contact Technology. IEEE Electron Device Lett. 2018, 39, 811–814. [Google Scholar] [CrossRef]

- Pharkphoumy, S.; Janardhanam, V.; Jang, T.-H.; Shim, K.-H.; Choi, C.-J. Correlation of Crystal Defects with Device Performance of AlGaN/GaN High-Electron-Mobility Transistors Fabricated on Silicon and Sapphire Substrates. Electronics 2023, 12, 1049. [Google Scholar] [CrossRef]

- Pandey, a.; Singh, V.K.; Dalal, S.; Bag, R.K.; Narang, K.; Kaur, D.; Raman, R.; Tyagi, R. Effect of two step GaN buffer on the structural and electrical characteristics in AlGaN/GaN heterostructure. Vacuum 2020, 178, 109442. [Google Scholar] [CrossRef]

- Han, K. Employing hole-array recess of barrier layer of AlGaN/GaN Heterostructures to reduce annealing Temperature of Ohmic contact. Semicond. Sci. Technol. 2017, 32, 105010. [Google Scholar] [CrossRef]

- Wang, Y.; Huang, S.; Wang, X.; Kang, X.; Zhao, R.; Zhang, Y.; Zhang, S.; Fan, J.; Yin, H.; Liu, C.; et al. Effects of Fluorine Plasma Treatment on Au-Free Ohmic Contacts to Ultrathin-Barrier AlGaN/GaN Heterostructure. IEEE Trans. Electron Devices 2019, 66, 2932–2936. [Google Scholar] [CrossRef]

- You, X.-R.; Chen, C.-W.; Tzou, J.; Hsin, Y.-M. Low-thermal-budget Au-free ohmic contact to an ultrathin barrier AlGaN/GaN heterostructure utilizing a micro-patterned ohmic recess. J. Semicond. 2021, 42, 092801. [Google Scholar]

| Dwell Time (µs) | Rc (Ω-mm) | ρc (Ω-cm2) |

|---|---|---|

| Conventional | 1.82 | 5.86 × 10−4 |

| 5 | 0.47 | 1.36 × 10−5 |

| 10 | 0.52 | 1.65 × 10−5 |

| 15 | 0.49 | 1.47 × 10−5 |

| 20 | 0.54 | 1.66 × 10−5 |

| 25 | 0.72 | 1.89 × 10−5 |

| 30 | 0.69 | 1.81 × 10−5 |

| HEMT | ID,max (mA/mm) | Ron (Ω-mm) | gm (mS/mm) |

|---|---|---|---|

| conventional | 319 | 1.03 | 80 |

| nanohole etching | 496 | 0.90 | 135 |

| Pattern | Size (μm) | Conventional Rc (Ω-mm) | POC Structure Rc (Ω-mm) | Ref. | Year |

|---|---|---|---|---|---|

| Horizontal line | 5 | - | 5.86 | [19] | 2015 |

| Close hole | 1 | - | 0.20 | [38] | 2017 |

| Square hole | 0.8 | 0.46 | 0.18 | [22] | 2017 |

| Square hole | 0.5 | 0.40 | 0.12 | [35] | 2018 |

| Grid line | 2 | 0.368 | 0.278 | [23] | 2020 |

| Graded hole | 1/3/5 | - | 0.89 | [24] | 2021 |

| Square hole | 1.5 | 1.57 | 0.56 | [39,40] | 2021 |

| Horizontal line | 1 | 0.429 | 0.154 | [25] | 2024 |

| Square hole | <0.02 × 0.02 | 1.82 | 0.47 | this work |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, H.-J.; Lee, C.-C.; Pan, H.-R.; Kuan, C.-H. Optimization of Contact Resistance and DC Characteristics for AlGaN/GaN HEMTs Utilizing Sub-10 nm Nanohole Etching. Electronics 2024, 13, 2490. https://doi.org/10.3390/electronics13132490

Lee H-J, Lee C-C, Pan H-R, Kuan C-H. Optimization of Contact Resistance and DC Characteristics for AlGaN/GaN HEMTs Utilizing Sub-10 nm Nanohole Etching. Electronics. 2024; 13(13):2490. https://doi.org/10.3390/electronics13132490

Chicago/Turabian StyleLee, Hsin-Jung, Cheng-Che Lee, Hong-Ru Pan, and Chieh-Hsiung Kuan. 2024. "Optimization of Contact Resistance and DC Characteristics for AlGaN/GaN HEMTs Utilizing Sub-10 nm Nanohole Etching" Electronics 13, no. 13: 2490. https://doi.org/10.3390/electronics13132490

APA StyleLee, H.-J., Lee, C.-C., Pan, H.-R., & Kuan, C.-H. (2024). Optimization of Contact Resistance and DC Characteristics for AlGaN/GaN HEMTs Utilizing Sub-10 nm Nanohole Etching. Electronics, 13(13), 2490. https://doi.org/10.3390/electronics13132490