Digital Finite Impulse Response Equalizer for Nonlinear Frequency Response Compensation in Wireless Communication

Abstract

1. Introduction

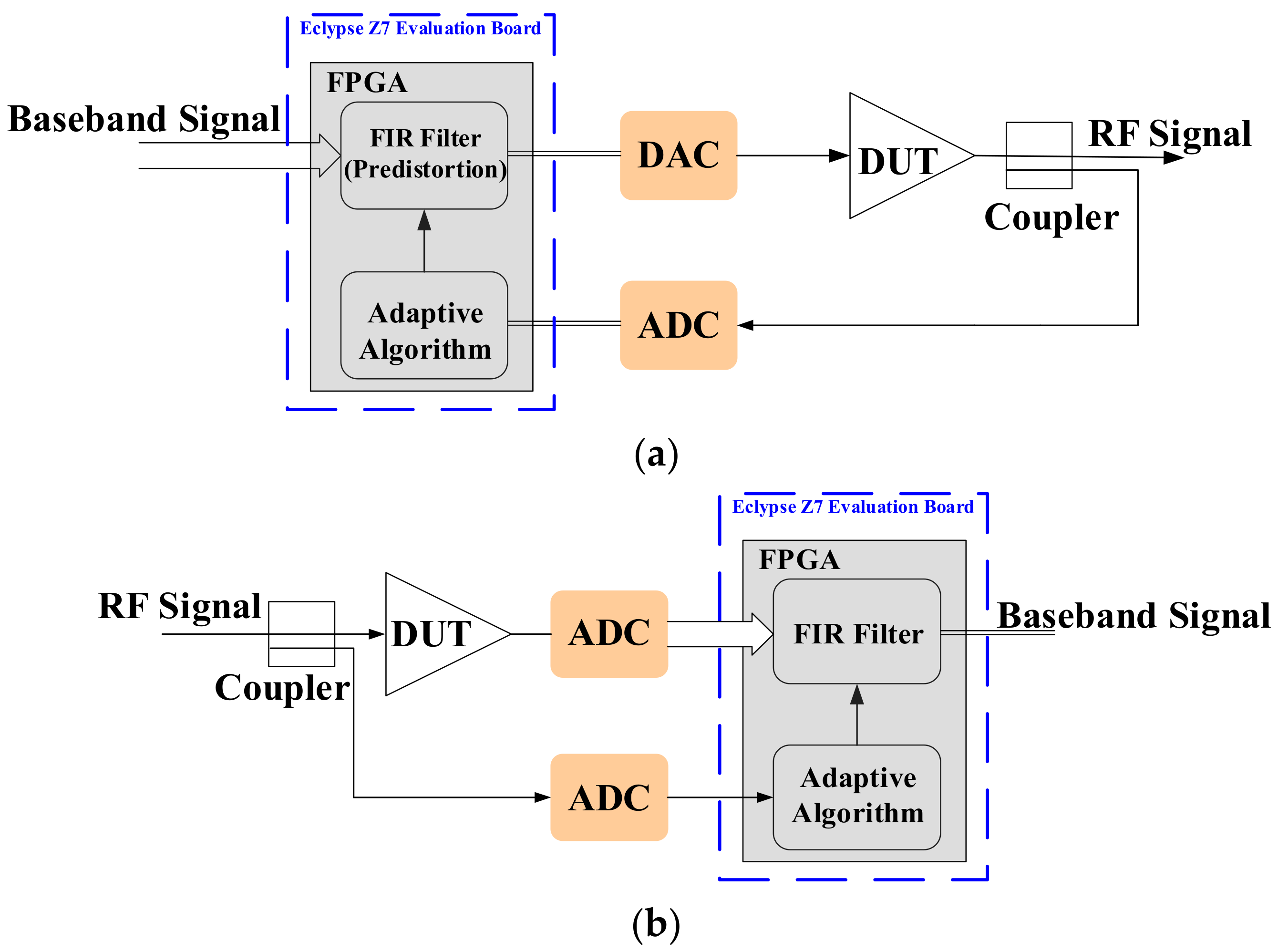

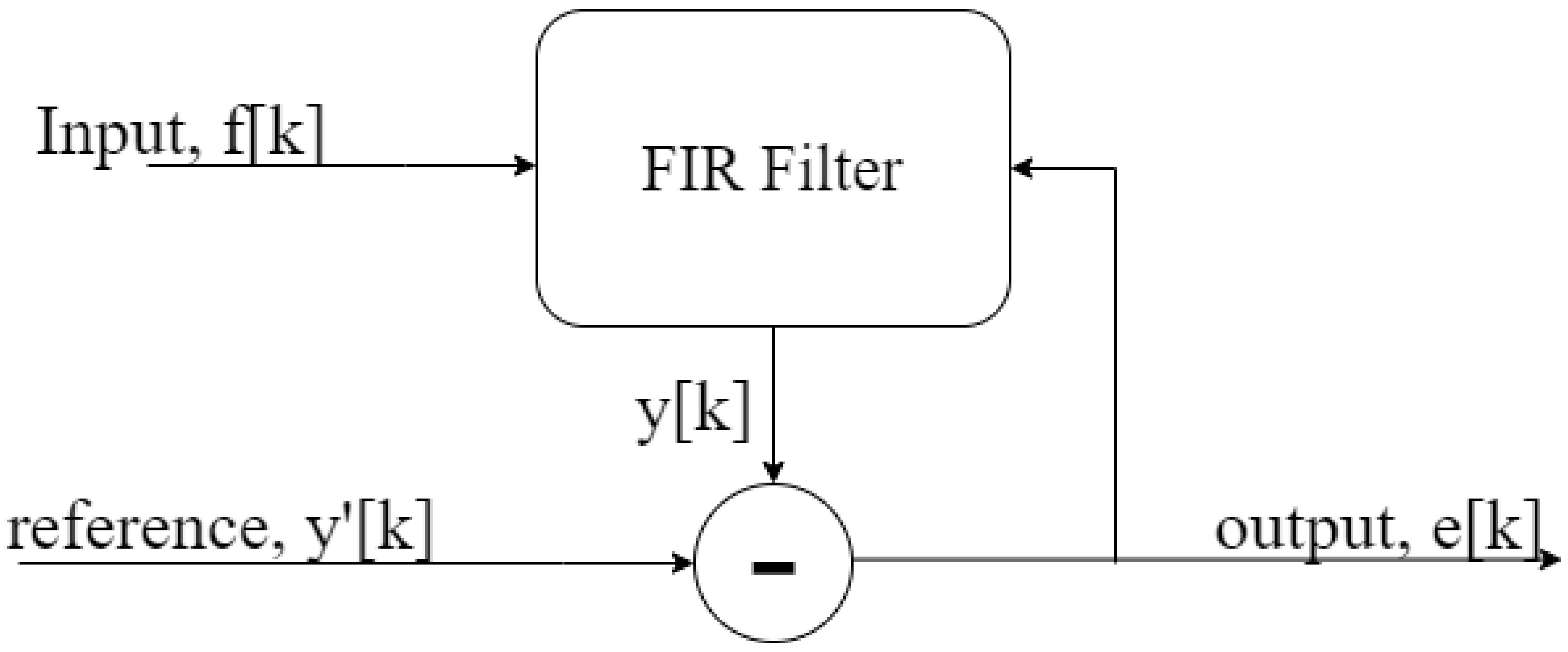

2. Principle of Digital Predistortion Equalizer Realized by Adaptive Algorithm

2.1. Equalizer Topology

2.2. LMS Coefficients Derivation

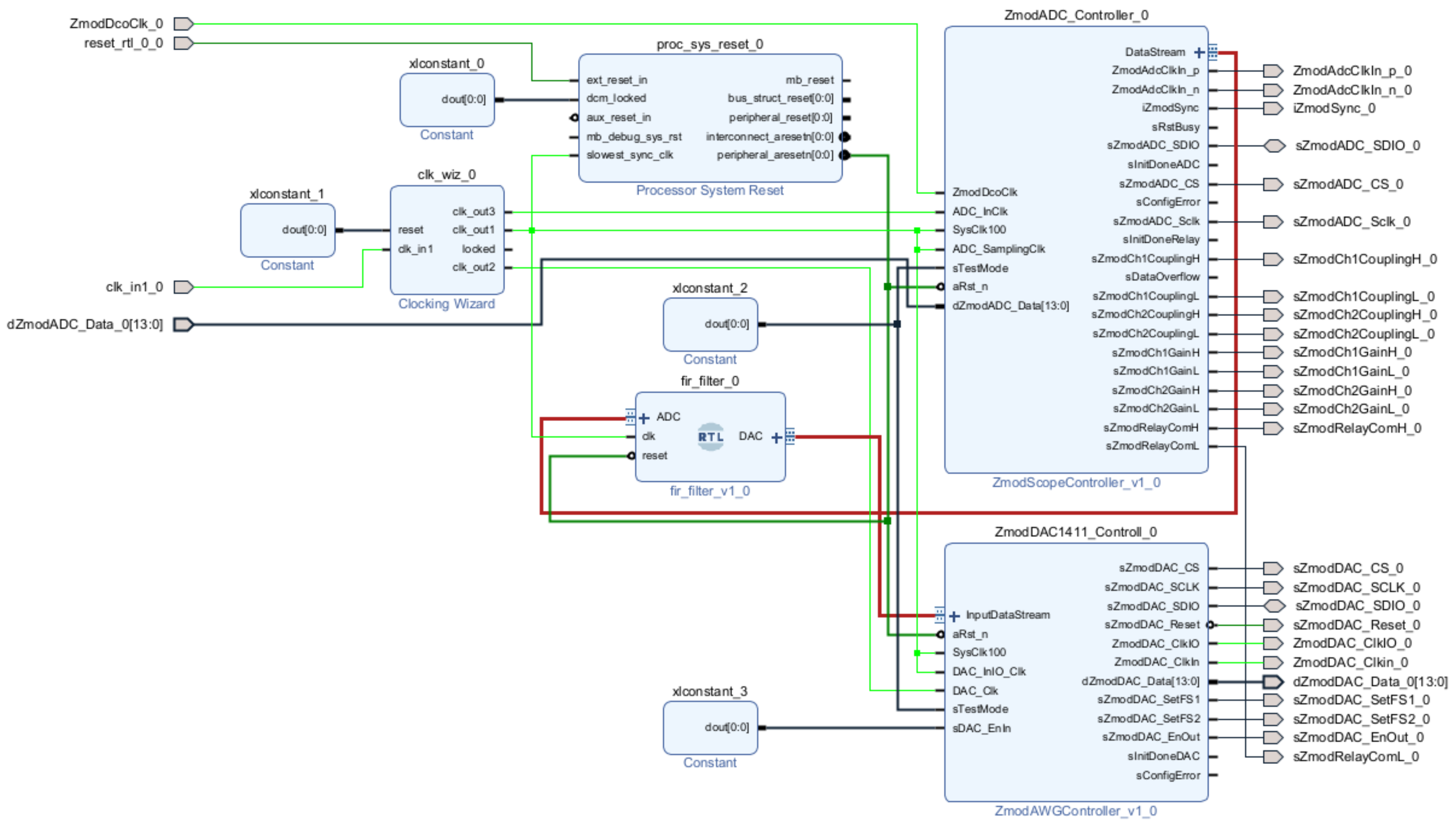

3. Implementation of Digital Predistortion Topology

3.1. MATLAB Coefficient Generation

3.2. MATLAB Sweep Read and Write

3.3. Verilog Design

4. Module Testing and Experimental Results

4.1. Software Test

4.2. RTL Module Simulation

4.3. Hardware Test

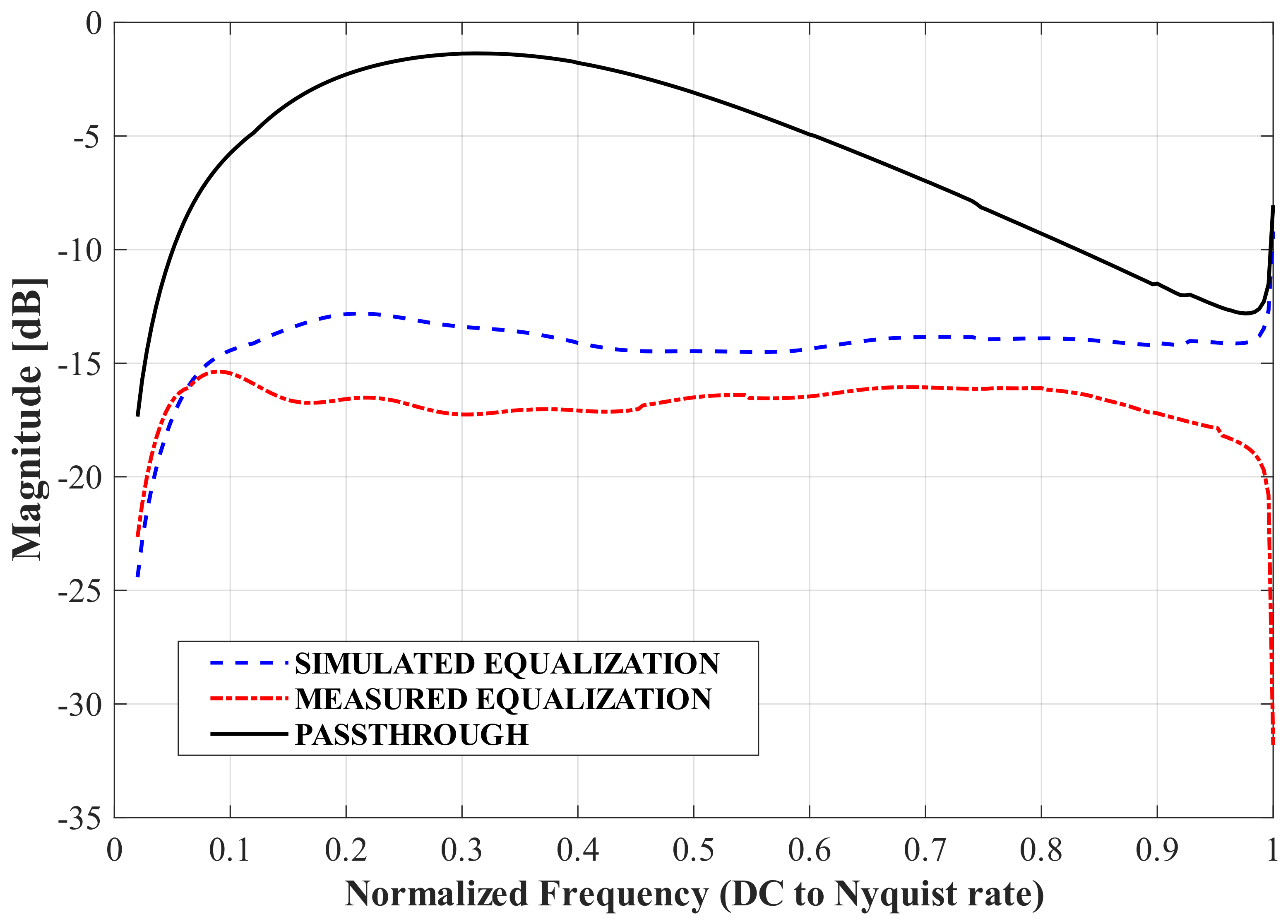

4.4. Static Equalization Results

4.5. Dynamic Equalization Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Choi, K.S.; Kim, J.H.; Ahn, D.; Jeong, N.H.; Pack, J.K. Trends in rain attenuation model in satellite system. In Proceedings of the 13th International Conference on Advanced Communication Technology (ICACT2011), Gangwon-Do, Republic of Korea, 13–16 February 2011; pp. 1530–1533. [Google Scholar]

- Dudley, D.G. Wireless propagation in circular tunnels. IEEE Trans. Antennas Propag. 2005, 53, 435–441. [Google Scholar] [CrossRef]

- Pingenot, J.; Rieben, R.; White, D. Full wave analysis of RF signal attenuation in a lossy cave using a high order time domain vector finite element method. In Proceedings of the IEEE/ACES International Conference on Wireless Communications and Applied Computational Electromagnetics, Honolulu, HI, USA, 3–7 April 2005; pp. 658–661. [Google Scholar] [CrossRef]

- Siles, G.A.; Riera, J.M.; Garcia-del-Pino, P. Atmospheric Attenuation in Wireless Communication Systems at Millimeter and THz Frequencies [Wireless Corner]. IEEE Antennas Propag. Mag. 2015, 57, 48–61. [Google Scholar] [CrossRef]

- Dulk, G.A.; Erickson, W.C.; Manning, R.; Bougeret, J.L. Calibration of low-frequency radio telescopes using the galactic background radiation. Astron. Astrophys. 2001, 365, 294–300. [Google Scholar] [CrossRef]

- Winder, S. Analog and Digital Filter Design; Newnes: Amsterdam, The Netherlands, 2007. [Google Scholar]

- Der Ziel, A. Thermal noise in field-effect transistors. In Proceedings of the IRE; IEEE: New York, NY, USA, 1962; Volume 50, pp. 1808–1812. [Google Scholar]

- Lin, Y.-S.; Chen, C.-Z.; Yang, H.-Y.; Chen, C.-C.; Lee, J.-H.; Huang, G.-W.; Lu, S.-S. Analysis and Design of a CMOS UWB LNA With Dual-RLC-Branch Wideband Input Matching Network. IEEE Trans. Microw. Theory Tech. 2010, 58, 287–296. [Google Scholar] [CrossRef]

- Wu, C.; Lin, Y.; Lee, J.; Wang, C. A 2.87 ± 0.19 dB NF 3.1∼10.6 GHz ultra-wideband low-noise amplifier using 0.18 µm CMOS technology. In Proceedings of the 2012 IEEE Radio and Wireless Symposium, Santa Clara, CA, USA, 15–18 January 2012; pp. 227–230. [Google Scholar] [CrossRef]

- Lathi, B.P. Principles of Signal Processing and Linear Systems; Oxford University Press: Oxford, UK, 2009. [Google Scholar]

- Borth, D.E.; Gerson, I.A.; Haug, J.R.; Thompson, C.D. A flexible adaptive FIR filter VLSI IC. IEEE J. Sel. Areas Commun. 1988, 6, 494–503. [Google Scholar] [CrossRef]

- Lucky, R.W. Techniques for adaptive equalization of digital communication systems. Bell Syst. Tech. J. 1966, 45, 255–286. [Google Scholar] [CrossRef]

- Moulines, E.; Duhamel, P.; Cardoso, J.; Mayrargue, S. Subspace methods for blind identification of multichannel FIR filters. IEEE Trans. Signal Process. 1995, 43, 516–525. [Google Scholar] [CrossRef]

- Widrow, B.; Stearns, S.D. Adaptive Signal Processing; Prentice-Hall: Engelwood Cliffs, NJ, USA, 1985. [Google Scholar]

- Haykin, S. Adaptive Filter Theory, 3rd ed.; Prentice-Hall: Engelwood Cliffs, NJ, USA, 1996. [Google Scholar]

- Lo, B.C.W.; Letaief, K. Adaptive equalization and interference cancellation for wireless communication systems. IEEE Trans. Commun. 1999, 47, 538–545. [Google Scholar] [CrossRef]

- Kollar, I.; Rolain, Y. Complex correction of data acquisition channels using FIR equalizer filters. IEEE Trans. Instrum. Meas. 1993, 42, 920–924. [Google Scholar] [CrossRef][Green Version]

- Johnson, R.; Schniter, P.; Endres, T.J.; Behm, J.D.; Brown, D.R.; Casas, R.A. Blind equalization using the constant modulus criterion: A review. Proc. IEEE 1998, 86, 1927–1950. [Google Scholar] [CrossRef]

- John, P.G.; Dimitris, M.G. Digital Signal Processing Principles, Algorithms, and Applications, 3rd ed.; Prentice-Hall: Engelwood Cliffs, NJ, USA, 1996. [Google Scholar]

- Smith, J.O., III. Spectral Audio Signal Processing; W3K Publishing: Berlin, German, 2011. [Google Scholar]

- Lai, Y.T.; Kao, C.C.; Chen, H.J. Design and Implementation of an Adaptive FIR Filter Based on Delayed Error LMS Algorithm. In Proceedings of the 1999 IEEE Workshop on Signal Processing Systems. SiPS 99. Design and Implementation (Cat. No.99TH8461), Taipei, Taiwan, 22 October 1999; pp. 704–712. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, Z.; Li, Y.; Nima, B. Digital Finite Impulse Response Equalizer for Nonlinear Frequency Response Compensation in Wireless Communication. Electronics 2023, 12, 2010. https://doi.org/10.3390/electronics12092010

Zhang Z, Li Y, Nima B. Digital Finite Impulse Response Equalizer for Nonlinear Frequency Response Compensation in Wireless Communication. Electronics. 2023; 12(9):2010. https://doi.org/10.3390/electronics12092010

Chicago/Turabian StyleZhang, Zhenyu, Yanan Li, and Bassam Nima. 2023. "Digital Finite Impulse Response Equalizer for Nonlinear Frequency Response Compensation in Wireless Communication" Electronics 12, no. 9: 2010. https://doi.org/10.3390/electronics12092010

APA StyleZhang, Z., Li, Y., & Nima, B. (2023). Digital Finite Impulse Response Equalizer for Nonlinear Frequency Response Compensation in Wireless Communication. Electronics, 12(9), 2010. https://doi.org/10.3390/electronics12092010