Design of a GaAs-Based Ka-Band Low Noise Amplifier MMIC with Gain Flatness Enhancement

Abstract

1. Introduction

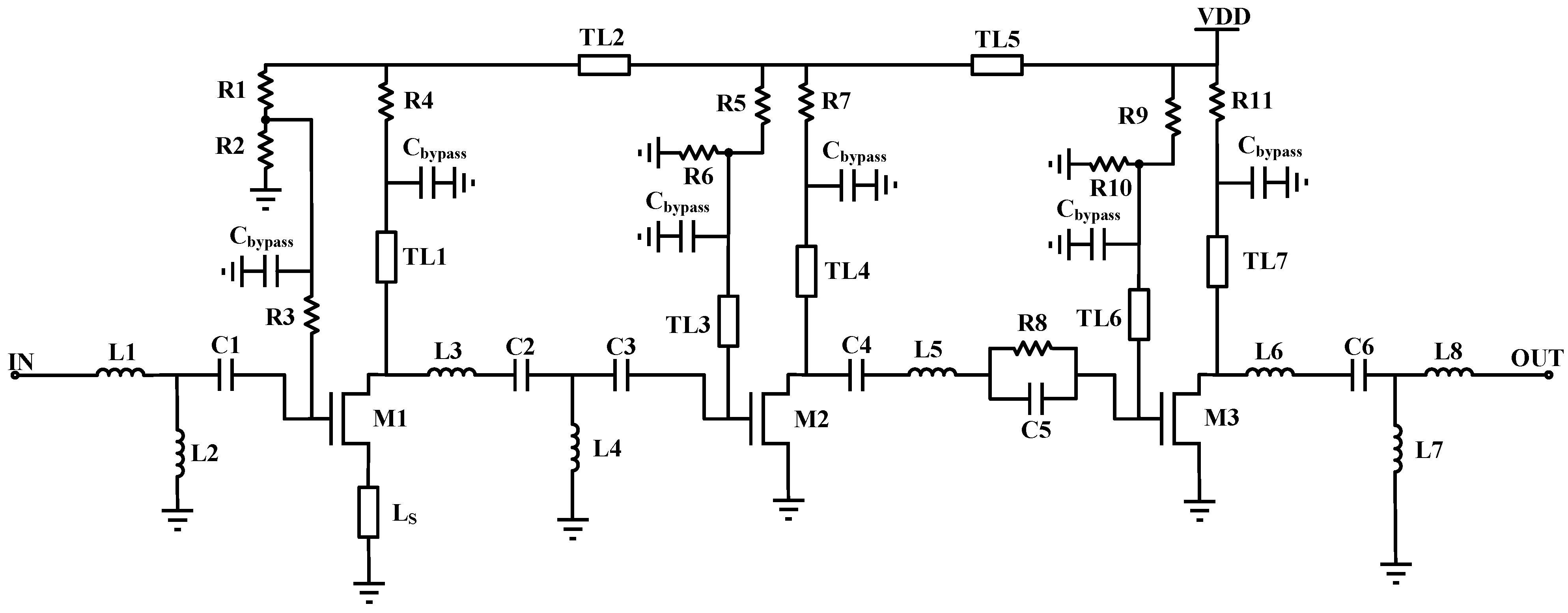

2. Circuit Design

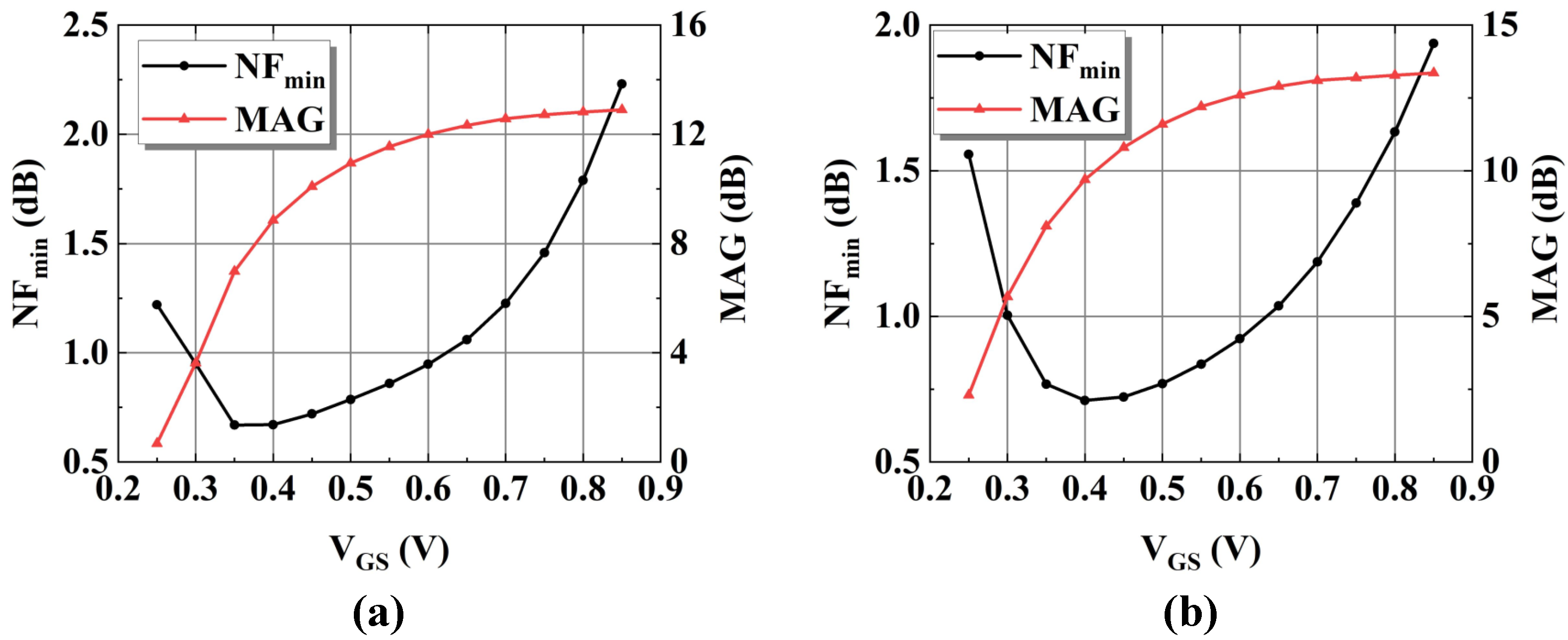

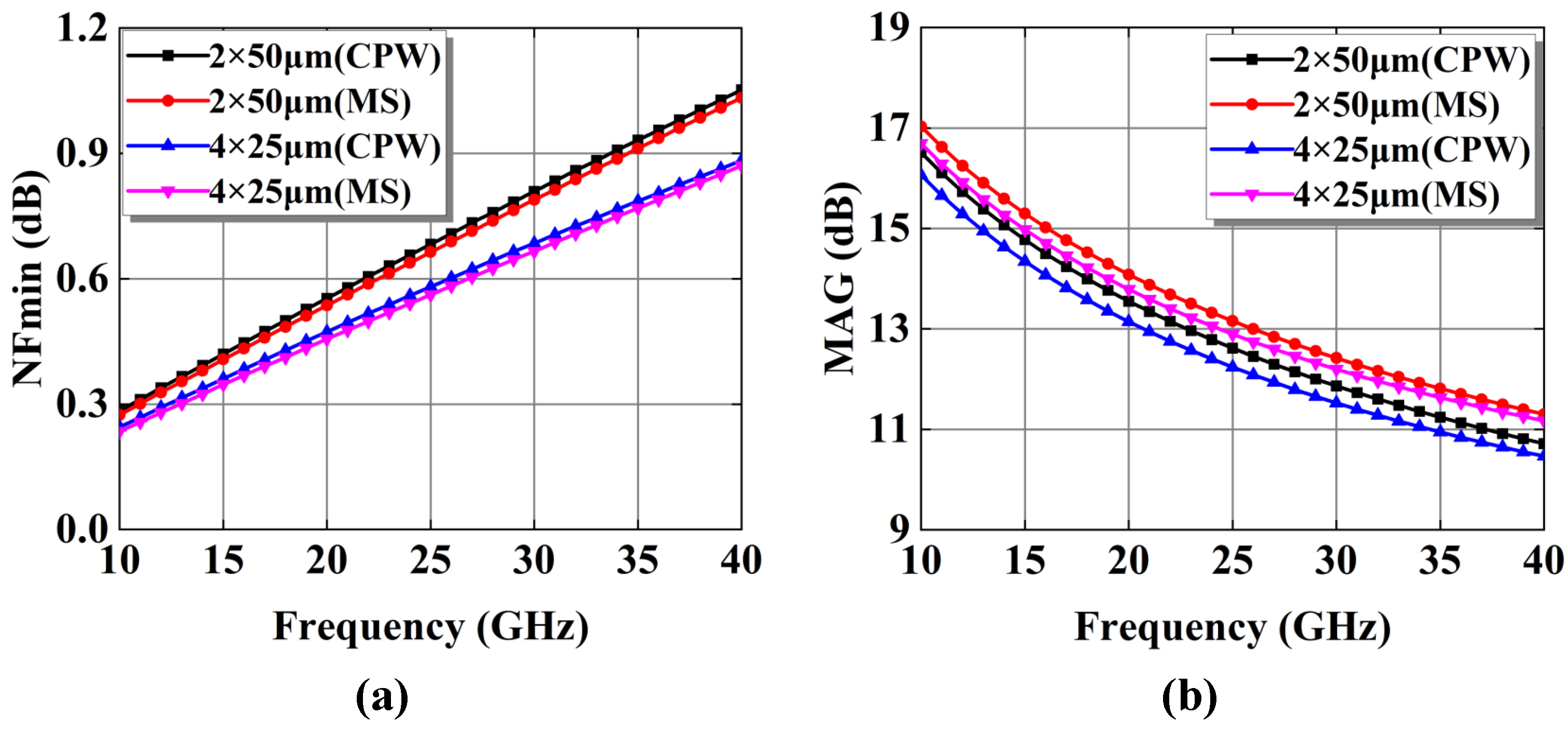

2.1. Active Device Optimization

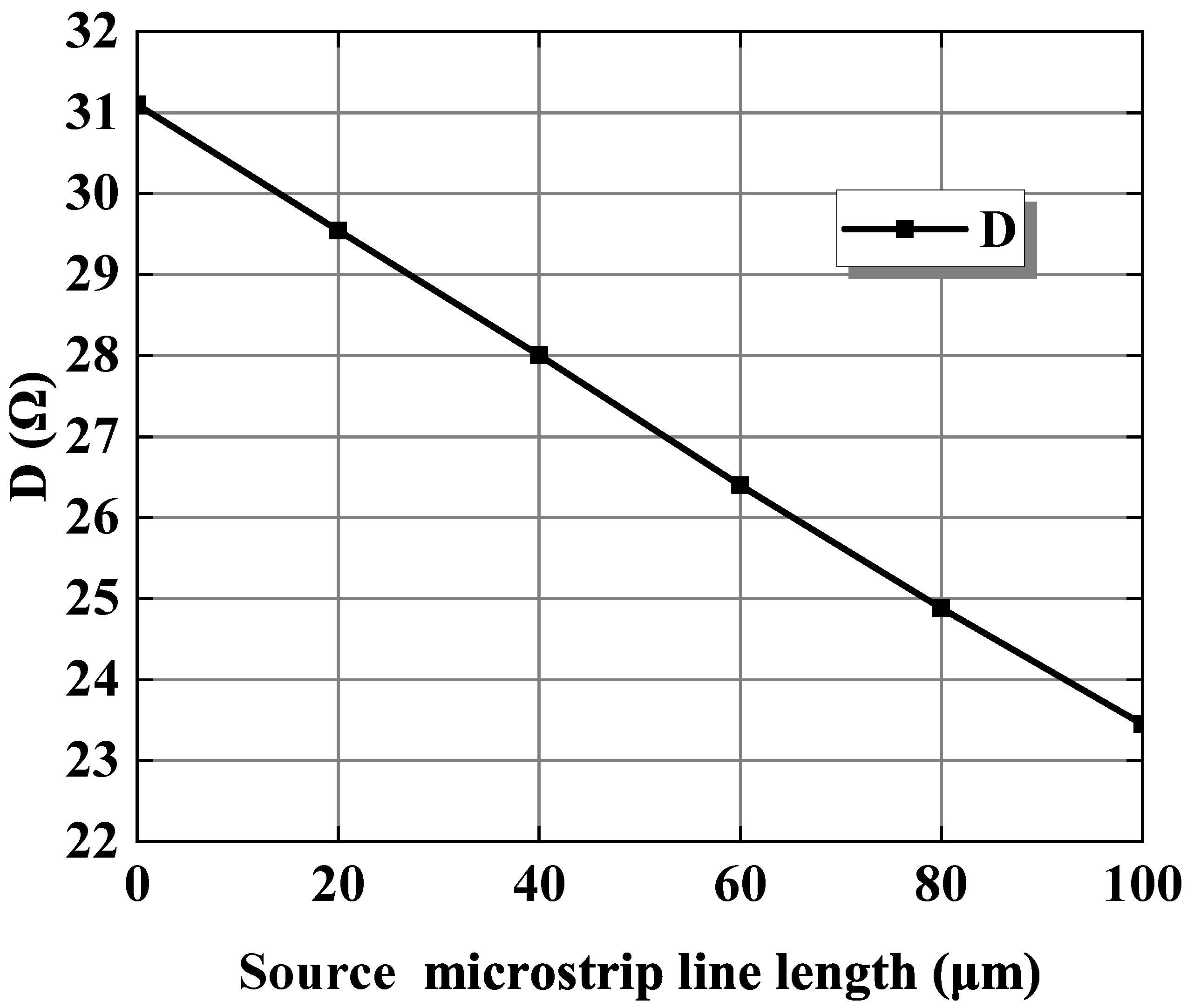

2.2. Inductive Degeneration

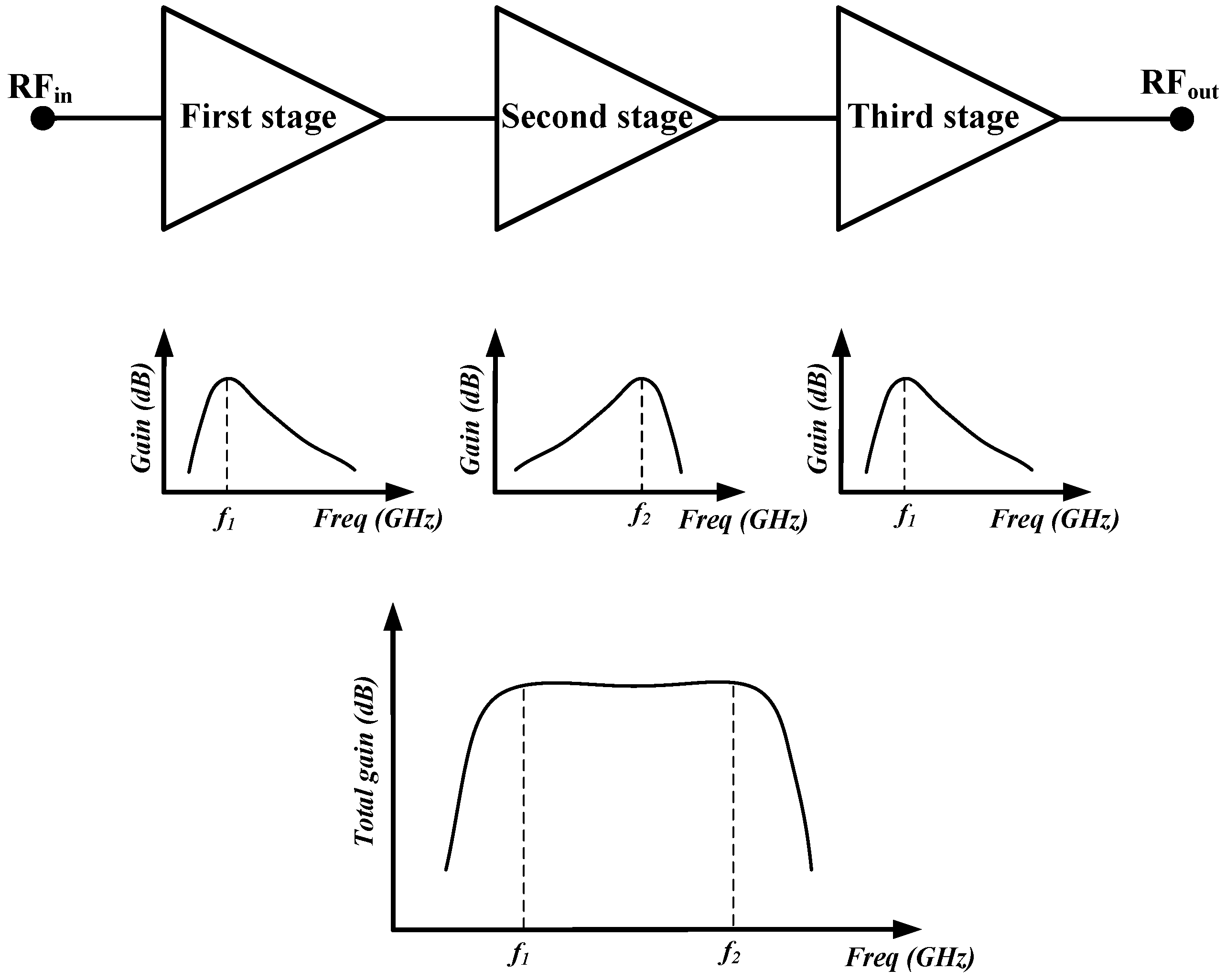

2.3. Gain Flatness Enhancement

2.3.1. Gain Analysis of the First Stage

2.3.2. Gain Analysis of the Second Stage

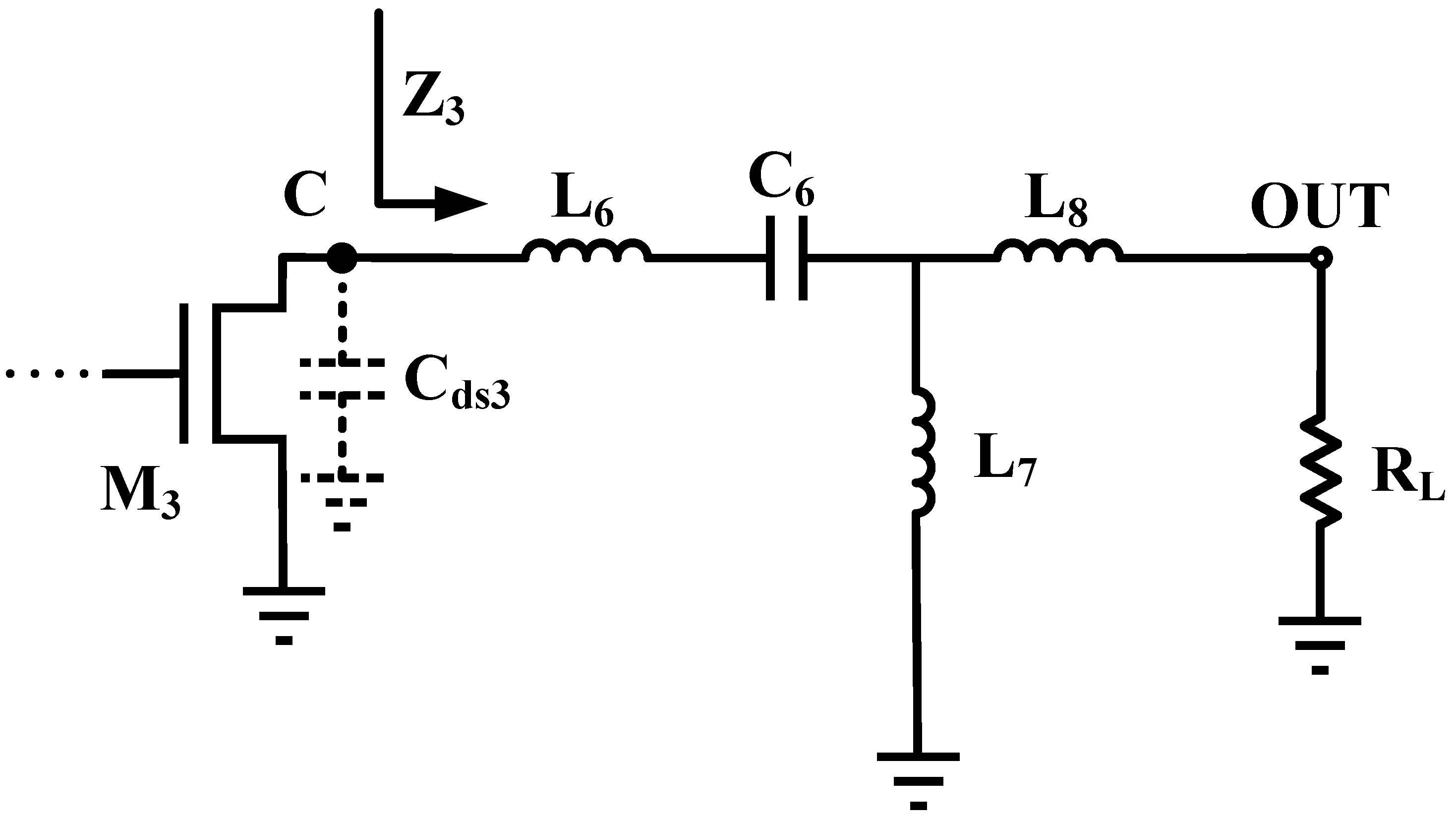

2.3.3. Gain Analysis of the Third Stage

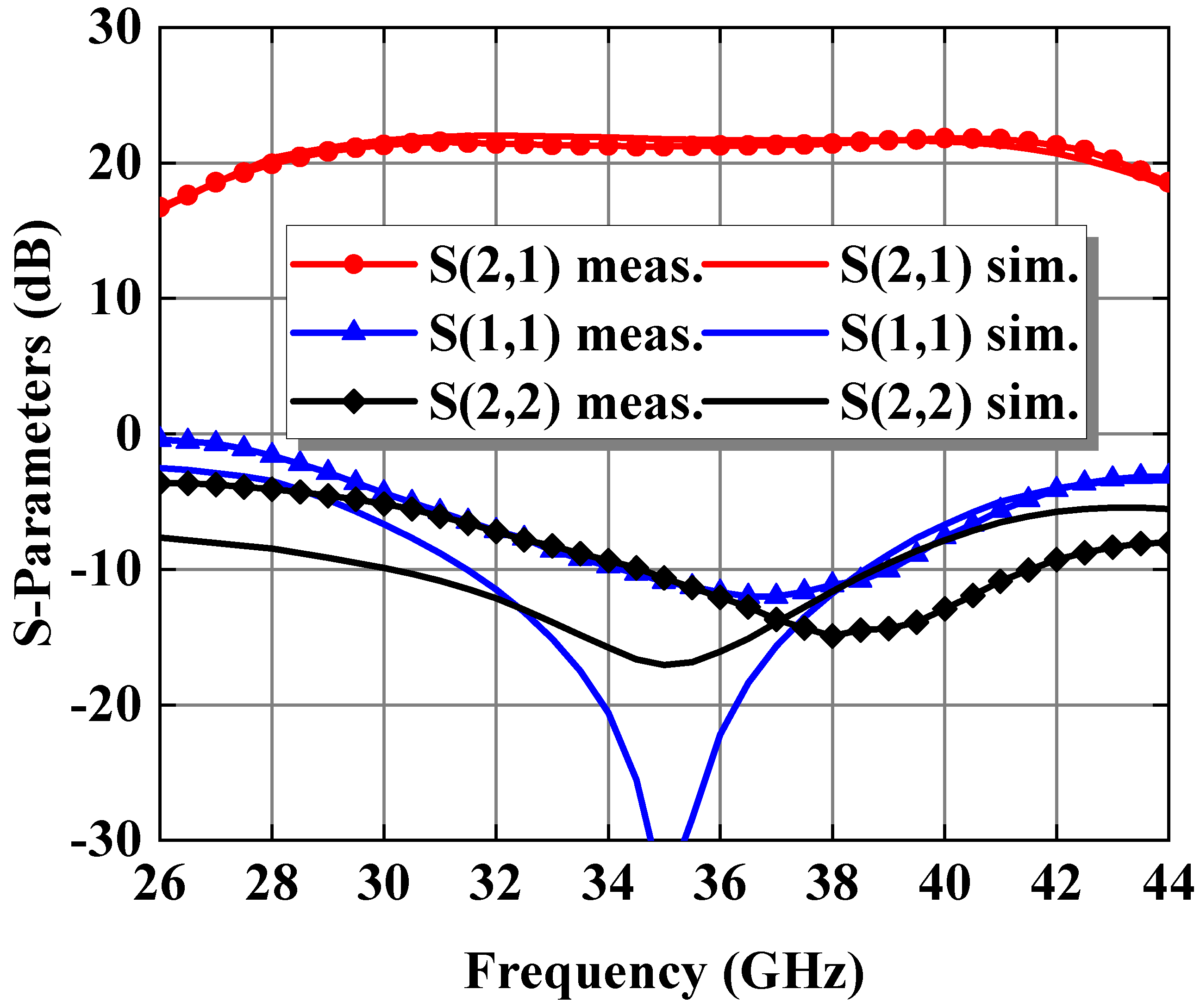

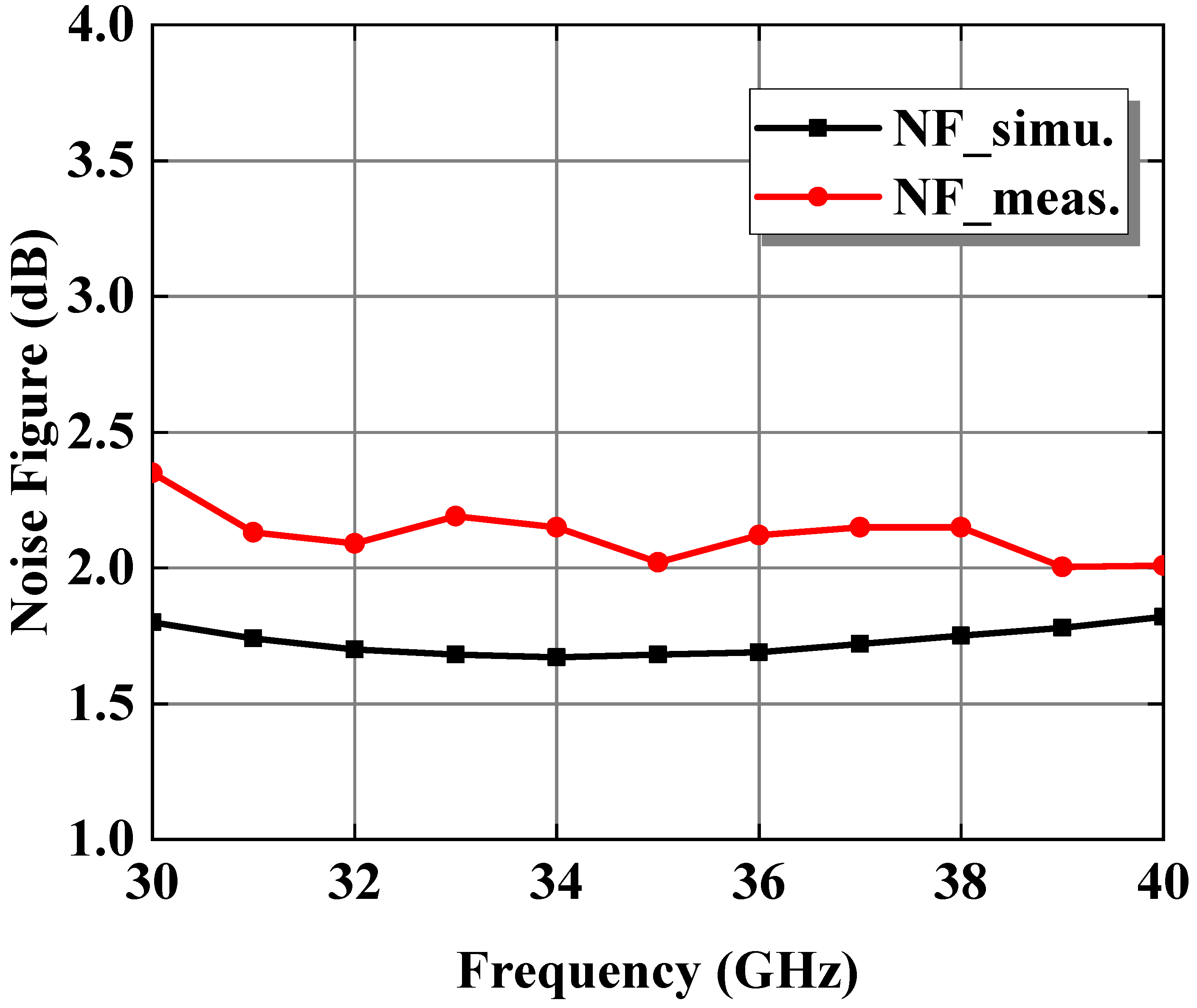

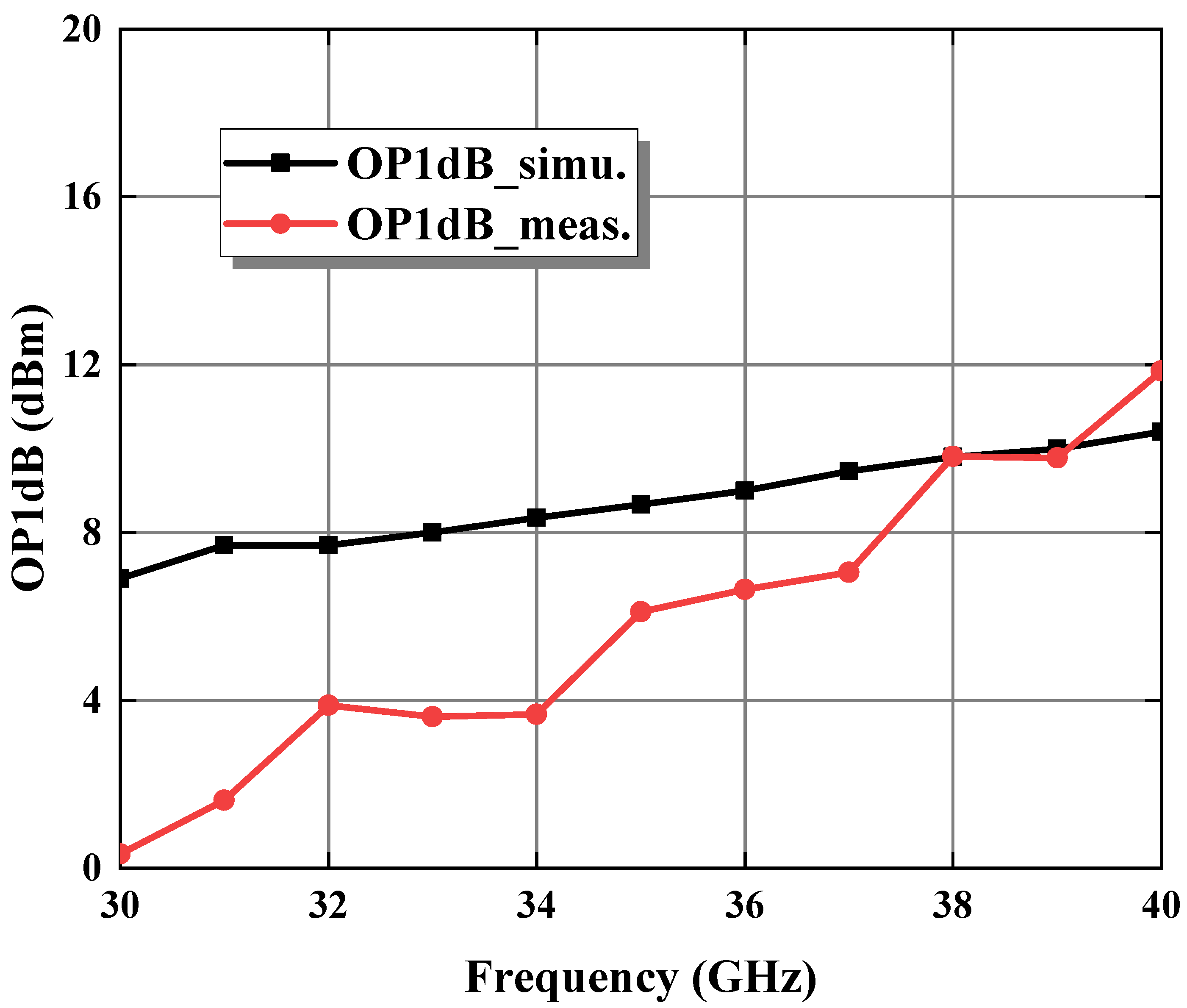

3. Experimental Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Hu, S.; Wang, F.; Wang, H. A 28-/37-/39-GHz Linear Doherty Power Amplifier in Silicon for 5G Applications. IEEE J. Solid-State Circuits 2019, 54, 1586–1599. [Google Scholar] [CrossRef]

- Schwantuschke, D.; Aja, B.; Seelmann-Eggebert, M.; Quay, R.; Leuther, A.; Bruckner, P.; Schlechtweg, M.; Mikulla, M.; Kallfass, I.; Ambacher, O. Q- and E-Band Amplifier MMICs for Satellite Communication. In Proceedings of the 2014 IEEE MTT-S International Microwave Symposium (IMS2014), Tampa, FL, USA, 1–6 June 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 1–4. [Google Scholar]

- Yujiri, L.; Shoucri, M.; Moffa, P. Passive Millimeter Wave Imaging. IEEE Microw. Mag. 2003, 4, 39–50. [Google Scholar] [CrossRef]

- Yujiri, L. Passive Millimeter Wave Imaging. In Proceedings of the 2006 IEEE MTT-S International Microwave Symposium Digest, San Francisco, CA, USA, 11–16 June 2006; pp. 98–101. [Google Scholar]

- Gong, J.; Chen, X.; Hu, A.; Miao, J. Design of a V-Band Low Noise Amplifier for Passive Millimeter Wave Imaging Application. Microelectron. J. 2022, 126, 105491. [Google Scholar] [CrossRef]

- Wan, Q.; Wang, C. Design of 3.1–10.6 GHz Ultra-Wideband CMOS Low Noise Amplifier with Current Reuse Technique. AEU-Int. J. Electron. Commun. 2011, 65, 1006–1011. [Google Scholar] [CrossRef]

- Yu, Y.-H.; Yang, Y.-S.; Chen, Y.-J.E. A Compact Wideband CMOS Low Noise Amplifier with Gain Flatness Enhancement. IEEE J. Solid-State Circuits 2010, 45, 502–509. [Google Scholar] [CrossRef]

- Liu, R.C.; Lin, C.S.; Deng, K.L.; Wang, H. A 0.5-14-GHz 10.6-dB CMOS Cascode Distributed Amplifier. In Proceedings of the 2003 Symposium on VLSI Circuits. Digest of Technical Papers (IEEE Cat. No.03CH37408), Kyoto, Japan, 12–14 June 2003; pp. 139–140. [Google Scholar]

- Lu, Y.; Yeo, K.S.; Cabuk, A.; Ma, J.; Do, M.A.; Lu, Z. A Novel CMOS Low-Noise Amplifier Design for 3.1- to 10.6-GHz Ultra-Wide-Band Wireless Receivers. IEEE Trans. Circuits Syst. I 2006, 53, 1683–1692. [Google Scholar] [CrossRef]

- Kim, C.W.; Kang, M.S.; Anh, P.T.; Kim, H.T.; Lee, S.G. An Ultra-Wideband CMOS Low Noise Amplifier for 3-5-GHz UWB System. IEEE J. -Solid-State Circuits 2005, 40, 544–547. [Google Scholar] [CrossRef]

- Zhan, J.H.C.; Taylor, S.S. A 5 GHz Resistive-Feedback CMOS LNA for Low-Cost Multi-Standard Applications. In Proceedings of the 2006 IEEE International Solid State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 6–9 February 2006; pp. 721–730. [Google Scholar]

- Ismail, A.; Abidi, A.A. A 3-10-GHz Low-Noise Amplifier with Wideband LC-Ladder Matching Network. IEEE J. -Solid-State Circuits 2004, 39, 2269–2277. [Google Scholar] [CrossRef]

- Nguyen, D.P.; Pham, B.L.; Pham, T.; Pham, A.-V. A 14–31 GHz 1.25 DB NF Enhancement Mode GaAs PHEMT Low Noise Amplifier. In Proceedings of the 2017 IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 4–9 June 2017; pp. 1961–1964. [Google Scholar]

- Weng, S.-H.; Lin, C.-H.; Chang, H.-Y.; Chiong, C.-C. Q-Band Low Noise Amplifiers Using a 0.15 μm MHEMT Process for Broadband Communication and Radio Astronomy Applications. In Proceedings of the 2008 IEEE MTT-S International Microwave Symposium Digest, Atlanta, GA, USA, 15–20 June 2008; pp. 455–458. [Google Scholar]

- Yang, L.; Yang, L.-A.; Rong, T.; Li, Y.; Jin, Z.; Hao, Y. Codesign of Ka-Band Integrated GaAs PIN Diodes Limiter and Low Noise Amplifier. IEEE Access 2019, 7, 88275–88281. [Google Scholar] [CrossRef]

- Feng, J.-H.; Ye, Y.-F.; Wu, L.-S.; Mao, J.-F. A Ka-Band Broadband Low Noise Amplifier with Resistive and Inductive Feedback. In Proceedings of the 2022 IEEE 4th International Conference on Circuits and Systems (ICCS), Chengdu, China, 23–26 September 2022; pp. 160–163. [Google Scholar]

- Lehmann, R.E.; Heston, D.D. X-Band Monolithic Series Feedback LNA. IEEE Trans. Microw. Theory Tech. 1985, 33, 1560–1566. [Google Scholar] [CrossRef]

- Nguyen, T.-K.; Kim, C.-H.; Ihm, G.-J.; Yang, M.-S.; Lee, S.-G. CMOS Low-Noise Amplifier Design Optimization Techniques. IEEE Trans. Microw. Theory Tech. 2004, 52, 1433–1442. [Google Scholar] [CrossRef]

- Hu, Y.; Chi, T. A 27–46-GHz Low-Noise Amplifier with Dual-Resonant Input Matching and a Transformer-Based Broadband Output Network. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 725–728. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics, 2nd ed.; Prentice Hall: Upper Saddle River, NJ, USA, 2012. [Google Scholar]

- Liu, J.; Tu, J.; Wu, Y.; Feng, G. Bandwidth Extension Techniques for CMOS Low-Noise Amplifiers. In Proceedings of the 2021 IEEE MTT-S International Wireless Symposium (IWS), Nanjing, China, 23 May 2021; pp. 1–3. [Google Scholar]

- Jang, T.H.; Jung, K.P.; Kang, J.-S.; Byeon, C.W.; Park, C.S. 120-GHz 8-Stage Broadband Amplifier with Quantitative Stagger Tuning Technique. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 785–796. [Google Scholar] [CrossRef]

- Yu, Y.-H.; Hsu, W.-H.; Chen, Y.-J.E. A Ka-Band Low Noise Amplifier Using Forward Combining Technique. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 672–674. [Google Scholar] [CrossRef]

- Wang, G.; Chen, W.; Liu, J.; Mo, J.; Chen, H.; Wang, Z.; Yu, F. Design of a Broadband Ka-Band MMIC LNA Using Deep Negative Feedback Loop. IEICE Electron. Express 2018, 15, 20180317. [Google Scholar] [CrossRef]

- Chen, Y.-M.; Wang, Y.; Chiong, C.-C.; Wang, H. A 21.5-50 GHz Low Noise Amplifier in 0.15-μm GaAs PHEMT Process for Radio Astronomical Receiver System. In Proceedings of the 2021 IEEE Asia-Pacific Microwave Conference (APMC), Brisbane, Australia, 28 November 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 7–9. [Google Scholar]

- Chou, Y.-T.; Chiong, C.-C.; Wang, H. A Q-Band LNA with 55.7% Bandwidth for Radio Astronomy Applications in 0.15-μm GaAs PHEMT Process. In Proceedings of the 2016 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Taipei, Taiwan, 24–26 August 2016; pp. 1–3. [Google Scholar]

- Nikandish, G.; Yousefi, A.; Kalantari, M. A Broadband Multistage LNA with Bandwidth and Linearity Enhancement. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 834–836. [Google Scholar] [CrossRef]

| Reference | This Work | [23] | [24] | [25] | [26] | [27] |

|---|---|---|---|---|---|---|

| Process | 0.15-µm GaAs pHEMT | 0.15-µm InGaAs pHEMT | 0.15-µm GaAs pHEMT | 0.15-µm GaAs pHEMT | 0.15-µm GaAs pHEMT | 0.1-µm GaAs pHEMT |

| Frequency (GHz) | 32–40 | 29–43 | 25–40 | 22.5–34 | 28.5–50.5 | 18–43 |

| Gain (dB) | 21.5 | 14.2 | 20 | 22.5 | 23 | 21.6 |

| Gain flatness (dB) | ±0.3 | NA | ±1.5 | ±1.2 | ±1.5 | ±1.5 |

| NF (dB) | 2.2 | 2–3.3 | 2.8 | 3–4.5 | 3.8 | 1.8–2.7 |

| Area (mm) | 1.5 × 0.9 | 0.65 × 0.72 | 2.5 × 1.2 | 2.5 × 1 | 2 × 1.5 | 2 × 1 |

| Power (mW) | 56 | 38 | 230 | 36 | 62.6 | 140 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, Z.; Wang, K.; Fan, Y.; Yan, Y.; Liang, X. Design of a GaAs-Based Ka-Band Low Noise Amplifier MMIC with Gain Flatness Enhancement. Electronics 2023, 12, 2325. https://doi.org/10.3390/electronics12102325

Yang Z, Wang K, Fan Y, Yan Y, Liang X. Design of a GaAs-Based Ka-Band Low Noise Amplifier MMIC with Gain Flatness Enhancement. Electronics. 2023; 12(10):2325. https://doi.org/10.3390/electronics12102325

Chicago/Turabian StyleYang, Zhe, Kuisong Wang, Yihui Fan, Yuepeng Yan, and Xiaoxin Liang. 2023. "Design of a GaAs-Based Ka-Band Low Noise Amplifier MMIC with Gain Flatness Enhancement" Electronics 12, no. 10: 2325. https://doi.org/10.3390/electronics12102325

APA StyleYang, Z., Wang, K., Fan, Y., Yan, Y., & Liang, X. (2023). Design of a GaAs-Based Ka-Band Low Noise Amplifier MMIC with Gain Flatness Enhancement. Electronics, 12(10), 2325. https://doi.org/10.3390/electronics12102325