Low-Power Single Bitline Load Sense Amplifier for DRAM

Abstract

:1. Introduction

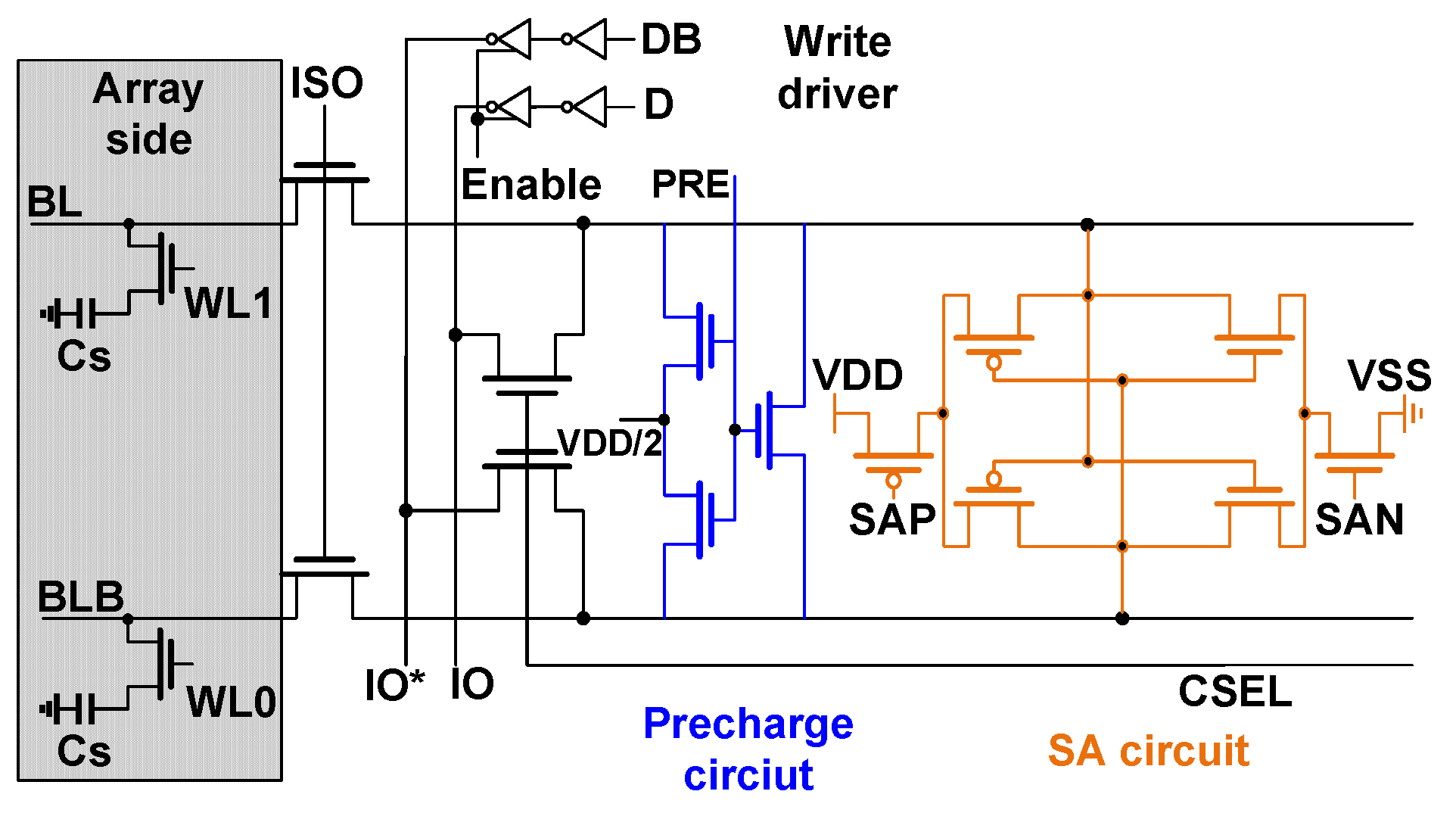

2. Methods

2.1. The Energy Consumption at Different Working Stages

2.1.1. Precharge Stage

2.1.2. Pre-Sense and Post-Sense Stage

2.1.3. IO Transition Stage

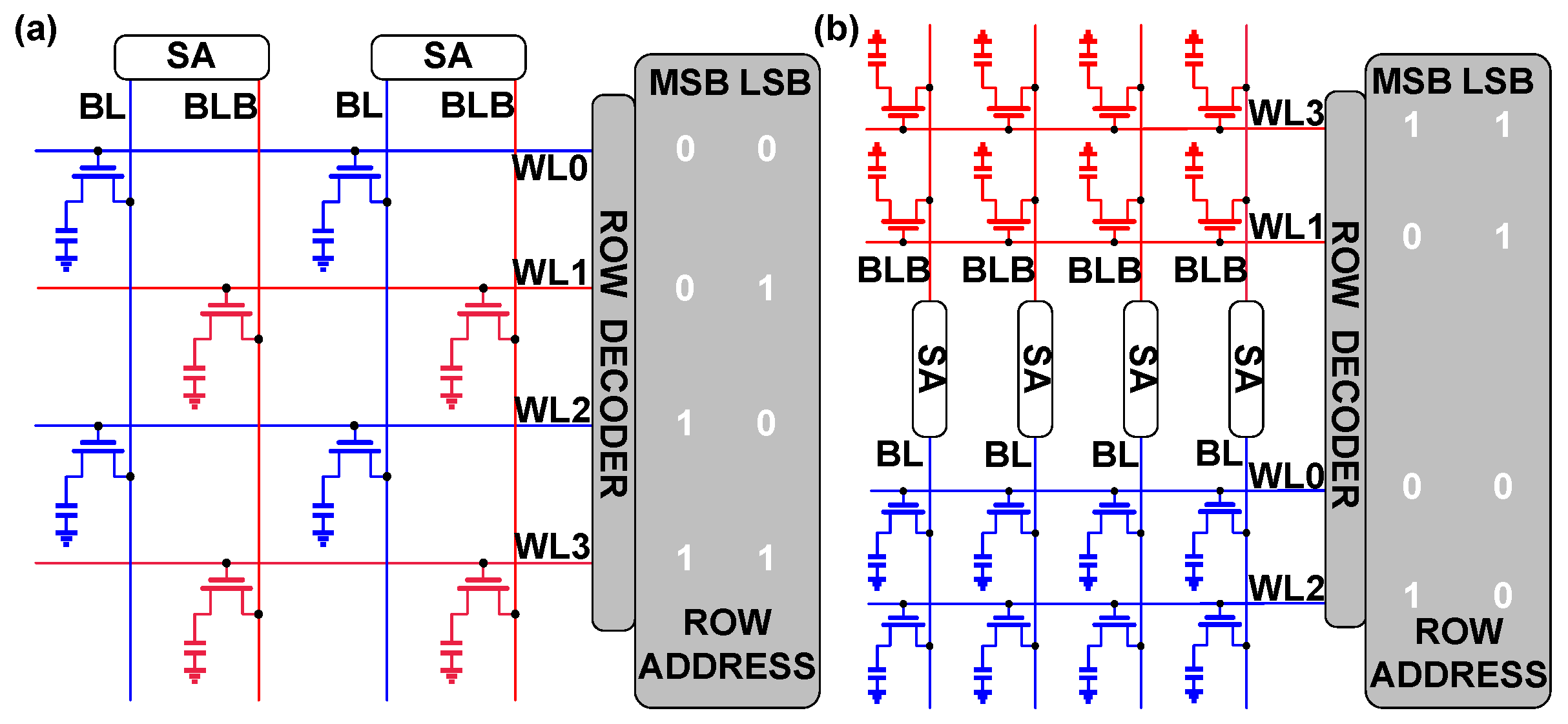

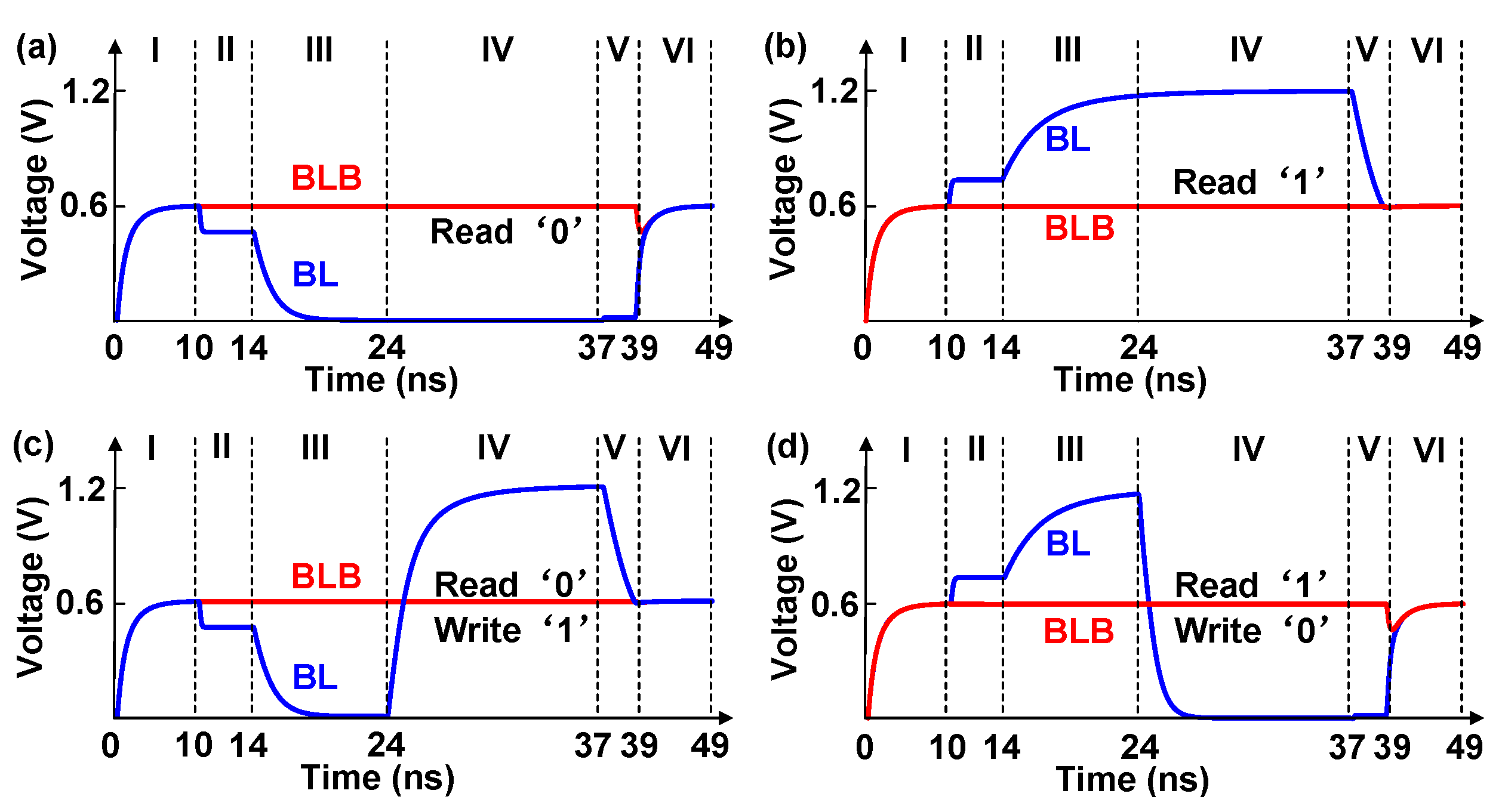

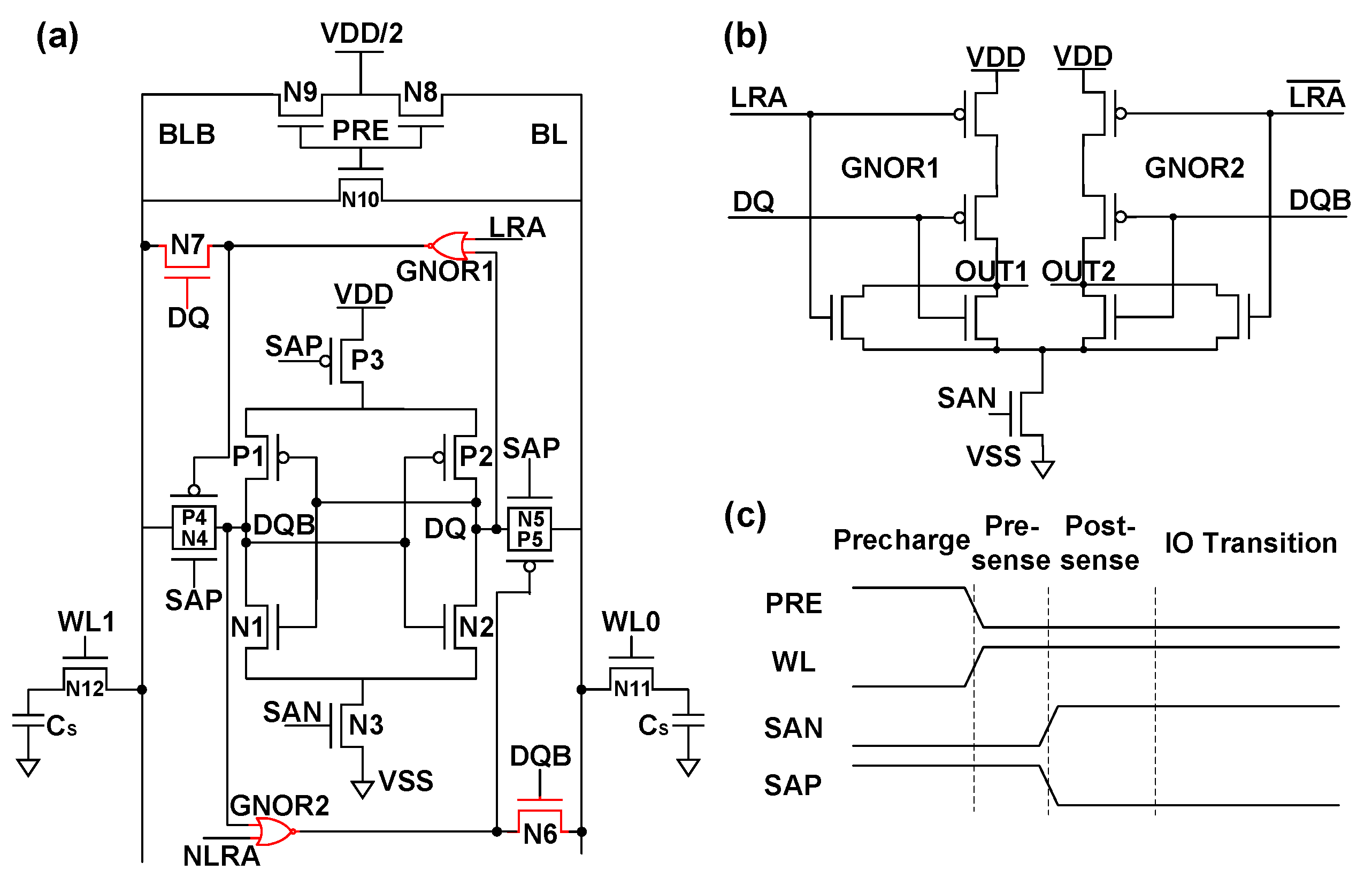

2.2. Analysis of the Single Bitline Load Sense Amplifier

2.3. Redundant Voltage Discharge Sense Amplifier

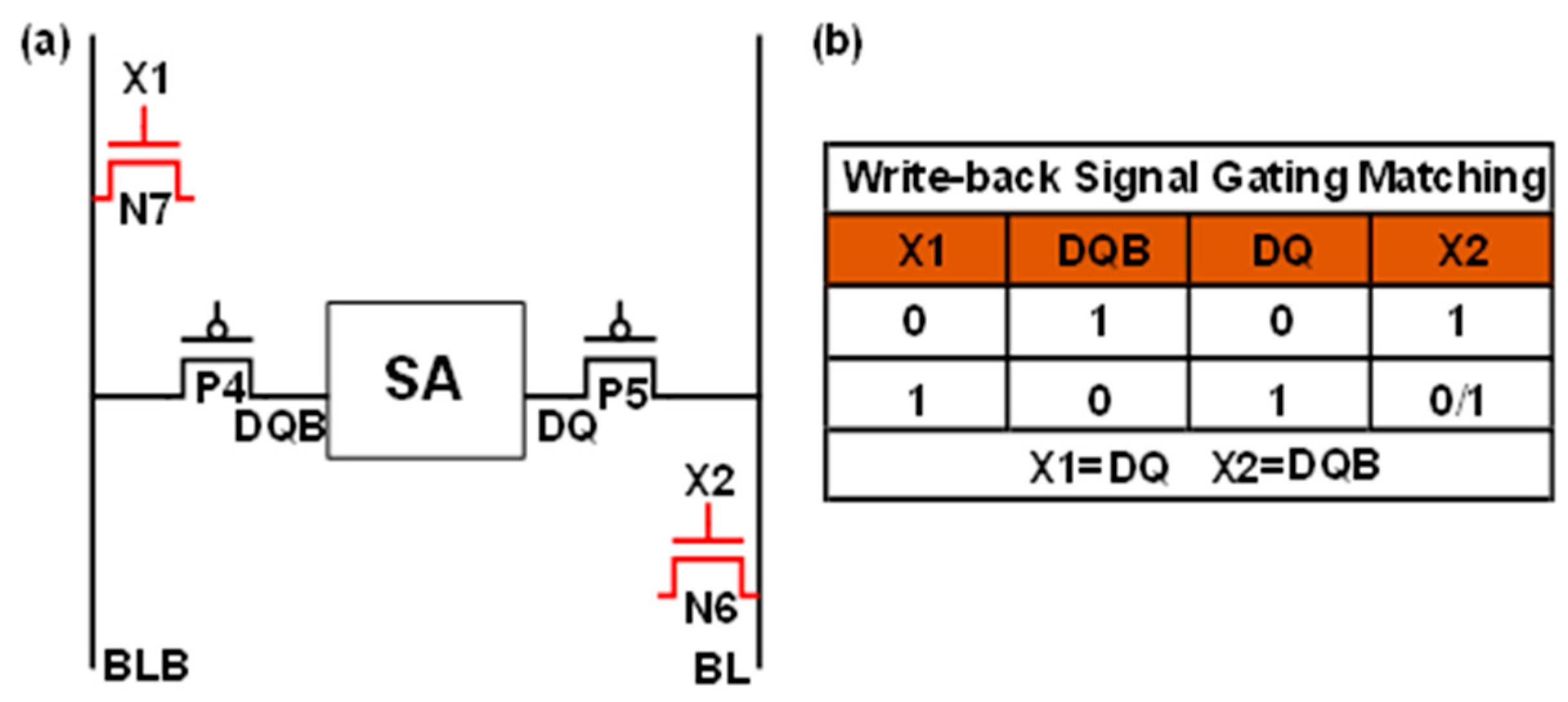

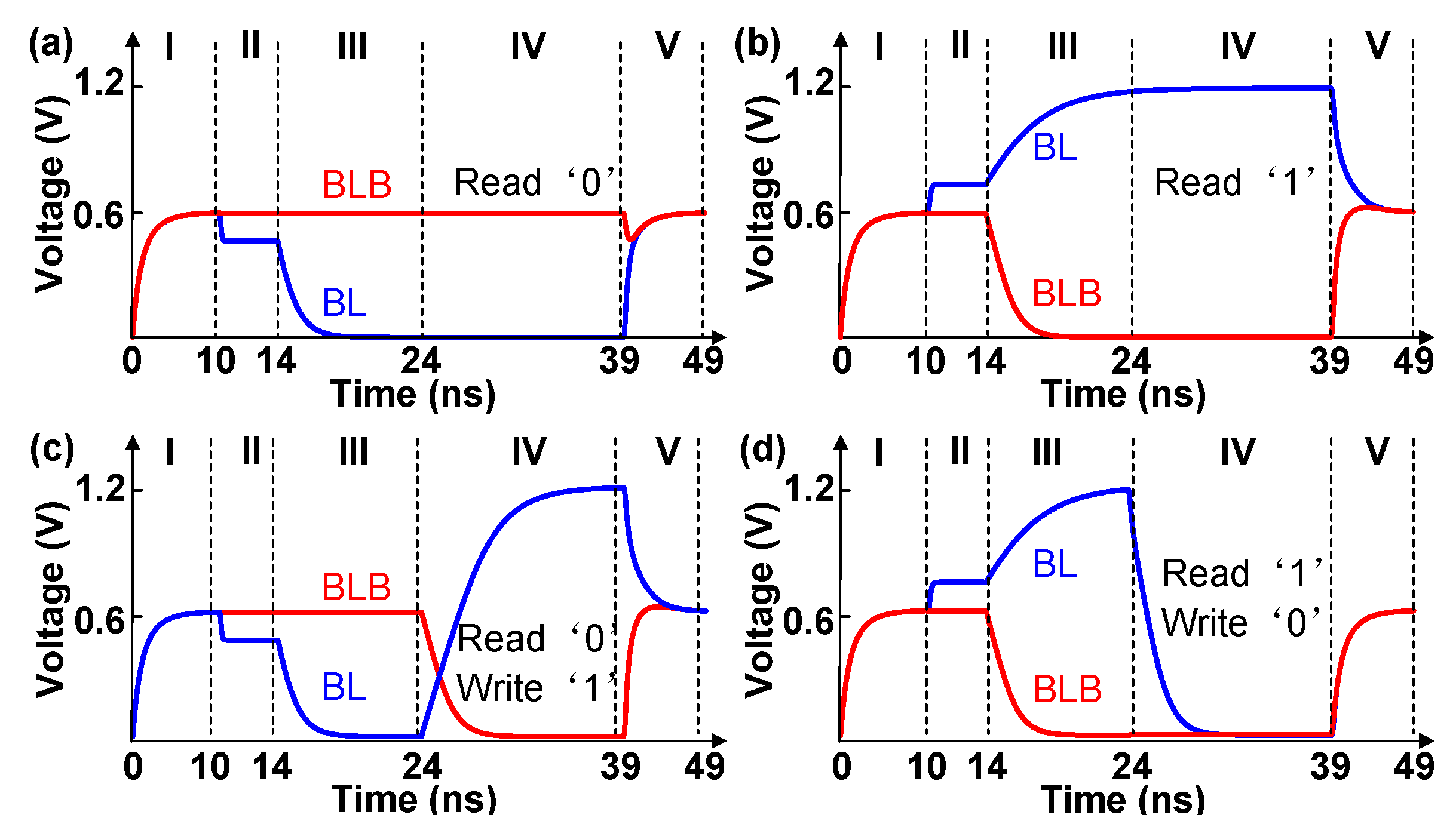

2.4. Bit Aware Sense Amplifier

Bit-Aware and Write-Back Logic

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kim, Y.; Yoo, C. Crosstalk Cancelling Voltage-Mode Driver for Multi-Gbps Parallel DRAM Interface. Int. J. Circuit Theory Appl. 2015, 43, 1175–1182. [Google Scholar] [CrossRef]

- Ravichandiran, P.P.; Franzon, P.D. A Review of 3D-Dynamic Random-Access Memory based Near-Memory Computation. In Proceedings of the IEEE International 3D Systems Integration Conference(3DIC), Raleigh, NC, USA, 26–29 October 2021; pp. 1–6. [Google Scholar]

- Hasan, S.S.; Imam, N.; Kannan, R.; Yoginath, S.; Kurte, K. Design Space Exploration of Emerging Memory Technologies for Machine Learning Applications. In Proceedings of the IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), Portland, OR, USA, 17–21 June 2021; pp. 439–448. [Google Scholar]

- Kim, Y.J.; Kwon, H.J.; Doo, S.Y.; Ahn, M.; Kim, Y.H.; Lee, Y.J.; Kang, D.S.; Do, S.G.; Lee, C.Y.; Cho, G.H.; et al. A 16-Gb, 18-Gb/s/pin GDDR6 DRAM with Per-Bit Trainable Single-Ended DFE and PLL-Less Clocking. IEEE J. Solid-State Circuits 2019, 54, 197–209. [Google Scholar] [CrossRef]

- Bhoj, A.N.; Jha, N.K. Gated-Diode FinFET DRAMs: Device and Circuit Design-Considerations. ACM J. Emerg. Technol. Comput. Syst. 2010, 6, 1–32. [Google Scholar] [CrossRef]

- Lin, C.H.; Greene, B.; Narasimha, S.; Cai, J.; Bryant, A.; Radens, C.; Narayanan, V.; Linder, B.; Ho, H.; Aiyar, A.; et al. High performance 14 nm SOI FinFET CMOS technology with 0.0174 µm2 Embedded DRAM and 15 levels of Cu metallization. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 3.8.1–3.8.3. [Google Scholar]

- Amat, E.; Calomarde, A.; Moll, F.; Canal, R.; Rubio, A. Feasibility of Embedded DRAM Cells on FinFET Technology. IEEE Trans. Comput. 2016, 65, 1068–1074. [Google Scholar] [CrossRef]

- Lim, D.Y.; Jung, I.J.; Kim, D.H.; Jung, S.O. Computing-in-Memory Using 1T1C Embedded DRAM Cell with Micro Sense Amplifier for Enhancing Throughput. In Proceedings of the IEEE International Conference on Consumer Electronics-Asia, Yeosu, Republic of Korea, 26–28 October 2022; pp. 1–4. [Google Scholar]

- Hamzaoglu, F.; Arslan, U.; Bisnik, N.; Ghosh, S.; Lal, M.B.; Lindert, N.; Meterelliyoz, M.; Osborne, R.B.; Park, J.; Tomishima, S.; et al. A 1 Gb 2 GHz Embedded DRAM in 22 nm Tri-gate CMOS Technology. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 230–231. [Google Scholar]

- Prasad, G.; Sahu, D.; Chandra Mandi, B.; Ali, M. Novel Low-Power and Stable Memory Cell Design using Hybrid CMOS and MTJ. Int. J. Circuit Theory Appl. 2022, 50, 465–477. [Google Scholar] [CrossRef]

- Kim, S.M.; Song, B.; Jung, S.O. Sensing Margin Enhancement Technique Utilizing Boosted Reference Voltage for Low-Voltage and High-Density DRAM. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 2413–2422. [Google Scholar] [CrossRef]

- Rana, M.; Canal, R.; Amat, E.; Rubio, A. Statistical Analysis and Comparison of 2T and 3T1D e-DRAM Minimum Energy Operation. IEEE Trans. Device Mater. Reliab. 2017, 17, 42–51. [Google Scholar] [CrossRef]

- Choi, H.; Hong, D.; Lee, J.; Yoo, S. Reducing DRAM Refresh Power Consumption by Runtime Profiling of Retention Time and Dual-Row Activation. Microprocess. Microsyst. 2020, 72, 102942. [Google Scholar] [CrossRef]

- Raghavendra, M.; Jha, S.; Pavan, R.; Hemanth, S. Comparative Analysis of MOSFET and FinFET DRAM N*N Array. In Proceedings of the International Conference for Emerging Technology (INCET), Belgaum, India, 27–29 May 2022; pp. 1–7. [Google Scholar]

- Sankpal, A.S.; Pethe, D.J. Study and Analysis of Retention Time and Refresh Frequency in 1T1C DRAM at Nanometer Regime. In Micro and Nanoelectronics Devices, Circuits and Systems: Select Proceedings of MNDCS; Springer: Singapore, 2022; pp. 449–458. [Google Scholar]

- Kumar, A.; Pandey, A.; Sahu, P.K. Design of DRAM Sense Amplifier using 45 nm technology. In Proceedings of the International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 29–31 March 2018; pp. 1–5. [Google Scholar]

- Saini, A.; Gupta, P.K.; Gupta, R. Analysis of Low Power SRAM Sense Amplifier. In Proceedings of the International Conference on Electrical, Electronics and Computer Engineering (UPCON), Aligarh, India, 8–10 November 2019; pp. 1–6. [Google Scholar]

- Kim, D.H.; Song, B.; Ahn, H.A.; Ko, W.; Do, S.; Cho, S.; Kim, K.; Oh, S.H.; Joo, H.Y.; Park, G.; et al. A 16 Gb 9.5 Gb/S/pin LPDDR5X SDRAM with Low-Power Schemes Exploiting Dynamic Voltage-Frequency Scaling and Offset-Calibrated Readout Sense Amplifiers in a Fourth Generation 10 nm DRAM Process. IEEE Int. Solid-State Circuits Conf. (ISSCC) 2022, 26, 448–450. [Google Scholar]

- Huang, P.; Chang, K.C.; Ge, J.; Peng, C.; Wu, X.; Chen, J.; Lin, Z. Offset-Compensation High-Performance Sense Amplifier for Low-Voltage DRAM Based on Current Mirror and Switching Point. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 2011–2015. [Google Scholar] [CrossRef]

- Kim, S.M.; Song, B.; Jung, S.O. Imbalance-Tolerant Bit-Line Sense Amplifier for Dummy-Less Open Bit-Line Scheme in DRAM. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2546–2554. [Google Scholar] [CrossRef]

- Rohbani, N.; Darabi, S.; Sarbazi-Azad, H. PF-DRAM: A Precharge-Free DRAM Structure. In Proceedings of the IEEE 48th Annual International Symposium on Computer Architecture (ISCA), Valencia, Spain, 14–18 June 2021; pp. 126–138. [Google Scholar]

- Kook, J.; Yoo, H.J. A Low Power Reconfigurable I/O DRAM Macro with Single Bit Line Writing Scheme. In Proceedings of the 26th European Solid-State Circuits Conference, Stockholm, Sweden, 19–21 September 2000; pp. 192–195. [Google Scholar]

- Na, T.; Song, B.; Choi, S.; Kim, J.P.; Kang, S.H.; Jung, S.O. Offset-Canceling Single-Ended Sensing Scheme with One-Bit-Line Precharge Architecture for Resistive Nonvolatile Memory in 65-nm CMOS. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 2548–2555. [Google Scholar] [CrossRef]

- Subramanian, L.; Vaidyanathan, K.; Nori, A.; Subramoney, S.; Karnik, T.; Wang, H. Closed yet Open DRAM: Achieving Low Latency and High Performance in DRAM Memory Systems. In Proceedings of the ACM/ESDA/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 24–29 June 2018; pp. 1–6. [Google Scholar]

- Olgun, A.; Patel, M.; Yağlıkçı, A.G.; Luo, H.; Kim, J.S.; Bostancı, F.N.; Vijaykumar, N.; Ergin, O.; Mutlu, O. QUAC-TRNG: High-Throughput True Random Number Generation Using Quadruple Row Activation in Commodity DRAM Chips. In Proceedings of the IEEE 48th Annual International Symposium on Computer Architecture (ISCA), Valencia, Spain, 14–18 June 2021; pp. 944–957. [Google Scholar]

- Li, Y. Robust Design of DRAM Core Circuits: Yield Estimation and Analysis by a Statistical Design Approach, München. Ph.D. Thesis, Technische Universität, Munich, Germany, 2011. [Google Scholar]

- Hwang, C.L.; Kirihata, T.; Wordernan, M.; Fifield, J.; Storaska, D.; Pontius, D.; Fredernan, G.; Ji, B.; Tomashot, S.; Dhong, S. A 2.9 ns Random Access Cycle Embedded DRAM with a Destructive-Read. In Proceedings of the Symposium on VLSI Circuits, Honolulu, HI, USA, 13–15 June 2002; pp. 174–175. [Google Scholar]

- Jang, J.; Shin, W.; Choi, J.; Suh, J.; Kwon, Y.; Kim, Y.; Kim, L.S. Refresh-Aware Write Recovery Memory Controller. IEEE Trans. Comput. 2017, 66, 688–701. [Google Scholar] [CrossRef]

- Park, Y.H.; Choi, S.; Yoo, H.J. Bit-Wise Read-Compare-Write Scheme for Low Power Read-Modify-Write DRAM Operation. Electron. Lett. 2002, 38, 62–63. [Google Scholar] [CrossRef]

- Kim, T.B.; Kwon, K.W. Quick and Efficient Offset Compensation by Noise-Aware Operation of DRAM Bit Line Sense Amplifier, International Technical Conference on Circuits/Systems. In Proceedings of the Computers and Communications (ITC-CSCC), Phuket, Thailand, 5–8 July 2022; pp. 497–500. [Google Scholar]

| Energy Consumption (fJ) | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Operation | Read ‘0’ | Read ‘1’ | Read ‘0’-Write ‘1’ | Read ‘1’-Write ‘0’ | ||||||||

| Process corner/ Temperature (°C) | FF/ −40 | TT/ 25 | SS/ 125 | FF/ −40 | TT/ 25 | SS/ 125 | FF/ −40 | TT/ 25 | SS/ 125 | FF/ −40 | TT/ 25 | SS/ 125 |

| Conventional | 113.8 | 116.4 | 121.5 | 113.8 | 116.4 | 121.2 | 365.7 | 366.4 | 371.1 | 333.0 | 334.3 | 339.1 |

| SBW | 67.5 | 68.7 | 71.1 | 146.5 | 146.3 | 146.9 | 278.0 | 276.0 | 271.8 | 160.4 | 163.5 | 161.6 |

| RVD-SBLSA (this work) | 69.1 | 70.4 | 73.0 | 109.2 | 99.6 | 91.7 | 231.2 | 215.3 | 208.5 | 159.0 | 160.0 | 155.8 |

| BA-SBLSA (this work) | 70.1 | 70.8 | 73.1 | 109.1 | 113.8 | 120.0 | 242.2 | 242.1 | 245.7 | 217.6 | 219.4 | 222.5 |

| BRV-SA [10] a | CSC-SA [19] a | *P1 [30] | Conventional SA b | SBW [14] b | RVD-SBLSA (This Work) | BA-SBLSA (This Work) | |

|---|---|---|---|---|---|---|---|

| Process (nm) | 65 | 28 | 180 | 65 | 65 | 65 | 65 |

| VDD (V) | 1.0 | 0.9 | 0.8 | 1.2 | 1.2 | 1.2 | 1.2 |

| Power consumption (μW) | 6.44 | 10.73 | 108.81 | 3.09 | 2.92 | 2.31 | 2.50 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dai, C.; Lu, Y.; Lu, W.; Lin, Z.; Wu, X.; Peng, C. Low-Power Single Bitline Load Sense Amplifier for DRAM. Electronics 2023, 12, 4024. https://doi.org/10.3390/electronics12194024

Dai C, Lu Y, Lu W, Lin Z, Wu X, Peng C. Low-Power Single Bitline Load Sense Amplifier for DRAM. Electronics. 2023; 12(19):4024. https://doi.org/10.3390/electronics12194024

Chicago/Turabian StyleDai, Chenghu, Yixiao Lu, Wenjuan Lu, Zhiting Lin, Xiulong Wu, and Chunyu Peng. 2023. "Low-Power Single Bitline Load Sense Amplifier for DRAM" Electronics 12, no. 19: 4024. https://doi.org/10.3390/electronics12194024

APA StyleDai, C., Lu, Y., Lu, W., Lin, Z., Wu, X., & Peng, C. (2023). Low-Power Single Bitline Load Sense Amplifier for DRAM. Electronics, 12(19), 4024. https://doi.org/10.3390/electronics12194024