1. Introduction

Data security and the latest advances in the video streaming field have gained importance. Secure and real-time image transfer is the focus of much multimedia research. Since digital images have low entropy, high redundancy, and strong pixel correlation, encrypting image data using traditional methods is not efficient. Thus, designing new cryptographic algorithms using chaotic systems has become an emerging field of research.

A cryptographic system uses keys to encrypt and decrypt data. There are two different cryptographic algorithm categories. These are symmetric encryption and asymmetric encryption [

1]. In symmetric encryption methods, both the sender and receiver must have the same key pair. Although these types of encryption methods have some advantages over asymmetric encryption methods, such as simplicity and the requirement of fewer resources, the key exchange process is a major problem [

2]. In asymmetric encryption methods, a public and private key pair are used. Everyone can know the public key, but the private key should be kept a secret. The private key cannot be derived from the public key.

Traditional asymmetric algorithms such as elliptic curve cryptography (ECC) [

3] or Rivest–Shamir–Adleman (RSA) [

4] and even symmetric algorithms such as Advanced Encryption Standard (AES) [

5] are very resource- and energy-consuming methods of image data encryption, which affects the performance of real-time streaming applications. This situation limits the use of those cryptographic algorithms in constrained environments. The problem typically applies to the Internet of Things (IoT) and urges the introduction of new lightweight cryptographic applications.

Chaotic maps are used to create chaotic sequences. It is not possible to predict or analyze chaotic sequences [

6,

7]. The complexity of the structure of a chaotic sequence is very high. Due to these advantages, chaotic systems have the potential to be actively used in encryption systems to increase overall system security. Two steps are generally followed to create a chaotic encryption method. These are scheme scrambling and diffusion.

The implementation of cryptographic algorithms on Field Programmable Gate Arrays (FPGAs) has become an important field of research due to their highly parallelized high-speed computing capabilities [

8]. Due to their reprogramming capability, it is possible to use them to rapidly develop and create Application-Specific Integrated Circuit (ASIC) prototypes. This method is applied to the FPGA since it is possible to reach higher encryption speeds due to its highly parallelized architecture.

Today, video streaming systems can stream videos at over 120 frames per second. Along with these high speeds, some industries, such as the defense industry and video streaming platforms, also need a secure end-to-end encryption methodology. However, when the performance levels of today’s chaotic encryption systems are considered, reaching those frame rates without high latency is impossible. Thus, a high-speed encryption methodology is required in this field to achieve up-to-date streaming technology.

One of the main problems in the image encryption field is that building a real-time solution with high security is difficult. It is possible to reach a high level of security with chaotic systems, but they still require significant time to encrypt images. The main motivation of this paper is to solve this issue. With the proposed approach, creating real-time encryption solutions with higher security is now possible. The proposed approach uses systolic arrays to ensure that a continuous image encryption pipeline is established to reach a high level of security when streaming images.

In this work, a new architecture that brings together the convolution operation with systolic arrays and chaotic oscillators is presented. It is shown that the proposed architecture can successfully encrypt images at higher speeds. Thus, implementing the proposed architecture makes it possible to create safe and low-latency video streaming pipelines. Along with this, a new architecture for further developments in the chaotic encryption field is proposed.

This paper proposes a novel FPGA-based chaotic encryption model using the convolution operation with systolic arrays over the Lü–Chen chaotic oscillator proposed by [

9].

The rest of this paper is organized as follows:

Section 2 reviews related work.

Section 3 introduces the proposed method.

Section 4 describes the experiments and the evaluation of the results. The discussion is presented in

Section 5. The conclusion is given in

Section 6.

2. Related Works

The fundamentals of chaos theory were proposed by Henri Poincaré [

10]. Lorenz then researched the application of chaos theory to weather systems [

11]. In his research, he tried to reuse outputs gathered from a mathematical model by rounding them. By applying this technique, he aimed to achieve results faster, but in the end, he observed unpredictable results. Li et al. used the term chaos to explain results such as those obtained by Lorenz [

12]. Leon O. Chua built an analog circuit and applied a chaotic system [

13,

14]. The continuous autonomous Chua circuit set an important example for later research conducted in this field [

15,

16].

In 2007, Zhang et al. proposed a chaos-based image encryption algorithm [

17]. To improve the security and speed of this method, standard maps, cat maps, and Baker maps were used [

18,

19]. E. Yavuz et al. have also proposed an image encryption algorithm using chaos [

20]. They proposed applying confusion and diffusion principles to an image using two independent chaotic functions. This method is preferred over advanced scrambling and diffusion methods in some studies. M. François et al. proposed a new approach by using symmetric chaotic encryption [

21]. The method depends on the bitmap permutation process, resulting in higher computational complexity. K.-W. Wong et al. proposed using a look-up table and a combination of swapping methods instead of a 1D chaotic map in the diffusion process [

22]. X. Zhang and Z. Zhao proposed a two-way diffusion method. In this method, they used pixel values from top to bottom and right to left in addition to the standard diffusion process [

23]. This helped to reduce time complexity by reducing the number of required rounds. J.-X. Chen et al. proposed a continuous diffusion method. They applied complementary diffusion in addition to the standard diffusion process [

24]. This method reduced the time complexity by increasing security in fewer rounds. X. Wang et al. proposed a chaotic block image encryption method. This method was based on the dynamic random growth technique [

25]. In this method, they applied an intermediate parameter as the initial conditions of a chaotic map and generated random data pruned against plaintext attacks.

Studies on FPGA-based high-speed methods have gained importance, along with the recent advancements in real-time streaming applications and increasing demand for encrypted video streams. Koyuncu et al. proposed a new design using a Burke–Shaw Chaotic system with an RK5-Butcher algorithm on Virtex-6 FPGA [

26]. Alcin et al. used the Pehlivan–Uyaroglu chaotic system along with the Artificial Neural Network approach on a Virtex-6 FPGA [

27]. Koyuncu et al. proposed a Pehlivan–Wei chaotic system design. In this design, they used Euler, RK4, and Heun algorithms instead of the Virtex-6 FPGA [

28]. Tuna et al. proposed using a chaotic system design that uses the Heun algorithm on a FPGA [

29]. Akgul et al. proposed a 3D chaotic system design using the RK4 algorithm [

30]. Two fractional-order 4D chaotic system designs on the Kintex 7 FPGA have been proposed by Rajagopal et al. [

31]. A multi-butterfly chaotic system design has been proposed by Lai et al. [

32]. Tlelo–Cuautle et al. have proposed a multi-scroll chaotic oscillator design on the Cyclone IV FPGA [

33]. A chaotic chameleon system with an RK5B algorithm on a Virtex-6 FPGA has been proposed by Rajagopal et al. [

34]. Aceng S. et al. have proposed a novel 3D chaotic system with line equilibrium to encrypt images [

35].

3. Materials and Methods

The system proposed in this study is an end-to-end parallel pipeline. Thus, it is possible to extend the pipeline for increased security. Confusion and a diffusion process are applied at each step of this pipeline. The standard methodology for applying the diffusion process to a FPGA is very costly. Thus, a new method to combine confusion and diffusion processes by using the systolic arrays is proposed in this work.

At the beginning of the process, a diffusion process is applied to the input array of pixels. The dimensionality of each array is 3 × 3. Then, the convolution process is applied to the array.

This work uses a Lü–Chen chaotic system as a chaotic oscillator to generate a randomized sequence of numbers. These numbers then feed forward to a systolic array to apply a convolutional filter for confusion. Due to the nature of the convolution operation, it is possible to create a sequential pipeline for further encryption. At the end of the process, a confused image is generated.

A standard deconvolution process is applied along with the inverse of the diffusion process to decrypt the resulting encrypted image. The number of layers used to encrypt the image directly must affect the time complexity of the decryption phase. Since the encrypted image is a confused and diffused version of the real image, using the wrong number of layers in the decryption phase will result in a meaningless image.

3.1. Lü–Chen Chaotic System

In 1999, Chen proposed a chaotic attractor that is topologically not equal to Lorenz’s attractor. Lorenz’s attractor is generalized by the a

12a

21 > 0 condition with its linear part [

36] A = [a

ij]. However, Chen’s system satisfies condition a

12a

21 < 0 and belongs to another canonical family of chaotic systems. Jinhu Lu and Guarong Chen later proposed a nonlinear differential equation called the Lü–Chen 2002 chaotic system, which satisfies the a

12a

21 = 0 condition [

37]. This system is shown in Equation (1).

where a, b, and c are ∈ R. The parameters a and b are fixed and set to a = 36 and b = 3. Parameter c is a variable that influences the system’s behavior by generating different types of attractors. Specifically, when c is set within the range of 12.7 to 17.0, the system produces an attractor resembling the Lorenz attractor. The system exhibits a transitory shape in the range of 18.0 to 22.0. Finally, for values of c between 23.0 and 28.5, the system generates an attractor similar to Chen’s attractor.

In part a of

Figure 1, c is set to 27, so a Lü–Chen attractor is produced. In part b, c is set to 29; in part c, it is set to 20; and in part d, it is set to 15. The solution of the Lü–Chen chaotic system creates an inner loop to generate an organization inside which it is impossible to predict the amplitude and frequency. In this work, the initial parameters are set as follows: parameter a is set to 36, b is set to 3, and c is set to 20. All figures are obtained by using the matplotlib library in Python.

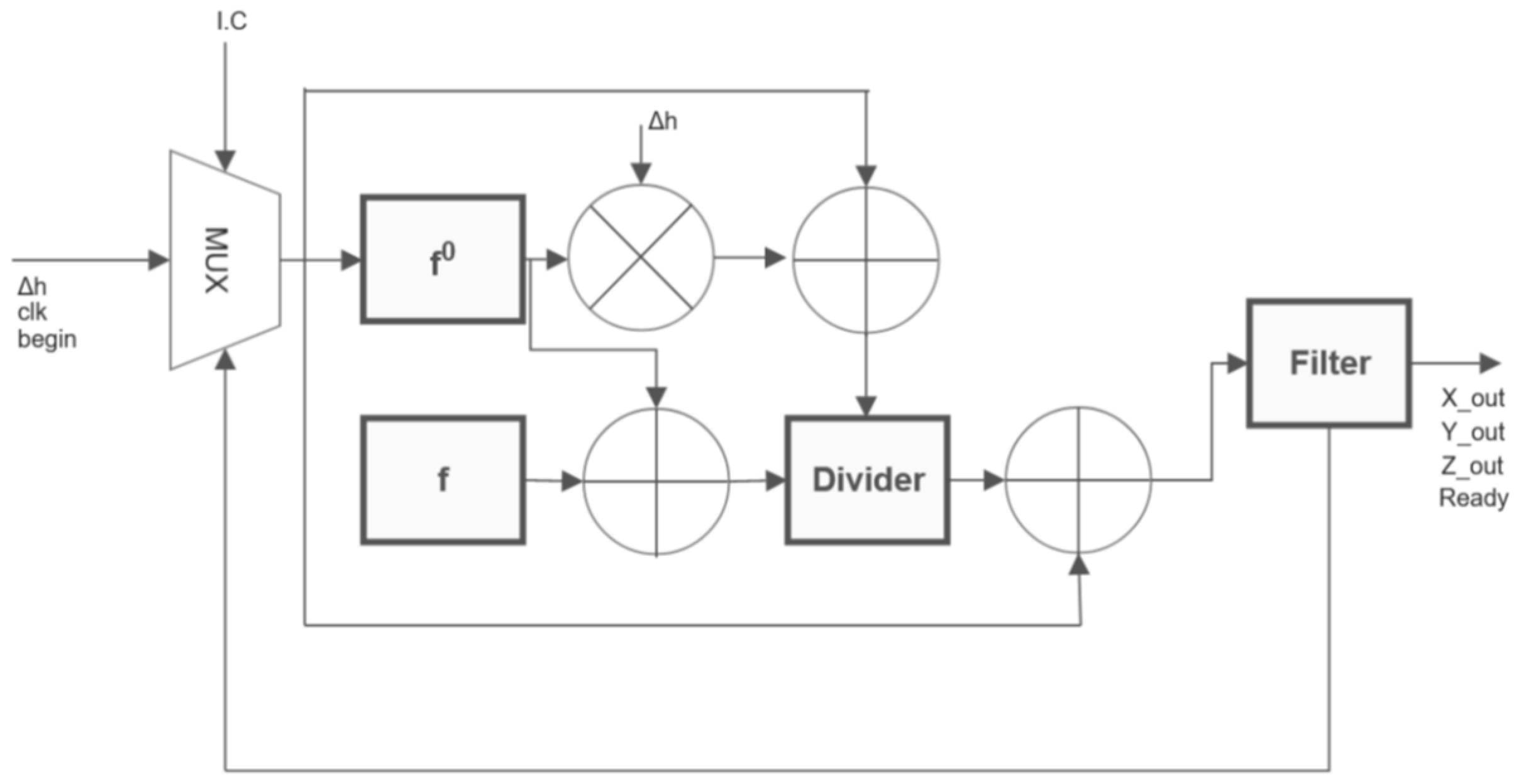

In 2019, M. Tuna et al. proposed a method to model a Lü–Chen chaotic oscillator on a FPGA using the Heun algorithm [

9]. We followed the same methodology using Verilog HDL. The equation for the Heun algorithm is given in Equation (2).

In this equation, the intermediate values

x(

k0 + 1),

y(

k0 + 1), and

z(k0 + 1) are presented. The intermediate values are calculated first since they are required in the next step. Then, the values of

x(

k + 1),

y(

k + 1), and

z(

k + 1) are calculated. Δ

h is given as the step size and set to 0.01. The block diagram of the FPGA implementation is shown in

Figure 2.

A Modulo 255 operation is carried out on each system output value presented in

Figure 2 to successfully apply the convolutional filter.

3.2. Systolic Array

A systolic array is a hardware structure designed to increase the speed and efficiency of algorithms that perform the same operation on different data at each time step [

38]. It is possible to use systolic arrays to change the standard pipeline architecture. Because of its regularity and scalability, a systolic array is used in this work to apply convolution to the input array of pixels. One of the advantages of the systolic-array-based architecture is its ability to handle high-throughput capacity requirements. This makes them useful in real-time encrypted video streaming applications.

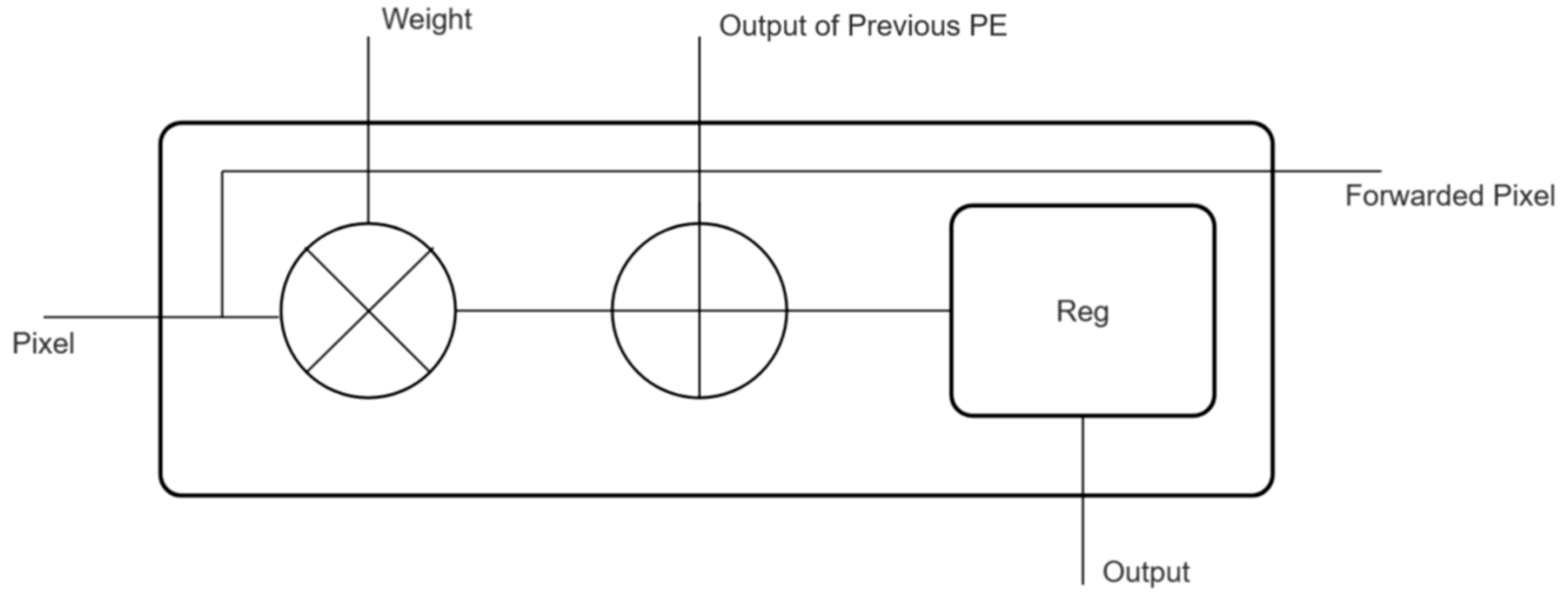

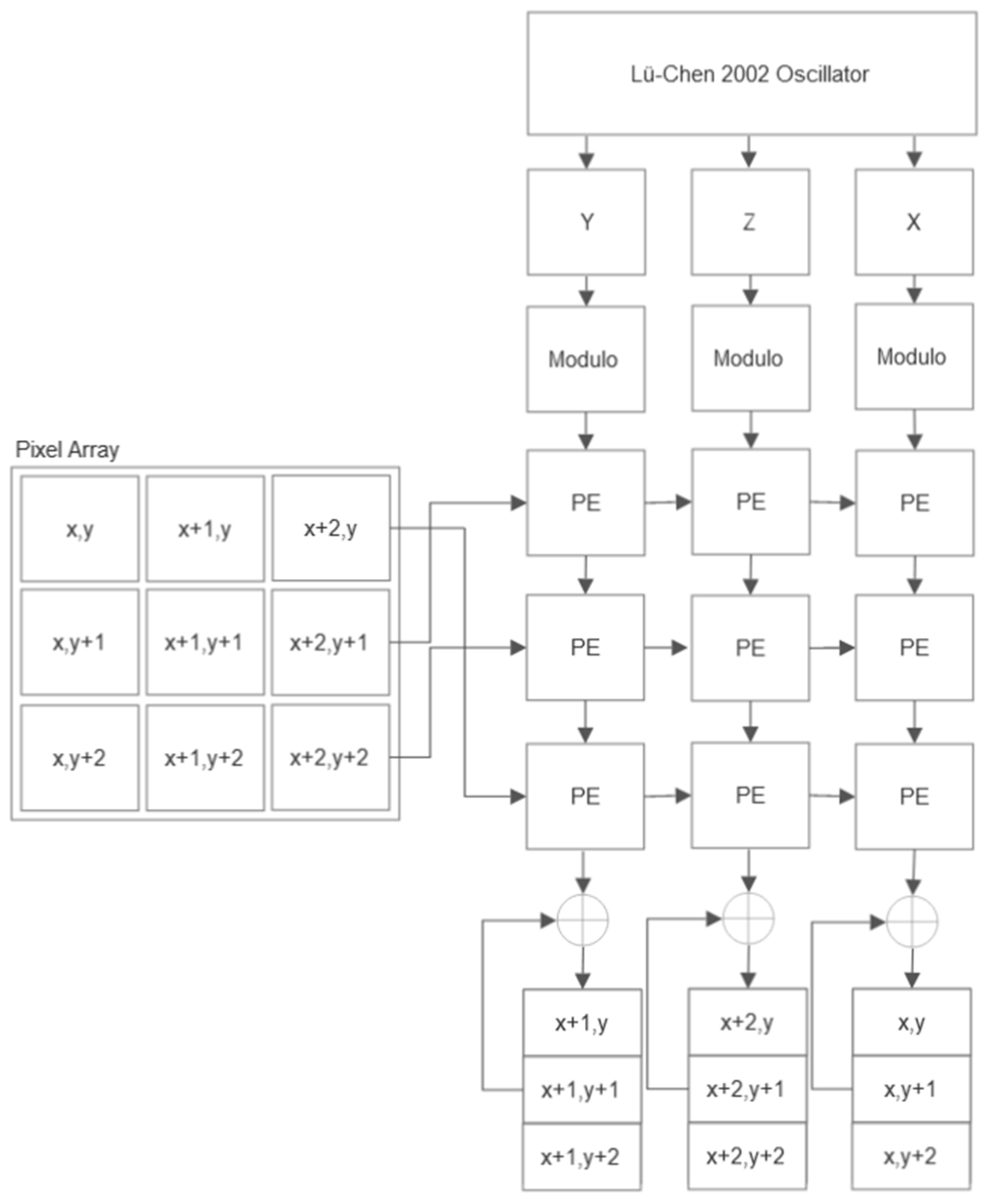

A standard systolic array architecture is shown in

Figure 3. For each 3 × 3 pixel array, weights repeat themselves to apply the same convolutional filter to an image. At each clock cycle, pixels are moved toward the systolic array units. Then, a pixel value is moved between systolic array units delayed by one clock cycle. Since the pixel array size is larger than the filter size, the result of each block is stored in the accumulators and added to the result of the next block.

The architecture of each Processing Element (PE) is shown in

Figure 4. It multiplies the inputting pixel value by the related weight and then applies the addition process to the output of the previous unit. It also passes the inputting value to the next unit and outputs a value to the unit under it.

With a standard pipeline architecture, the diffusion process on FPGA is very costly since saving a copy of the diffused version of an image on RAM and the amount of logic required to compute the location changes in parallel is necessary. Thus, a new methodology to combine confusion and diffusion processes is required to decrease the cost of implementation. This work proposes a systolic array-based solution to overcome the problem.

As shown in

Figure 5, it is possible to apply convolution-based confusion and diffusion processes using systolic arrays with an additional multiplexer implementation. In the first step of this architecture, pixels are vertically fed through PEs. Then, the outputs of the Lü–Chen 2002 oscillators are fed through the systolic arrays as weight values in the order of Y, Z, and X. Those values are stored in horizontally changed accumulators at the final step. Thus, pixels change places in 2 by 2, and the convolution process is applied to every pixel passed through.

3.3. Experimental Design

All experiments were conducted on a Xilinx VC707 FPGA card with a XC7VX485T-2FFG1761 FPGA chip. It has 485,760 logic cells, 8175 Kb distributed RAM, and 37,080 Kb Block RAM. The 32-bit IQ Math format was used to represent floating numbers. The number of resources used by the chaotic oscillator is given in

Table 1.

As shown in

Table 1, resource utilization of the oscillator is minimal (3% LUT utilization) compared to the available resources. The number of resources used by the 300 × 300 systolic array architecture is given in

Table 2.

Since Block RAMs are used instead of distributed RAM, Block RAM usage is given in

Table 2. Resources used by the complete system are given in

Table 3.

It takes 129,600 clock cycles to process a 300 × 300 image. It is possible to process 4421 images per second using a single block. This work used up to five sequential blocks since achieving higher-level security with less resource consumption in five layers is possible. The proposed architecture can process 276 images per second.

4. Results

To demonstrate the proposed method, it was used to encrypt three images, and the results were evaluated using the Correlation Coefficient Test (CCT)—to understand the degree of similarity of adjacent pixels—and the Entropy test.

4.1. Resulting Images

Three images were selected and encrypted to evaluate the proposed approach. Since it is possible to build sequential models, up to five blocks were used to encrypt the images, and the results of each step are shown in

Figure 6,

Figure 7 and

Figure 8.

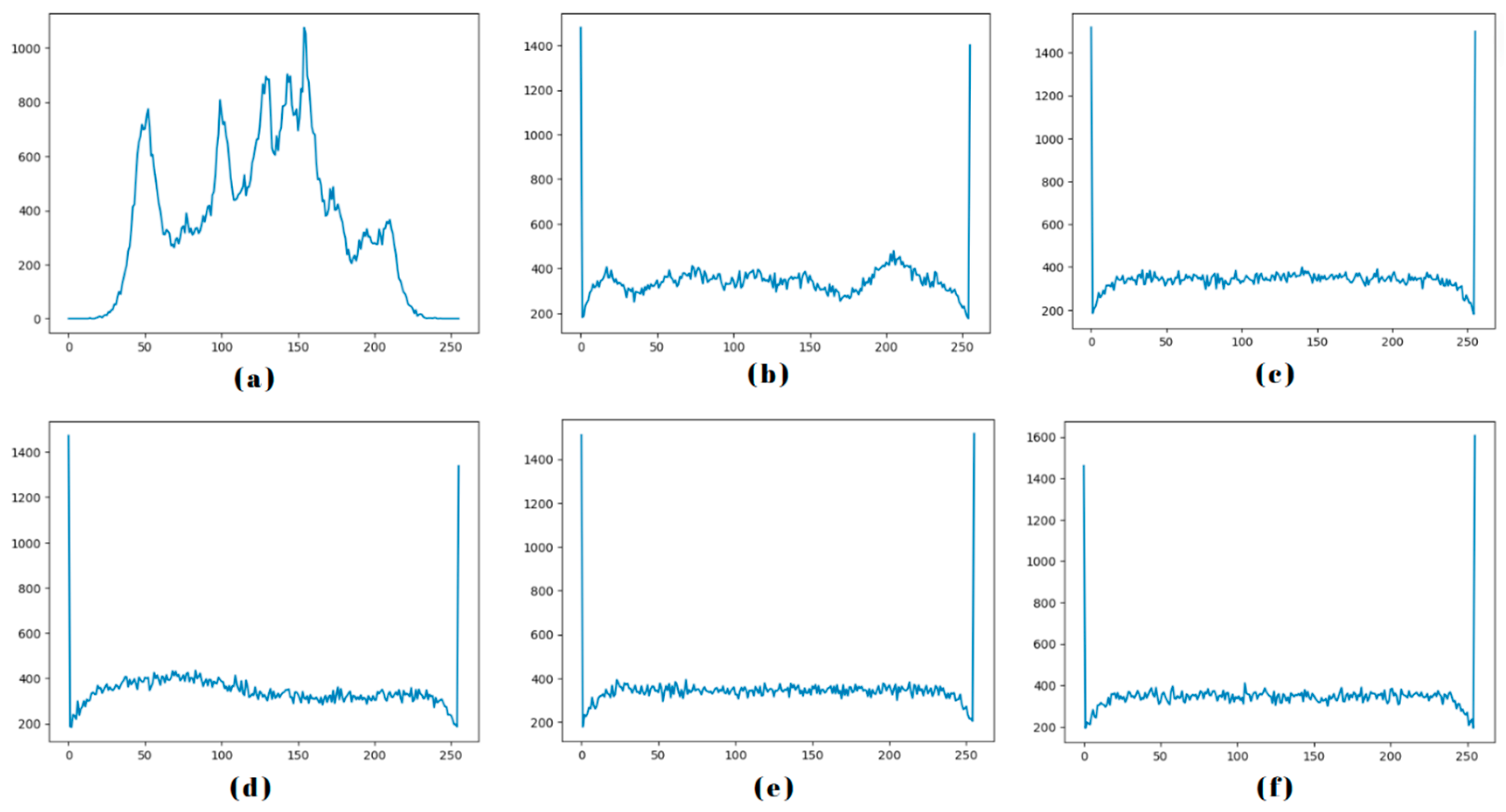

4.2. Histogram Analysis

It is possible to create an image’s histogram by using intensity values. In this study, 8-bit grayscale images are used so that there are 256 possible intensity values. If the distribution of values is fairly uniform in the encrypted image, it is possible to conclude that the proposed encryption method can successfully encrypt the image.

Histograms of non-encrypted and encrypted images of Lena are shared in

Figure 9.

Histograms of the non-encrypted and encrypted images of peppers are shared in

Figure 10.

Histograms of the non-encrypted and encrypted images of a raccoon are shared in

Figure 11.

As shown in

Figure 9,

Figure 10 and

Figure 11, the histograms of the encrypted images are uniformly distributed and different from the original image. It can also be seen that the histograms change after the addition of each new encryption layer. These almost-random histograms show that the proposed method can successfully encrypt grayscale images.

4.3. Correlation Coefficient Test

CCT is an important method of statistical analysis used to find the success rate of an image encryption method. It measures the degree of similarity between adjacent pixels; ideally, dependency should not exist between them, and the correlation coefficient should be near 0. CCT is calculated with Equation (3).

In this equation, the number of pixels is represented by N; xi and yi represent the x and y coordinates of a pixel, respectively; and and represent the coordinates of adjacent pixels.

The results of the CCT for the output of each sequential block when encrypting the pepper image are shown in

Table 4.

The results of the CCT for the output of each sequential block when encrypting Lena’s image are shown in

Table 5.

The results of the CCT for the output of each sequential block when encrypting the raccoon image are shown in

Table 6.

As shown in

Table 4,

Table 5 and

Table 6, the correlation between adjacent pixels in an encrypted image decreases. Thus, it is possible to state that the proposed approach can successfully break the correlation between adjacent pixels.

4.4. Image Entropy Analysis

It is possible to use image entropy analysis to measure the unpredictability of an image. Shannon introduced this concept in [

39]. It tests whether or not an image has a random distribution of pixel values. The mathematical expression of the method is given in Equation (4):

where

Ki represents the pixel values,

P(

Ki) represents the probability that a pixel value is found, and

r represents the number of symbols (set to 256 for grayscale images). If a grayscale image has pixel values with equal probabilities,

K = (

K0,

K1,

K2,

K3…

K255), its entropy value is set to 8. In an image that has not been encrypted yet, there is a correlation between pixel values; they are seldom random, and their entropy is generally smaller than 8. If the entropy reaches 8, it can be stated that it has reached the maximum ideal value, and all pixels are distributed randomly.

The results of entropy analysis for the output of each sequential block for the pepper image are shown in

Table 7.

The results of entropy analysis for the output of each sequential block for the image of Lena are shown in

Table 8.

The results of entropy analysis for the output of each sequential block for the raccoon image are shown in

Table 9.

As shown in

Table 7,

Table 8 and

Table 9, the entropy of the image approaches the ideal level when encrypted using the proposed method. Thus, it is possible to state that the proposed approach is successful.

4.5. Diffusion Analysis Test

We conducted Rate of Change of the Number of Pixels (NPCR) and Unified Mean Intensity of Change (UACI) tests to measure the resistance against differential attacks. Values between 33.3115 and 33.6156 are considered good for the UACI. Additionally, values between 99.3082 and 99.5906 are considered good for the NPCR, depending on the image size [

40]. The NPCR metric can be expressed as Equation (5), and the UACI metric can be expressed as Equation (6):

where

m and

n represent the number of rows and columns of the image, respectively, and are set to 256 in a grayscale image.

are the elements at positions

i and

j of the ciphers of images

I1 and

I2.

The results of the NPCR test for the output of each sequential block for the pepper image are shown in

Table 10.

The results of the UACI test for the output of each sequential block for the pepper image are shown in

Table 11.

The results of the NPCR test for the output of each sequential block for the image of Lena are shown in

Table 12.

The results of the UACI test for the output of each sequential block for the image of Lena are shown in

Table 13.

The results of the NPCR test for the output of each sequential block for the raccoon image are shown in

Table 14.

The results of the UACI test for the output of each sequential block for the raccoon image are shown in

Table 15.

The results of the NPCR and UACI tests prove that the proposed method can generate encrypted images prone to differential attacks.

5. Discussion

Based on the conducted experiments, the proposed approach can successfully encrypt images by highly increasing entropy and decreasing correlation. The NPCR and UACI results show that the proposed method is prone to diffusion attacks. The performance of the system increases with the number of sequential blocks used. It might be possible to increase the system’s overall performance in images with more than one dimension (such as RGB images) using a 3D diffusion approach.

The results of the proposed method are compared with other methodologies in

Table 16.

Table 16 shows that the proposed method gives results competitive with state-of-the-art work conducted in this field. The resulting UACI score is lower than the optimal level. Similar results have also been observed in [

48]. Both works share the same chaotic oscillator. Thus, it is possible to conclude that the Lü–Chen chaotic oscillator can result in lower UACI levels.

The primary objective of this paper was to decrease the time required to encrypt images for streaming applications by using the parallel processing capabilities of FPGAs and systolic array architectures. To provide a comprehensive analysis,

Table 17 compares the times needed to encrypt data when using different methodologies.

It is possible to continue the research by implementing new nonlinear chaotic map approaches, such as the one proposed in [

49], on the proposed architecture to improve the system’s security. Another avenue to explore is using fuzzy modeling to model chaotic behavior, as in [

50], to decrease the overall computational complexity of the system.

The proposed approach gives state-of-the-art encryption time results and better performance than all other proposed methods. The time required to decrypt the image has not been shared, as it is not realized on a FPGA. This research can be furthered by realizing the required deconvolution process to decrypt the image on a FPGA using a systolic array approach.

In this work, a 2 × 2 diffusion method was used. It is possible to change this to obtain different results in future research.

The current study used a 32-bit IQ Math approach to represent the oscillator’s output. It is possible to use a 64-bit floating point representation to improve security or a 16-bit float type to decrease resource consumption while measuring how the level of security is preserved.

6. Conclusions

This research proposes a FPGA-based chaotic image encryption method that uses systolic arrays. To achieve this, the Lü–Chen chaotic oscillator generates weights for the convolutional filter. Then, the image is fed to the systolic array architecture. The most resource-consuming part of the encryption process is the diffusion process. The confusion and diffusion processes are fused to decrease overall resource consumption and create a fully systolic array-based architecture.

We conducted experiments to show that the proposed method can produce promising results. It can perform very high-speed encryption processes and has a comparable level of security compared to other methods.

The proposed method can achieve higher encryption speeds compared to the other methodologies. Along with this improvement, it may become possible to use chaotic encryption methodologies in low-latency encrypted video streaming applications.

It is possible to increase the number of sequential encryption layers to add an extra layer of protection to the system. Still, the resources of the FPGA are limited, and the total time required for both encryption and decryption processes increases with each new encryption layer.

It is possible to further this research by changing the chaotic oscillator used to achieve higher levels of security. A systolic array-based decryption architecture can also be developed to decrease the total time needed to decrypt the system’s output.