Total Ionizing Dose Effects of 60Co γ-Ray Radiation on Split-Gate SiC MOSFETs

Abstract

:1. Introduction

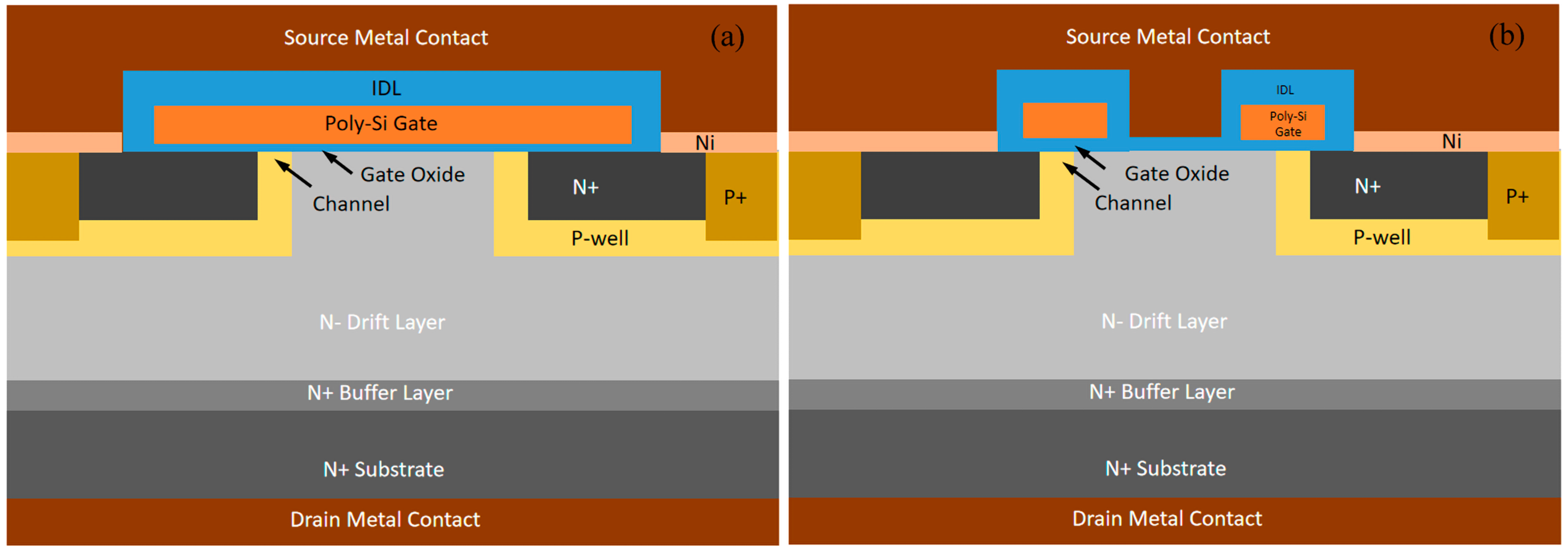

2. Samples and Experimental Setup

3. Results and Analyses

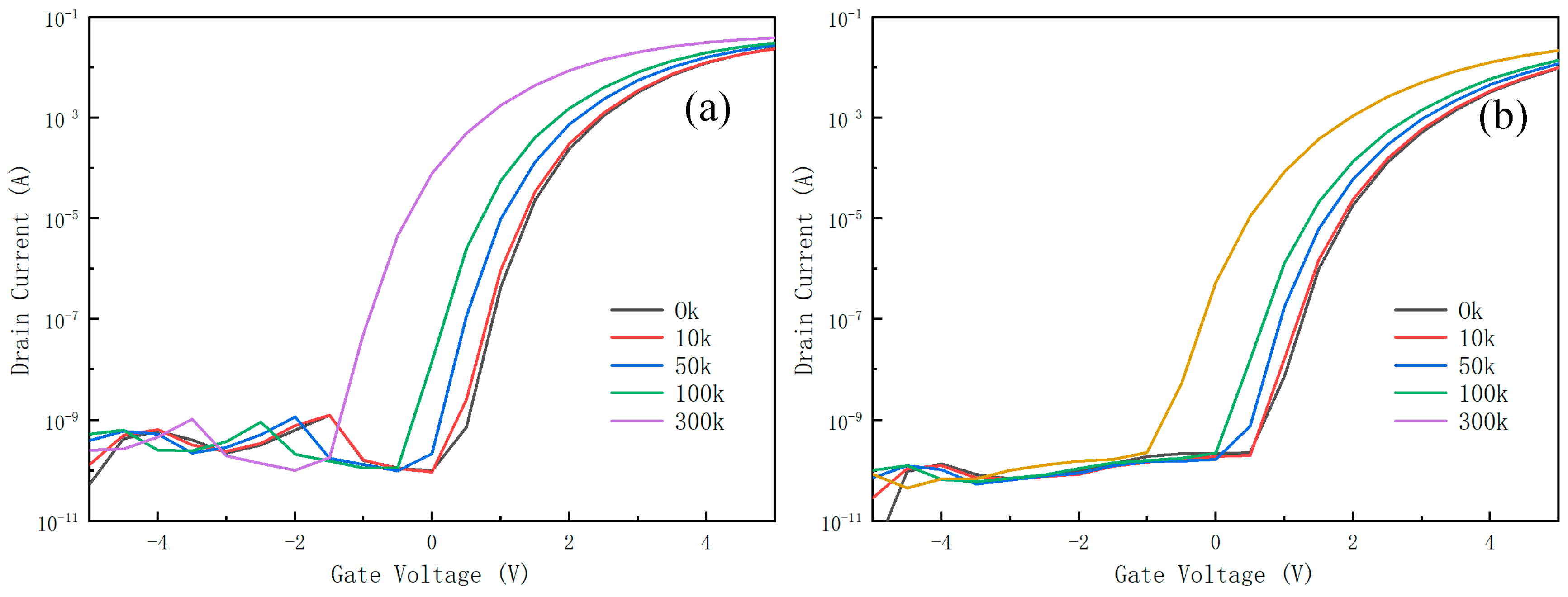

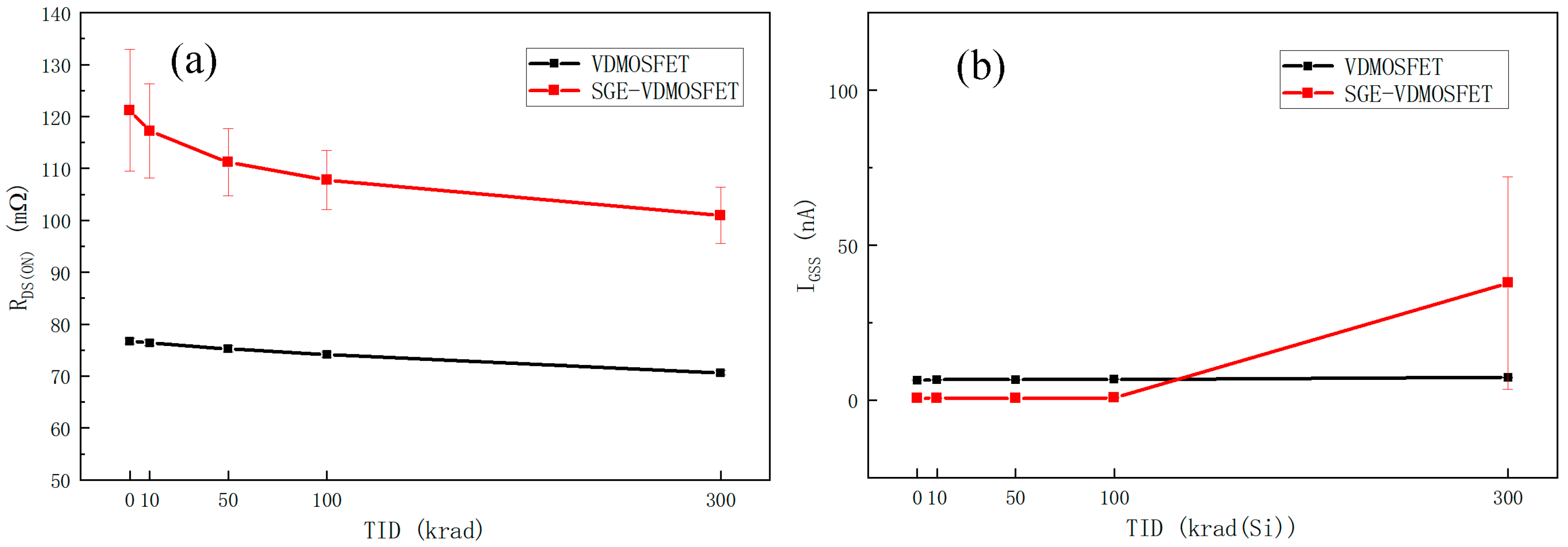

3.1. The Influence of TID Radiation on the Static Characteristics of SGE-VDMOSFET and PG-VDMOSFET

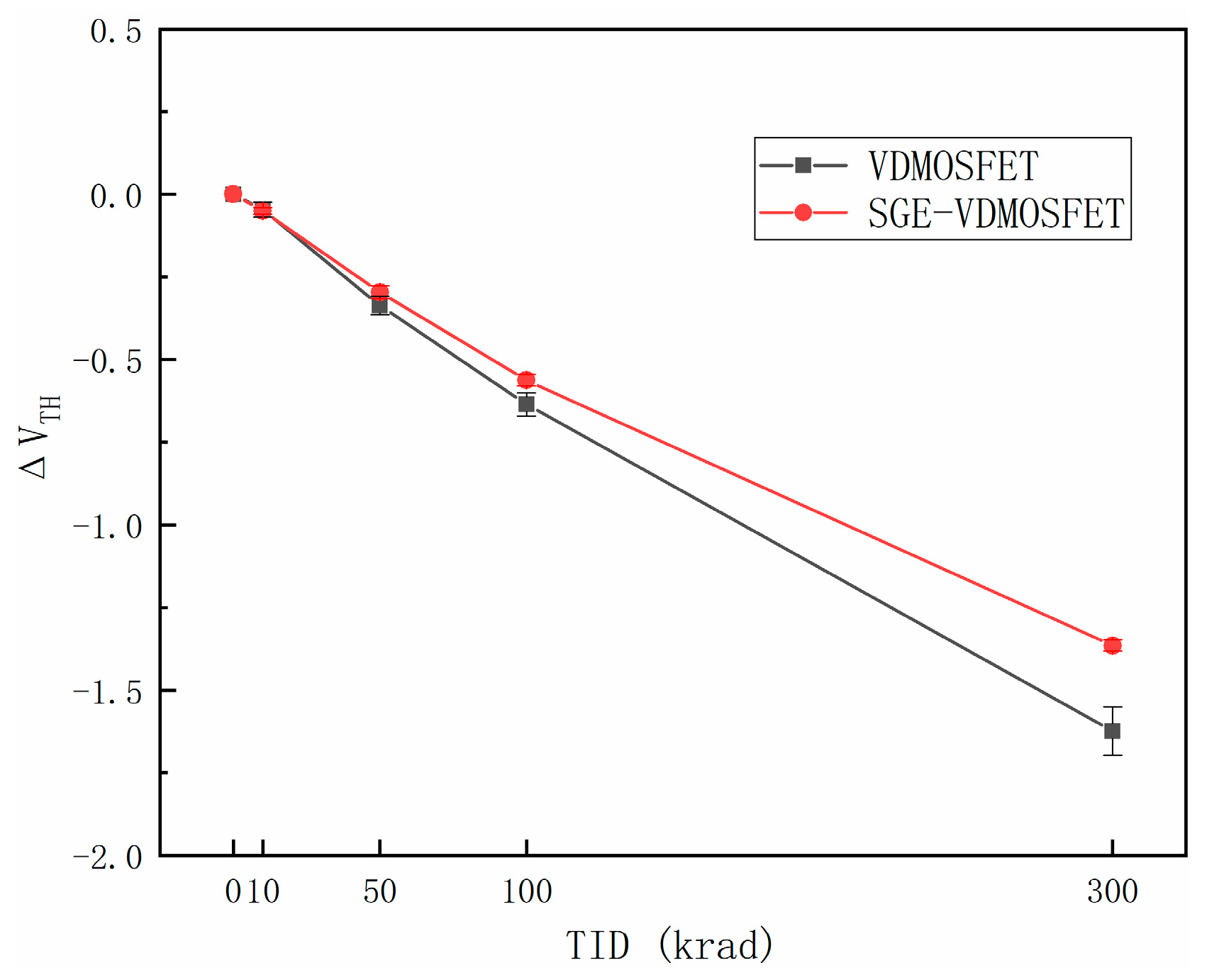

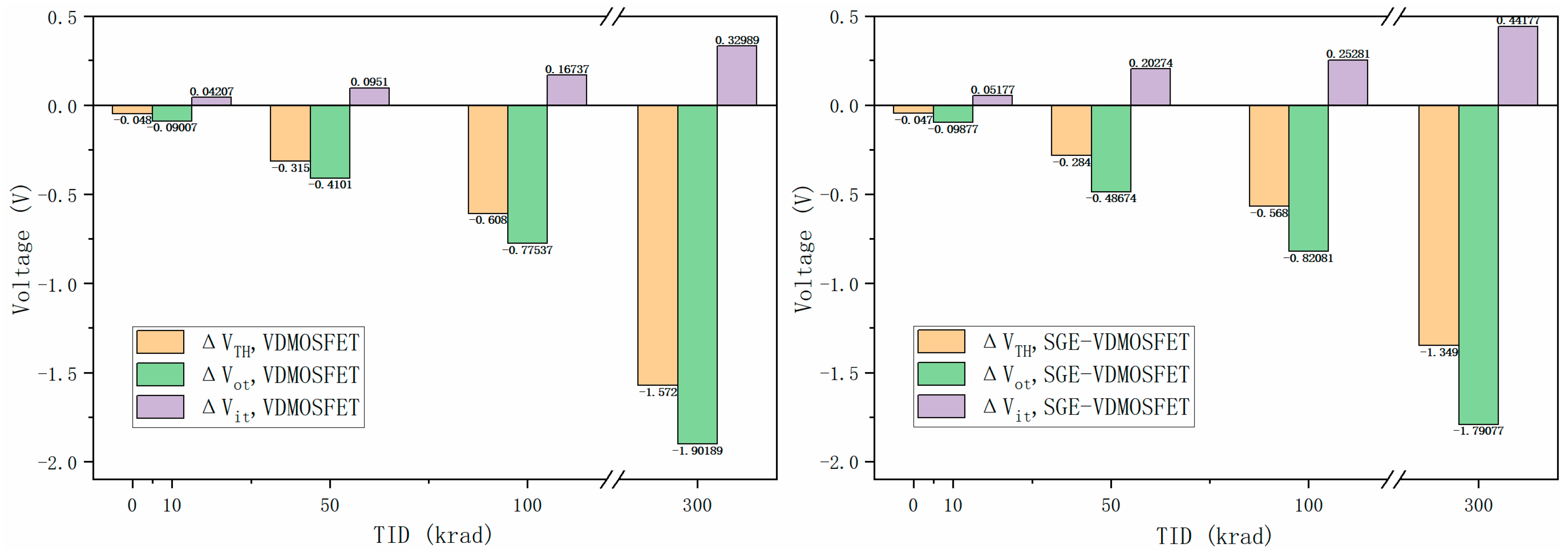

3.2. Differences in Threshold Voltage Degradation between SGE-VDMOSFET and PG-VDMOSFET

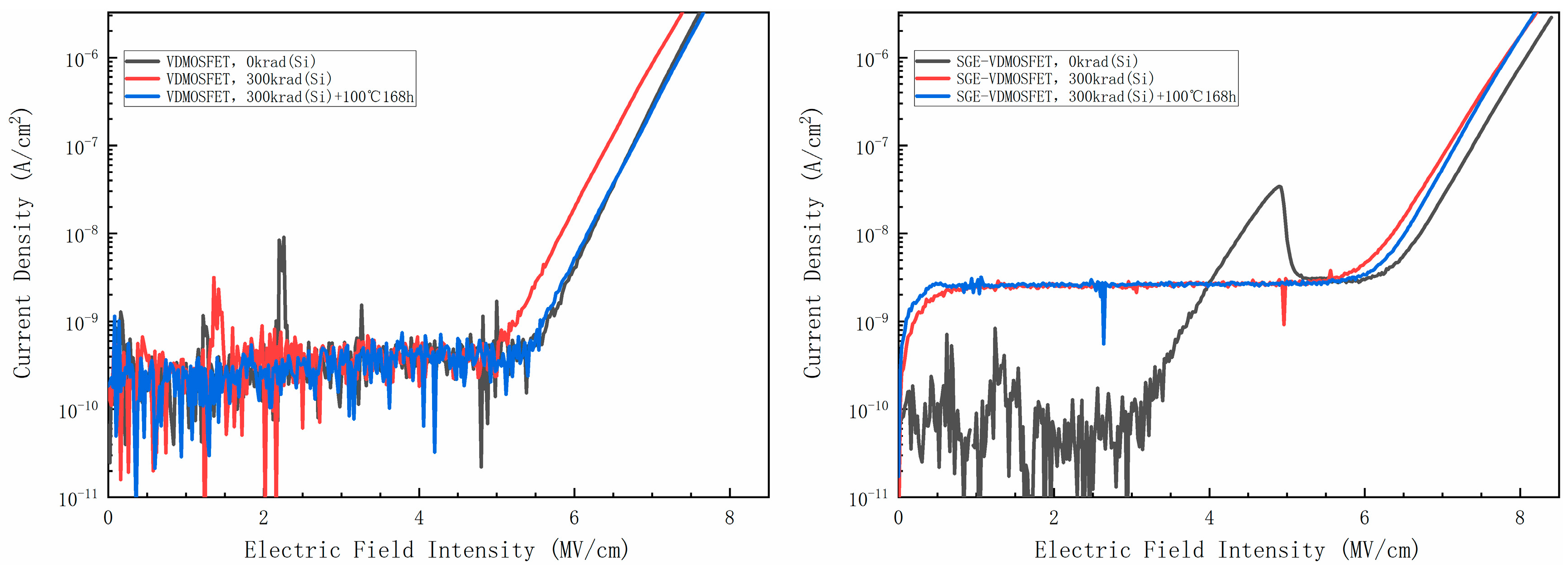

3.3. The Influence of TID Radiation on Electron Tunneling in Gate Oxide

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Fleetwood, D.M. Total-Ionizing-Dose Effects, Border Traps, and 1/f Noise in Emerging MOS Technologies. IEEE Trans. Nucl. Sci. 2020, 67, 1216–1240. [Google Scholar] [CrossRef]

- Adell, P.C.; Scheick, L.Z. Radiation Effects in Power Systems: A Review. IEEE Trans. Nucl. Sci. 2013, 60, 1929–1952. [Google Scholar] [CrossRef]

- Jie, X.; Qing, K.; Xuan, Z.; Feng, L. Application Prospect of SiC Power Semiconductor Devices in Spacecraft Power Systems. In Proceedings of the 2017 13th IEEE International Conference on Electronic Measurement & Instruments (ICEMI), Yangzhou, China, 20–22 October 2017; pp. 185–190. [Google Scholar]

- Roccaforte, F.; Fiorenza, P.; Greco, G.; Nigro, R.L.; Giannazzo, F.; Iucolano, F.; Saggio, M. Emerging trends in wide band gap semiconductors (SiC and GaN) technology for power devices. Microelectron. Eng. 2018, 187–188, 66–77. [Google Scholar] [CrossRef]

- Sun, Y.; Wan, X.; Liu, Z.; Jin, H.; Yan, J.; Li, X.; Shi, Y. Investigation of total ionizing dose effects in 4H–SiC power MOSFET under gamma ray radiation. Radiat. Phys. Chem. 2022, 197, 110219. [Google Scholar] [CrossRef]

- Murata, K.; Mitomo, S.; Matsuda, T.; Yokoseki, T.; Makino, T.; Onoda, S.; Takeyama, A.; Ohshima, T.; Okubo, S.; Tanaka, Y.; et al. Impacts of gate bias and its variation on gamma-ray irradiation resistance of SiC MOSFETs. Phys. Status Solidi (A) 2017, 214, 1600446. [Google Scholar] [CrossRef]

- Zhang, T.; Allard, B.; Bi, J. The synergetic effects of high temperature gate bias and total ionization dose on 1.2 kV SiC devices. Microelectron. Reliab. 2018, 88–90, 631–635. [Google Scholar] [CrossRef]

- Zhang, C.X.; Shen, X.; Zhang, E.X.; Fleetwood, D.M.; Schrimpf, R.D.; Francis, S.A.; Roy, T.; Dhar, S.; Ryu, S.-H.; Pantelides, S.T. Temperature Dependence and Postirradiation Annealing Response of the 1/f Noise of 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2013, 60, 2361–2367. [Google Scholar] [CrossRef]

- Akturk, A.; McGarrity, J.M.; Potbhare, S.; Goldsman, N. Radiation Effects in Commercial 1200 V 24 A Silicon Carbide Power MOSFETs. IEEE Trans. Nucl. Sci. 2012, 59, 3258–3264. [Google Scholar] [CrossRef]

- Alexandru, M.; Florentin, M.; Constant, A.; Schmidt, B.; Michel, P.; Godignon, P. 5 MeV proton and 15 MeV electron radiation effects study on 4H-SiC nMOSFET electrical parameters. IEEE Trans. Nucl. Sci. 2014, 61, 1732–1738. [Google Scholar] [CrossRef]

- Lebedev, A.A.; Kozlovski, V.V.; Levinshtein, M.E.; Ivanov, A.E.; Strel, A.M.; Zubov, A.V.; Fursin, L. Impact of 0.9 MeV electron irradiation on main properties of high voltage vertical power 4H-SiC MOSFETs. Radiat. Phys. Chem. 2020, 177, 109200. [Google Scholar] [CrossRef]

- Hazdra, P.; Popelka, S. Displacement damage and total ionisation dose effects on 4H-SiC power devices. IET Power Electron. 2019, 12, 3910–3918. [Google Scholar] [CrossRef]

- Peng, C.; Lei, Z.; Zhang, Z.; Chen, Y.; He, Y.; Yao, B.; En, Y. Influence of Drain Bias and Flux on Heavy Ion-Induced Leakage Currents in SiC Power MOSFETs. IEEE Trans. Nucl. Sci. 2022, 69, 1037–1043. [Google Scholar] [CrossRef]

- Zhang, H.; Guo, H.-X.; Zhang, F.-Q.; Lei, Z.-F.; Pan, X.-Y.; Liu, Y.-T.; Gu, Z.-Q.; Ju, A.-A.; Zhong, X.-L.; Ouyang, X.-P. Study on proton-induced single event effect of SiC diode and MOSFET. Microelectron. Reliab. 2021, 124, 114329. [Google Scholar] [CrossRef]

- Martinella, C.; Alia, R.G.; Stark, R.; Coronetti, A.; Cazzaniga, C.; Kastriotou, M.; Kadi, Y.; Gaillard, R.; Grossner, U.; Javanainen, A. Impact of Terrestrial Neutrons on the Reliability of SiC VD-MOSFET Technologies. IEEE Trans. Nucl. Sci. 2021, 68, 634–641. [Google Scholar] [CrossRef]

- Zhou, X.; Tang, Y.; Jia, Y.; Hu, D.; Wu, Y.; Xia, T.; Gong, H.; Pang, H.Y. Single-Event Effects in SiC Double-Trench MOSFETs. IEEE Trans. Nucl. Sci. 2019, 66, 2312–2318. [Google Scholar] [CrossRef]

- Waskiewicz, A.E.; Groninger, J.W.; Strahan, V.H.; Long, D.M. Burnout of Power MOS Transistors with Heavy Ions of Californium-252. IEEE Trans. Nucl. Sci. 1986, 33, 1710–1713. [Google Scholar] [CrossRef]

- Fischer, T.A. Heavy-Ion-Induced, Gate-Rupture in Power MOSFETs. IEEE Trans. Nucl. Sci. 1987, 34, 1786–1791. [Google Scholar] [CrossRef]

- Cascio, A.; Curro, G. MOS Device Resistant to Ionizing Radiation. U.S. Patent EP1918986A2, 22 February 2010. [Google Scholar]

- Zhaohuan, T.; Gangyi, H.; Guangbing, C.; Kaizhou, T.; Yong, L.; Jun, L.; Xueliang, X. A novel structure for improving the SEGR of a VDMOS. J. Semicond. 2012, 33, 044002. [Google Scholar]

- Wei, J.X.; Liu, S.Y.; Zhao, H.B.; Fu, H.; Zhang, X.B.; Li, S.Y.; Sun, W.F. Verification of Single-Pulse Avalanche Failure Mechanism for Double-Trench SiC Power MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 2190–2200. [Google Scholar] [CrossRef]

- Mantia, S.L.; Pulvirenti, M.; Sciacca, A.G.; Nania, M. SiC MOSFETs Applications and Technology Robustness Evaluation under Avalanche Conditions. In Proceedings of the PCIM Europe Digital Days 2020; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremburg, Germany, 7–8 July 2020. [Google Scholar]

- Sharov, F.V.; Moxim, S.J.; Haase, G.S.; Hughart, D.R.; Lenahan, P.M. A Comparison of Radiation-Induced and High-Field Electrically Stress-Induced Interface Defects in Si/SiO2 MOSFETs via Electrically Detected Magnetic Resonance. IEEE Trans. Nucl. Sci. 2022, 69, 208–215. [Google Scholar] [CrossRef]

- Lelis, A.J.; Green, R.; Habersat, D.B. SiC MOSFET Reliability and Implications for Qualification Testing. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. 2A-4.1–2A-4.4. [Google Scholar]

- Chaturvedi, M.; Dimitrijev, S.; Haasmann, D.; Moghadam, H.A.; Pande, P.; Jadli, U. Quantified density of performance-degrading near-interface traps in SiC MOSFETs. Sci. Rep. 2022, 12, 4076. [Google Scholar] [CrossRef]

- Terman, L.M. An investigation of surface states at a silicon/silicon oxide interface employing metal-oxide-silicon diodes. Solid-State Electron. 1962, 5, 285–299. [Google Scholar] [CrossRef]

- Moll, J.L. Physics of Semiconductors, 1st ed.; McGraw-Hill: New York, NY, USA, 1964; pp. 145–166. [Google Scholar]

- Lenzlinger, M.; Snow, E.H. Fowler-Nordheim Tunneling into Thermally Grown SiO2. J. Appl. Phys. 1969, 40, 278–283. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Feng, H.; Liang, X.; Pu, X.; Xiang, Y.; Zhang, T.; Wei, Y.; Feng, J.; Sun, J.; Zhang, D.; Li, Y.; et al. Total Ionizing Dose Effects of 60Co γ-Ray Radiation on Split-Gate SiC MOSFETs. Electronics 2023, 12, 2398. https://doi.org/10.3390/electronics12112398

Feng H, Liang X, Pu X, Xiang Y, Zhang T, Wei Y, Feng J, Sun J, Zhang D, Li Y, et al. Total Ionizing Dose Effects of 60Co γ-Ray Radiation on Split-Gate SiC MOSFETs. Electronics. 2023; 12(11):2398. https://doi.org/10.3390/electronics12112398

Chicago/Turabian StyleFeng, Haonan, Xiaowen Liang, Xiaojuan Pu, Yutang Xiang, Teng Zhang, Ying Wei, Jie Feng, Jing Sun, Dan Zhang, Yudong Li, and et al. 2023. "Total Ionizing Dose Effects of 60Co γ-Ray Radiation on Split-Gate SiC MOSFETs" Electronics 12, no. 11: 2398. https://doi.org/10.3390/electronics12112398

APA StyleFeng, H., Liang, X., Pu, X., Xiang, Y., Zhang, T., Wei, Y., Feng, J., Sun, J., Zhang, D., Li, Y., Yu, X., & Guo, Q. (2023). Total Ionizing Dose Effects of 60Co γ-Ray Radiation on Split-Gate SiC MOSFETs. Electronics, 12(11), 2398. https://doi.org/10.3390/electronics12112398