Volatile Memristor in Leaky Integrate-and-Fire Neurons: Circuit Simulation and Experimental Study

Abstract

:1. Introduction

2. Materials and Methods

3. Simulation of LIF Neuron with Volatile Memristor

4. Experimental Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Appendix A

| SPICE CODE for volatile memristor |

| *Volatile Memristor Model *Copyright 2021 FTS UNS MEMR Research Group |

| .param Ron=1 Roff=100k uv=1e-10 D=10n qp=300e-9 qn=-300e-9 Rint=15k + k={uv*Ron/D**2} deltaR={Roff-Ron} p=10 .param x0={(Roff-Rint)/(Roff-Ron)} y0={(Roff-Rint)/(Roff-Ron)} z0=0 *New window functions .func fours(x)={(1-(2*x-1)**2)/(1-(2*x-1)**2+(2*x-1)**(2*p))} .func iy(y,v,z)={if(v>0,if(z>qp,I(Emem)*uv*Ron*fours(y)/D**2,0),if(z<qn,I(Emem)*uv*Ron*fours(y)/D**2,0))} .subckt memristor_vol 1 2 x y z *terminal cell Roff 1 aux {Roff} Emem aux 2 value={-deltaR*v(x)*I(Emem)} *end of terminal cell *x-module Gx 0 x value={I(Emem)*uv*Ron*fours(v(x))/D**2} Cx x 0 0.5 IC={x0} Rx x 3 1 Enov 3 0 value={v(y)} *end of x-module *y-module Gy 0 y value={iy(v(y),v(x),v(z))} Cy y 0 1 IC={y0} *end of y-module *z-module Gch 0 z value={I(Emem)} Cz z 0 1 IC={0} Rz z 0 0.1 *end of z-module .ends memristor_vol |

References

- Krestinskaya, O.; James, A.P.; Chua, L.O. Neuromemristive circuits for edge computing: A review. IEEE Trans. Neural Netw. Learn Syst. 2020, 31, 4–23. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Xu, W.; Wang, J.; Yan, X. Advances in memristor-based neural networks. Front. Nanotechnol. 2021, 3, 20. [Google Scholar] [CrossRef]

- Sung, C.; Hwang, H.; Yoo, I.K. Perspective: A review on memristive hardware for neuromorphic computation. J. Appl. Phys. 2018, 124, 151903. [Google Scholar] [CrossRef] [Green Version]

- Schuman, C.D.; Potok, T.E.; Patton, R.M.; Birdwell, J.D.; Dean, M.E.; Rose, G.S.; Plank, J.S. A survey of neuromorphic computing and neural networks in hardware. arXiv 2017, arXiv:1705.06963. [Google Scholar]

- Zhang, Y.; Wang, X.; Friedman, E.G. Memristor-Based circuit design for multilayer neural networks. IEEE Trans. Circuits Syst. I Regul Pap. 2018, 65, 677–686. [Google Scholar] [CrossRef]

- Pantazi, A.; Woźniak, S.; Tuma, T.; Eleftheriou, E. All-Memristive neuromorphic computing with level-tuned neurons. Nanotechnology 2016, 27, 355205. [Google Scholar] [CrossRef] [PubMed]

- Chua, L. Memristor, Hodgkin-Huxley, and edge of chaos. Nanotechnology 2013, 27, 383001. [Google Scholar] [CrossRef] [PubMed]

- Gerasimova, S.A.; Belov, A.I.; Korolev, D.S.; Guseinov, D.V.; Lebedeva, A.V.; Koryazhkina, M.N.; Mikhaylov, A.N.; Kazantsev, V.B.; Pisarchik, A.N. Stochastic memristive interface for neural signal processing. Sensors 2021, 21, 5587. [Google Scholar] [CrossRef] [PubMed]

- Tan, Y.; Wang, C. A simple locally active memristor and its application in HR neurons. Chaos 2020, 30, 053118. [Google Scholar] [CrossRef]

- Rozenberg, M.J.; Schneegans, O.; Stoliar, P. An ultra-compact leaky-integrate-and-fire model for building spiking neural networks. Sci. Rep. 2019, 9, 11123. [Google Scholar] [CrossRef] [Green Version]

- Hodgkin, A.L.; Huxley, A.F. A quantitative description of membrane current and its application to conduction and excitation in nerve. J. Physiol. 1952, 117, 500–544. [Google Scholar] [CrossRef] [PubMed]

- Yi, W.; Tsang, K.K.; Lam, S.K.; Bai, X.; Crowell, J.A.; Flores, E.A. Biological plausibility and stochasticity in scalable VO2 active memristor neurons. Nat. Commun. 2018, 9, 4661. [Google Scholar] [CrossRef] [PubMed]

- Ascoli, A.; Demirkol, A.S.; Tetzlaff, R.; Slesazeck, S.; Mikolajick, T.; Chua, L.O. on local activity and edge of chaos in a NaMLab memristor. Front. Neurosci. 2021, 15, 651452. [Google Scholar] [CrossRef] [PubMed]

- Kornijcuk, V.; Lim, H.; Seok, J.Y.; Guhyun, K.; Seong, K.K.; Kim, I.; Choi, B.J.; Jeong, D.S. Leaky integrate-and-fire neuron circuit based on floating-gate integrator. Front. Neurosci. 2016, 10, 212. [Google Scholar] [CrossRef] [PubMed]

- Guo, T.; Pan, K.; Sun, B.; Wei, L.; Yan, Y.; Zhou, Y.N.; Wu, Y.A. Adjustable leaky-integrate-and-fire neurons based on memristor-coupled capacitors. Mater. Today Adv. 2021, 12, 100192. [Google Scholar] [CrossRef]

- Yang, J.; Wang, R.; Wang, Z.; .Ma, Q.; Mao, J.; Ren, Y.; Yang, X.; Zhou, Y.; Han, S. Leaky integrate-and-fire neurons based on perovskite memristor for spiking neural networks. Nano Energy 2020, 74, 104828. [Google Scholar] [CrossRef]

- Wang, Z.; Joshi, S.; Savel’ev, S.; Song, W.; Midya, R.; Li, Y.; Rao, M.; Yan, P.; Asapu, S.; Zhuo, Y.; et al. Fully memristive neural networks for pattern classification with unsupervised learning. Nat. Electron. 2018, 1, 137–145. [Google Scholar] [CrossRef]

- Wang, Z.; Joshi, S.; Savel’ev, S.; Jiang, H.; Midya, R.; Lin, P.; Hu, M.; Ge, N.; Strachan, J.P.; Li, Z.; et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 2017, 16, 101–108. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Lu, Y.-F.; Li, Y.; Li, H.; Wan, T.Q.; Huang, X.; He, Y.H.; Miao, X. Low-Power artificial neurons based on Ag/TiN/HfAlOx/Pt threshold switching memristor for neuromorphic computing. IEEE Electron Device Lett. 2020, 41, 1245–1248. [Google Scholar] [CrossRef]

- Midya, R.; Wang, Z.; Zhang, J.; Savel’ev, S.E.; Li, C.; Rao, M.; Jang, M.H.; Joshi, S.; Jiang, H.; Lin, P.; et al. Anatomy of Ag/Hafnia-based selectors with 1010 nonlinearity. Adv. Mater. 2017, 29, 1604457. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Jiang, H.; Belkin, D.; Savel’ev, S.E.; Lin, S.; Wang, Z.; Li, Y.; Joshi, S.; Midya, R.; Li, C.; Rao, M.; et al. A novel true random number generator based on a stochastic diffusive memristor. Nat. Commun. 2017, 8, 882. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Giotis, C.; Serb, A.; Stathopoulos, S.; Michalas, L.; Khiat, A.; Prodromakis, T. Bidirectional volatile signatures of metal–oxide memristors—Part I: Characterization. IEEE Trans. Electron Devices 2020, 67, 5158–5165. [Google Scholar] [CrossRef]

- Berdan, R.; Lim, C.; Khiat, A.; Papavassiliou, C.; Prodromakis, T. A memristor SPICE model accounting for volatile characteristics of practical ReRAM. IEEE Electron Device Lett. 2014, 35, 135–137. [Google Scholar] [CrossRef]

- Giotis, C.; Serb, A.; Stathopoulos, S.; Prodromakis, T. Bidirectional volatile signatures of metal-oxide memristors—Part II: Modeling. IEEE Trans. Electron Devices 2020, 67, 5166–5173. [Google Scholar] [CrossRef]

- Wang, W.; Laudato, M.; Ambrosi, E.; Bricalli, A.; Covi, E.; Lin, Y.H.; Ielmini, D. Volatile resistive switching memory based on Ag ion drift/diffusion part I: Numerical modelling. IEEE Trans. Electron Devices 2019, 66, 3795–3801. [Google Scholar] [CrossRef]

- Wang, W.; Laudato, M.; Ambrosi, E.; Bricalli, A.; Covi, E.; Lin, Y.H.; Ielmini, D. Volatile resistive switching memory based on Ag ion drift/diffusion—Part II: Compact modelling. IEEE Trans. Electron Devices 2019, 66, 3802–3808. [Google Scholar] [CrossRef]

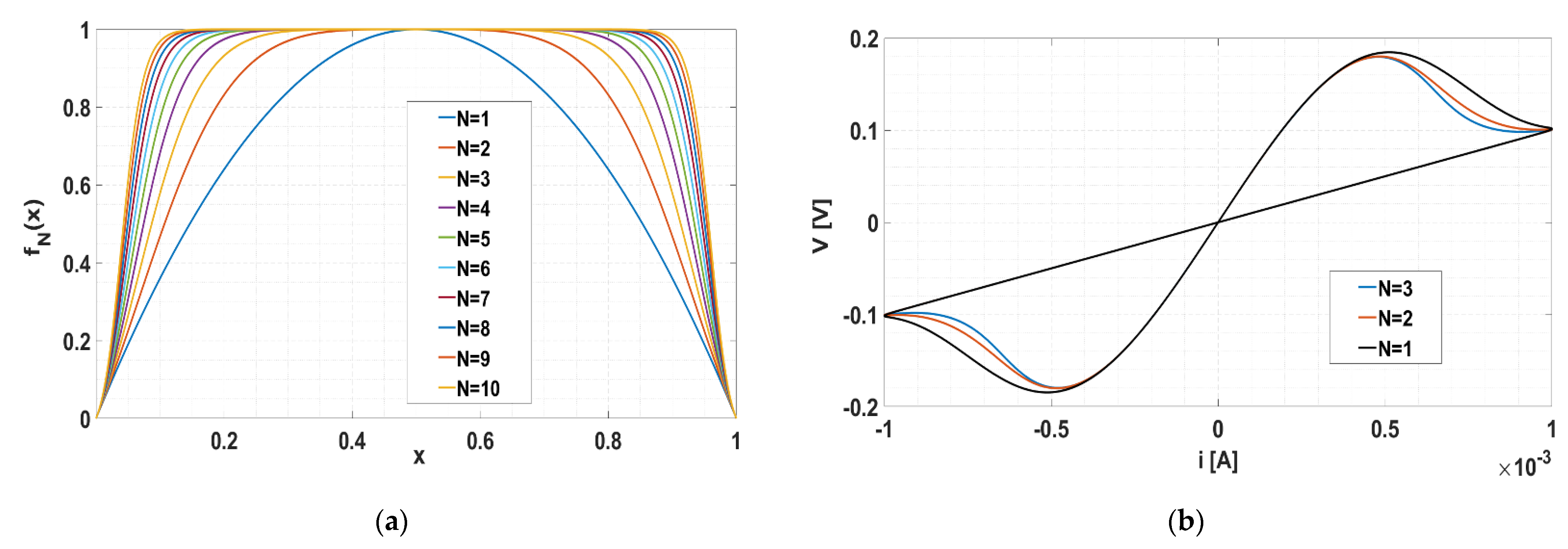

- Dautovic, S.; Samardzic, N.; Juhas, A.; Ascoli, A.; Tetzlaff, R. On Window Functions for Ideal Generic Memristor. 2022; unpublished. [Google Scholar]

- Dautovic, S.; Samardzic, N.; Juhas, A.; Ascoli, A.; Tetzlaff, R. Simscape and LTspice models of HP ideal generic memristor based on finite closed form solution for window functions. In Proceedings of the 28th IEEE International Conference on Electronics Circuits and Systems (ICECS), Dubai, United Arab Emirates, 28 November–1 December 2021. [Google Scholar]

- Bajac, B.; Vukmirovic, J.; Tripkovic, D.; Djurdjic, E.; Stanojev, J.; Cvejic, Z.; Škorić, B.; Srdić, V.V. Structural characterization and dielectric properties of BaTiO3 thin films obtained by spin coating. Process. Appl. Ceram. 2014, 8, 219–224. [Google Scholar] [CrossRef]

- Joglekar, Y.N.; Wolf, S.J. The elusive memristor: Properties of basic electrical circuits. Eur. J. Phys. 2009, 30, 661–675. [Google Scholar] [CrossRef] [Green Version]

- Prodromakis, T.; Peh, B.P.; Papavassiliou, C.; Toumazou, C. A versatile memristor model with nonlinear dopant kinetics. IEEE Trans. Electron. Devices 2011, 58, 3099–3105. [Google Scholar] [CrossRef]

- Biolek, Z.; Biolek, D.; Biolkova, V. SPICE model of memristor with nonlinear dopant drift. Radioengineering 2009, 18, 210–214. [Google Scholar]

- Kvatinsky, S.; Friedman, E.G.; Kolodny, A.; Weiser, U.C. TEAM: ThrEshold adaptive memristor model. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 211–221. [Google Scholar] [CrossRef]

- Singh, J.; Raj, B. An accurate and generic window function for nonlinear memristor models. J. Comput. Electron. 2019, 18, 640–647. [Google Scholar] [CrossRef]

- Li, Q.; Serb, A.; Prodromakis, T.; Xu, H. A memristor SPICE model accounting for synaptic activity dependence. PLoS ONE 2015, 10, e0120506. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Dawson, J.A. Dynamical insights into oxygen diffusion in BaTiO3 and SrTiO3. Phys. Status Solidi B 2020, 257, 1900422. [Google Scholar] [CrossRef]

- Chang, T.; Jo, S.; Wei, L. Short-Term memory to long-term memory transition in a nanoscale memristor. ACS Nano 2011, 5, 7669–7676. [Google Scholar] [CrossRef] [PubMed]

- Sokolov, A.S.; Ali, M.; Riaz, R.; Abbas, Y.; Ko, M.J.; Choi, C. Silver-Adapted diffusive memristor based on organic nitrogen-doped graphene oxide quantum dots (N-GOQDs) for artificial biosynapse applications. Adv. Funct. Mater. 2019, 29, 1807504. [Google Scholar] [CrossRef]

- Abbas, H.; Abbas, Y.; Hassan, G.; Sokolov, A.S.; Jeon, Y.R.; Ku, B.; Kang, C.J.; Choi, C. The coexistence of threshold and memory switching characteristics of ALD HfO2 memristor synaptic arrays for energy-efficient neuromorphic computing. Nanoscale 2020, 12, 14120–14134. [Google Scholar] [CrossRef] [PubMed]

- Wang, R.; Yang, J.; Mao, J.; Wang, Z.; Wu, S.; Zhou, M.; Chen, T.; Zhou, Y.; Han, S. Recent advances of volatile memristors: Devices, mechanisms, and applications. Adv. Intell. Syst. 2020, 2, 2000055. [Google Scholar] [CrossRef]

| Different Window Functions | Joglekar [30] | Prodromakis [31] | Biolek [32] | Kvatinsky [33] | Singh [34] | This Paper |

|---|---|---|---|---|---|---|

| Symmetric | Yes | Yes | Yes | Not necessarily | Yes | Yes |

| Resolve boundary conditions | No | Practically Yes | Yes | Practically Yes | Yes | Practically Yes |

| Accounts for non-linear effects | Partially | Partially | Partially | Yes | Partially | Partially |

| Scalability 0 ≤ fmax (x) ≤ 1 | No | Yes | No | No | Yes | Partially * |

| Fits memristive device model | L/N/TEAM | L/N/TEAM | L/N/TEAM | TEAM | L/N/TEAM | L/N/TEAM |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Samardzic, N.M.; Bajic, J.S.; Sekulic, D.L.; Dautovic, S. Volatile Memristor in Leaky Integrate-and-Fire Neurons: Circuit Simulation and Experimental Study. Electronics 2022, 11, 894. https://doi.org/10.3390/electronics11060894

Samardzic NM, Bajic JS, Sekulic DL, Dautovic S. Volatile Memristor in Leaky Integrate-and-Fire Neurons: Circuit Simulation and Experimental Study. Electronics. 2022; 11(6):894. https://doi.org/10.3390/electronics11060894

Chicago/Turabian StyleSamardzic, Natasa M., Jovan S. Bajic, Dalibor L. Sekulic, and Stanisa Dautovic. 2022. "Volatile Memristor in Leaky Integrate-and-Fire Neurons: Circuit Simulation and Experimental Study" Electronics 11, no. 6: 894. https://doi.org/10.3390/electronics11060894

APA StyleSamardzic, N. M., Bajic, J. S., Sekulic, D. L., & Dautovic, S. (2022). Volatile Memristor in Leaky Integrate-and-Fire Neurons: Circuit Simulation and Experimental Study. Electronics, 11(6), 894. https://doi.org/10.3390/electronics11060894