A 48 GHz Fundamental Frequency PLL with Quadrature Clock Generation for 60 GHz Transceiver

Abstract

:1. Introduction

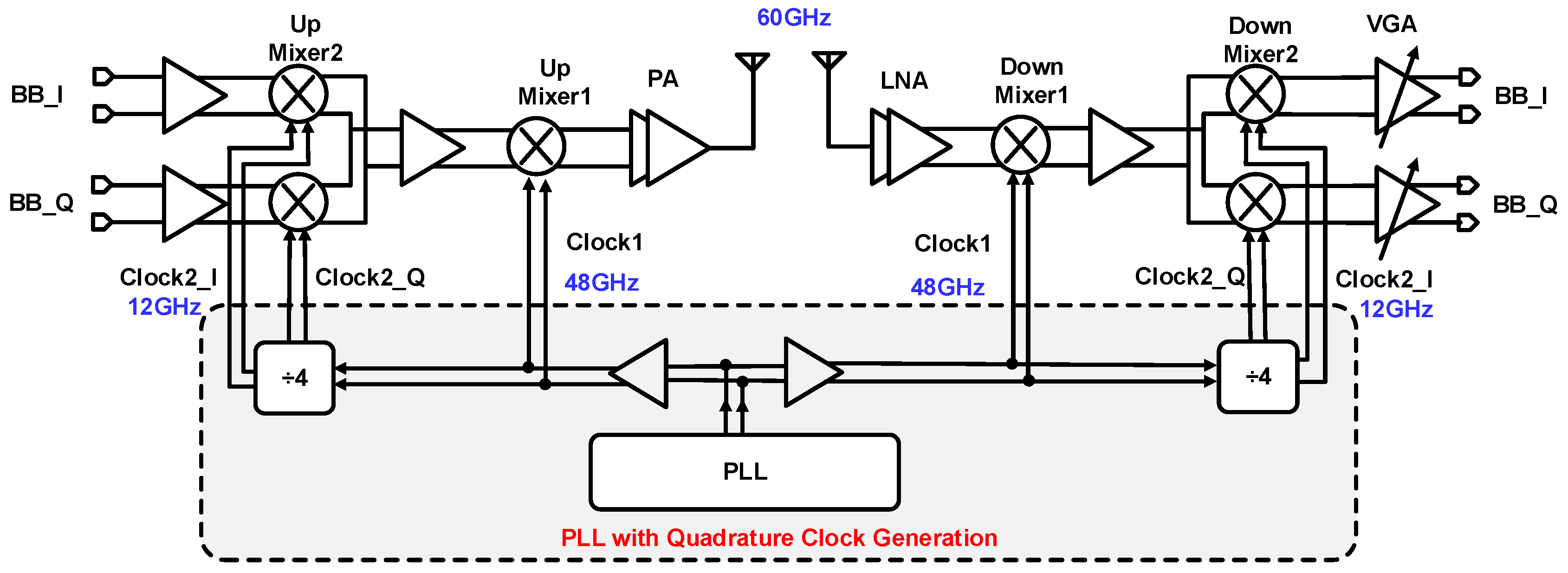

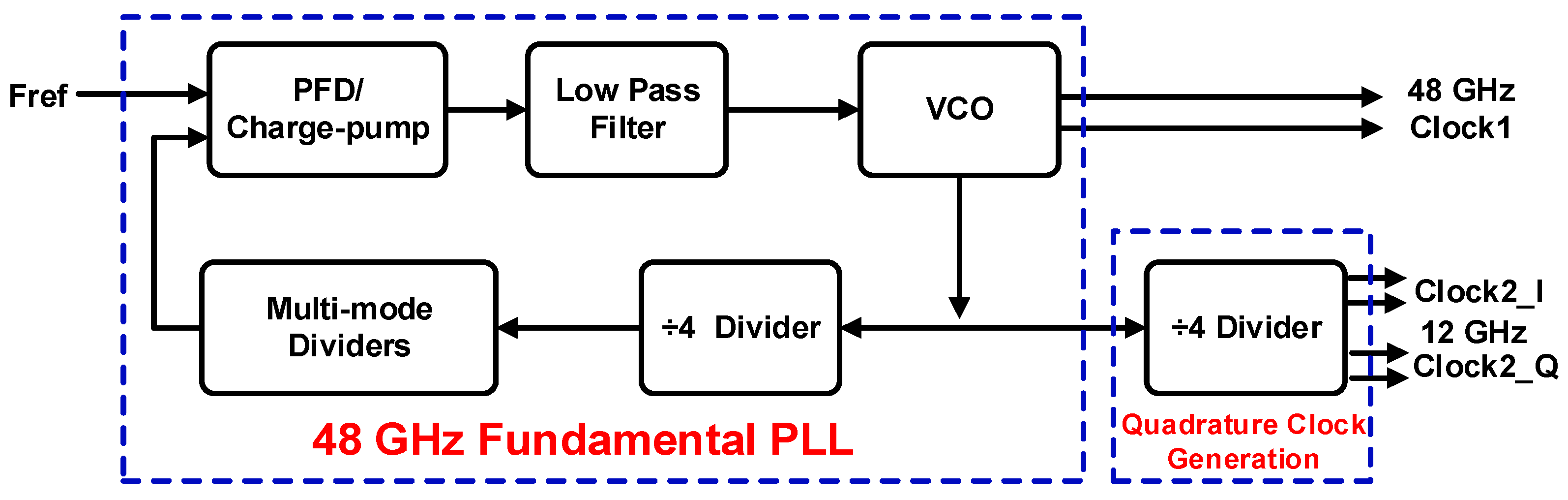

2. Proposed PLL Topology for the 60 GHz Sliding-IF Transceiver

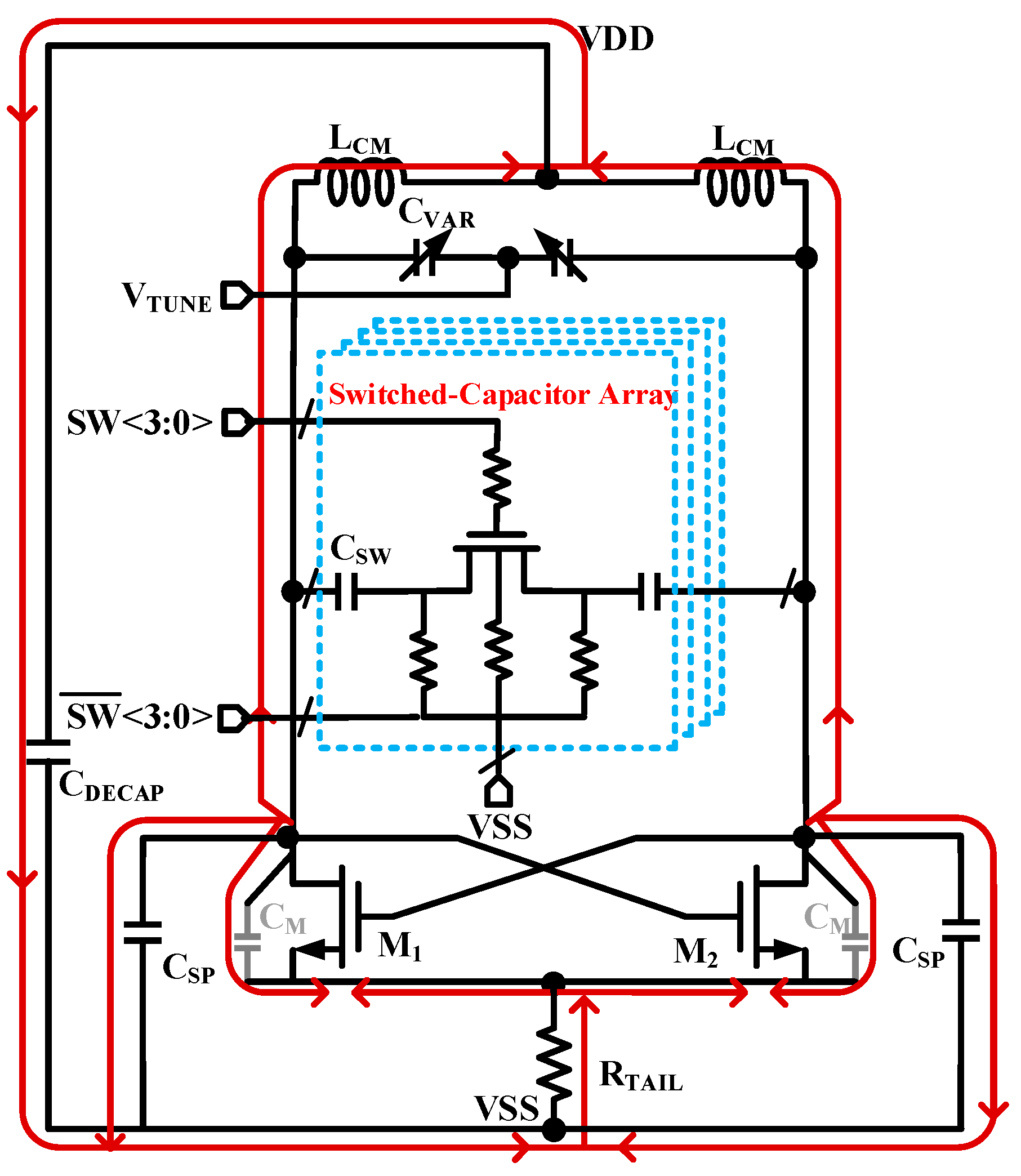

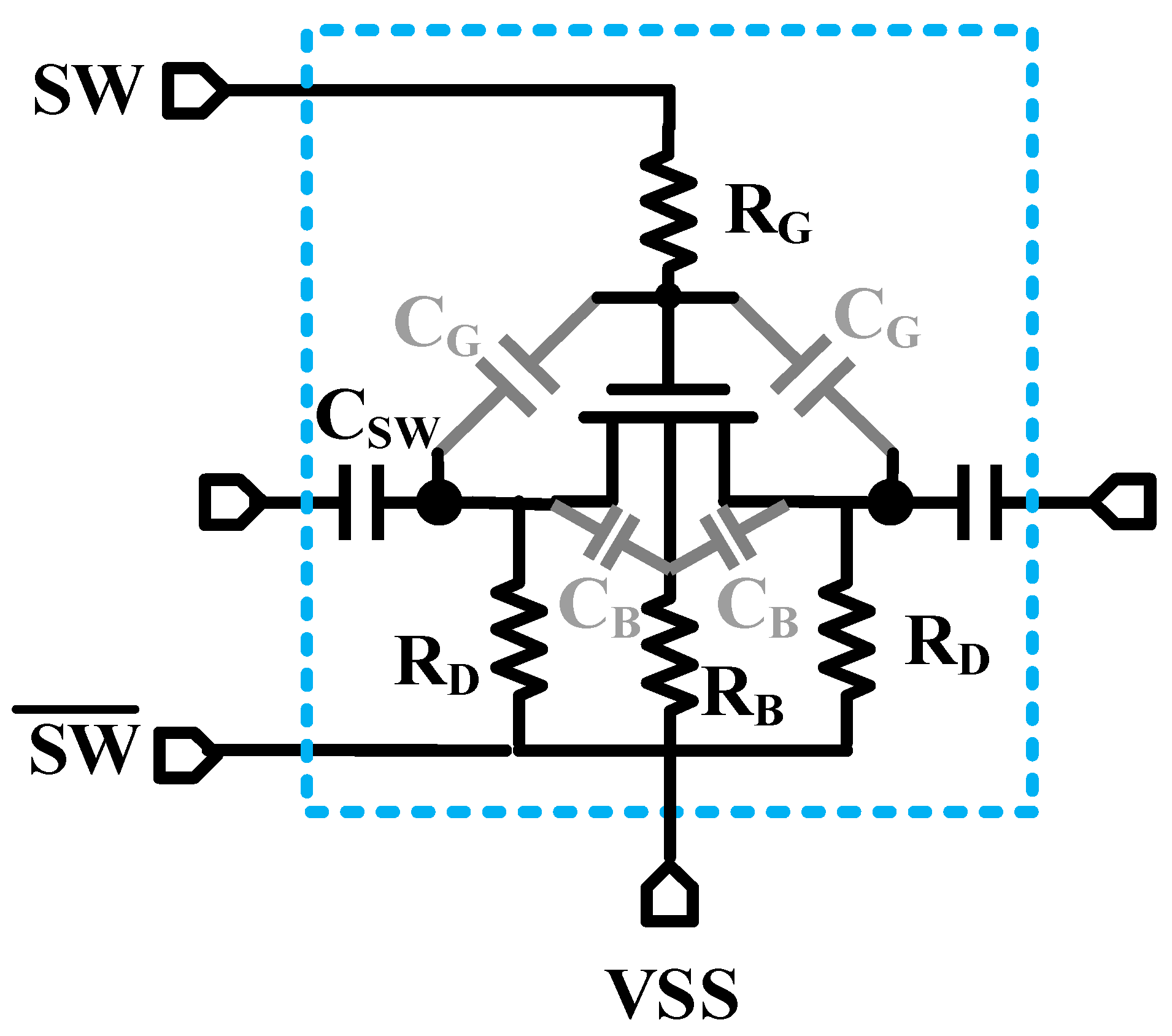

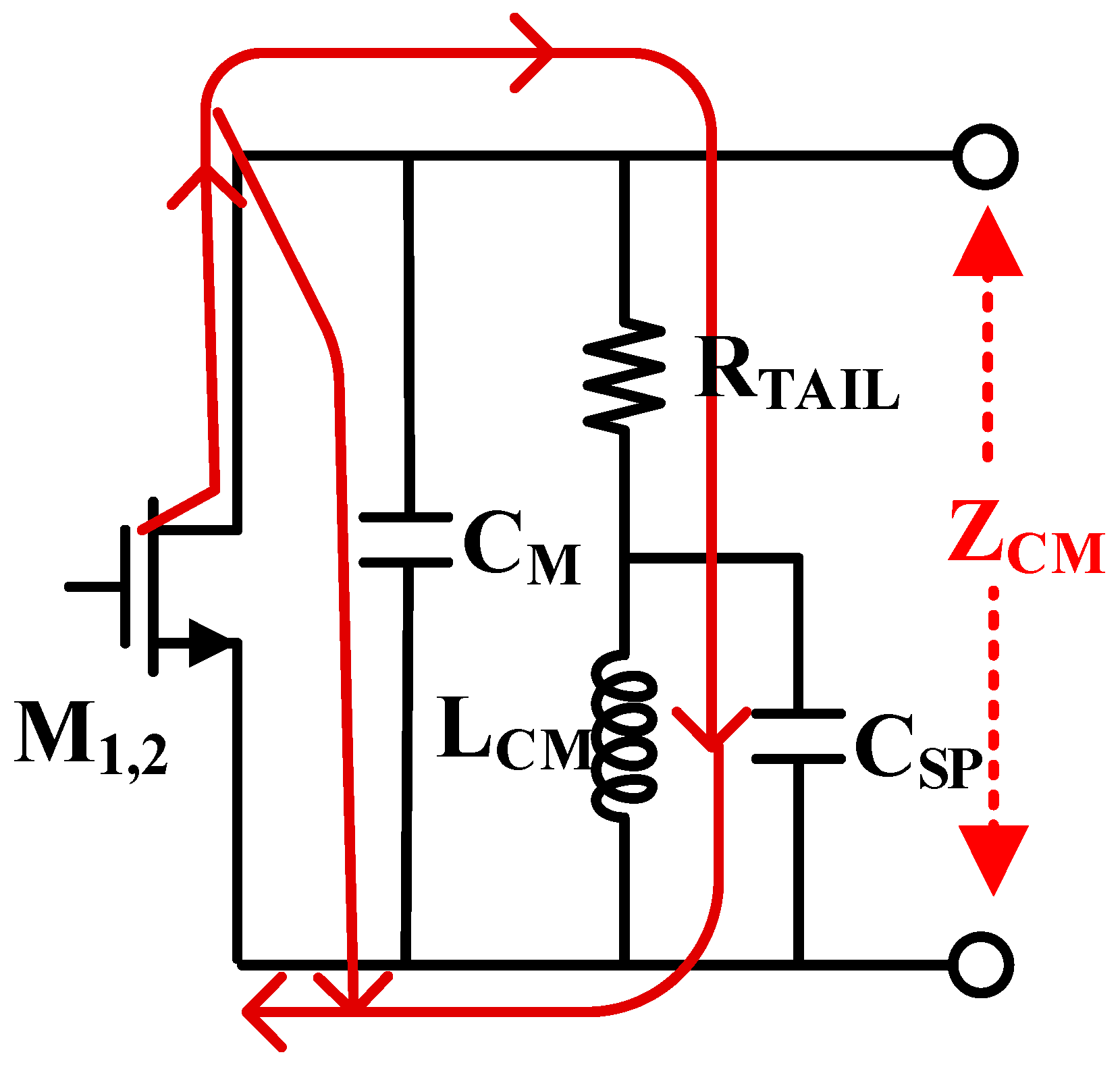

3. VCO Implementation

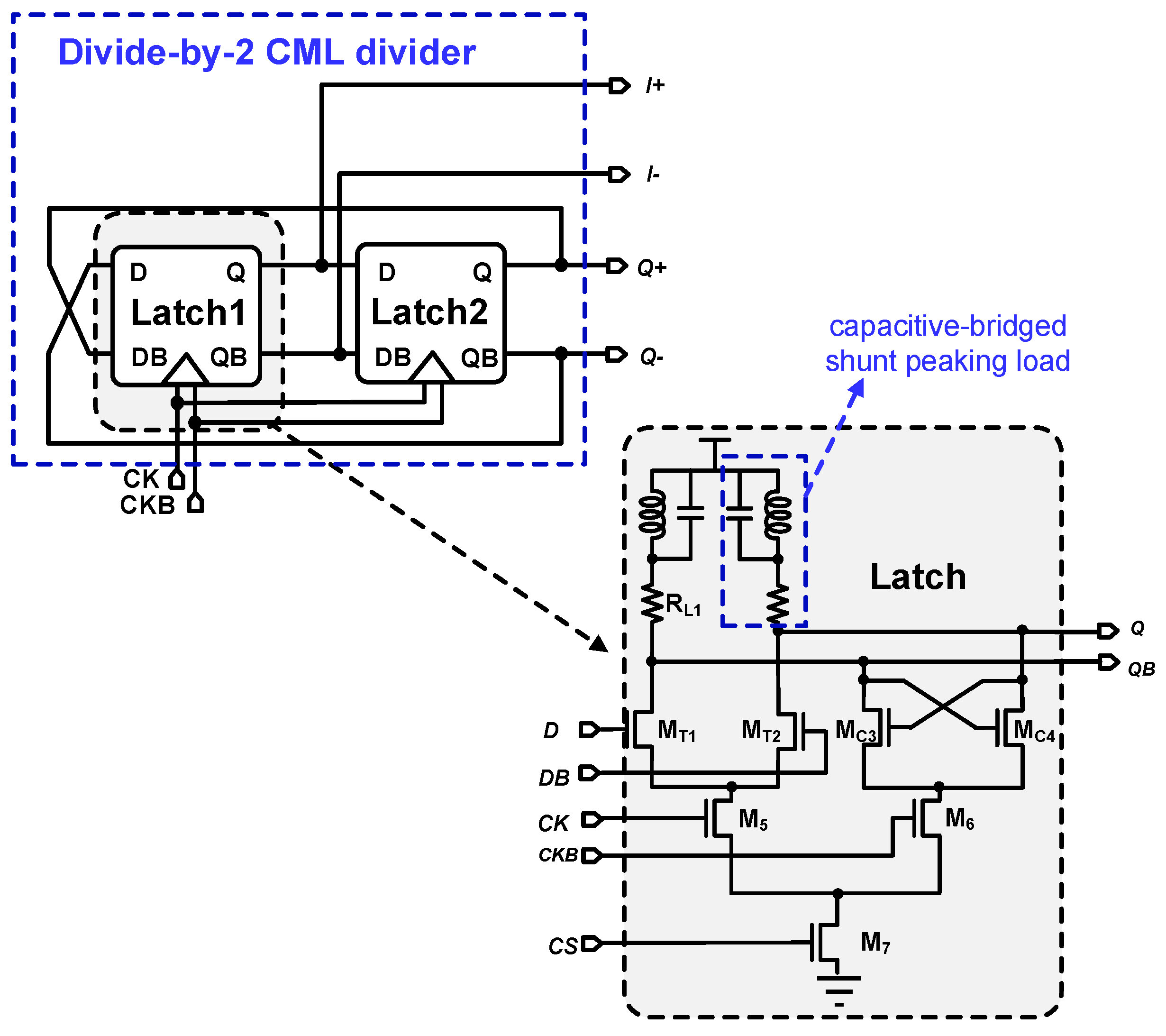

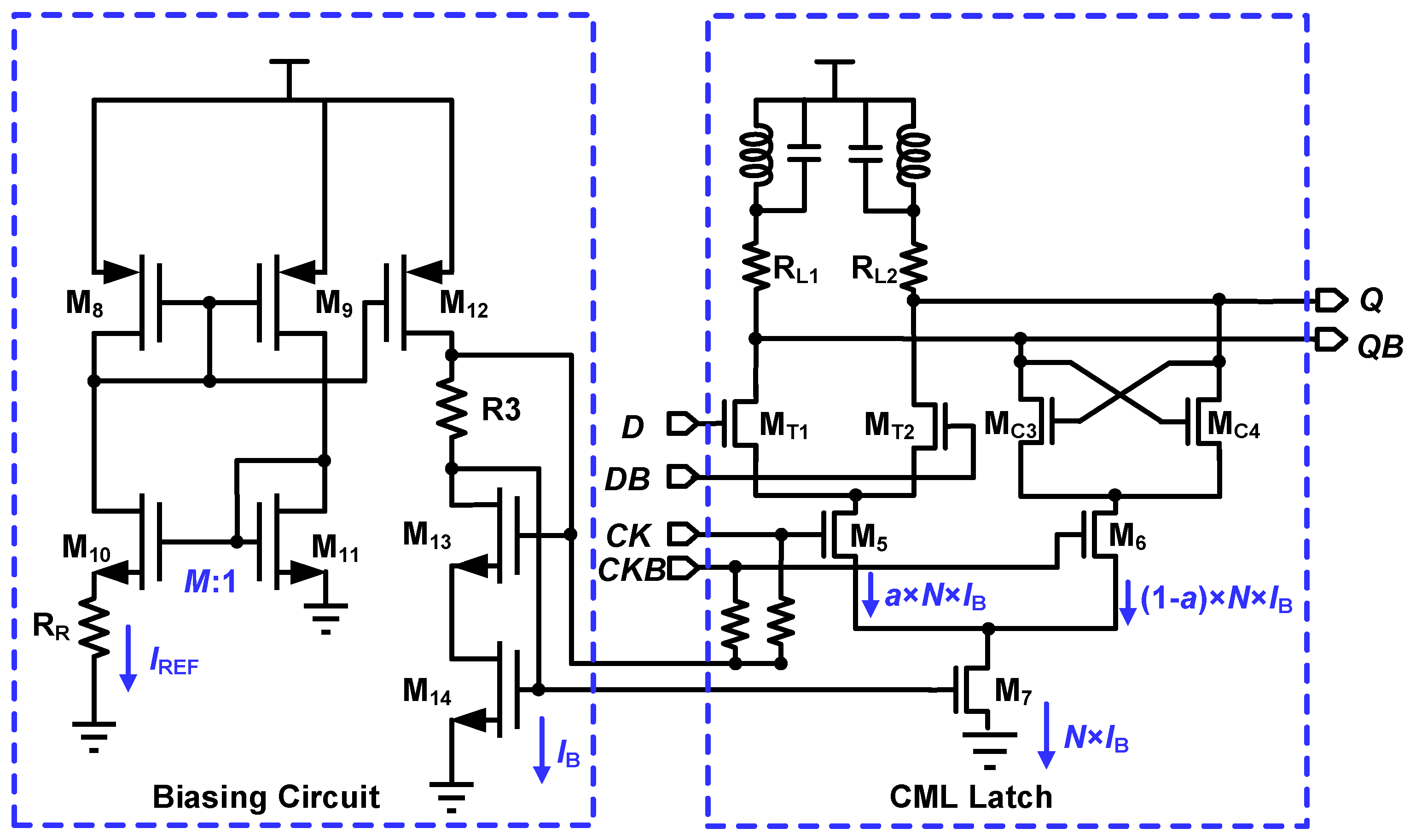

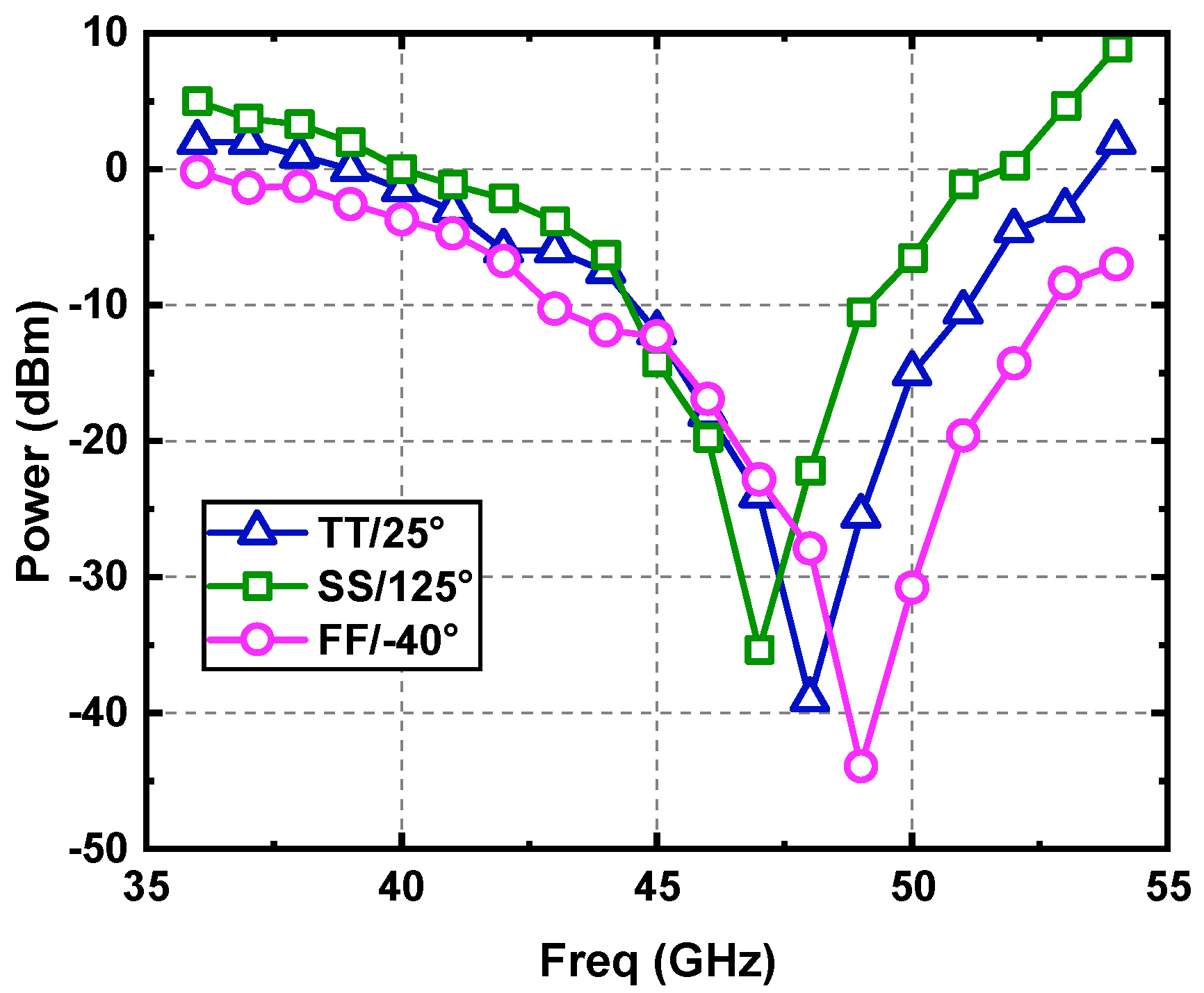

4. Frequency Dividers Implementation

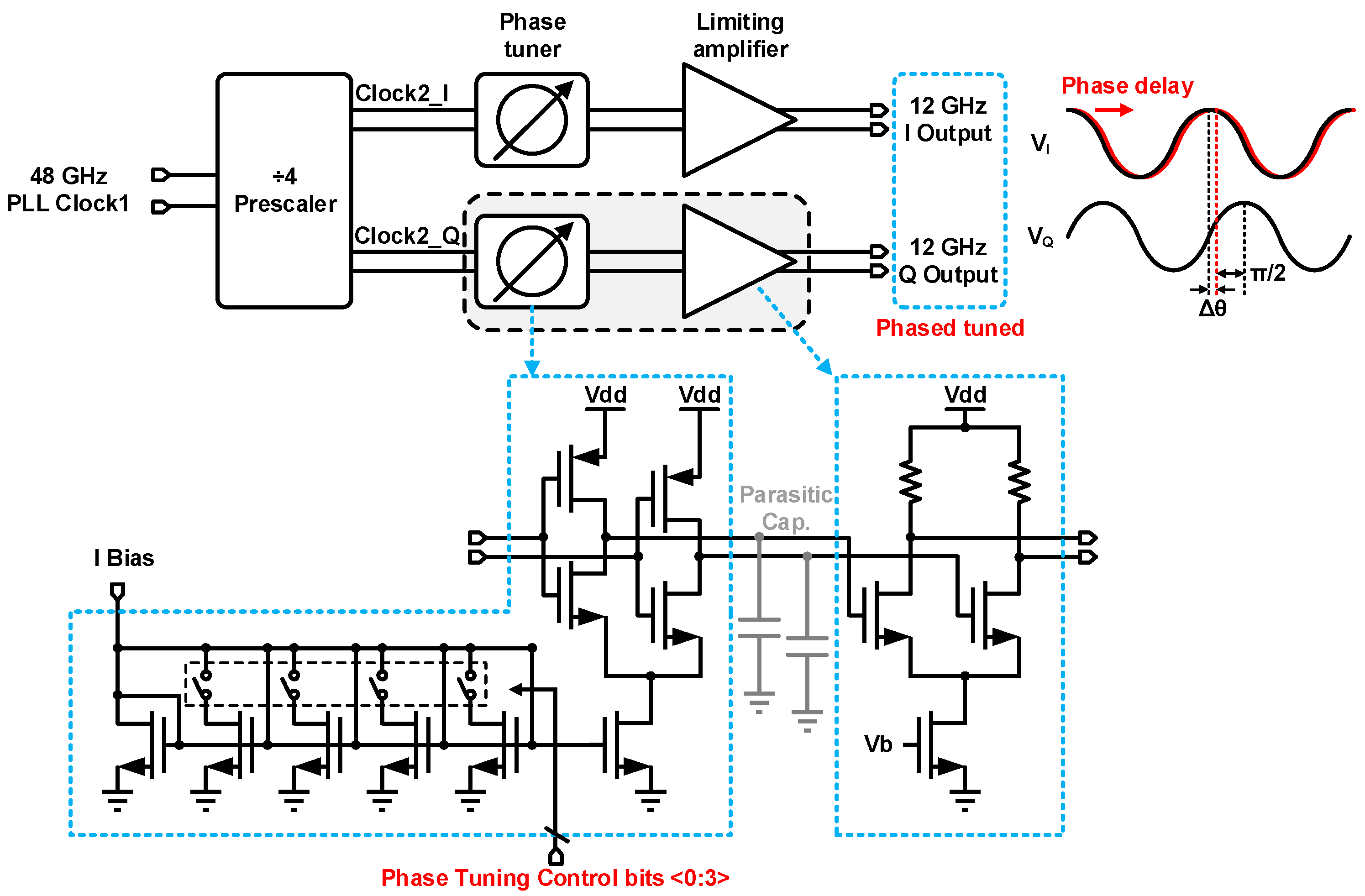

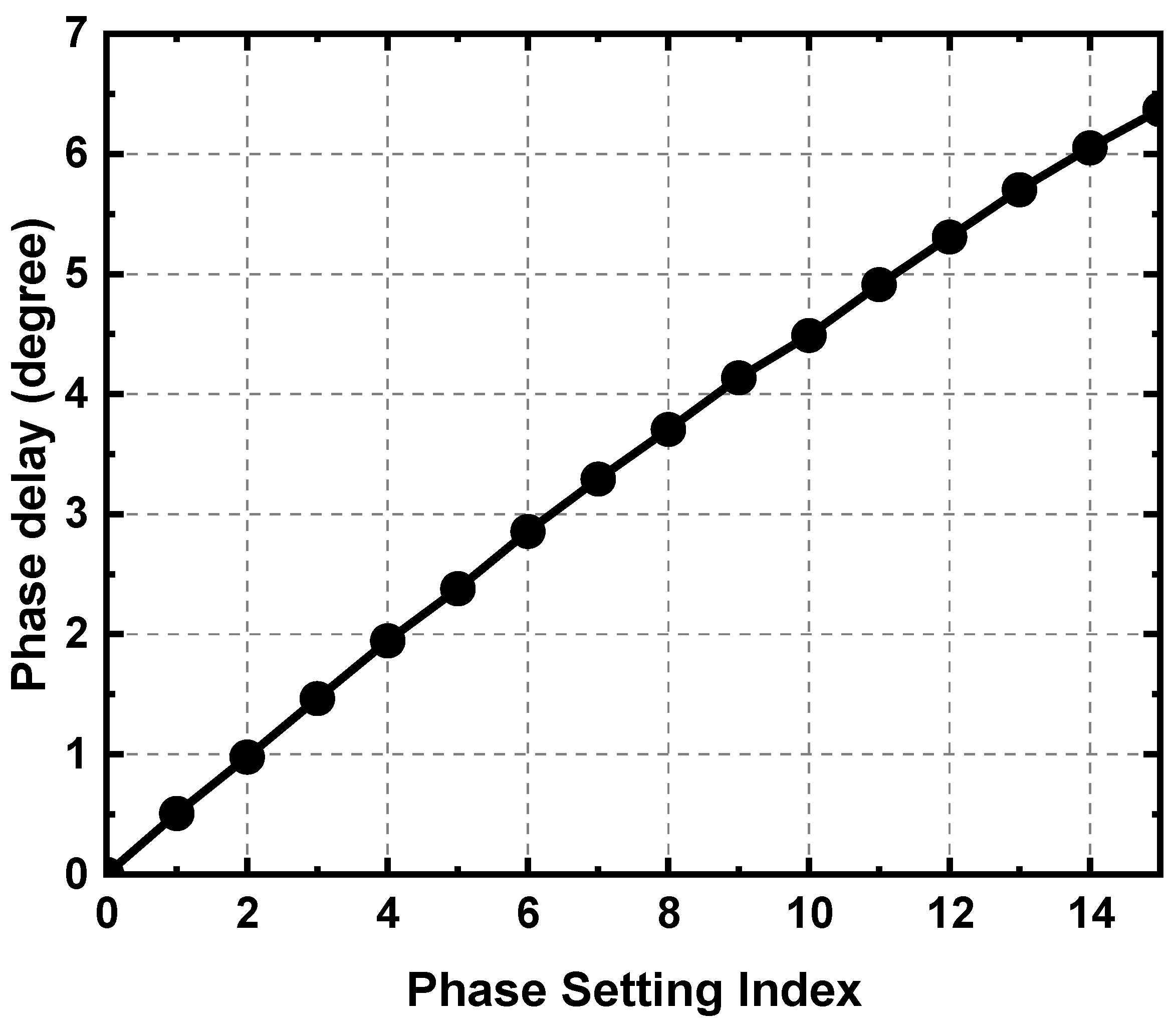

5. Quadrature Clock Calibration

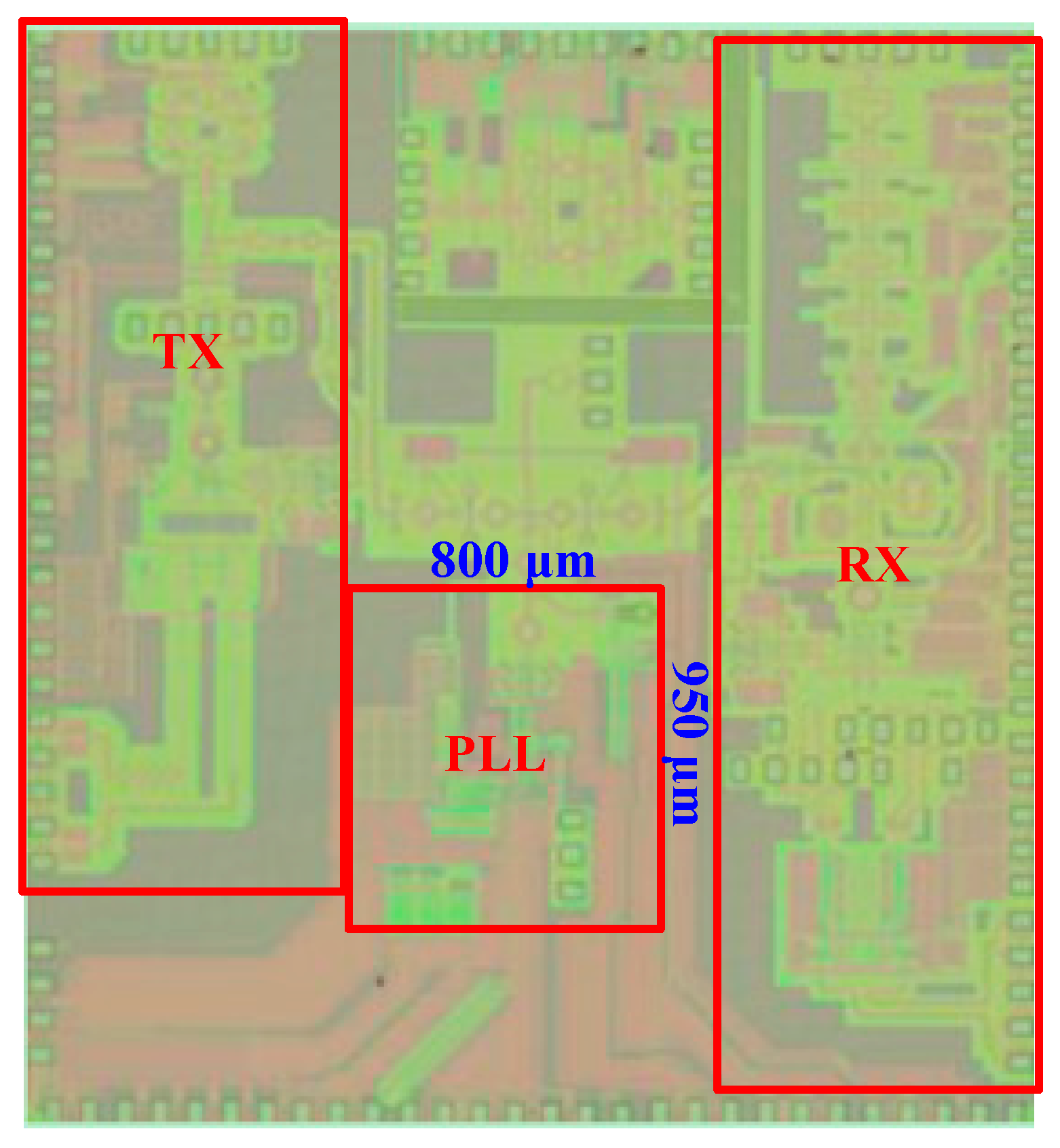

6. Measurement Results

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Tabesh, M.; Chen, J.; Marcu, C.; Kong, L.; Kang, S.; Alon, E.; Niknejad, A. A 65 nm CMOS 4-element Sub-34mW/element 60 GHz phased-array transceiver. In Proceedings of the 2011 IEEE Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 20–24 February 2011; pp. 166–168. [Google Scholar]

- Wu, R.; Minami, R.; Tsukui, Y.; Kawai, S.; Seo, Y.; Sato, S.; Kimura, K.; Kondo, S.; Ueno, T.; Fajri, N.; et al. 64-QAM 60-GHz CMOS Transceivers for IEEE 802.11ad/ay. IEEE J. Solid-State Circuits 2017, 52, 2871–2891. [Google Scholar] [CrossRef]

- Dasgupta, K.; Daneshgar, S.; Thakkar, C.; Kang, S.; Chakrabarti, A.; Yamada, S.; Narevsky, N.; Choudhury, D.; Jaussi, J.E.; Casper, B. A 60-GHz Transceiver and Baseband with Polarization MIMO in 28-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 3613–3627. [Google Scholar] [CrossRef]

- Lin, Y.; Chen, F.T.; Chen, W.Z. A Millimeter-Wave Frequency Synthesizer for 60 GHz Wireless Interconnect. In Proceedings of the 2020 International Symposium on VLSI Design, Automation and Test (VLSI-DAT), Hsinchu, Taiwan, 10–13 August 2020; pp. 1–2. [Google Scholar]

- Lee, W.; Dinc, T.; Valdes-Garcia, A. Multi-Mode 60-GHz Radar Transmitter SoC in 45-nm SOI CMOS. IEEE J. Solid-State Circuits 2020, 55, 1187–1198. [Google Scholar] [CrossRef]

- Ma, K.; Mou, S.; Mahalingam, N.; Wang, Y.; Thangarasu, B.K.; Yan, J.; Ye, W.; Wang, K.; Lim, W.M.; Wong, T.S.; et al. An Integrated 60GHz Low Power Two-Chip Wireless System Based on IEEE802.11ad Standard. In Proceedings of the 2014 IEEE MTT-S International Microwave Symposium (IMS2014), Tampa, FL, USA, 1–6 June 2014; pp. 1–6. [Google Scholar]

- Wu, W.; Staszewski, R.B.; Long, J.R. A 56.4-to-63.4 GHz Multi-Rate All-Digital Fractional-N PLL for FMCW Radar Applications in 65 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 1081–1096. [Google Scholar] [CrossRef]

- Hussein, A.; Vasadi, S.; Soliman, M.; Paramesh, J. 19.3 A 50-to-66GHz 65nm CMOS all-digital fractional-N PLL with 220fsrms jitter. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 326–327. [Google Scholar]

- Elbadry, M.; Sadhu, B.; Qiu, J.X.; Harjani, R. Dual-channel injection-locked quadrature LO generation for a 4-GHz instantaneous bandwidth receiver at 21-GHz center frequency. IEEE Trans. Microw. Theory Techn. 2013, 61, 1186–1199. [Google Scholar] [CrossRef]

- Deng, W.; Siriburanon, T.; Musa, A.; Okada, K.; Matsuzawa, A. A Sub-Harmonic Injection-Locked Quadrature Frequency Synthesizer With Frequency Calibration Scheme for Millimeter-Wave TDD Transceivers. IEEE J. Solid-State Circuits 2013, 48, 1710–1720. [Google Scholar] [CrossRef]

- Sadhu, B.; Ferriss, M.; Valdes-Garcia, A. A 52 GHz frequency synthesizer featuring a 2nd harmonic extraction technique that preserves VCO performance. IEEE J. Solid-State Circuits 2015, 50, 1214–1223. [Google Scholar] [CrossRef]

- Sadhu, B.; Kalia, S.; Harjani, R. A 3-band switched-inductor LC VCO and differential current re-use doubler achieving 0.7-to-11.6 GHz tuning range. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Phoenix, AZ, USA, 17–19 May 2015; pp. 191–194. [Google Scholar]

- Wang, H.; Momeni, O. Low-Power and Low-Noise Millimeter-Wave SSPLL with Subsampling Lock Detector for Automatic Dividerless Frequency Acquisition. IEEE Trans. Microw. Theory Tech. 2021, 69, 469–481. [Google Scholar] [CrossRef]

- Lim, Y.; Kim, J.; Jo, Y.; Bang, J.; Yoo, S.; Park, H.; Yoon, H.; Choi, J. A 170MHz-Lock-In-Range and −253dB-FoMjitter 12-to-14.5GHz Subsampling PLL with a 150µW Frequency-Disturbance-Correcting Loop Using a Low-Power Unevenly Spaced Edge Generator. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 280–282. [Google Scholar]

- Liao, D.; Zhang, Y.; Dai, F.F.; Chen, Z.; Wang, Y. An mm-Wave Synthesizer With Robust Locking Reference-Sampling PLL and Wide-Range Injection-Locked VCO. IEEE J. Solid-State Circuits 2020, 55, 536–546. [Google Scholar] [CrossRef]

- Bertulessi, L.; Grimaldi, L.; Cherniak, D.; Samori, C.; Levantino, S. A low-phase-noise digital bang-bang PLL with fast lock over a wide lock range. In Proceedings of the 2018 IEEE International Solid—State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 252–254. [Google Scholar]

- Hegazi, E.; Sjoland, H.; Abidi, A. A filtering technique to lower LC oscillator phase noise. IEEE J. Solid-State Circuits 2001, 36, 1921–1930. [Google Scholar] [CrossRef] [Green Version]

- Fu, Y.; Li, L.; Wang, D.; Wang, X. A −193.6 dBc/Hz FoMT 28.6-to-36.2 GHz Dual-Core CMOS VCO for 5G Applications. IEEE Access 2020, 8, 62191–62196. [Google Scholar] [CrossRef]

- Fei, W.; Yu, H.; Yeo, K.S.; Lim, W.M. A 60GHz VCO with 25.8% Tuning Range by Switching Return-Path in 65nm CMOS. In Proceedings of the IEEE Asian Solid-State Circuits Conference 2012, Kobe, Japan, 12–14 November 2012; pp. 277–280. [Google Scholar]

- Hu, Y.; Siriburanon, T.; Staszewski, R.B. A Low-Flicker-Noise 30-GHz Class-F23 Oscillator in 28-nm CMOS Using Implicit Resonance and Explicit Common-Mode Return Path. IEEE J. Solid-State Circuits 2018, 53, 1977–1987. [Google Scholar] [CrossRef] [Green Version]

- Fu, H.; Fei, W.; Yu, H. A 60.8–67GHz and 6.3mW injection-locked frequency divider with switching-inductor loaded transformer in 65nm CMOS. In Proceedings of the 2014 IEEE MTT-S International Microwave Symposium (IMS2014), Tampa, FL, USA, 1–6 June 2014; pp. 1–4. [Google Scholar]

- Wong, Y.; Lin, W.; Tsai, J.; Huang, T. A 50-to-62GHz wide-locking-range CMOS injection-locked frequency divider with transformer feedback. In Proceedings of the 2008 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA, 15–17 June 2008; pp. 435–538. [Google Scholar]

- Wang, Y.; Ma, K.; Mahalingam, N.; Yeo, K.S. A delta-sigma fractional-N frequency divider for a Phase Lock Loop in 60GHz transceiver. In Proceedings of the 2011 IEEE International Conference of Electron Devices and Solid-State Circuits, Tianjin, China, 17–18 November 2011; pp. 1–2. [Google Scholar]

- Siriburanon, T.; Kondo, S.; Katsuragi, M.; Liu, H.; Kimura, K.; Deng, W.; Okada, K.; Matsuzawa, A. A Low-Power Low-Noise mm-Wave Subsampling PLL Using Dual-Step-Mixing ILFD and Tail-Coupling Quadrature Injection-Locked Oscillator for IEEE 802.11ad. IEEE J. Solid-State Circuits 2016, 51, 1246–1260. [Google Scholar] [CrossRef]

- Pang, J.; Wu, R.; Wang, Y.; Dome, M.; Kato, H.; Huang, H.; Narayanan, A.T.; Liu, H.; Liu, B.; Nakamura, T.; et al. A 28-GHz CMOS Phased-Array Transceiver Based on LO Phase-Shifting Architecture With Gain Invariant Phase Tuning for 5G New Radio. IEEE J. Solid-State Circuits 2019, 54, 1228–1242. [Google Scholar] [CrossRef]

- Mitomo, T.; Tsutsumi, Y.; Hoshino, H.; Hosoya, M.; Wang, T.; Tsubouchi, Y.; Tachibana, R.; Sai, A.; Kobayashi, Y.; Kurose, D.; et al. A 2-Gb/s throughput CMOS transceiver chipset with in-package antenna for 60-GHz short-range wireless communication. IEEE J. Solid-State Circuits 2012, 43, 3171–3460. [Google Scholar] [CrossRef]

- Sadhu, B.; Valdes-Garcia, A.; Plouchart, J.-O.; Ainspan, H.; Gupta, A.K.; Ferriss, M.; Yeck, M.; Sanduleanu, M.; Gu, X.; Baks, C.W.; et al. A 250-mW 60-GHz CMOS Transceiver SoC Integrated With a Four-Element AiP Providing Broad Angular Link Coverage. IEEE J. Solid-State Circuits 2020, 55, 1516–1529. [Google Scholar] [CrossRef]

- Li, L.; Niu, X.; Chen, L.; Yuan, C.; Tao, Z.; Jun, S.; Aili, W.; Ying, L.; Long, H.; Depeng, C.; et al. Design of 60 GHz RF Transceiver in CMOS: Challenges and Recent Advances. China Commun 2014, 11, 32–41. [Google Scholar]

- Shekhar, S.; Walling, J.S.; Allstot, D.J. Bandwidth Extension Techniques for CMOS Amplifiers. IEEE J. Solid-State Circuits 2006, 41, 2424–2439. [Google Scholar] [CrossRef]

- Fu, Y.; Li, L.; Wang, D.; Wang, X.; He, L. 28-GHz CMOS VCO With Capacitive Splitting and Transformer Feedback Techniques for 5G Communication. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 2088–2095. [Google Scholar] [CrossRef]

- Katayama, K.; Amakawa, S.; Takano, K.; Fujishima, M. Parasitic conscious 54 GHz divide-by-4 injection-locked frequency divider. In Proceedings of the 2015 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Senda, Japan, 26–28 August 2014; pp. 1–3. [Google Scholar]

- Chen, Z.; Wang, M.; Chen, J.; Liang, W.-F.; Yan, P.-P.; Zhai, J.F.; Hong, W. Linear CMOS LC -VCO Based on Triple-Coupled Inductors and Its Application to 40-GHz Phase-Locked Loop. IEEE Trans. Microw. Theory Tech 2017, 65, 2977–2989. [Google Scholar] [CrossRef]

- Yi, X.; Boon, C.C.; Liu, H.; Lin, J.F.; Lim, W.M. A 57.9-to-68.3 GHz 24.6 mW Frequency Synthesizer With In-Phase Injection-Coupled QVCO in 65 nm CMOS Technology. IEEE J. Solid-State Circuits 2014, 49, 347–359. [Google Scholar] [CrossRef]

- Abbas, W.; Mehmood, Z.; Seo, M. A V-Band Phase-Locked Loop with a Novel Phase-Frequency Detector in 65 nm CMOS. Electronics 2020, 9, 1502. [Google Scholar] [CrossRef]

| References | [19] | [20] | [18] | This Work |

|---|---|---|---|---|

| 65 nm | 28 nm | 65 nm | 65 nm | |

| Oscillation Frequency (GHz) | 51.9–67.3 | 27.3–31.2 | 28.6–36.2 | 45.2–52.6 |

| Tuning Range (GHz) | 16.4 | 14 | 23.5 | 15.1 |

| PN@1MHz (dBc/Hz) | −80 | −106 | −103 | −99 |

| Power consumption (mW) | 5.4 | 11.6 | 4.6 | 5 |

| FOM | −168 | −184 | −186.2 | −186.4 |

| Core Aera (mm2) | 0.03 | 0.064 | 0.12 | 0.018 |

| References | [21] | [22] | [31] | This Work |

|---|---|---|---|---|

| Technology | 65 nm | 130 nm | 65 nm | 65 nm |

| Architecture | ILFD | ILFD | ILFD | CML |

| Operation Frequency (GHz) | 60.8–67 | 49.8–62.0 | 53.9–54.2 | 38–54 |

| Locking Range | 6.2 | 12.2 | 0.8 | 16 |

| Power Consumption (mW) | 6.3 | 10.8 | 21 | 14 |

| Core Area (mm²) | 0.058 | <0.32 | 0.005 | 0.008 |

| Sub-bands Tuning Needed | Yes | No | No | No |

| Channel 1 | Channel 2 | Channel 3 | Channel 4 | |

|---|---|---|---|---|

| Frequency (GHz) | 46.656 | 48.384 | 50.112 | 51.84 |

| Int.PN (dBc) | −29.4 | −29 | −29.2 | −28.8 |

| Int.PN (Degree) | 2.7 | 2.9 | 2.8 | 2.9 |

| RMS Jitter (fs) | 163 | 165 | 155 | 157 |

| PN@1MHz (dBc/Hz) | −93.7 | −93.8 | −92.8 | −92.3 |

| Spur (dBc) | −63 | −65 | −64 | −62 |

| Power consumption (mW) | 75 | 77 | 78 | 80 |

| References | [7] | [8] | [15] | [24] | [32] | [33] | [34] | This Work |

|---|---|---|---|---|---|---|---|---|

| Topology | ADPLL | ADPLL | SSPLL | SSPLL + QILO | PLL + Doubler | CP PLL + QVCO | CP PLL | CP PLL |

| Technology | 65 nm | 65 nm GP | 45 nm | 65 nm | 90 nm | 65 nm | 65 nm LP | 65 nm LP |

| Locking range (GHz) | 56.4–63 (11.6%) | 50–66.5 (28%) | 33.6–36 (6.9%) | 55.6–65 (15.9%) | 38.6–45 (14.3%) | 57.9–68 (16.5%) | 65–67.4 (1.6%) | 45.2–52.56 (15%) |

| Fref (MHz) | 100 | 100 | 80 | 36/40 | 33.75 | 135 | 515 | 108 |

| In-band PN (dBc/Hz) | −75 | −79–−83 | -- | −78.5 | −82.5 | −91–−84 | -- | <−90 |

| PN@1MHz (dBc/Hz) | −90 | −88–−93 | −94.9 | 92 | <−80 | −89.8 | −84.4 | <−92 |

| RMS jitter (fs) | 590.2 | 223–261 | 251 | 290 | -- | 238 | -- | 155–165 |

| Spur (dBc) | −74 | −59–−68 | <−60 | −73 | −46 | −54 | -- | <−60 |

| Area (mm2) | 0.48 | 0.45 | 0.41 | 1.08 | 1.38 | 0.19 | 0.37 | <0.72 |

| Power consumption (mW) | 48 | 46 | 20.6 | 32 | 76 | 24.6 | 88 | 80 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Niu, X.; Wu, X.; Li, L.; He, L.; Cheng, D.; Wang, D. A 48 GHz Fundamental Frequency PLL with Quadrature Clock Generation for 60 GHz Transceiver. Electronics 2022, 11, 415. https://doi.org/10.3390/electronics11030415

Niu X, Wu X, Li L, He L, Cheng D, Wang D. A 48 GHz Fundamental Frequency PLL with Quadrature Clock Generation for 60 GHz Transceiver. Electronics. 2022; 11(3):415. https://doi.org/10.3390/electronics11030415

Chicago/Turabian StyleNiu, Xiaokang, Xu Wu, Lianming Li, Long He, Depeng Cheng, and Dongming Wang. 2022. "A 48 GHz Fundamental Frequency PLL with Quadrature Clock Generation for 60 GHz Transceiver" Electronics 11, no. 3: 415. https://doi.org/10.3390/electronics11030415

APA StyleNiu, X., Wu, X., Li, L., He, L., Cheng, D., & Wang, D. (2022). A 48 GHz Fundamental Frequency PLL with Quadrature Clock Generation for 60 GHz Transceiver. Electronics, 11(3), 415. https://doi.org/10.3390/electronics11030415