A 1.25 MHz, 108 dB Chopped Sampling-Mixer-Based Impedance Spectroscopy SoC in 0.18-

Abstract

1. Introduction

2. Sampling-Mixer-Based Impedance Spectroscopy

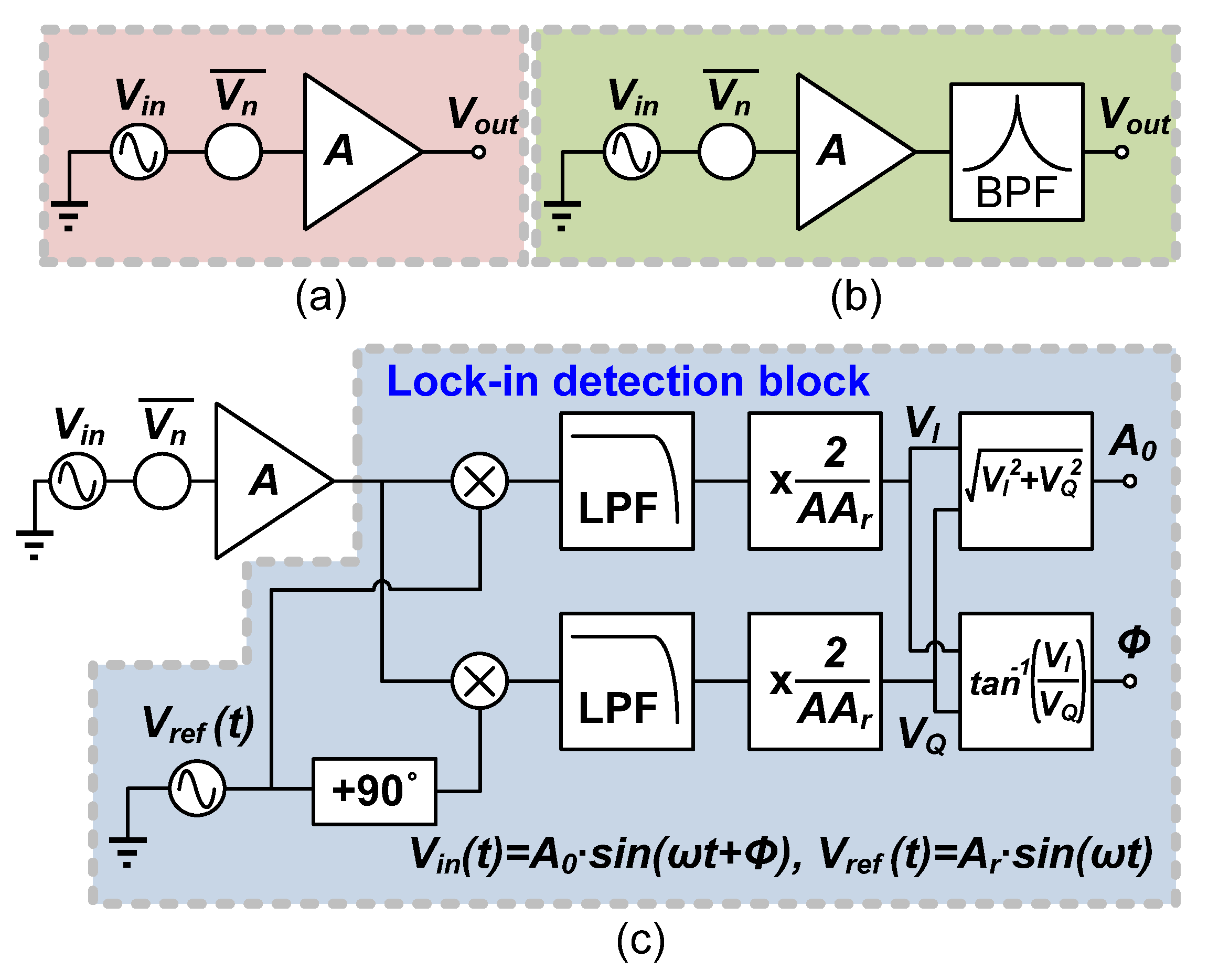

2.1. Review of Lock-In Detection Theory

2.2. Sampling-Mixer-Based Impedance Measurement

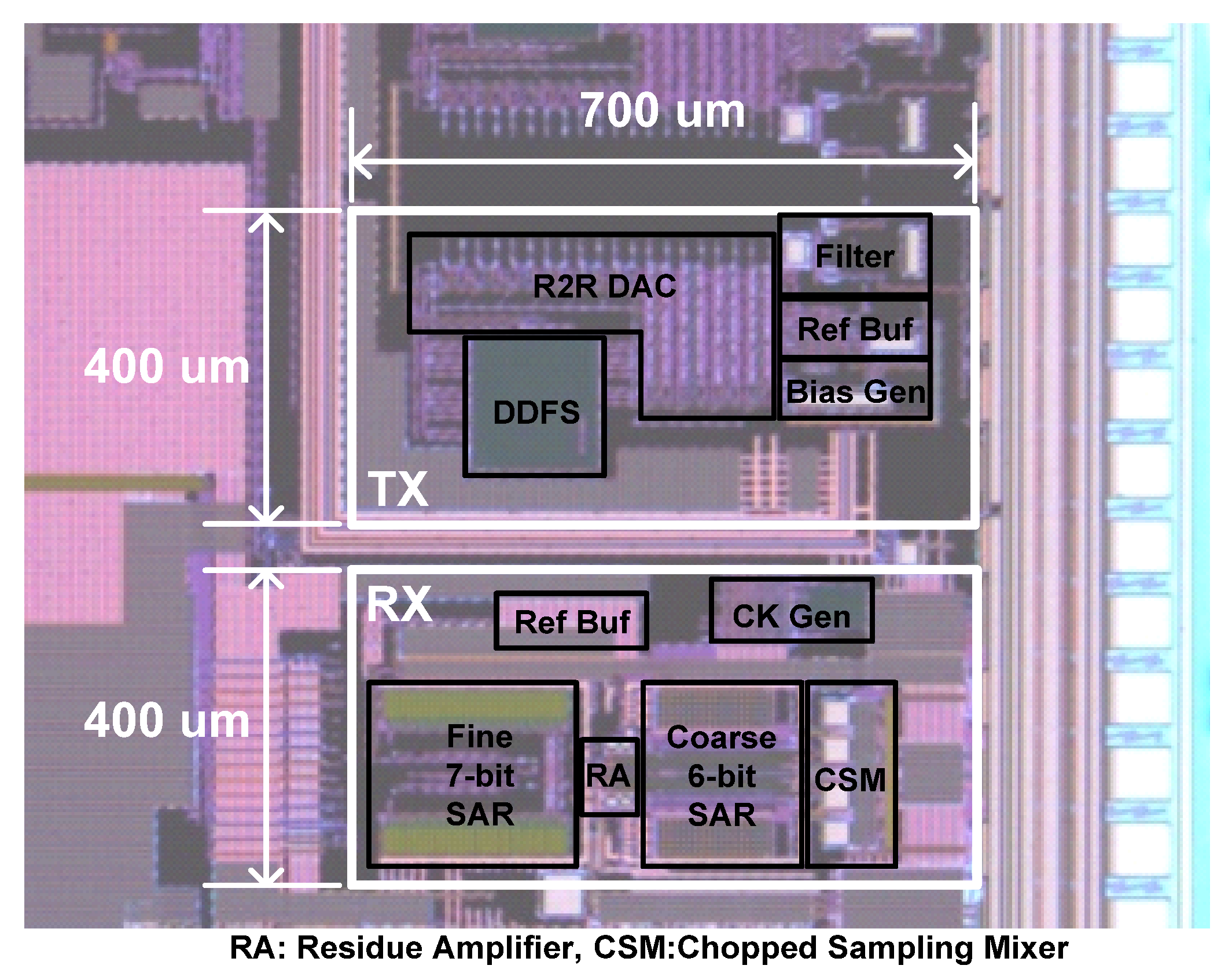

3. EIS Architecture and Implementation

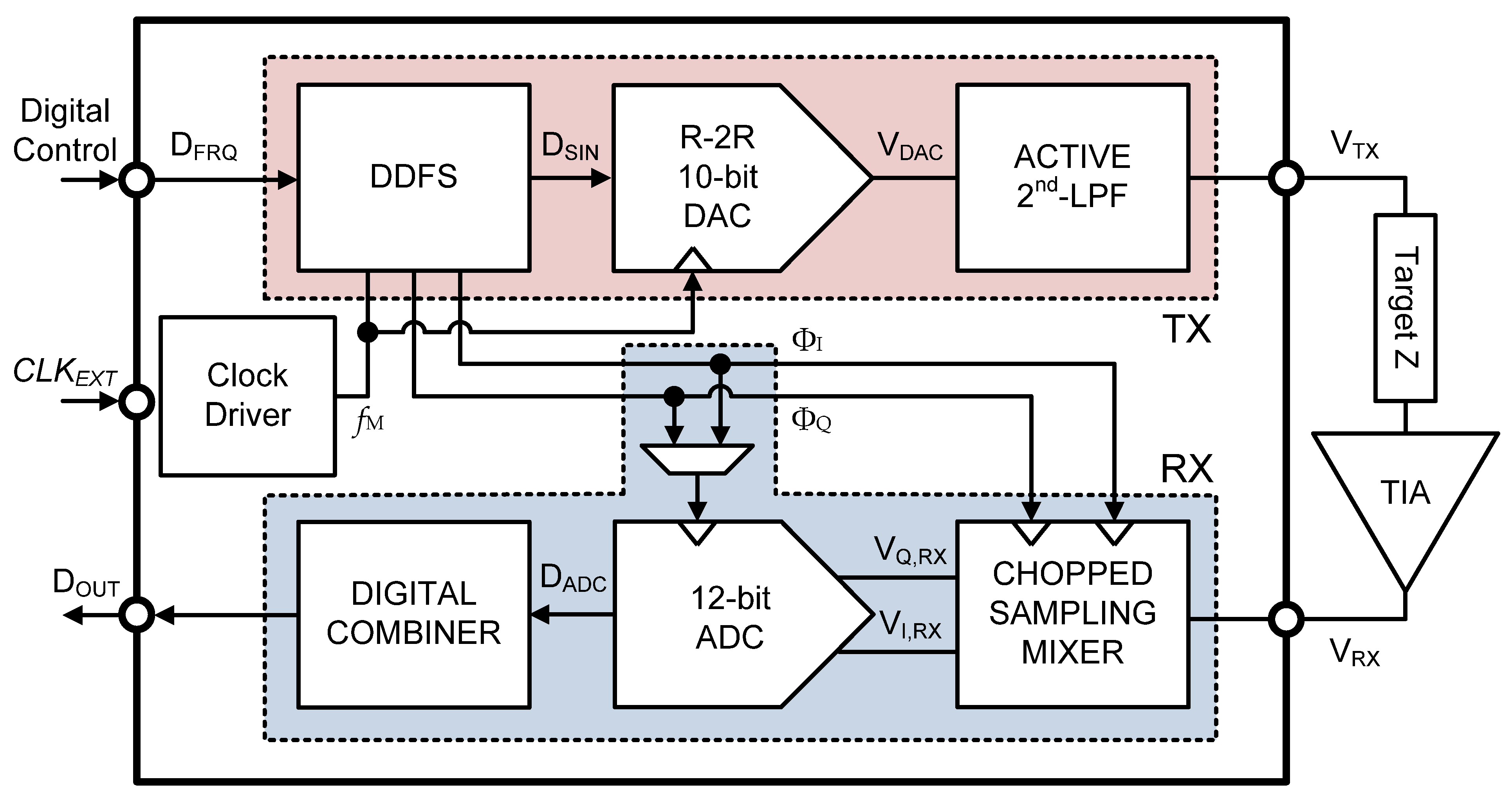

3.1. EIS Architecture Overview

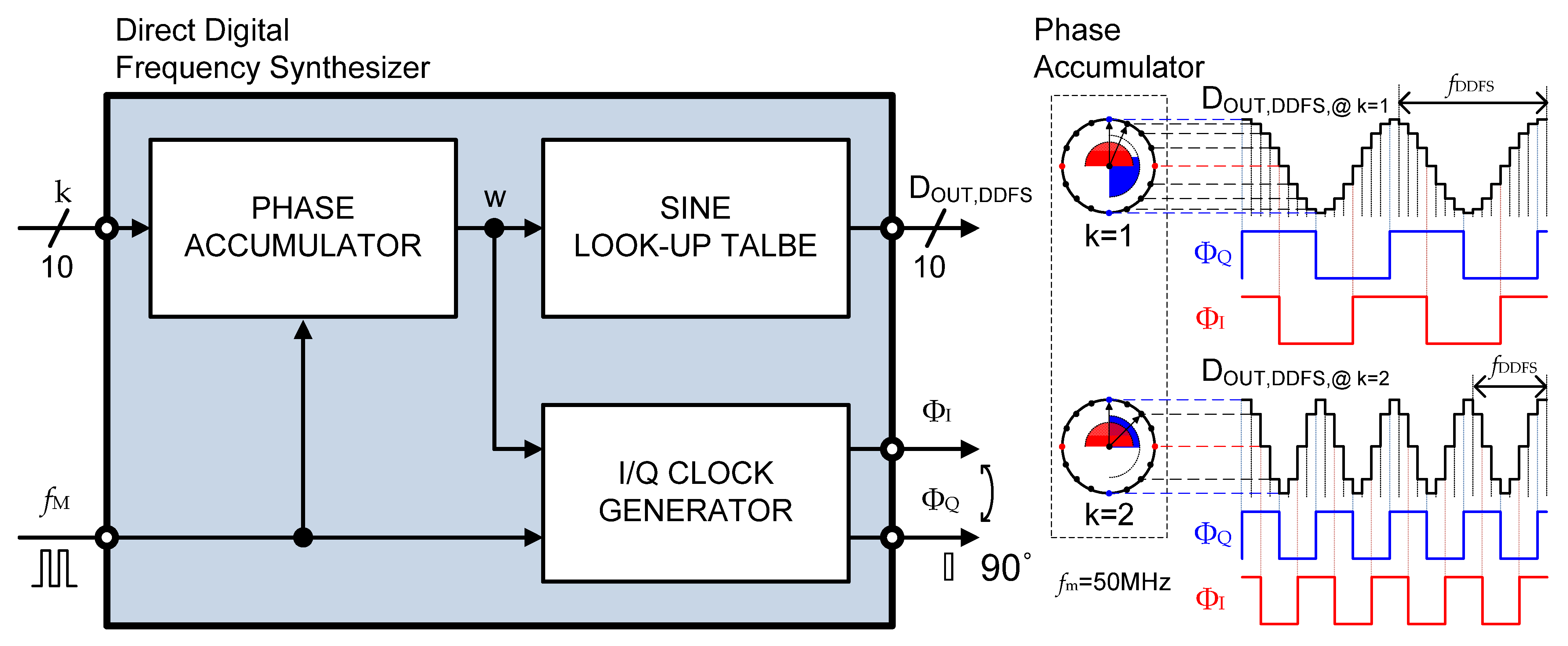

3.2. DDFS Implementation

3.3. EIS Receiver

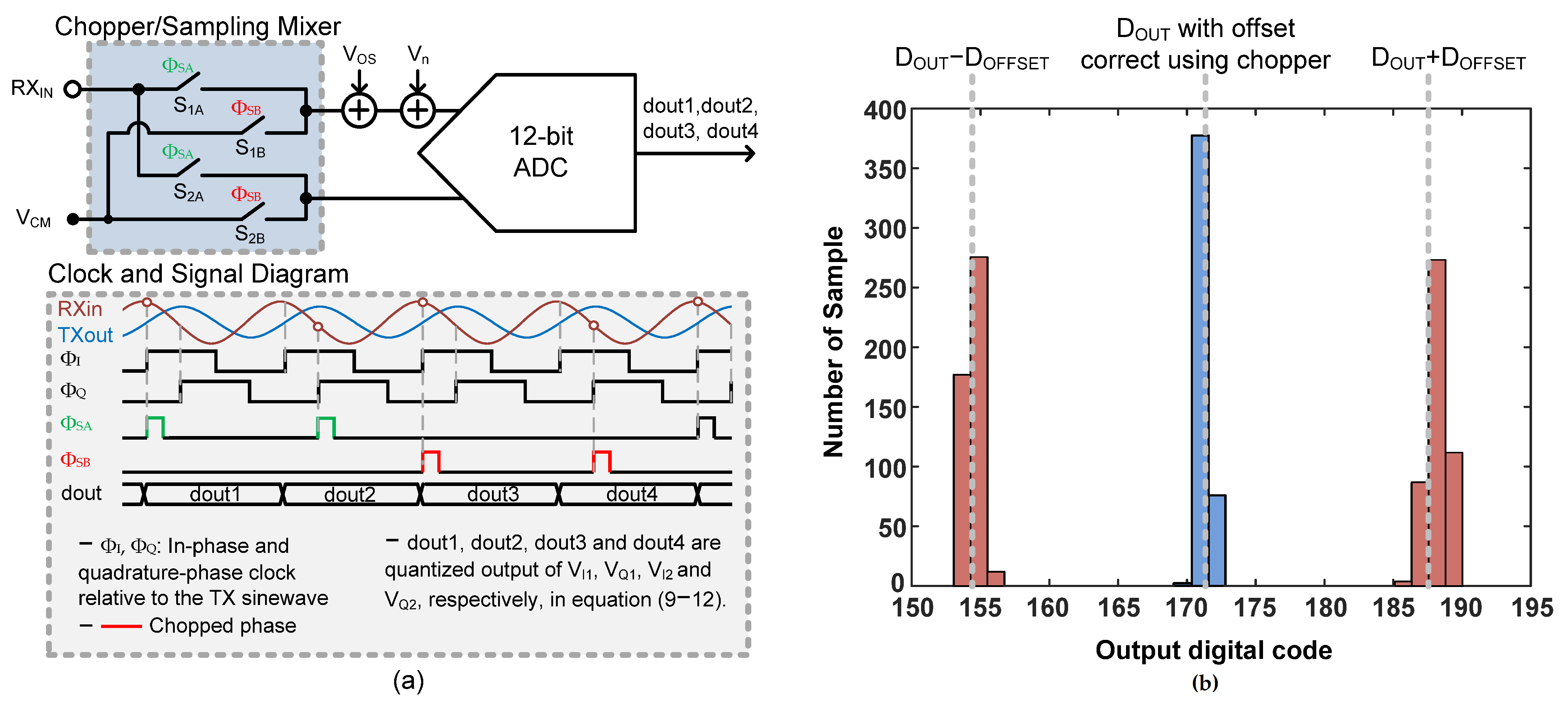

3.3.1. Chopped Sampling Mixer

3.3.2. A 12-Bit 2-Stage Pipelined SAR ADC

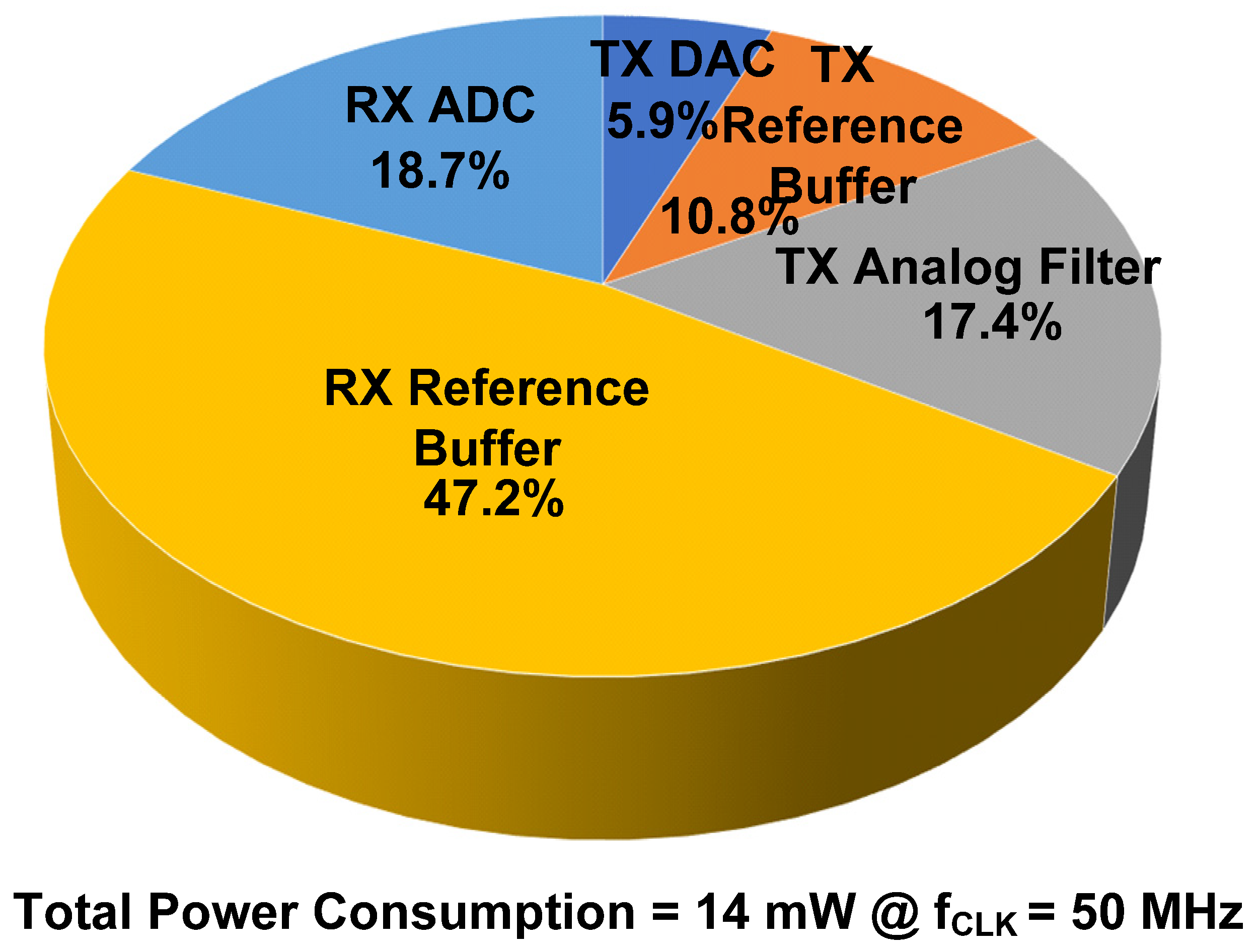

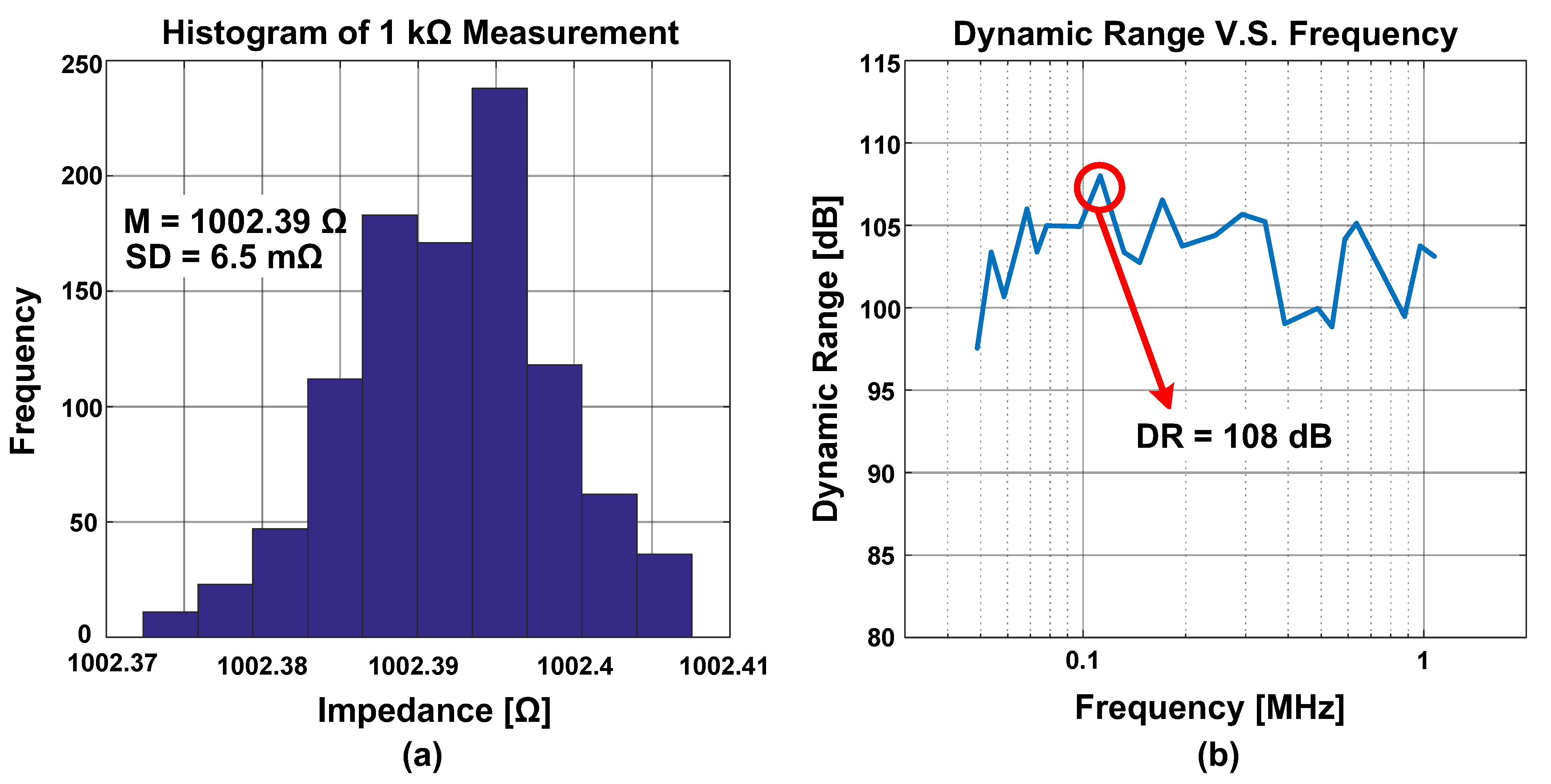

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Appendix A

References

- Qu, G.; Wang, H.; Zhao, Y.; O’Donnell, J.; Lyden, C.; Liu, Y.; Ding, J.; Dempsey, D.; Chen, L.; Bourke, D.; et al. A 0.28 mΩ-Sensitivity 105 dB-Dynamic-Range Electrochemical Impedance Spectroscopy SoC for Electrochemical Gas Detection. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 286–288. [Google Scholar]

- Chen, C.H.; Liu, J.; Amine, K. Symmetric cell approach and impedance spectroscopy of high power lithium-ion batteries. J. Power Sources 2001, 96, 321–328. [Google Scholar] [CrossRef]

- Fosbøl, M.Ø.; Zerahn, B. Contemporary methods of body composition measurement. Clin. Physiol. Funct. Imaging 2015, 35, 81–97. [Google Scholar] [CrossRef] [PubMed]

- Hafid, A.; Benouar, S.; Kedir-Talha, M.; Abtahi, F.; Attari, M.; Seoane, F. Full Impedance Cardiography measurement device using Raspberry PI3 and System-on-Chip biomedical Instrumentation Solutions. IEEE J. Biomed Health Inform. 2018, 22, 1883–1894. [Google Scholar] [CrossRef] [PubMed]

- Kim, M.; Kim, H.; Jang, J.; Lee, J.; Lee, K.; Kim, K.; Lee, Y.; Yoo, H.J. A 1.4 mΩ-sensitivity 94 dB-dynamic-range electrical impedance tomography SoC and 48-channel Hub SoC for 3D lung ventilation monitoring system. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 354–355. [Google Scholar]

- Lopez, C.M.; Chun, H.S.; Berti, L.; Wang, S.; Putzeys, J.; Bulcke, C.V.D.; Weijers, J.W.; Firrincieli, A.; Reumers, V.; Braeken, D.; et al. A 16384-Electrode 1024-Channel Multimodal CMOS MEA for High-Throughput Intracellular Action Potential Measurements and Impedance Spectroscopy in Drug-Screening Applications. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 464–466. [Google Scholar]

- Manickam, A.; Singh, R.; McDermott, M.W.; Wood, N.; Bolouki, S.; Naraghi-Arani, P.; Jhonson, K.A.; Kuimelis, R.G.; Schoolnik, G.; Hassibi, A. A Fully Integrated CMOS Fluorescence Biochip for DNA and RNA Testing. IEEE J. Solid-State Circuits 2017, 52, 2857–2870. [Google Scholar] [CrossRef] [PubMed]

- Velmanickam, L.; Pokharel, R.; Lima, I.T.; Nawarathna, D. Label Free MicroRNA Biomarker Detection in Serum Samples for Diagnosis Applications at Point-of Care. In Proceedings of the 2019 IEEE Research and Applications of Photonics in Defense Conference (RAPID), Miramar Beach, FL, USA, 19–21 August 2019; pp. 1–4. [Google Scholar]

- Sui, J.; Gandotra, N.; Xie, P.; Lin, Z.; Scharfe, C.; Javanmard, M. Multi-frequency impedance sensing for detection and sizing of DNA fragments. Sci. Rep. 2021, 11, 6490. [Google Scholar] [CrossRef] [PubMed]

- Kim, Y.; Goo, S.-G.; Lim, J.S. Multi-Gas Analyzer Based on Tunable Filter Non-Dispersive Infrared Sensor: Application to the Monitoring of Eco-Friendly Gas Insulated Switchgears. Sensors 2022, 22, 8662. [Google Scholar] [CrossRef] [PubMed]

- Manickam, A.; Johnson, C.A.; Kavusi, S.; Hassibi, A. Interface Design for CMOS-Integrated Electrochemical Impedance Spectroscopy (EIS) Biosensors. Sensors 2012, 12, 14467–14488. [Google Scholar] [CrossRef] [PubMed]

- Masciotti, J.M.; Lasker, J.M.; Hielscher, A.H. Digital Lock-In Detection for Discriminating Multiple Modulation Frequencies With High Accuracy and Computational Efficiency. IEEE Trans. Instrum. Meas. 2008, 57, 182–189. [Google Scholar] [CrossRef]

- Pekau, H.; Haslett, J.W. A 2.4 GHz CMOS sub-sampling mixer with integrated filtering. IEEE J. Solid-State Circuits 2005, 40, 2159–2166. [Google Scholar] [CrossRef]

- Yoon, J.S.; Kim, J. An Efficient Digital-Domain Calibration Technique for SAR ADCs Using a Bridge Capacitor. J. Semicond. Technol. Sci. 2019, 19, 79–86. [Google Scholar] [CrossRef]

- Lee, C.C.; Flynn, M.P. A SAR-Assisted Two-Stage Pipeline ADC. IEEE J. Solid-State Circuits 2011, 46, 859–869. [Google Scholar] [CrossRef]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z. A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Kim, K.; Kim, J.H.; Gweon, S.; Kim, M.; Yoo, H.J. A 0.5-V Sub-10-μW 15.28-mΩ/√Hz Bio-Impedance Sensor IC With Sub-1° Phase Error. IEEE J. Solid-State Circuits 2020, 55, 2161–2173. [Google Scholar] [CrossRef]

| Features | This Work | ISSCC 18 [1] | ISSCC 17 [5] | ISSCC 18 [6] | JSSC 20 [17] |

|---|---|---|---|---|---|

| Technology | 180 nm | 180 nm | 65 nm | 130 nm | 65 nm |

| Dynamic Range | 108 dB | 105 dB | 94 dB | Unknown | 76.32 dB |

| Power | 14 mW | 20.6 mW | 6.69 mW | 95 mW | 9 mW |

| Operating Frequency Range | 1.25 MHz | 200 kHz | 128 kHz | 1 MHz | 408 kHz |

| Frequency Tunability | Tunable | Tunable | Tunable | N/A | Tunable |

| ADC Structure | 12-bit pipelined SAR | 16-bit SAR | 12-bit SAR | 10-bit SAR | Not included |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.; Lee, H.; Kim, J.

A 1.25 MHz, 108 dB Chopped Sampling-Mixer-Based Impedance Spectroscopy SoC in 0.18-

Kim H, Lee H, Kim J.

A 1.25 MHz, 108 dB Chopped Sampling-Mixer-Based Impedance Spectroscopy SoC in 0.18-

Kim, Hyeonsik, Heejune Lee, and Jintae Kim.

2022. "A 1.25 MHz, 108 dB Chopped Sampling-Mixer-Based Impedance Spectroscopy SoC in 0.18-

Kim, H., Lee, H., & Kim, J.

(2022). A 1.25 MHz, 108 dB Chopped Sampling-Mixer-Based Impedance Spectroscopy SoC in 0.18-