A Compact Model for Single-Event Transient in Fully Depleted Silicon on Insulator MOSFET Considering the Back-Gate Voltage Based on Time-Domain Components

Abstract

1. Introduction

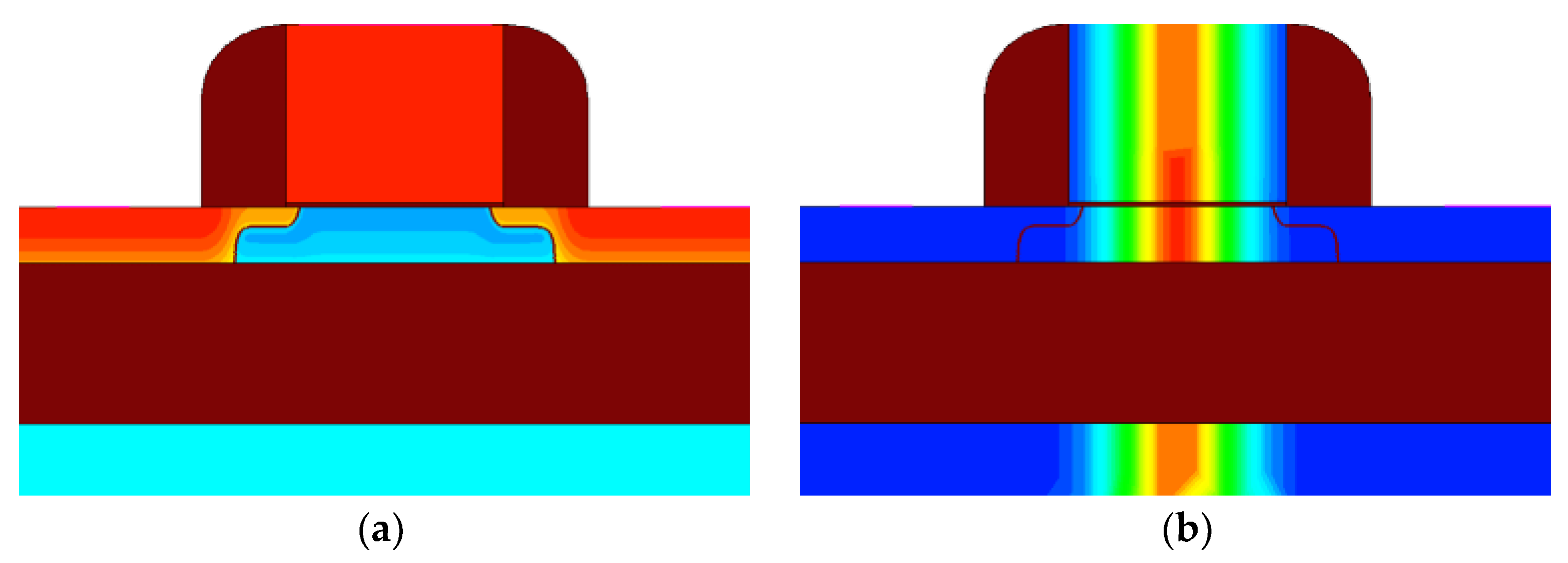

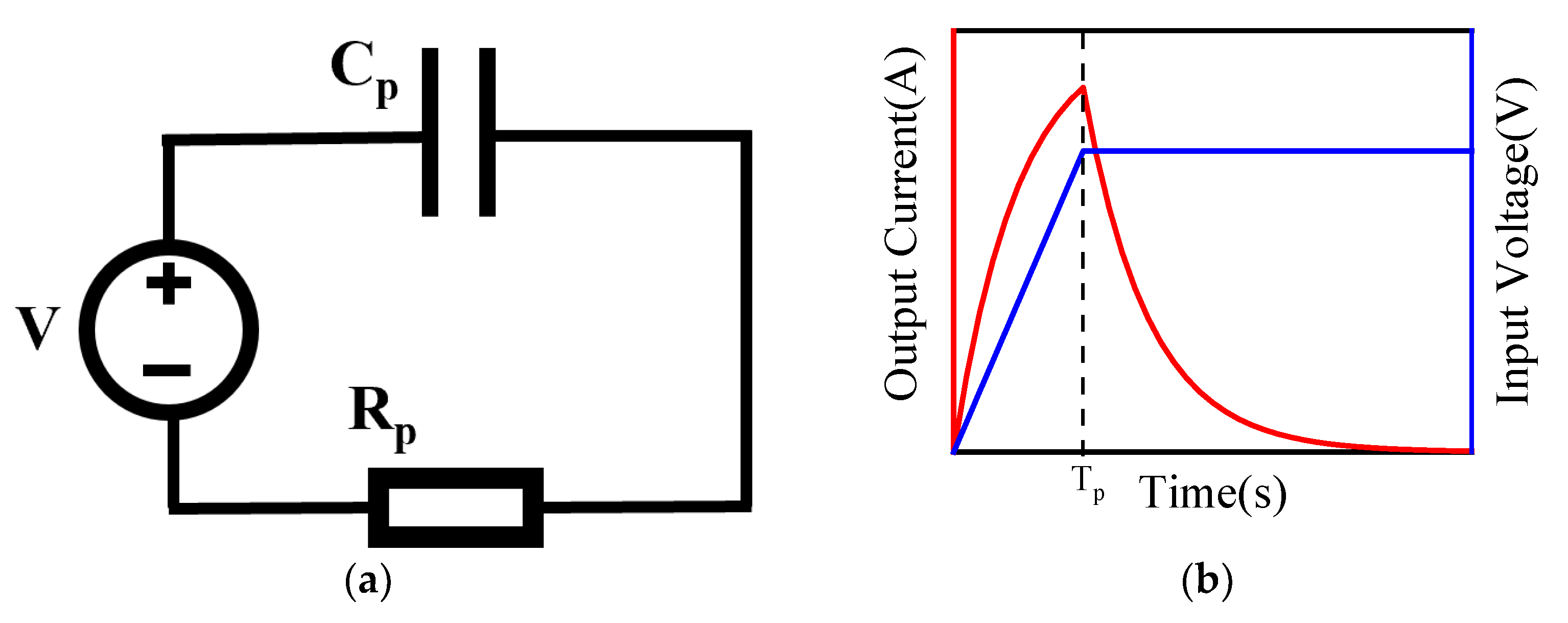

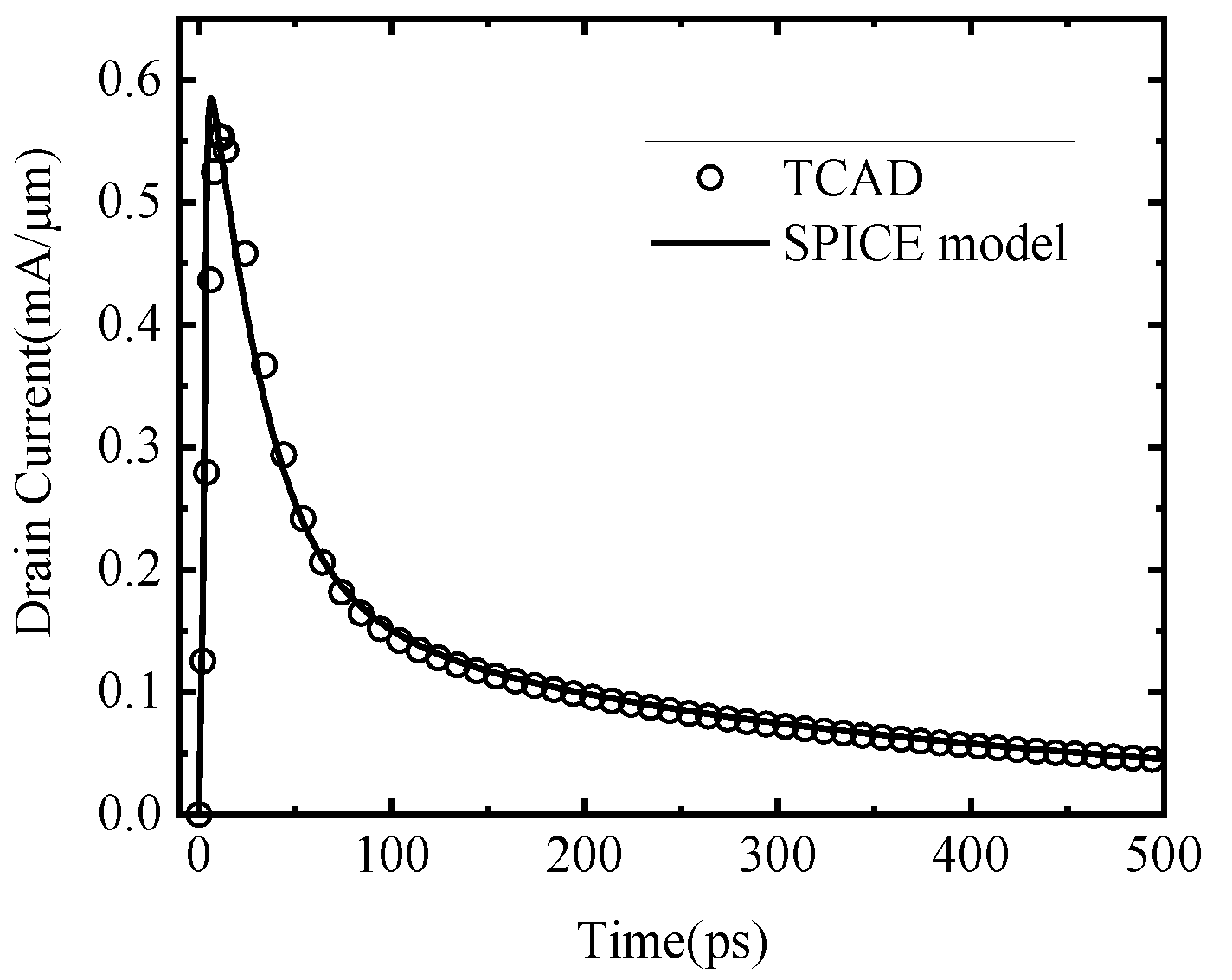

2. TCAD Simulation Details and Result Discussion

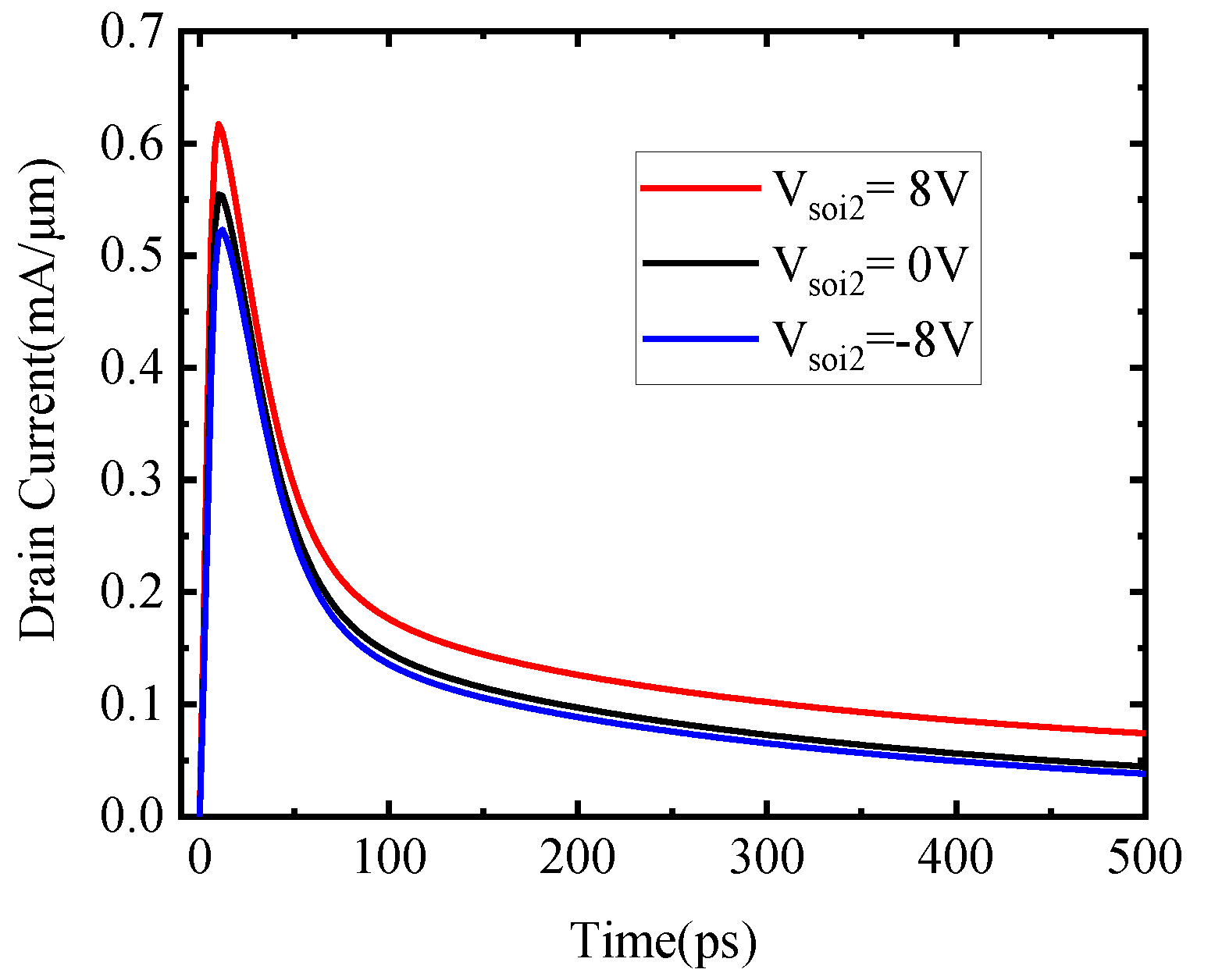

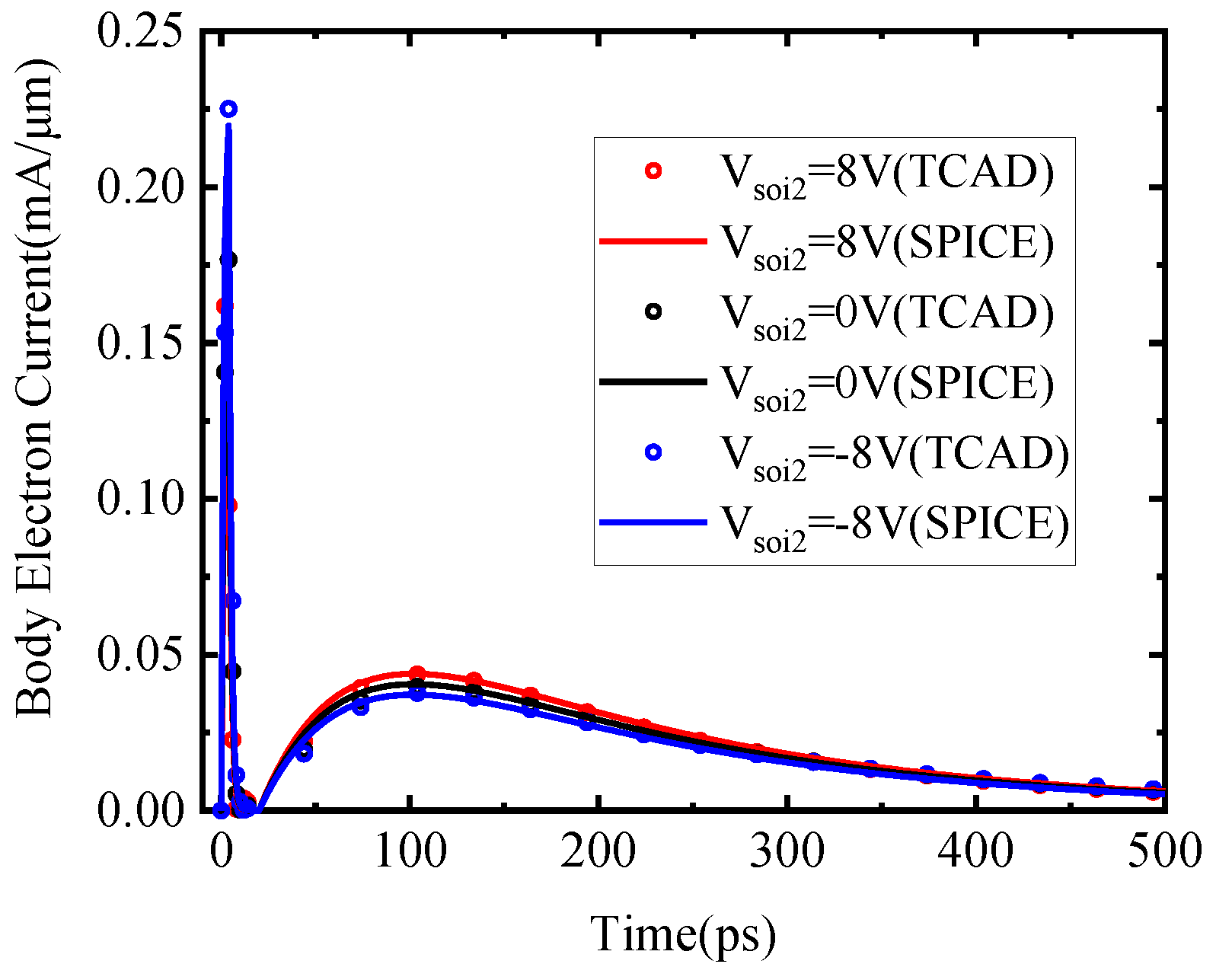

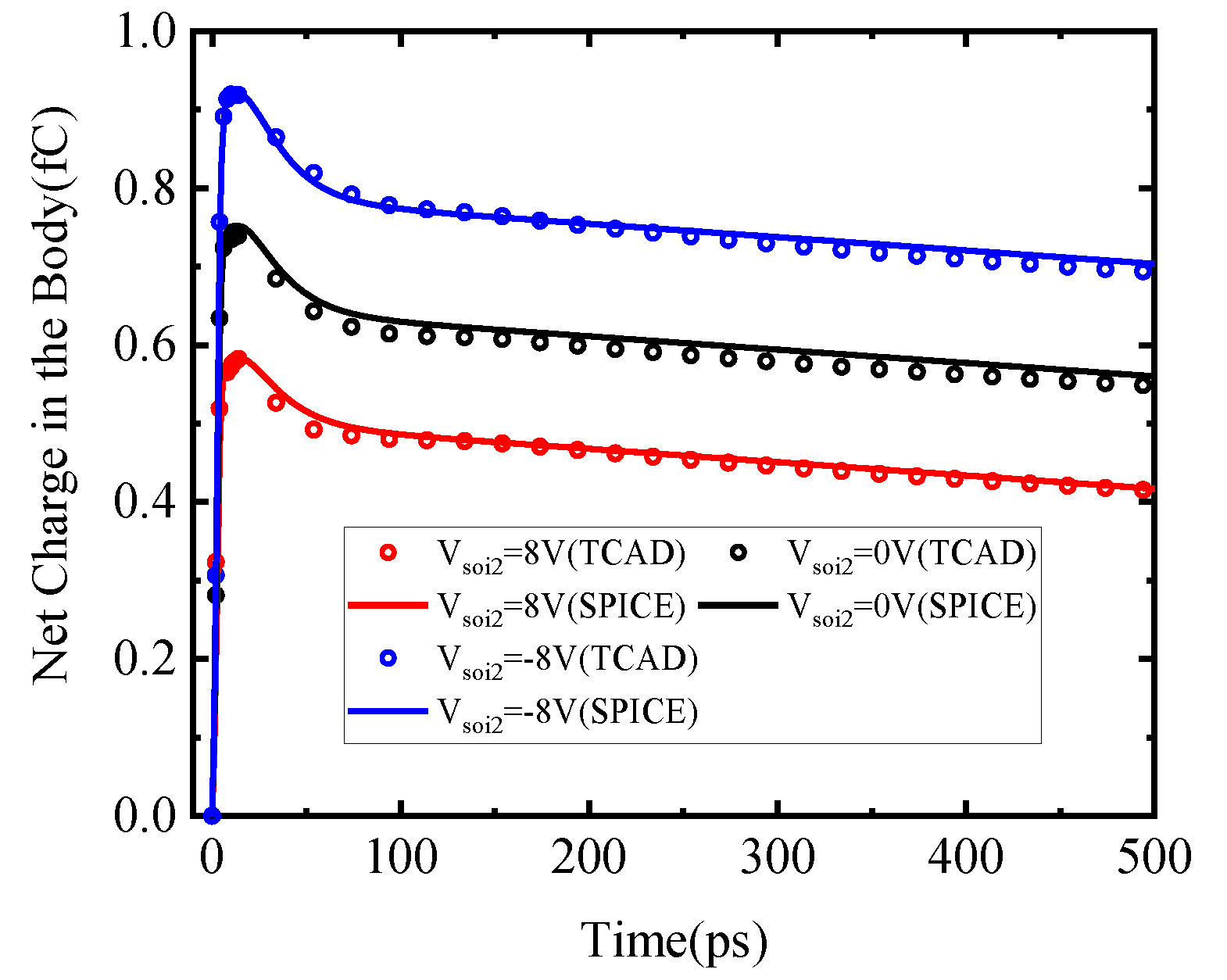

- -

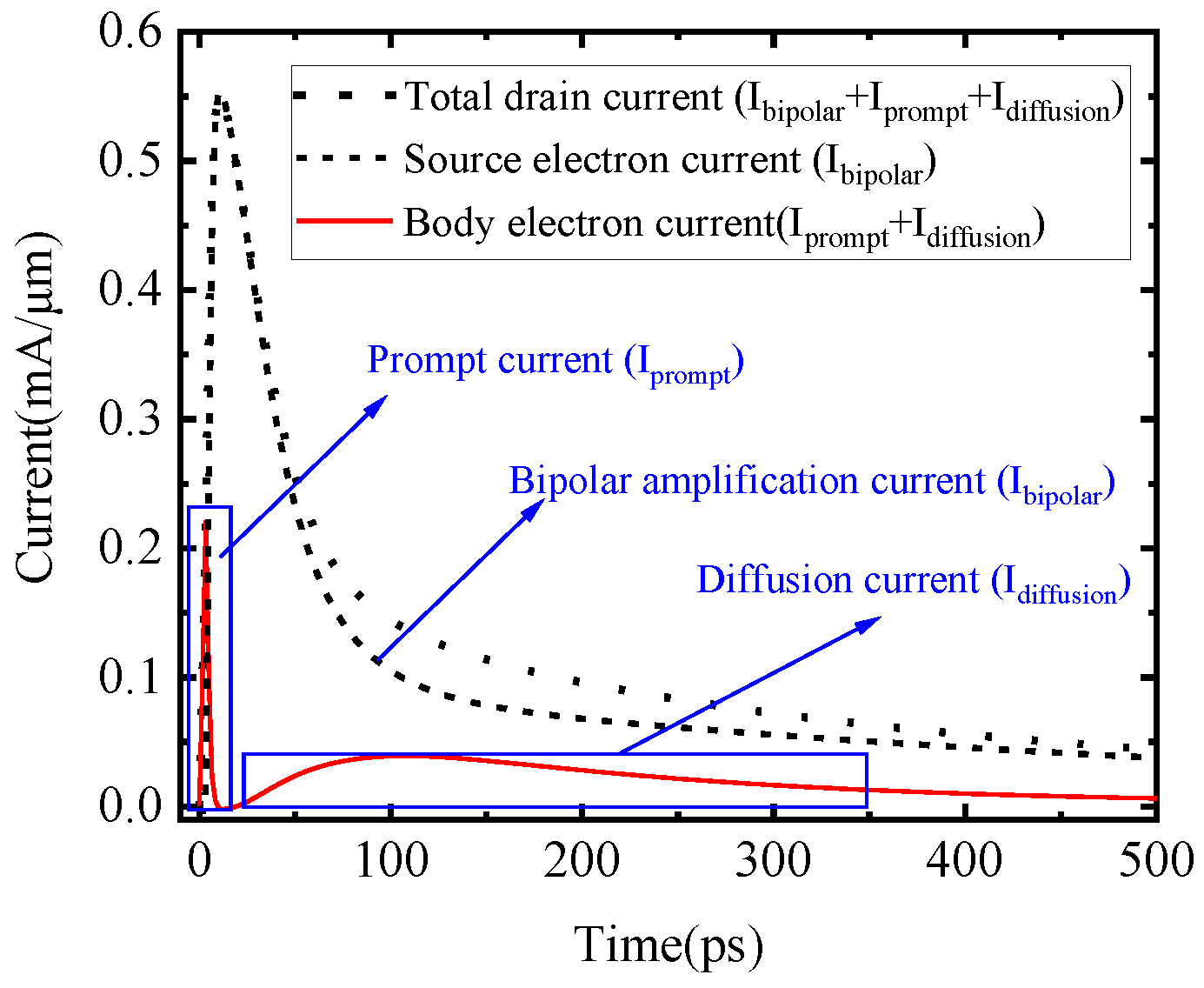

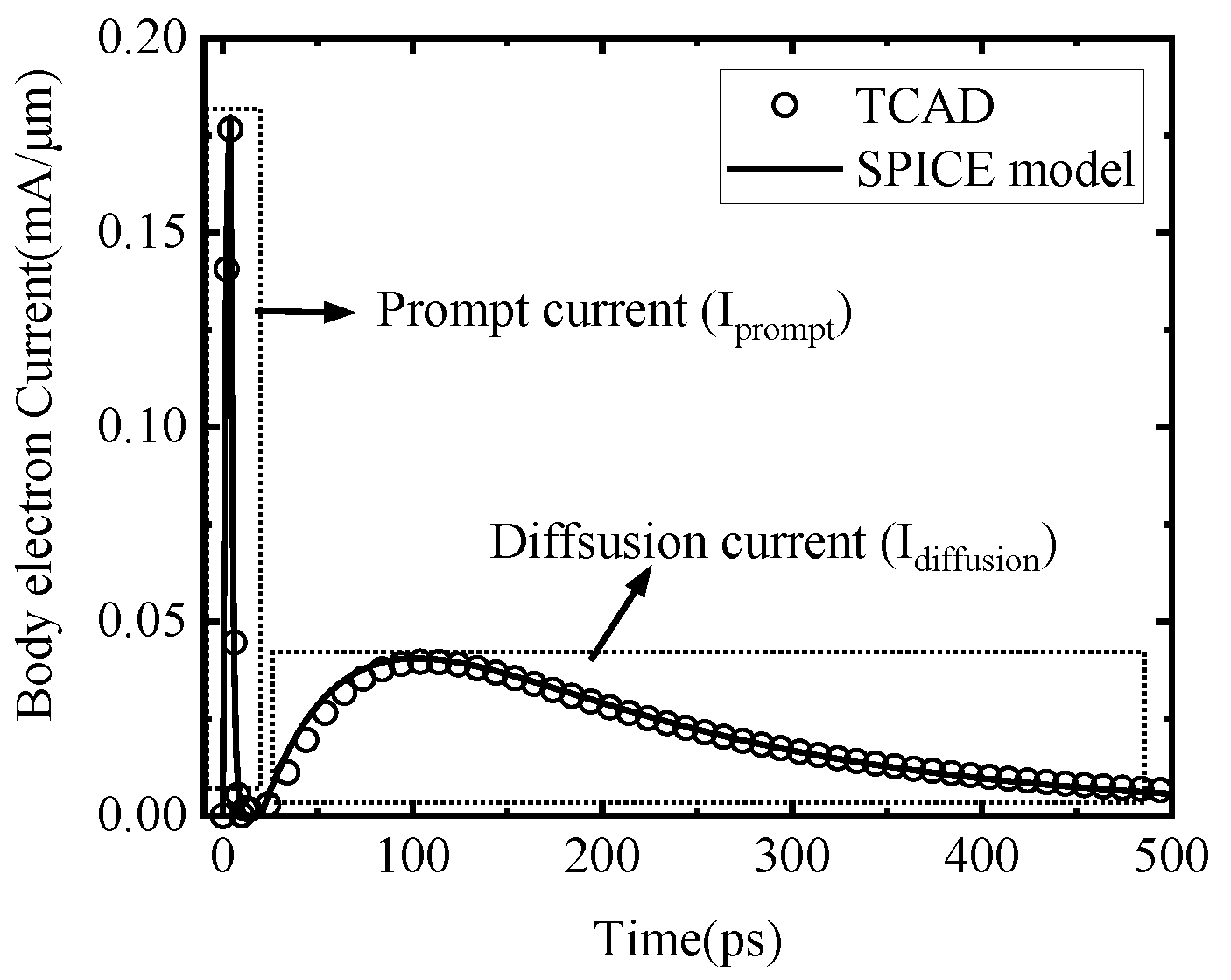

- The first one is the prompt current. This current is formed by the ionized electrons around the PN junction between the body and the drain leaving more holes than electrons in the body. This process will increase the body’s potential and cause the bipolar amplification effect;

- -

- The second one is the diffusion current formed by the diffusion of the ionized electrons that still remain in the body. The diffusion current of the ionized holes will be collected by the source. As carrier diffusion proceeds, the difference in concentration between ionized holes and electrons in the body decreases, and the bipolar amplification effect diminishes instantaneously;

- -

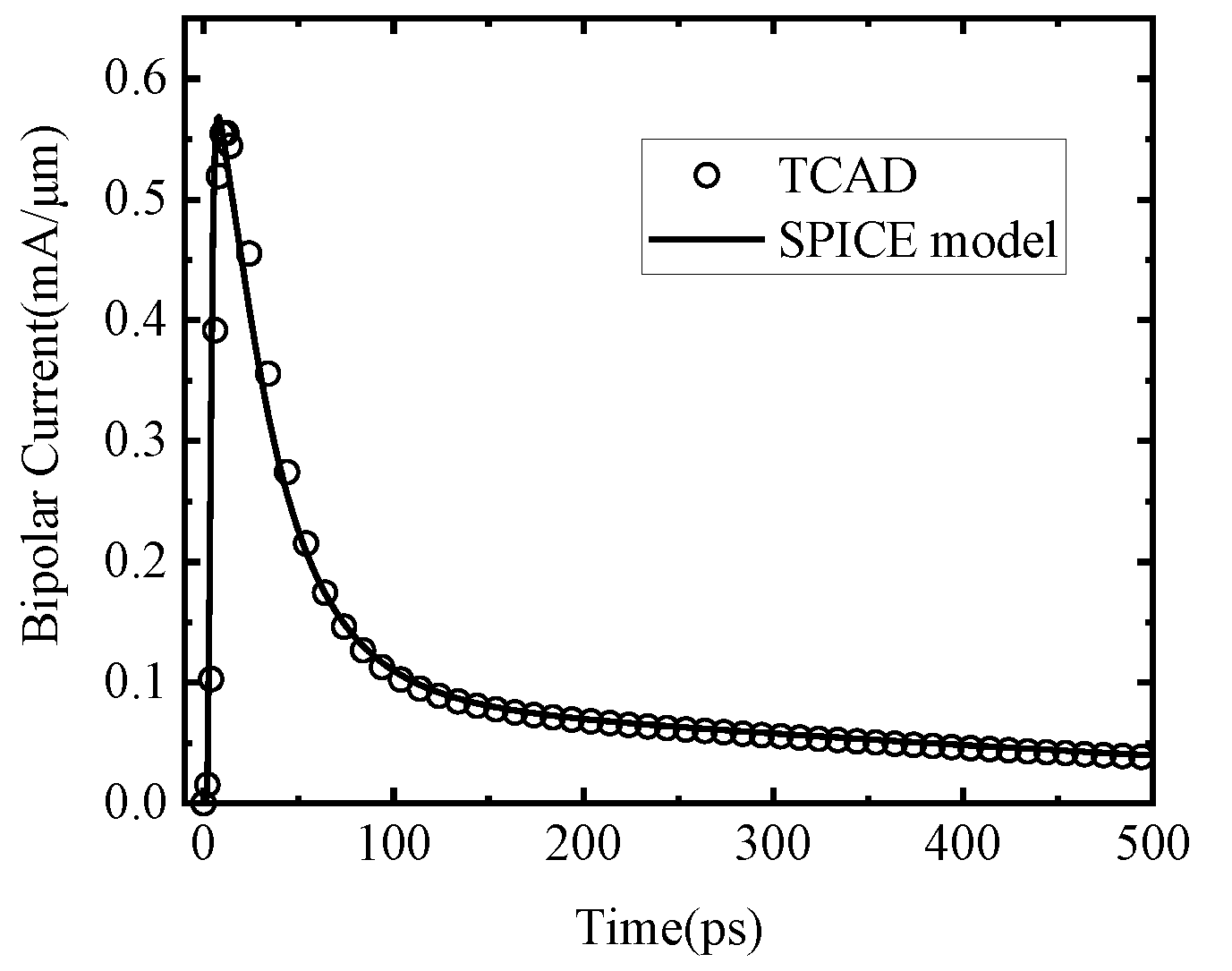

- The third one which is the largest part is the bipolar amplification current. It represents a drift current from the source to the drain caused by the BAE.

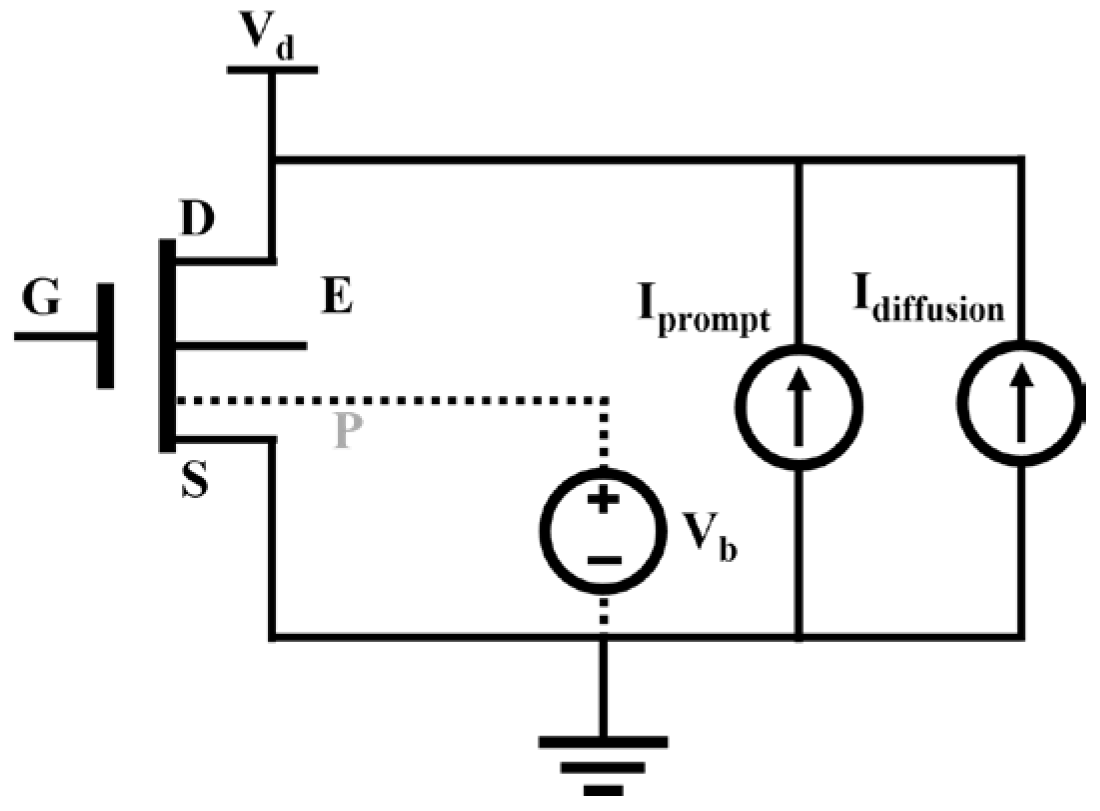

3. Modeling of SET Current

3.1. Modeling of Prompt Current

3.2. Modeling of Diffusion Current

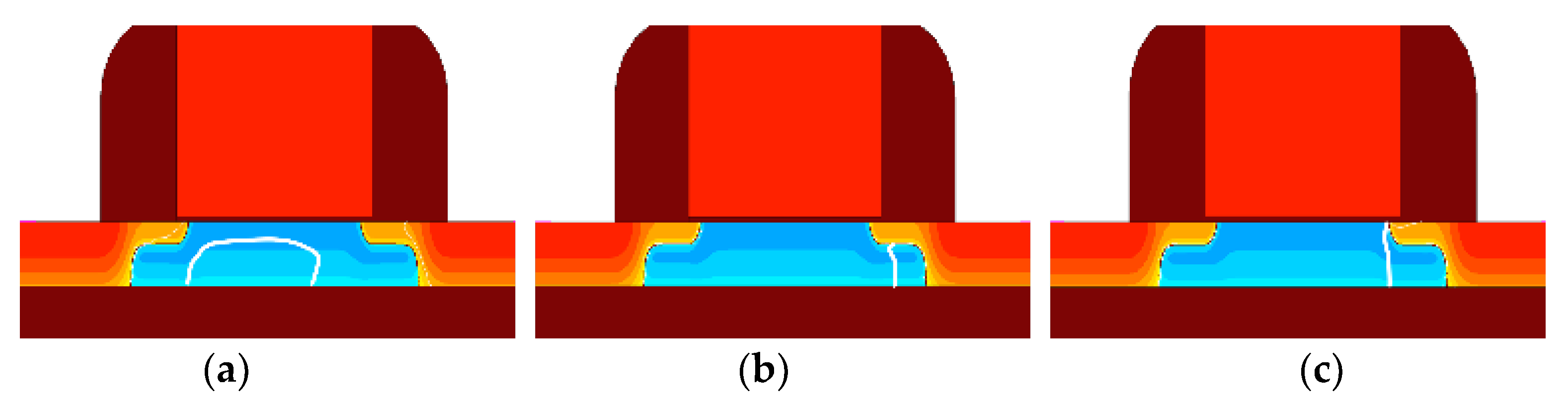

- (1)

- at the beginning, the cloud shape is Gaussian because of free diffusion;

- (2)

- the Gaussian distribution will be transformed to an approximately “linear” shape after the cloud collides with the source and the drain junction;

- (3)

- the “linear” cloud decays because of the discharge of the source hole current and the drain electron current [14].

3.3. Modeling of Bipolar Amplification Current

4. Model Considering the Back-Gate Voltage

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Hubert, G.; Artola, L.; Regis, D. Impact of scaling on the soft error sensitivity of bulk, FDSOI and FinFET technologies due to atmospheric radiation. Integration 2015, 50, 39–47. [Google Scholar] [CrossRef]

- Ebara, M.; Yamada, K.; Kojima, K.; Furuta, J.; Kobayashi, K. Process dependence of soft errors induced by alpha particles, heavy ions, and high energy neutrons on flip flops in FDSOI. IEEE J. Electron Devices Soc. 2019, 7, 817–824. [Google Scholar] [CrossRef]

- Ebara, M.; Yamada, K.; Kojima, K.; Tsukita, Y.; Furuta, J.; Kobayashi, K. Evaluation of soft-error tolerance by neutrons and heavy ions on flip flops with guard gates in a 65-nm thin BOX FDSOI process. IEEE Trans. Nucl. Sci. 2020, 67, 1470–1477. [Google Scholar] [CrossRef]

- Ferlet-Cavrois, V.; Marcandella, C.; Giraud, G.; Gasiot, G.; Colladant, T.; Musseau, O.; Fenouillet, C.; du Port de Poncharra, J. Characterization of the parasitic bipolar amplification in SOI technologies submitted to transient irradiation. IEEE Trans. Nucl. Sci. 2002, 49, 1456–1461. [Google Scholar] [CrossRef]

- Castellani-Coulié, K.; Munteanu, D.; Ferlet-Cavrois, V.; Autran, J.-L. Simulation analysis of the bipolar amplification in fully-depleted SOI technologies under heavy-ion irradiations. IEEE Trans. Nucl. Sci. 2005, 52, 1474–1479. [Google Scholar] [CrossRef]

- Liu, F.Y.; Ionica, I.; Bawedin, M.; Cristoloveanu, S. Parasitic bipolar effect in ultra-thin FD SOI MOSFETs. Solid-State Electron. 2015, 112, 29–36. [Google Scholar] [CrossRef]

- Liu, J.; Qin, Y.; Li, T.; Wang, Y.; Yang, W.; Liu, J.; Li, R. Using VerilogA for modeling of Single Event current pulse: Implementation and application. In Proceedings of the 2017 China Semiconductor Technology International Conference (CSTIC), Shanghai, China, 12–13 March 2017; IEEE: New York, NY, USA, 2017; pp. 1–3. [Google Scholar]

- Wang, J.; Lin, F.; Wang, D.; Song, W.; Liu, L.; Song, Q.; Chen, L. Collection of charge in NMOS from single event effect. IEICE Electron. Express 2016, 13, 1–8. [Google Scholar] [CrossRef][Green Version]

- Black, D.A.; Robinson, W.H.; Wilcox, I.Z.; Limbrick, D.B.; Black, J.D. Modeling of single event transients with dual double-exponential current sources: Implications for logic cell characterization. IEEE Trans. Nucl. Sci. 2015, 62, 1540–1549. [Google Scholar] [CrossRef]

- Loveless, T.D.; Kauppila, J.S.; Jagannathan, S.; Ball, D.R.; Rowe, J.D.; Gaspard, N.J.; Atkinson, N.M.; Blaine, R.W.; Reece, T.R.; Ahlbin, J.R.; et al. On-chip measurement of single-event transients in a 45 nm silicon-on-insulator technology. IEEE Trans. Nucl. Sci. 2012, 59, 2748–2755. [Google Scholar] [CrossRef]

- DasGupta, S.; Witulski, A.F.; Bhuva, B.L.; Alles, M.L.; Reed, R.A.; Amusan, O.A.; Ahlbin, J.R.; Schrimpf, R.D.; Massengill, L.W. Effect of well and substrate potential modulation on single event pulse shape in deep submicron CMOS. IEEE Trans. Nucl. Sci. 2007, 54, 2407–2412. [Google Scholar] [CrossRef]

- Messenger G, C. Collection of charge on junction nodes from ion tracks. IEEE Trans. Nucl. Sci. 1982, 29, 2024–2031. [Google Scholar] [CrossRef]

- Kobayashi, D.; Aimi, M.; Saito, H.; Hirose, K. Time-domain component analysis of heavy-ion-induced transient currents in fully-depleted SOI MOSFETs. IEEE Trans. Nucl. Sci. 2006, 53, 3372–3378. [Google Scholar] [CrossRef]

- Fulkerson, D.E.; Liu, H. A charge-control SPICE engineering model for the parasitic bipolar transistor action in SOI CMOS single-event upsets. IEEE Trans. Nucl. Sci. 2004, 51, 275–287. [Google Scholar] [CrossRef]

- Rostand, N.; Martinie, S.; Lacord, J.; Rozeau, O.; Poiroux, T.; Hubert, G. Single Event Transient Compact Model for FDSOI MOSFETs Taking Bipolar Amplification and Circuit Level Arbitrary Generation into Account. In Proceedings of the 2019 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Udine, Italy, 4–6 September 2019; IEEE: New York, NY, USA, 2019. [Google Scholar]

- Fulkerson, D.E.; Vogt, E.E. Prediction of SOI single-event effects using a simple physics-based SPICE model. IEEE Trans. Nucl. Sci. 2005, 52, 2168–2174. [Google Scholar] [CrossRef]

- Lim, H.K.; Fossum, J.G. Threshold voltage of thin-film silicon-on-insulator (SOI) MOSFET’s. IEEE Trans. Electron Devices 1983, 30, 1244–1251. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, K.; Zhang, X.; Li, B.; Li, D.; Zhao, F.; Bu, J.; Han, Z. A Compact Model for Single-Event Transient in Fully Depleted Silicon on Insulator MOSFET Considering the Back-Gate Voltage Based on Time-Domain Components. Electronics 2022, 11, 4022. https://doi.org/10.3390/electronics11234022

Wang K, Zhang X, Li B, Li D, Zhao F, Bu J, Han Z. A Compact Model for Single-Event Transient in Fully Depleted Silicon on Insulator MOSFET Considering the Back-Gate Voltage Based on Time-Domain Components. Electronics. 2022; 11(23):4022. https://doi.org/10.3390/electronics11234022

Chicago/Turabian StyleWang, Kewei, Xinyi Zhang, Bo Li, Duoli Li, Fazhan Zhao, Jianhui Bu, and Zhengsheng Han. 2022. "A Compact Model for Single-Event Transient in Fully Depleted Silicon on Insulator MOSFET Considering the Back-Gate Voltage Based on Time-Domain Components" Electronics 11, no. 23: 4022. https://doi.org/10.3390/electronics11234022

APA StyleWang, K., Zhang, X., Li, B., Li, D., Zhao, F., Bu, J., & Han, Z. (2022). A Compact Model for Single-Event Transient in Fully Depleted Silicon on Insulator MOSFET Considering the Back-Gate Voltage Based on Time-Domain Components. Electronics, 11(23), 4022. https://doi.org/10.3390/electronics11234022