Reset Noise Sampling Feedforward Technique (RNSF) for Low Noise MEMS Capacitive Accelerometer

Abstract

:1. Introduction

2. Noise Performance of Traditional Readout Circuit

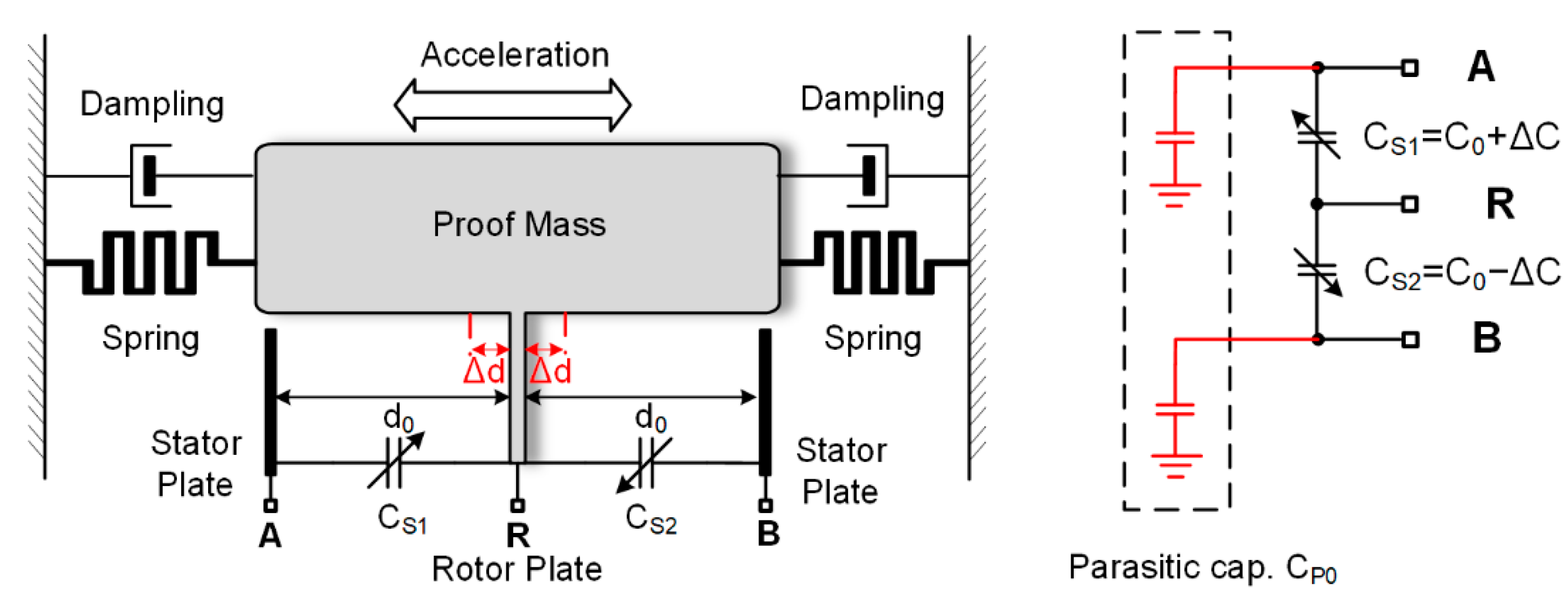

2.1. Sensor Structure

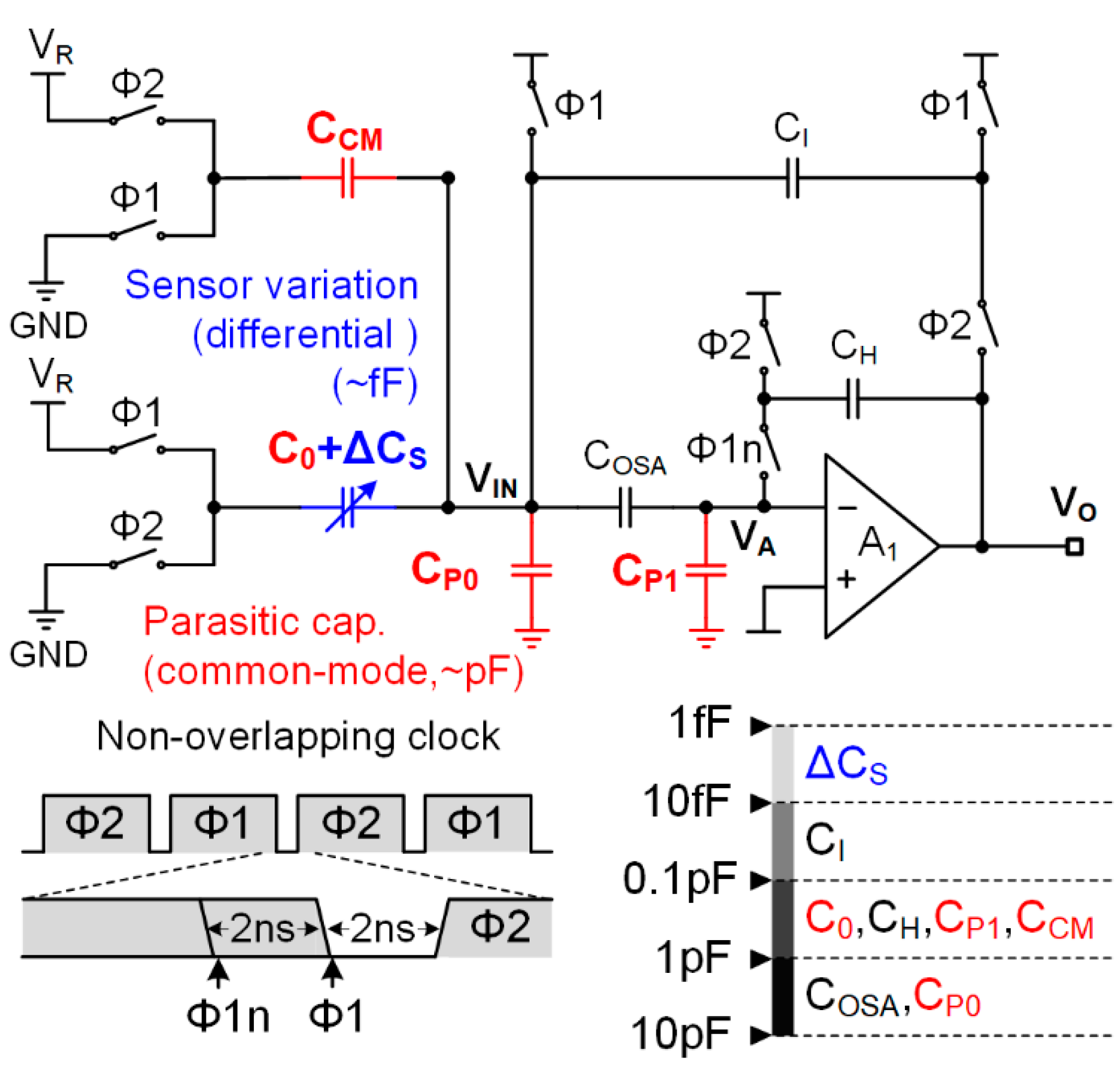

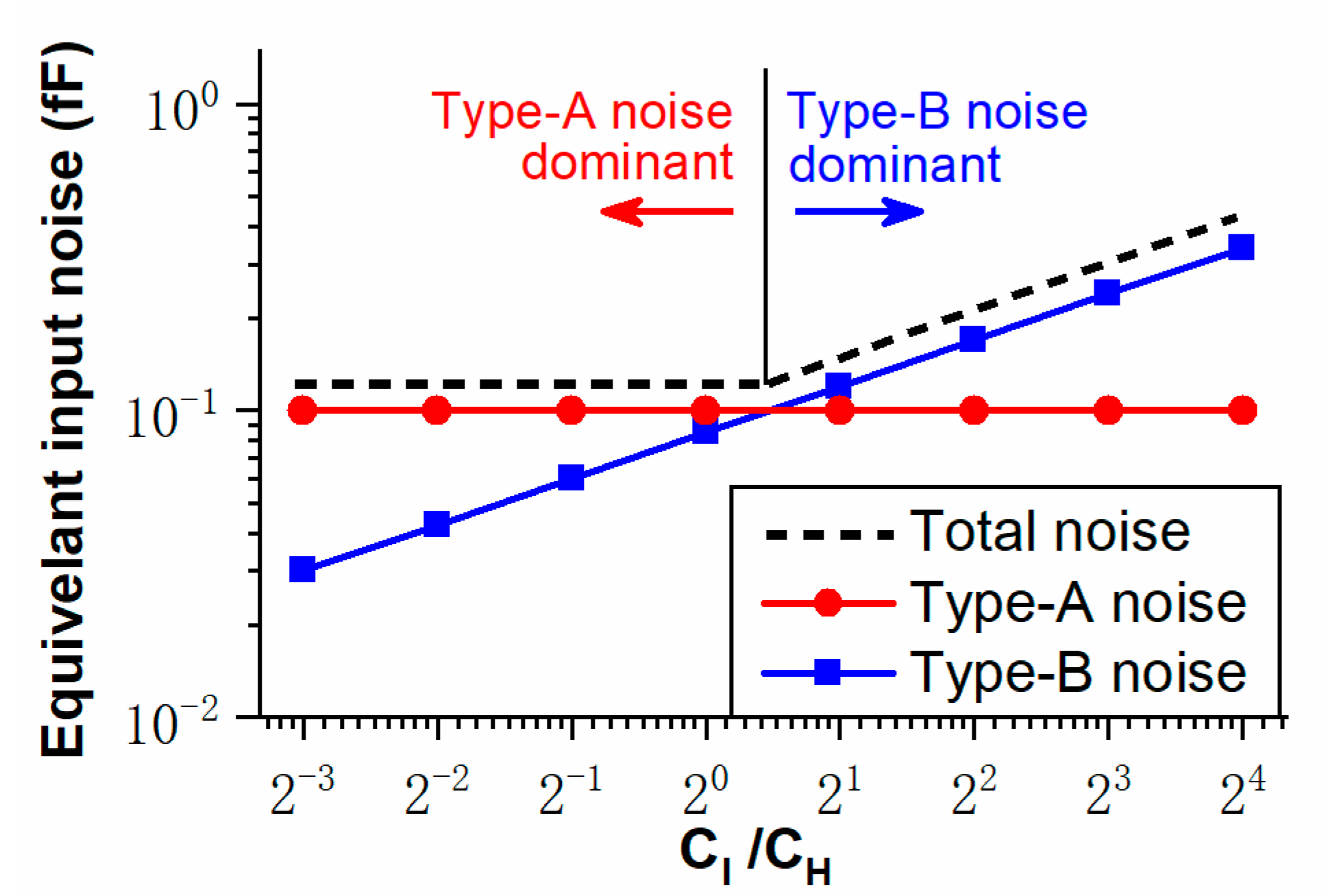

2.2. Noise Performance of Switched-Capacitor Capacitance-to-Voltage Converter

3. Reset Noise Sampling Feedforward (RNSF) Technique

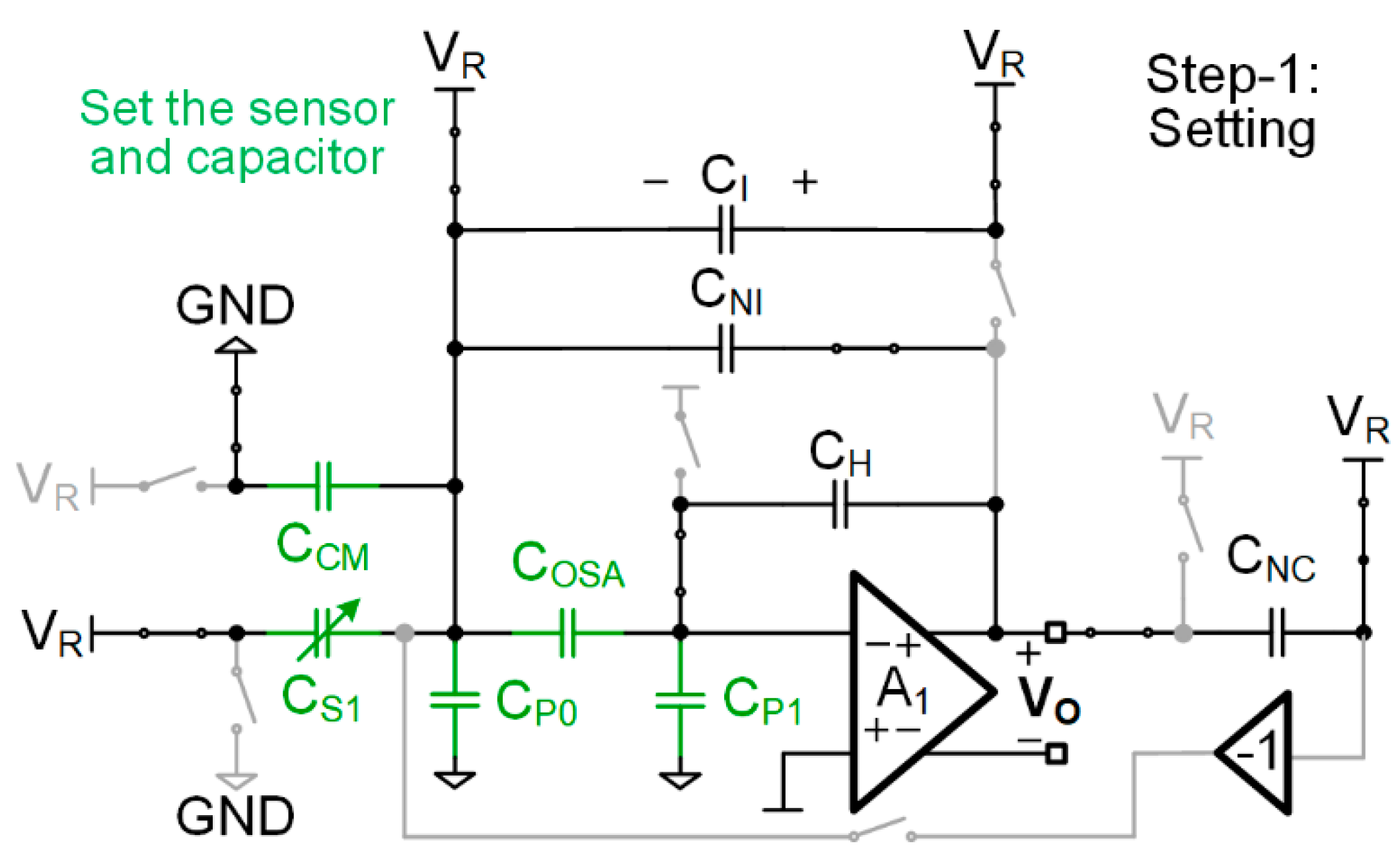

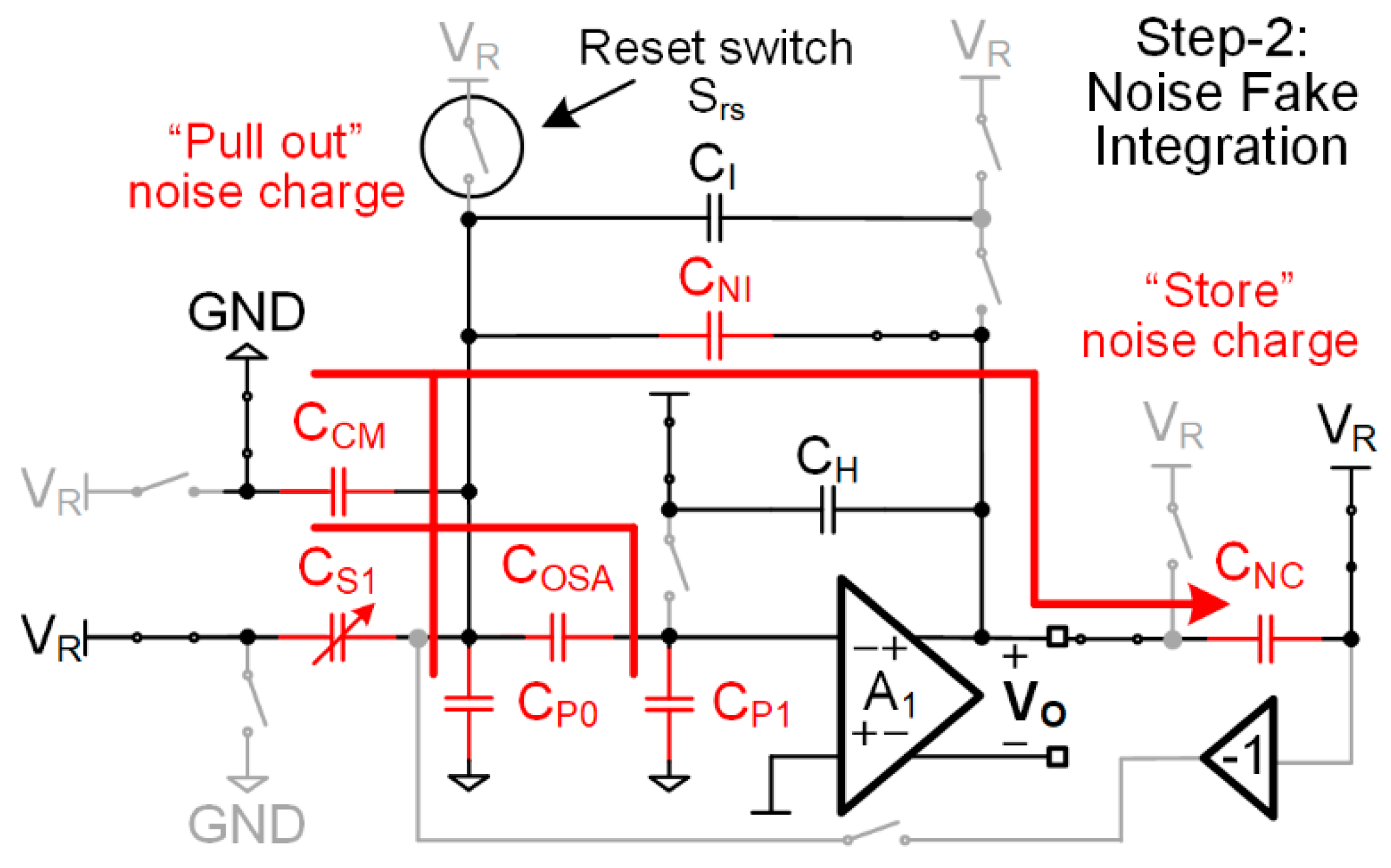

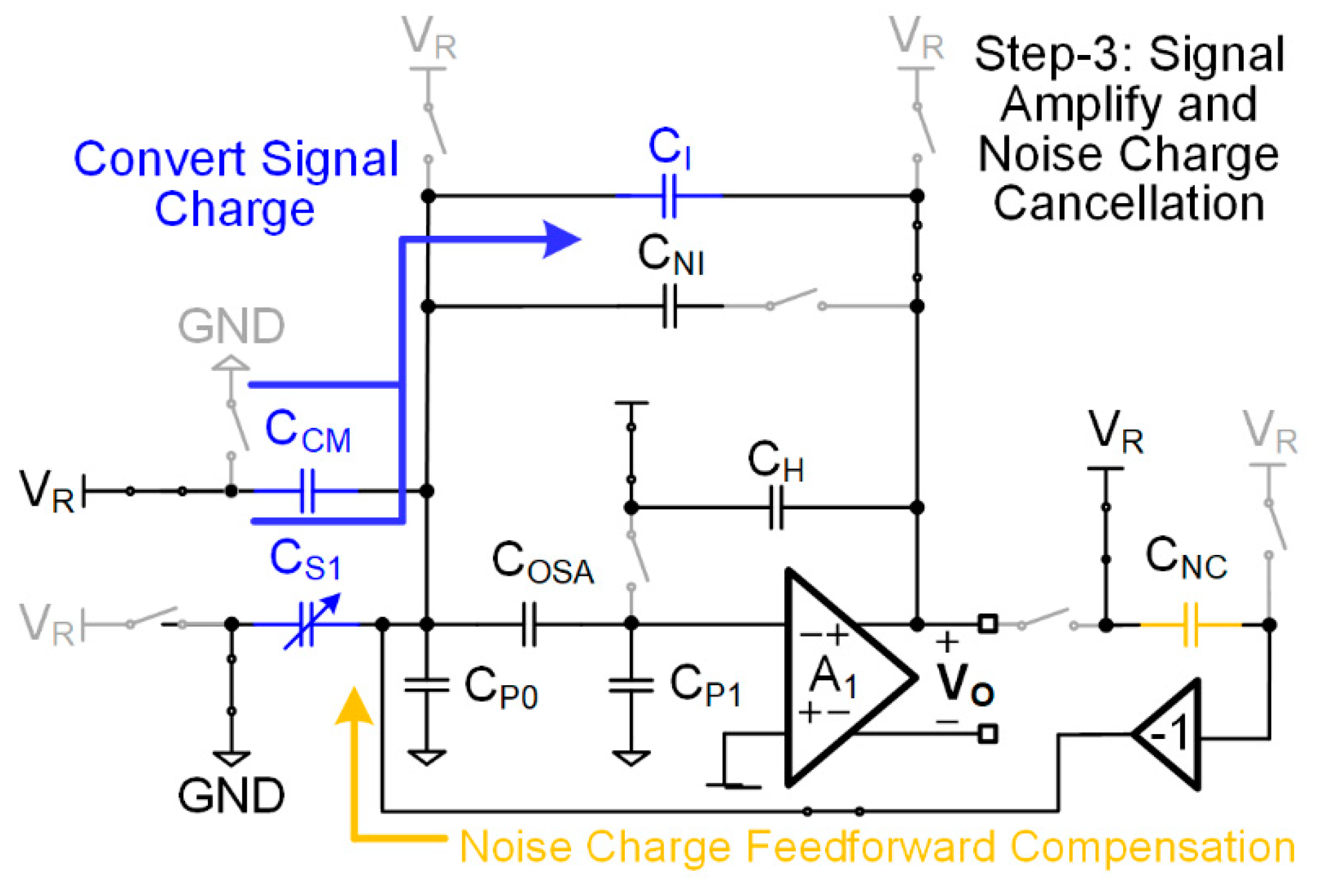

3.1. Circuit Implementation

3.2. Principle

3.3. Noise Performance Analysis

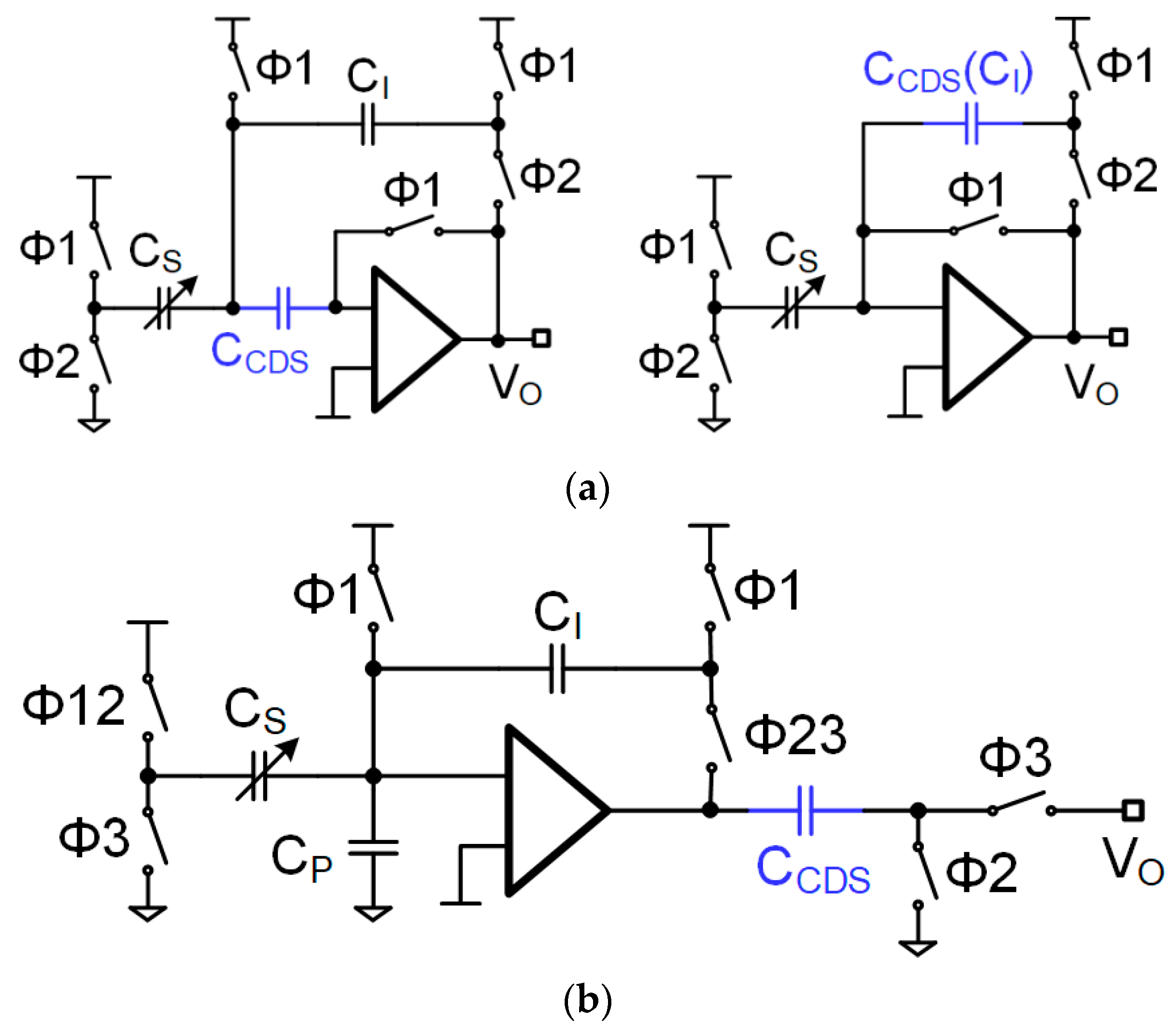

3.4. Noise Performance Comparison between RNSF and CDS

3.5. Drawbacks of RNSF Technique

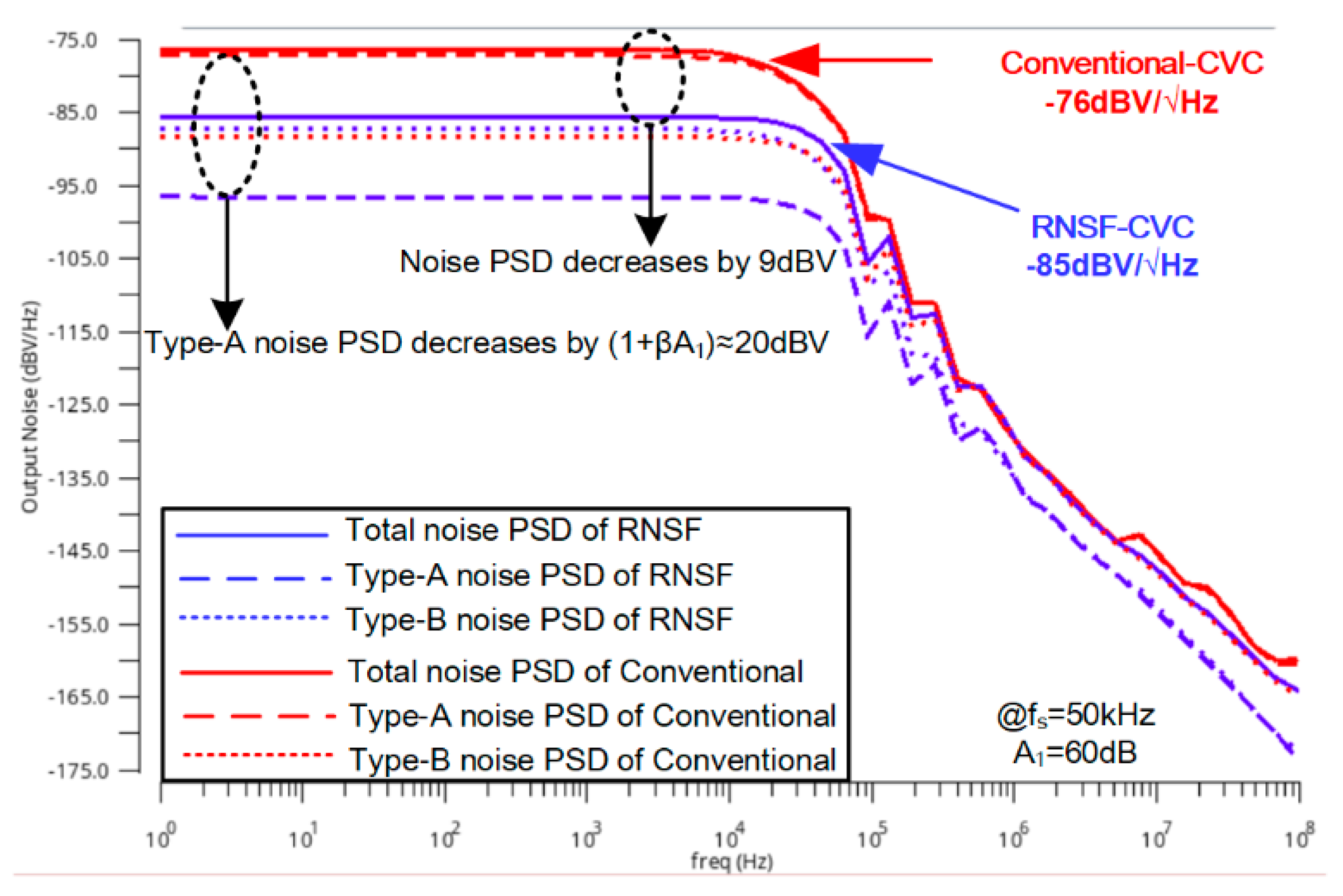

4. Simulation Results

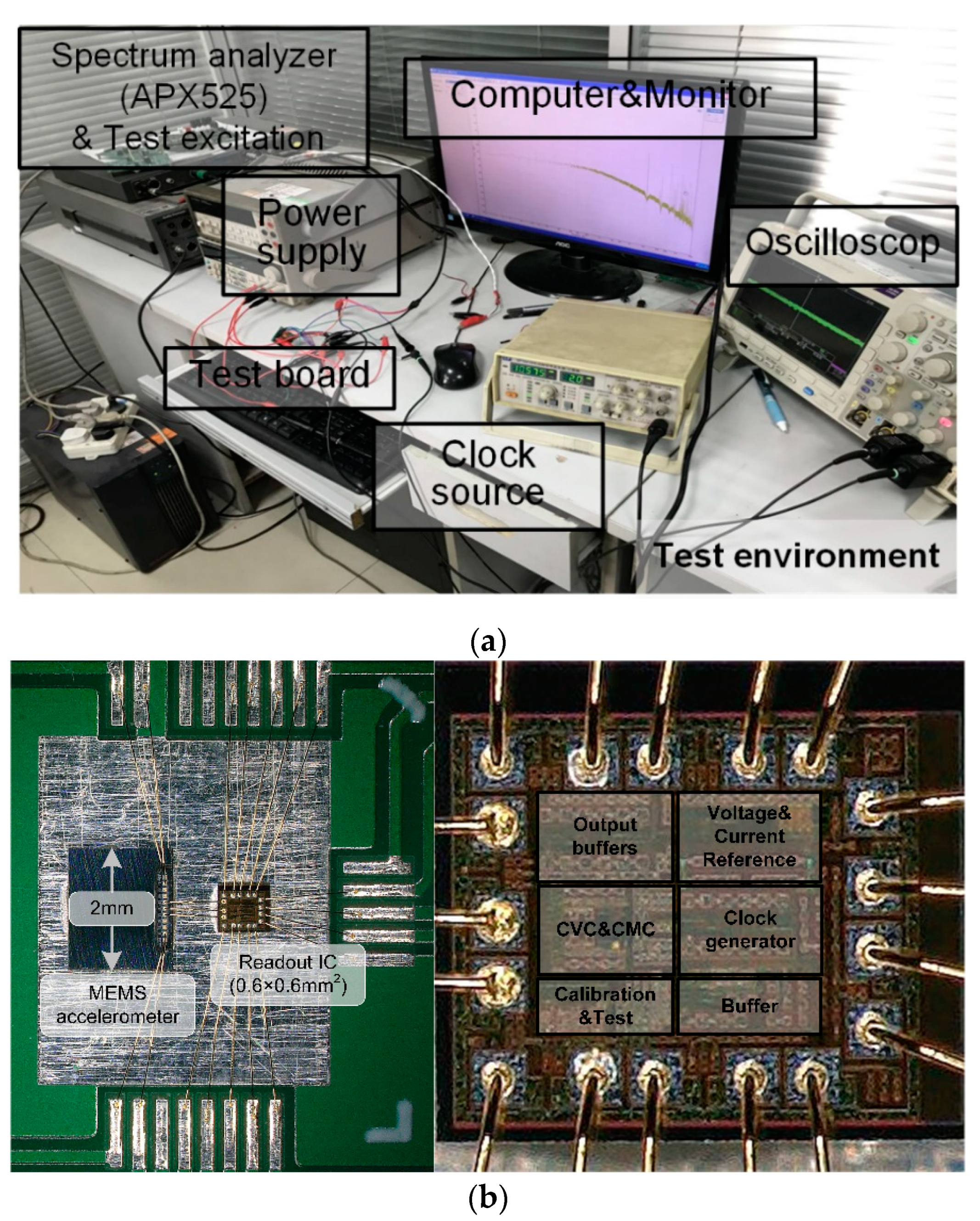

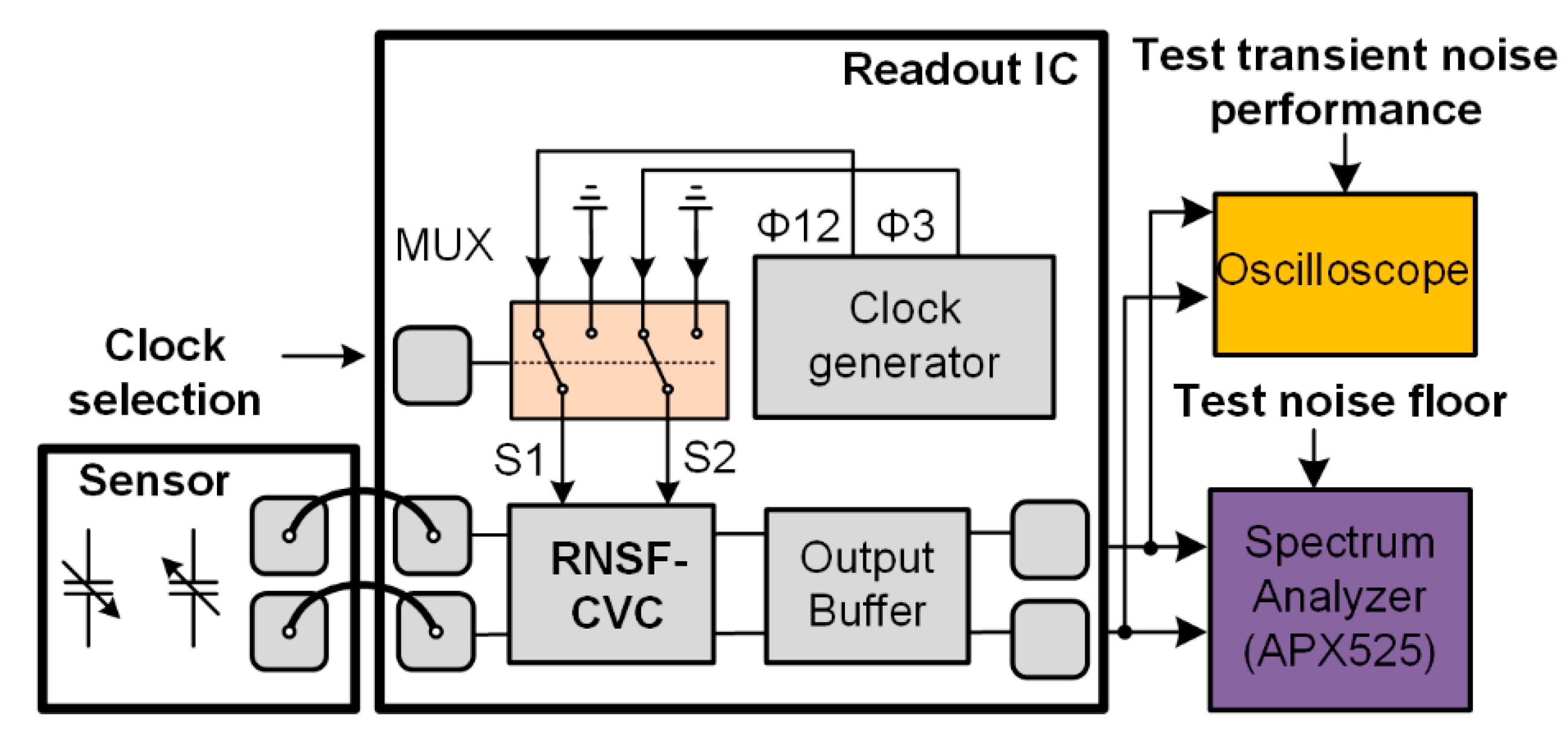

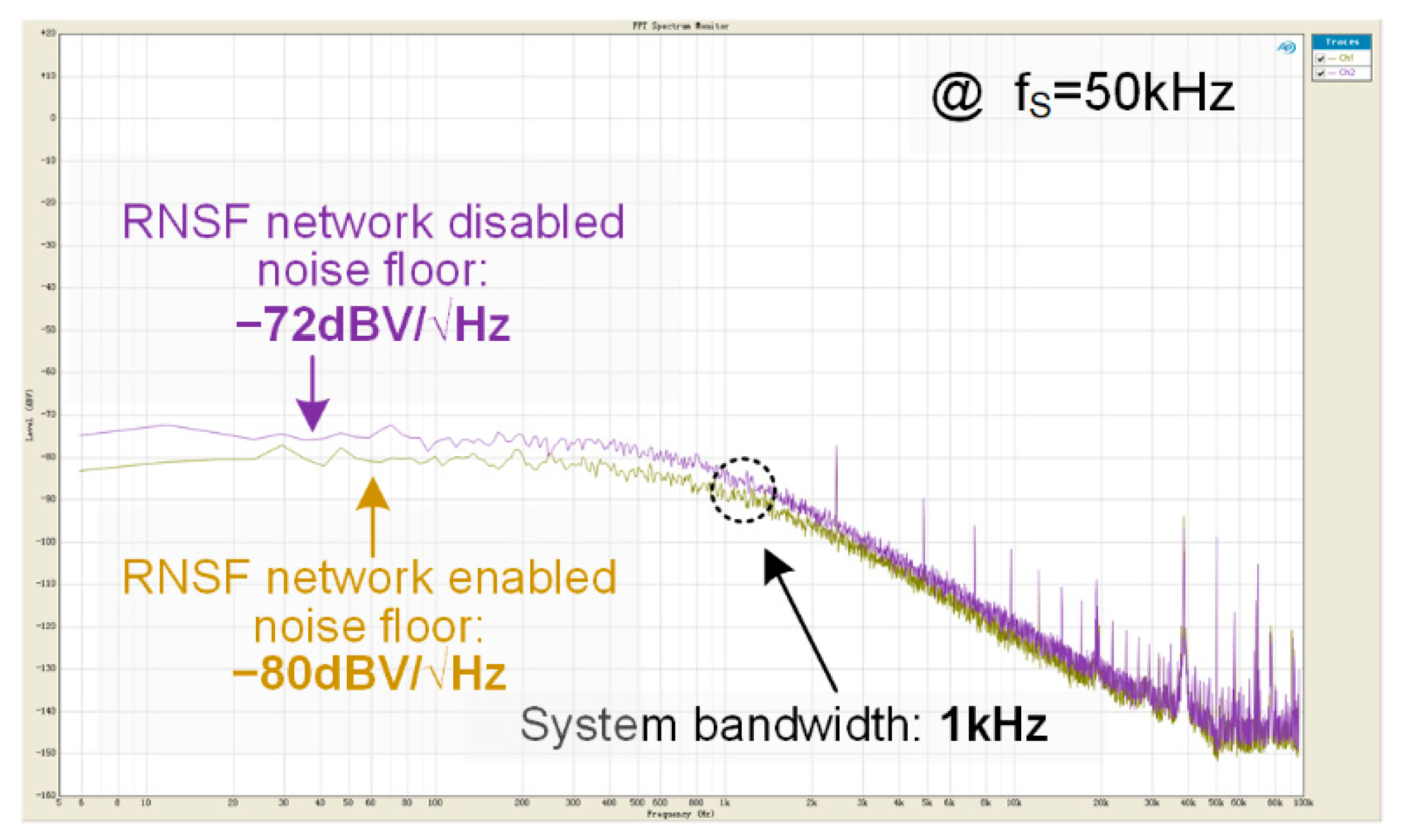

5. Physical Verification

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kamada, Y.; Isobe, A.; Oshima, T.; Furubayashi, Y.; Ido, T.; Sekiguchi, T. Capacitive MEMS Accelerometer with Perforated and Electrically Separated Mass Structure for Low Noise and Low Power. J. Microelectromech. Syst. 2019, 28, 401–408. [Google Scholar] [CrossRef]

- Shi, S.; Geng, W.; Bi, K.; Shi, Y.; Li, F.; He, J.; Chou, X. High Sensitivity MEMS Accelerometer Using PZT-Based Four L-Shaped Beam Structure. IEEE Sens. J. 2022, 22, 7627–7636. [Google Scholar] [CrossRef]

- Chiang, C.-T. Design of a CMOS MEMS Accelerometer Used in IoT Devices for Seismic Detection. IEEE J. Emerg. Sel. Top. Circuits Syst. 2018, 8, 566–577. [Google Scholar] [CrossRef]

- Liu, G.; Wang, C.; Jia, Z.; Wang, K.; Ma, W.; Li, Z. A Rapid Design and Fabrication Method for a Capacitive Accelerometer Based on Machine Learning and 3D Printing Techniques. IEEE Sens. J. 2021, 21, 17695–17702. [Google Scholar] [CrossRef]

- ADXL355 Datasheet. Low Noise, Low Drift, Low Power, 3-Axis MEMS Accelerometers; Analog Devices: Wilmington, MA, USA, 2018. [Google Scholar]

- IIS2ICLX Datasheet. High-Accuracy, High-Resolution, Low-Power, 2-Axis Digital Inclinometer with Embedded Machine Learing Core; STMicroelectronics: Geneva, Switzerland, 2022. [Google Scholar]

- Lemkin, M.; Boser, B.E. A three-axis micromachined accelerometer with a CMOS position-sense interface and digital offset-trim electronics. IEEE J. Solid-State Circuits 1999, 34, 456–468. [Google Scholar] [CrossRef]

- Furubayashi, Y.; Oshima, T.; Yamawaki, T.; Watanabe, K.; Mori, K.; Mori, N.; Matsumoto, A.; Kamada, Y.; Isobe, A.; Sekiguchi, T. A 22-ng/√Hz 17-mW Capacitive MEMS Accelerometer with Electrically Separated Mass Structure and Digital Noise- Reduction Techniques. IEEE J. Solid-State Circuits 2020, 55, 2539–2552. [Google Scholar] [CrossRef]

- Tabrizi, H.O.; Forouhi, S.; Farhanieh, O.; Bozkurt, A.; Magierowski, S.; Ghafar-Zadeh, E. Calibration-Free CMOS Capacitive Sensor for Life Science Applications. IEEE Trans. Instrum. Meas. 2021, 70, 2006512. [Google Scholar] [CrossRef]

- Lanniel, A.; Alpert, T.; Boeser, T.; Ortmanns, M. Evaluation of Frontend Readout Circuits for High Performance Automotive MEMS Accelerometers. In Proceedings of the 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Prague, Czech Republic, 2–5 July 2018; pp. 229–232. [Google Scholar]

- Ferlito, U.; Grasso, A.D.; Pennisi, S.; Vaiana, M.; Bruno, G. Sub-Femto-Farad Resolution Electronic Interfaces for Integrated Capacitive Sensors: A Review. IEEE Access 2020, 8, 153969–153980. [Google Scholar] [CrossRef]

- Paavola, M.; Kamarainen, M.; Laulainen, E.; Saukoski, M.; Koskinen, L.; Kosunen, M.; Halonen, K.A. A Micropower ΔΣ-Based Interface ASIC for a Capacitive 3-Axis Micro-Accelerometer. IEEE J. Solid-State Circuits 2009, 44, 3193–3210. [Google Scholar] [CrossRef]

- Lanniel, A.; Boeser, T.; Alpert, T.; Ortmanns, M. Noise Analysis of Charge-Balanced Readout Circuits for MEMS Accelerometers. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 175–184. [Google Scholar] [CrossRef]

- Zhong, L.; Lai, X.; Xu, D. Oversampling Successive Approximation Technique for MEMS Differential Capacitive Sensor. IEEE J. Solid-State Circuits 2018, 53, 2240–2251. [Google Scholar] [CrossRef]

- Ghanbari, M.M.; Tsai, J.M.; Nirmalathas, A.; Muller, R.; Gambini, S. An Energy-Efficient Miniaturized Intracranial Pressure Monitoring System. IEEE J. Solid-State Circuits 2017, 52, 720–734. [Google Scholar] [CrossRef]

- Shiah, J.; Mirabbasi, S. A 5-V 290-μW Low-Noise Chopper-Stabilized Capacitive-Sensor Readout Circuit in 0.8-μm CMOS Using a Correlated-Level-Shifting Technique. IEEE Trans. Circuits Syst. II Exp. Briefs 2014, 61, 254–258. [Google Scholar] [CrossRef]

- Sun, H.; Fang, D.; Jia, K.; Maarouf, F.; Qu, H.; Xie, H. A low power low-noise dual-chopper amplifier for capacitive CMOS-MEMS accelerometers. IEEE Sens. J. 2011, 11, 925–933. [Google Scholar] [CrossRef]

- Enz, C.C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef]

- Hafiz, O.A.; Wang, X.; Hurst, P.J.; Lewis, S.H. Immediate Calibration of Operational Amplifier Gain Error in Pipelined ADCs Using Extended Correlated Double Sampling. IEEE J. Solid-State Circuits 2013, 48, 749–759. [Google Scholar] [CrossRef]

- Yoshizawa, H.; Temes, G.C. Switched-Capacitor Track-and-Hold Amplifiers with Low Sensitivity to Op-Amp Imperfections. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 193–199. [Google Scholar] [CrossRef]

- Chae, Y.; Han, G. Low Voltage, Low Power, Inverter-Based Switched-Capacitor Delta-Sigma Modulator. IEEE J. Solid-State Circuits 2009, 44, 458–472. [Google Scholar] [CrossRef]

- Hershberg, B.; Weaver, S.; Sobue, K.; Takeuchi, S.; Hamashita, K.; Moon, U. Ring Amplifiers for Switched Capacitor Circuits. IEEE J. Solid-State Circuits 2012, 47, 2928–2942. [Google Scholar] [CrossRef]

- Shen, L.; Lu, N.; Sun, N. A 1-V 0.25- uW Inverter Stacking Amplifier with 1.07 Noise Efficiency Factor. IEEE J. Solid-State Circuits 2018, 53, 896–905. [Google Scholar] [CrossRef]

- Johnson, B.; Molnar, A. An Orthogonal Current-Reuse Amplifier for Multi-Channel Sensing. IEEE J. Solid-State Circuits 2013, 48, 1487–1496. [Google Scholar] [CrossRef]

- Sahoo, B.D.; Inamdar, A. Thermal-Noise-Canceling Switched-Capacitor Circuit. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 628–632. [Google Scholar] [CrossRef]

- Akita, I.; Okazawa, T.; Kurui, Y.; Fujimoto, A.; Asano, T. A Feedforward Noise Reduction Technique in Capacitive MEMS Accelerometer Analog Front-End for Ultra-Low-Power IoT Applications. IEEE J. Solid-State Circuits 2020, 55, 1599–1609. [Google Scholar] [CrossRef]

- Murmann, B. Thermal noise in track-and-hold circuits: Analysis and simulation techniques. IEEE Solid-State Circuits Mag. 2012, 4, 46–54. [Google Scholar] [CrossRef]

- Zhong, L.; Yang, J.; Xu, D.; Lai, X. Bandwidth-Enhanced Oversampling Successive Approximation Readout Technique for Low-Noise Power-Efficient MEMS Capacitive Accelerometer. IEEE J. Solid-State Circuits 2020, 55, 2529–2538. [Google Scholar] [CrossRef]

- Makinwa, K.A.; Baschirotto, A.; Harpe, P. Low-Power Analog Techniques, Sensors for Mobile Devices, and Energy Efficient Amplifiers; Part III; Springer: Cham, Switzerland, 2018; pp. 253–296. [Google Scholar]

- Yazdi, N.; Kulah, H.; Najafi, K. Precision readout circuits for capacitive microaccelerometers. In Proceedings of the SENSORS, 2004 IEEE, Vienna, Austria, 24–27 October 2004; pp. 28–31. [Google Scholar]

- Kapusta, R.; Zhu, H.; Lyden, C. Sampling Circuits That Break the kT/C Thermal Noise Limit. IEEE J. Solid-State Circuits 2014, 49, 1694–1701. [Google Scholar] [CrossRef]

- Liu, J.; Tang, X.; Zhao, W.; Shen, L.; Sun, N. 16.5 A 13b 0.005mm2 40MS/s SAR ADC with kT/C Noise Cancellation. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 258–260. [Google Scholar]

- Yucetas, M.; Pulkkinen, M.; Kalanti, A.; Salomaa, J.; Aaltonen, L.; Halonen, K. A high-resolution accelerometer with electrostatic damping and improved supply sensitivity. IEEE J. Solid-State Circuits 2012, 47, 1721–1730. [Google Scholar] [CrossRef]

- Wang, Y.-H.; Lai, X.-Q.; Li, Q.-Q.; Habib, K. Efficiency-enhanced and high-precision of input common-mode feedback control using OSA–CLS technique. Electron. Lett. 2020, 56, 1303–1306. [Google Scholar] [CrossRef]

- LIS2DS12 Datasheet. MEMS Digital Output Motion Sensor: Ultra-Low-Power, High-Performance 3-Axis “Pico” Accelerometer; STMicroelectronics: Geneva, Switzerland, 2017. [Google Scholar]

- Langfelder, G.; Frizzi, T.; Longoni, A.; Tocchio, A.; Manelli, D.; Lasalandra, E. Readout of MEMS capacitive sensors beyond the condition of pull-in instability. Sens. Actuator A Phys. 2011, 167, 374–384. [Google Scholar] [CrossRef]

- LIS3DHH Datasheet. MEMS Digital Output Sensor: Ultra-High-Resolution and Low-Noise Three-Axis Linear Accelerometer; STMicroelectronics: Geneva, Switzerland, 2017. [Google Scholar]

| Type-I | Type-II | Type-III | RNSF | |

|---|---|---|---|---|

| Thermal noise | - | O | + | + |

| Gain error | O | O | O | + |

| Flicker noise and offset reduction | O | O | O | O |

| Bandwidth & driving ability | O | O | - | O |

| Clock phase | 2 | 2 | 3 | 3 |

| Device size | (X and Y axis) |

| Capacitive gap | |

| Proof Mass | |

| Static capacitance | 550 fF |

| Bandwidth | 2 kHz |

| Sensitivity | 4 fF/g |

| Reference/Paper | Zhong [28] | Sun [17] | Akita [26] | Paavola [12] | Yucetas [37] | This Work |

|---|---|---|---|---|---|---|

| Noise Reduction Technique | Bandwidth-Enhanced OSA | Dual-Chopper | Feedforward Noise Reduction | Correlated Double Sampling | Traditional Oversampling | RNSF |

| Full scale (g) | ±8 | ±11.5 | ±5 | ±4 | ±1.15 | ±8 |

| Nonlinearity @ FS | <1% | - | <1% | 0.3% | 0.27% | <1% |

| Bandwidth (Hz) | 10 k | 10 k | 50 | 25 | 200 | 1 k |

| Sampling rate (Hz) | 100 k | - | 100 | 51.2 k | - | 50 k |

| Sensor sens (fF/g) | 1.0 | - | 15 | - | - | 4 |

| IC sens (mV/fF) | 90 | - | - | - | - | 100 |

| Noise floor () | 900 | 40 | 290 | 275 | 2.0 | 250 |

| Power () | 248 | 1000 | 0.25 | 97.6 | 3600 | 62 |

| Supply voltage (V) | 1.8 | - | 1.0 | 1.2 | 3.6 | 1.8 |

| ) | 2232 | 400 | 10 | 5368 | 509 | 490 |

| Process | BCD | CMOS- MEMS | CMOS | CMOS | CMOS | BCD |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lai, X.; Wang, Y.; Li, Q.; Habib, K. Reset Noise Sampling Feedforward Technique (RNSF) for Low Noise MEMS Capacitive Accelerometer. Electronics 2022, 11, 2693. https://doi.org/10.3390/electronics11172693

Lai X, Wang Y, Li Q, Habib K. Reset Noise Sampling Feedforward Technique (RNSF) for Low Noise MEMS Capacitive Accelerometer. Electronics. 2022; 11(17):2693. https://doi.org/10.3390/electronics11172693

Chicago/Turabian StyleLai, Xinquan, Yuheng Wang, Qinqin Li, and Kashif Habib. 2022. "Reset Noise Sampling Feedforward Technique (RNSF) for Low Noise MEMS Capacitive Accelerometer" Electronics 11, no. 17: 2693. https://doi.org/10.3390/electronics11172693

APA StyleLai, X., Wang, Y., Li, Q., & Habib, K. (2022). Reset Noise Sampling Feedforward Technique (RNSF) for Low Noise MEMS Capacitive Accelerometer. Electronics, 11(17), 2693. https://doi.org/10.3390/electronics11172693