Substrate-Induced Dissipative and Non-Linear Effects in RF Switches: Probing Ultimate Performance Based on Laser-Machined Membrane Suspension

Abstract

:1. Introduction

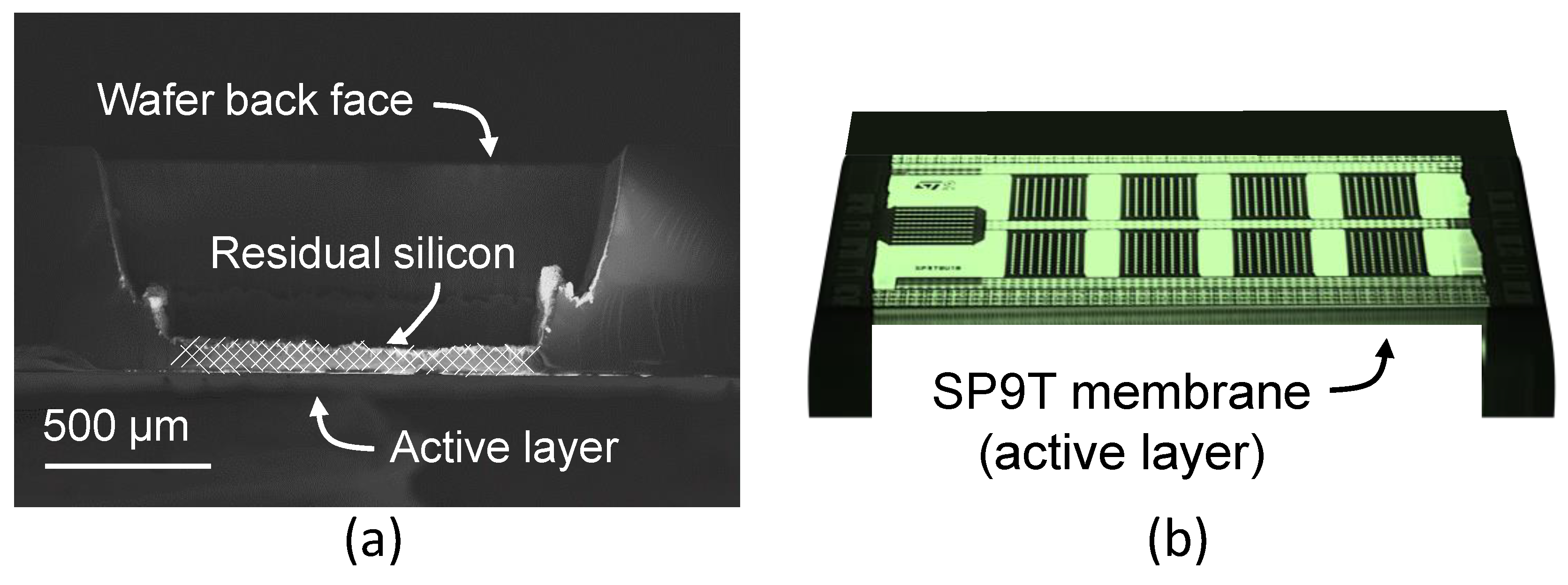

2. Laser-Assisted Substrate Removal

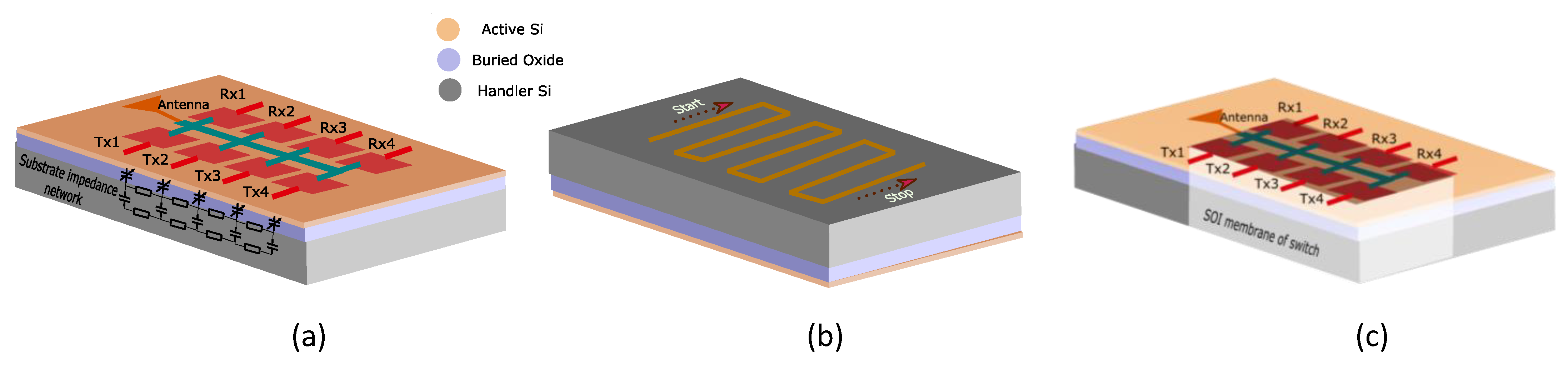

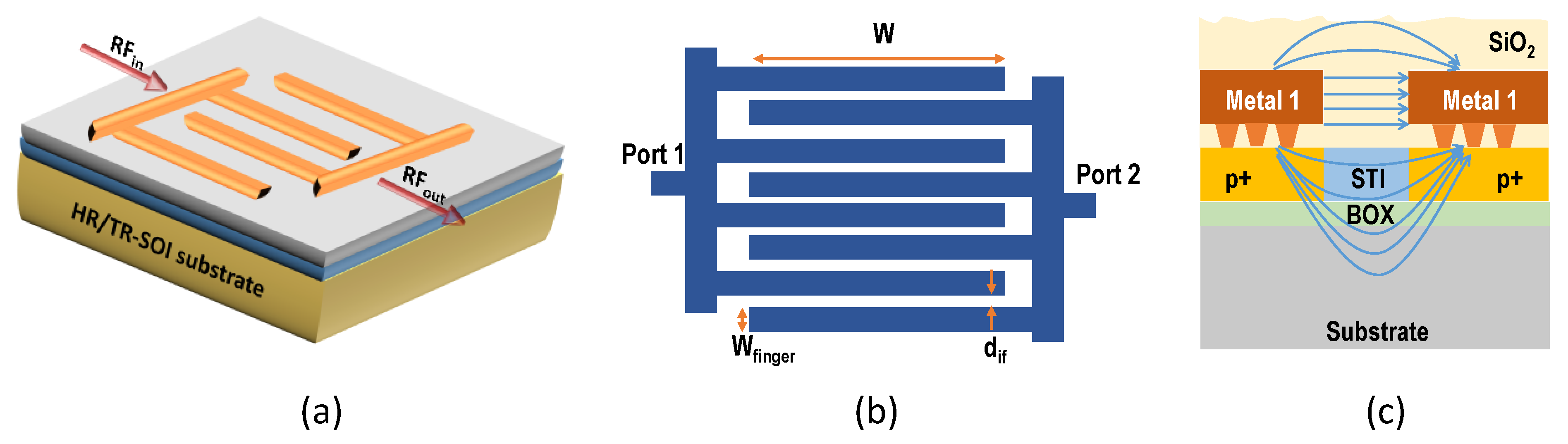

3. Capacitive Comb Coupling Structure

3.1. Device Structure and Post-Processing

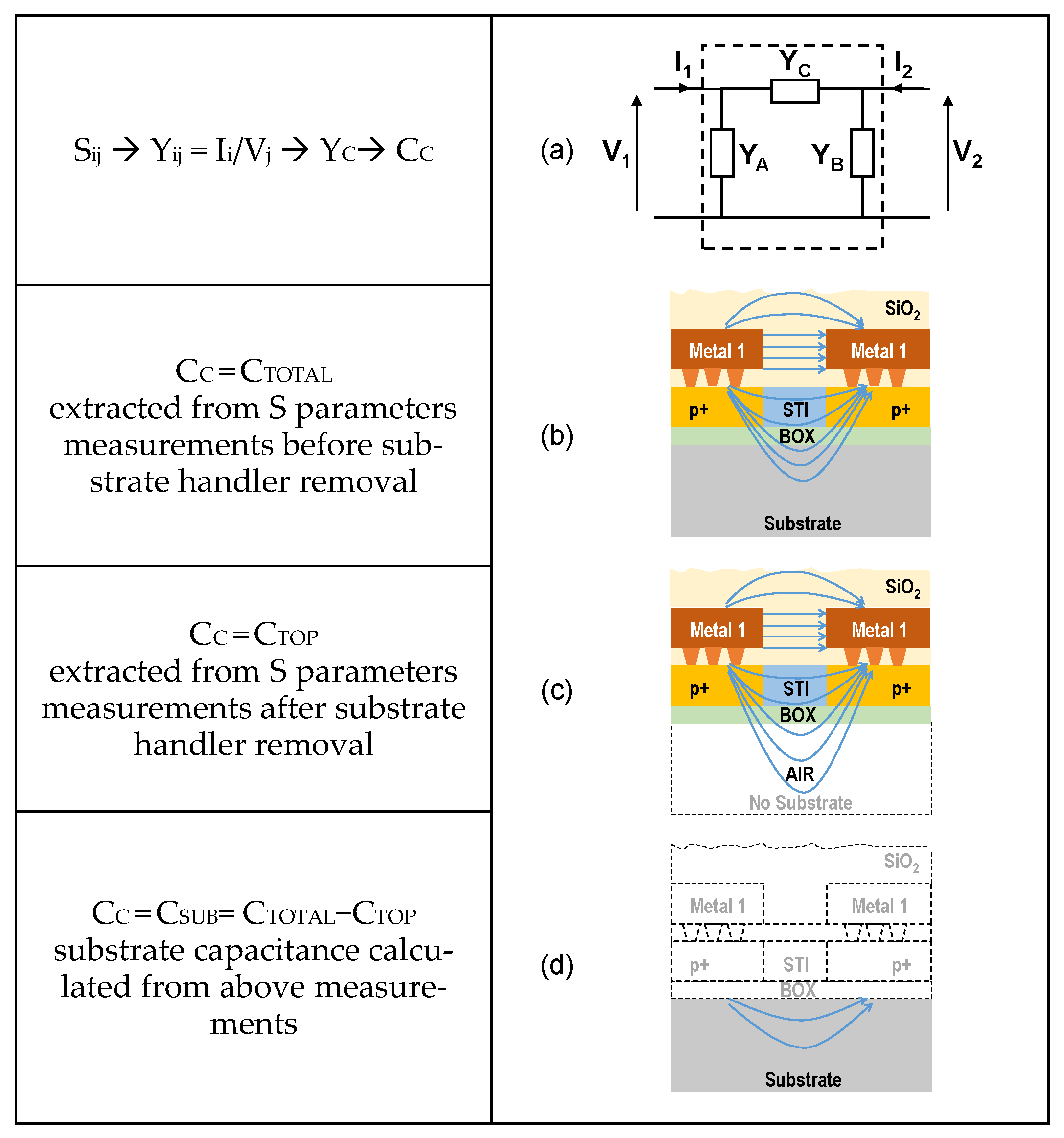

3.2. Extraction of the Substrate Coupling Contribution

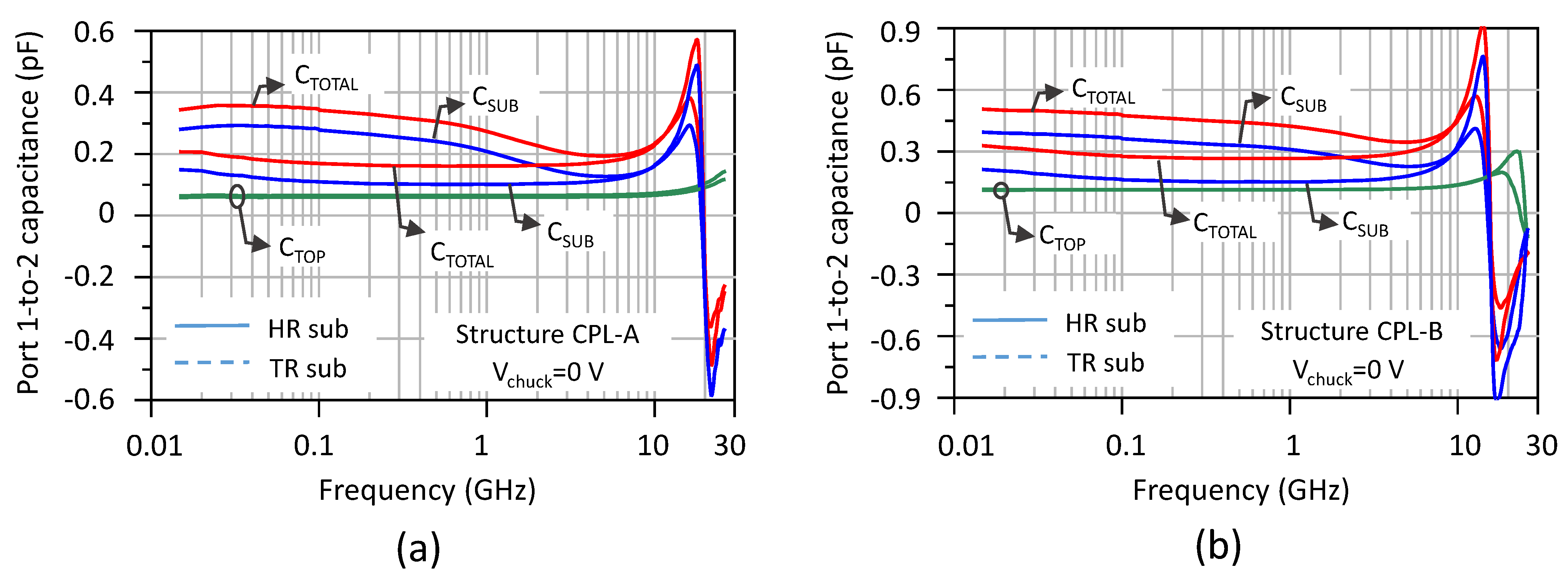

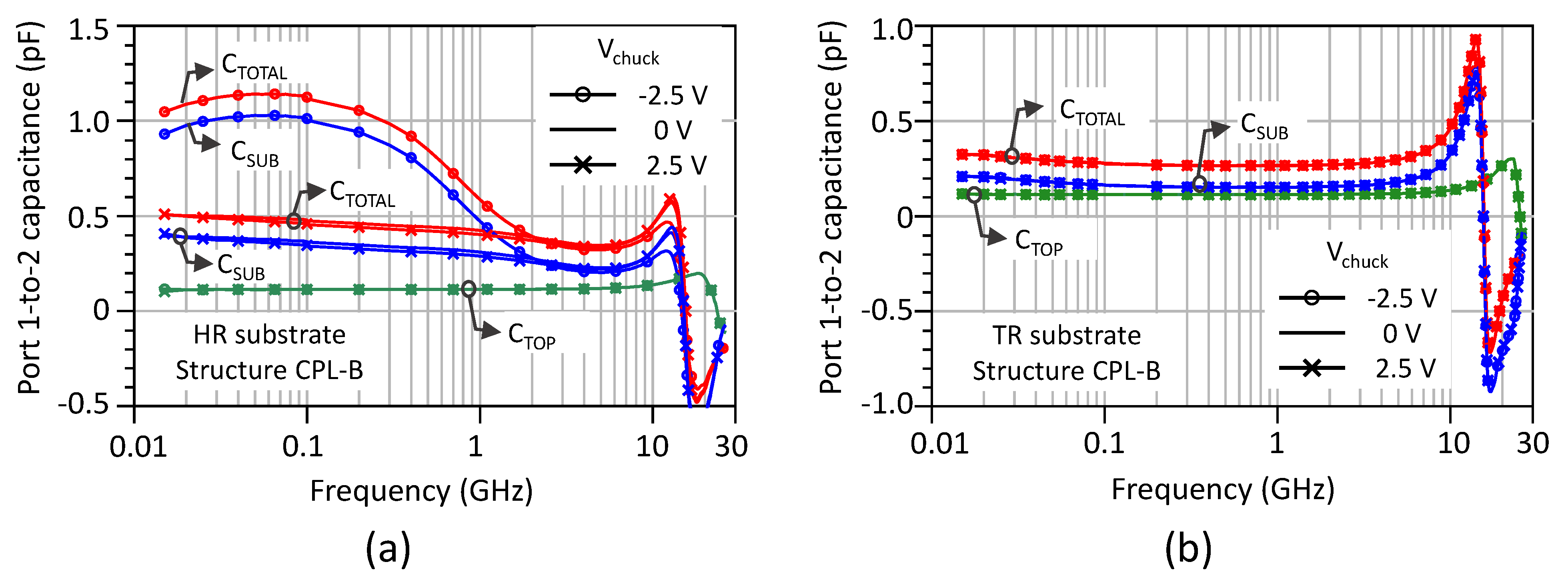

- S-parameter measurements are first performed on a structure with an unmodified substrate. From this step, the evaluation of the total CTOTAL capacitance is obtained as shown in Figure 4b

- After the local removal of the substrate down to the BOX, a second sequence of S-parameter measurements is used to extract the CTOP capacitance, which mainly reflects the electrostatic coupling introduced by the metal combs belonging to the back-end of line interconnects (Figure 4c)

- Finally, the substrate capacitance CSUB is deduced from the previous measurements, considering that CTOP and CSUB are associated in parallel to yield the total capacitance CTOTAL (Figure 4d).

- Firstly, the substrate makes a substantial contribution to the total capacitance for both types of substrates even though its relative importance is lesser in the TR case.

- Secondly, CTOP is the same regardless of the initial substrate, HR or TR. As this capacitance is measured after local removal of the substrate, this result is expected and verified, and validates the method of the dissociation of capacitive contributions detailed in Figure 4. It can also be noted that CTOP remains strictly flat and frequency-independent, as one would expect from an insulating dielectric material free of any space charge.

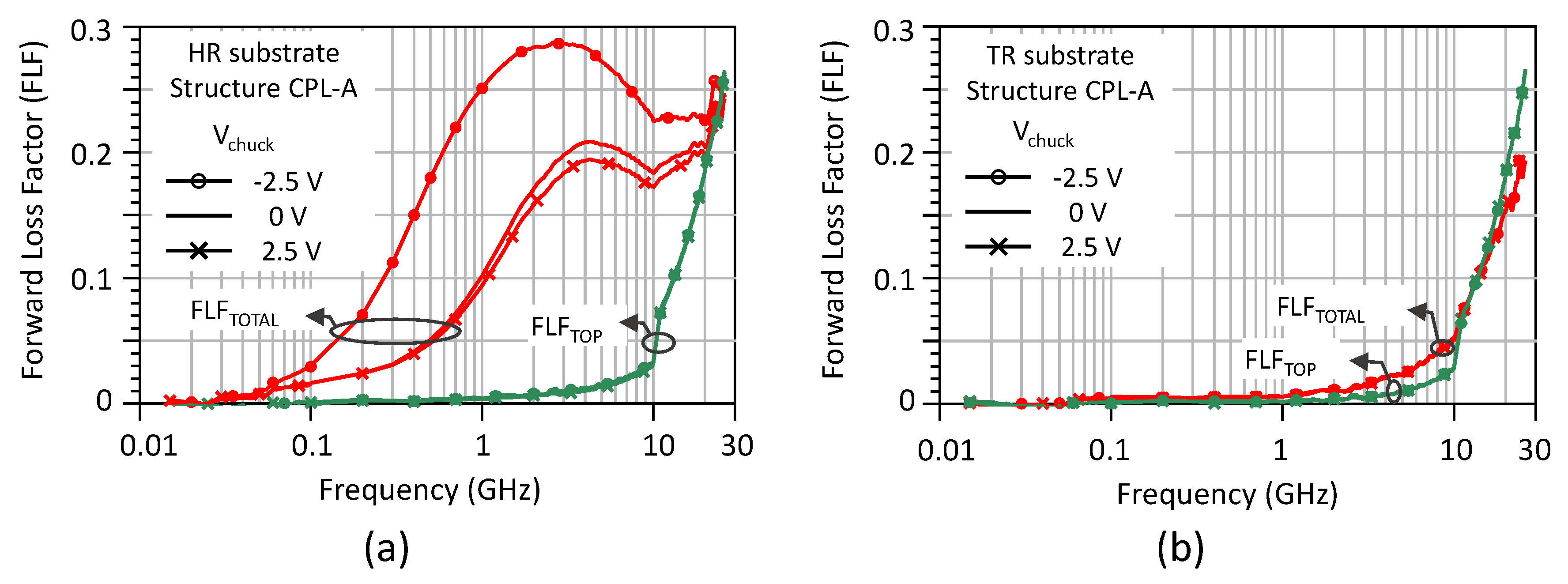

3.3. Substrate Dissipation Losses

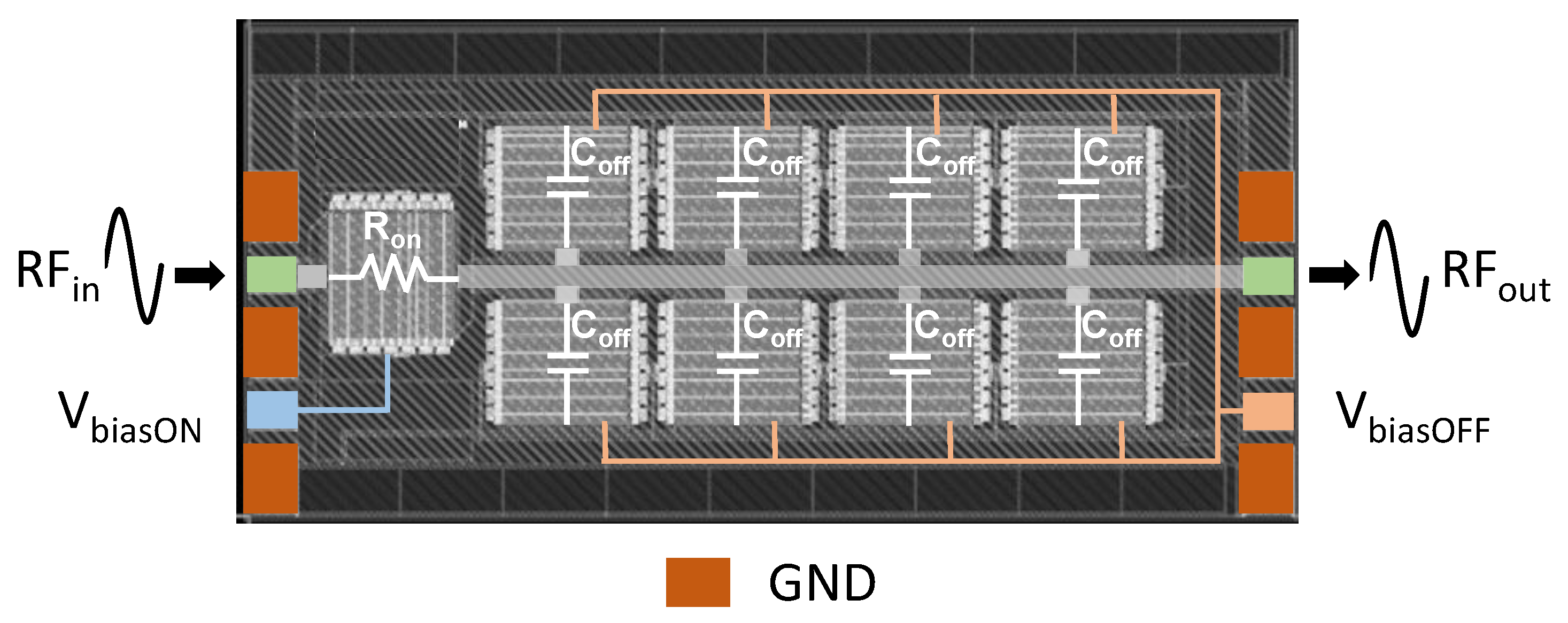

4. SP9T Switch Test Structure

4.1. Device Structure, RF Ports and DC Bias

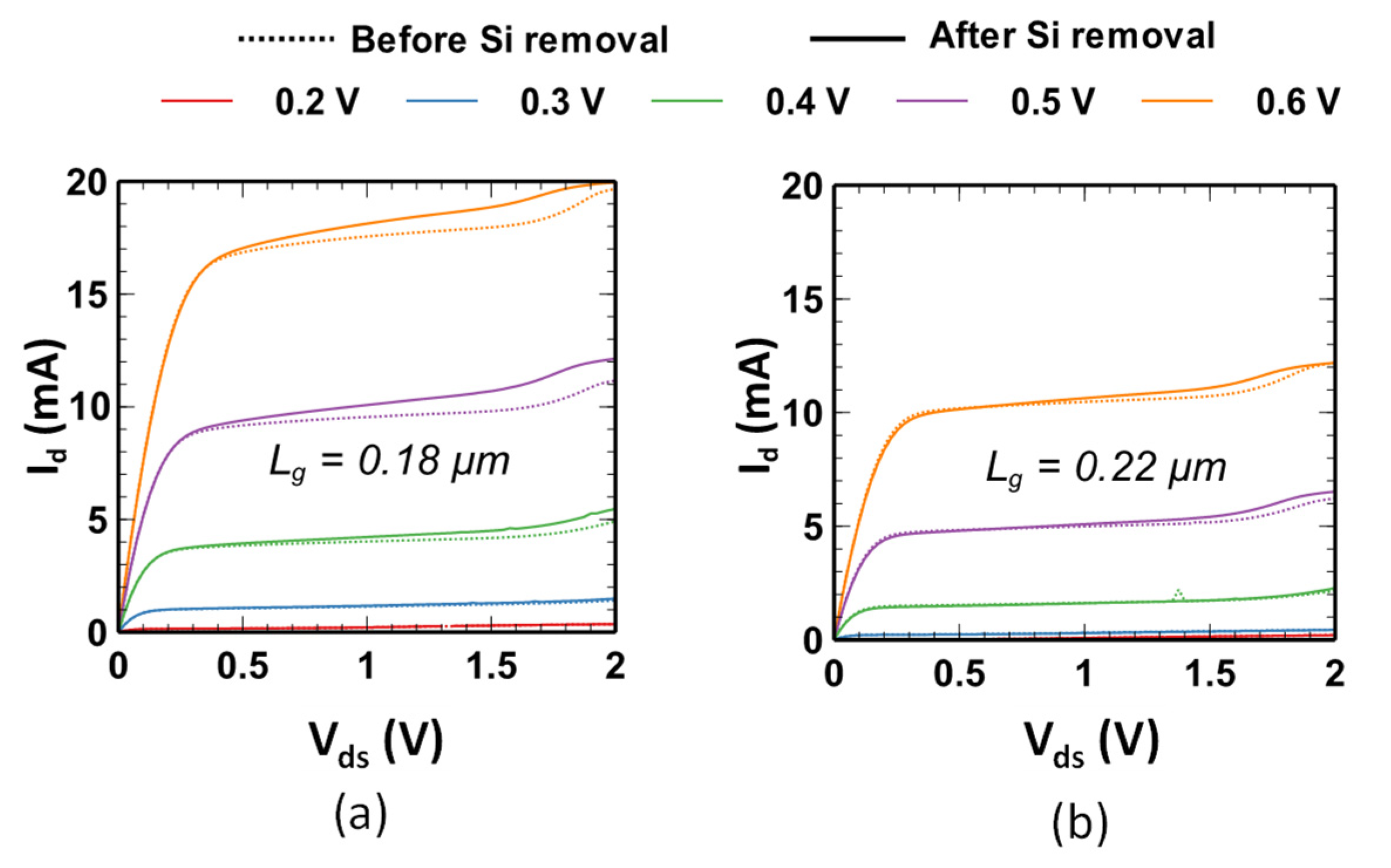

4.2. DC Characterization

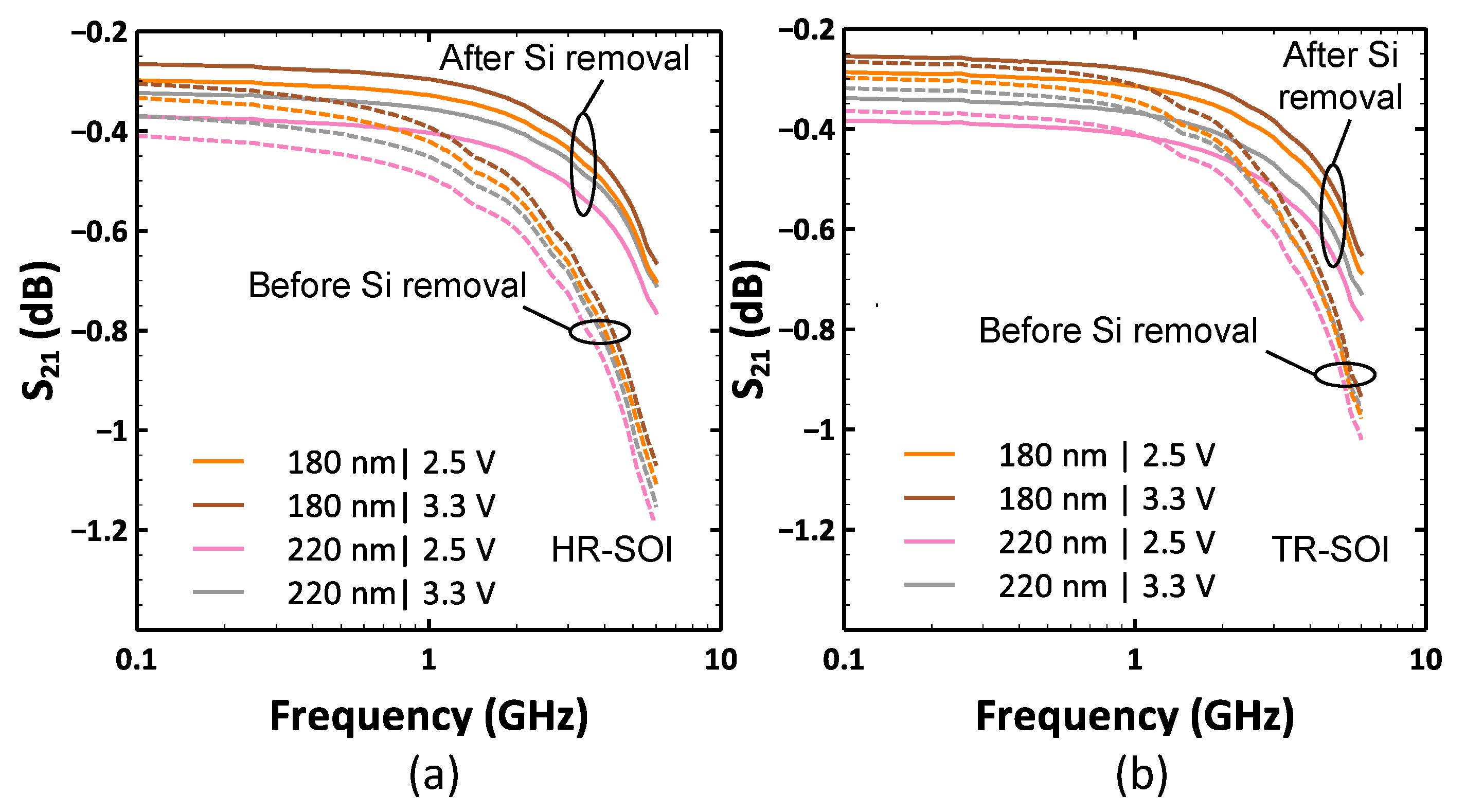

4.3. Two-Port S-Parameter Characterization

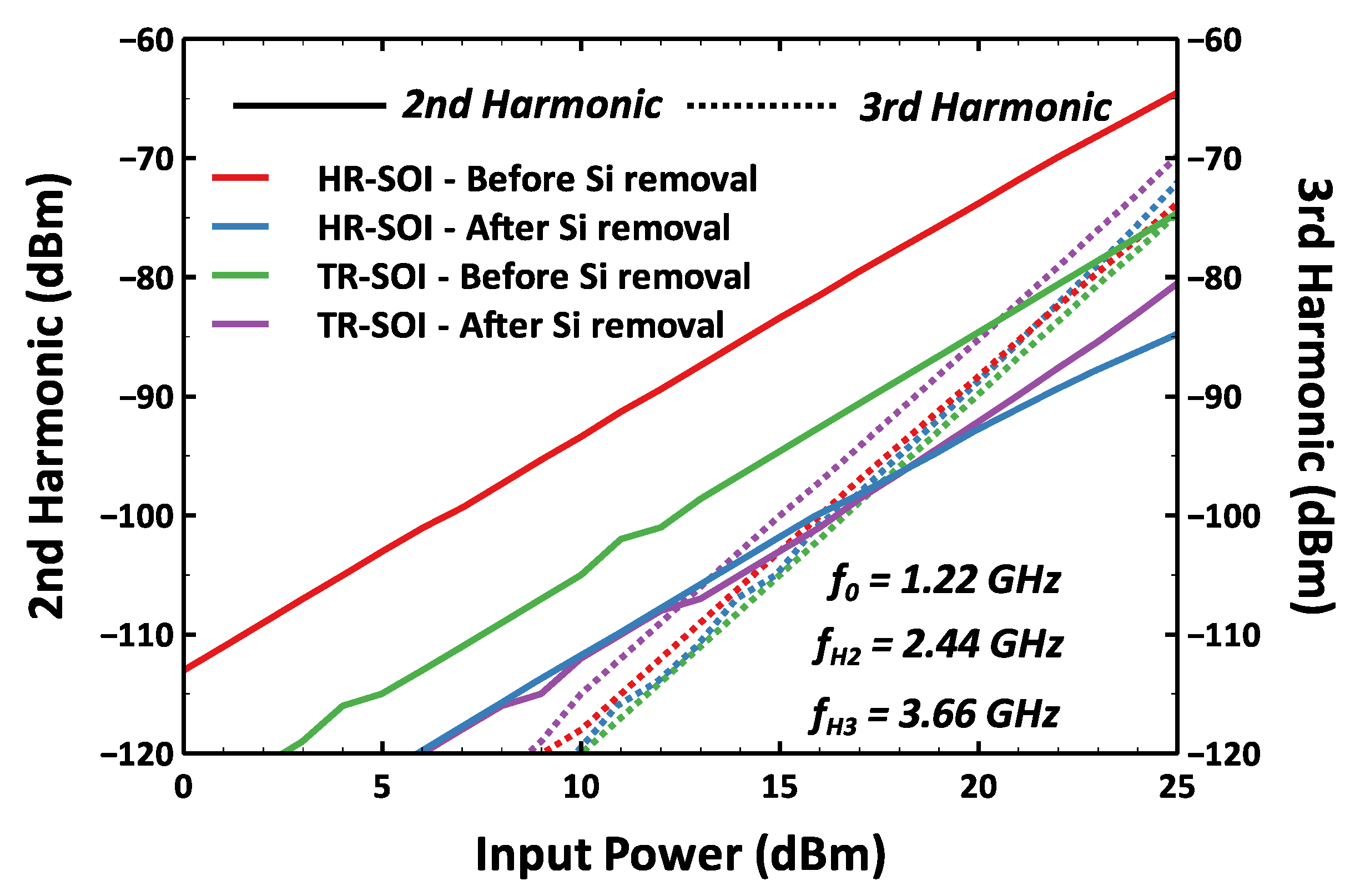

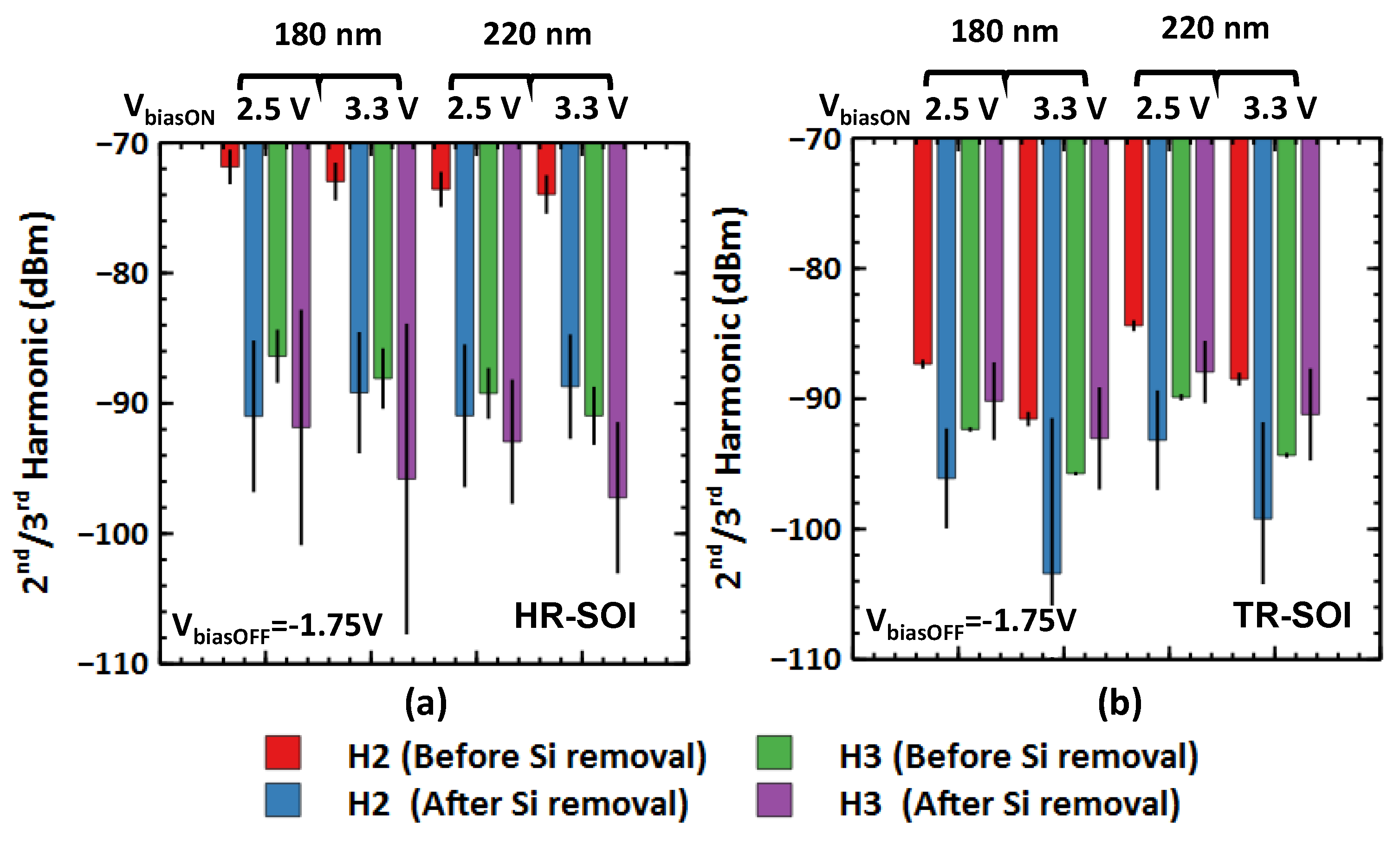

4.4. Large-Signal Harmonic Distortion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Solutions, I.S. Choosing the Right RF Switches for Smart Mobile Device Applications; Technical Report; Skyworks Solutions, Inc.: Irvine, CA, USA, 2011. [Google Scholar]

- Li, J.Y.; Chang, W.-C. Wideband and high isolation RF carrier-aggregated switch module for LTE-Advanced base station. In Proceedings of the European Microwave Conference (EuMC), London, UK, 4–6 October 2016; pp. 695–698. [Google Scholar]

- Chiu, H.C.; Yeh, T.J.; Hsieh, Y.Y.; Hwang, T.; Yeh, P.; Wu, C.S. Low insertion loss switch technology using 6-inch InGaP/AlGaAs/InGaAs pHEMT production process. In Proceedings of the IEEE Compound Semiconductor Integrated Circuit Symposium, Monterey, CA, USA, 24–27 October 2004; pp. 119–122. [Google Scholar]

- Kelly, D.; Brindle, C.; Kemerling, C.; Stuber, M. The state-of-the-art of silicon-on-sapphire CMOS RF switches. In Proceedings of the IEEE Compound Semiconductor Integrated Circuit Symposium, Palm Springs, CA, USA, 30 October–2 November 2005; p. 4. [Google Scholar]

- Blaschke, V.; Unikovski, A.; Hurwitz, P.; Chaudhry, S. A SP9T cellular antenna switch in 2.5 V CMOS thin-film SOI. In Proceedings of the IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Austin, TX, USA, 21–23 January 2013; pp. 144–146. [Google Scholar]

- Im, D.; Lee, K. Characterization and optimization of partially depleted SOI MOSFETs for high power RF switch applications. J. Solid-State Electron. 2013, 90, 94–98. [Google Scholar] [CrossRef]

- Tinella, C.; Fournier, J.M.; Belot, D.; Knopik, V. A 0.7 dB insertion loss CMOS-SOI antenna switch with more than 50 dB isolation over the 2.5 to 5GHz band. In Proceedings of the European Solid-State Circuits Conference, Florence, Italy, 24–26 September 2002; pp. 483–486. [Google Scholar]

- Kim, D.; Min, B.W. High Power Ku-Band T/R and SP4T Switches in SOI CMOS. J. Electromagn. Waves Appl. 2016, 30, 728–739. [Google Scholar] [CrossRef]

- Rack, M.; Allibert, F.; Raskin, J.-P. Modeling of Semiconductor Substrates for RF Applications: Part I—Static and Dynamic Physics of Carriers and Traps. IEEE Trans. Electron Devices 2021, 68, 4598–4605. [Google Scholar] [CrossRef]

- Rack, M.; Allibert, F.; Raskin, J.-P. Modeling of Semiconductor Substrates for RF Applications: Part II—Parameter Impact on Harmonic Distortion. IEEE Trans. Electron Devices 2021, 68, 4606–4613. [Google Scholar] [CrossRef]

- Ali, K.B.; Neve, C.R.; Gharsallah, A.; Raskin, J.P. RF Performance of SOI CMOS Technology on Commercial 200-mm Enhanced Signal Integrity High Resistivity SOI Substrate. IEEE Trans. Electron Devices 2014, 61, 722–728. [Google Scholar] [CrossRef]

- Kerr, D.C.; Gering, J.M.; McKay, T.G.; Carroll, M.S.; Neve, C.R.; Raskin, J.P. Identification of RF harmonic distortion on Si substrates and its reduction using a trap-rich layer. In Proceedings of the IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Orlando, FL, USA, 23–25 January 2008; pp. 151–154. [Google Scholar]

- Liu, S.; Zhu, L.; Allibert, F.; Radu, I.; Zhu, X.; Lu, Y. Physical Models of Planar Spiral Inductor Integrated on the High-Resistivity and Trap-Rich Silicon-on-Insulator Substrates. IEEE Trans. Electron Devices 2007, 64, 2775–2781. [Google Scholar] [CrossRef]

- Mueller, J.E.; Bruder, T.; Herrero, P.; Norholm, N.; Olesen, P.; Rizk, J.; Schumacher, L. Requirements for reconfigurable 4G front-ends. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest, Seattle, WA, USA, 2–7 June 2013; pp. 1–4. [Google Scholar]

- Tombak, A.; Iversen, C.; Pierres, J.B.; Kerr, D.; Carroll, M.; Mason, P.; Spears, E.; Gillenwater, T. Cellular antenna switches for multimode applications based on a Silicon-on-Insulator technology. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, USA, 23–25 May 2010; pp. 271–274. [Google Scholar]

- Shaked, Z.; Hurwitz, P.; Heiman, A.; Moen, K.; Kanawati, R.; Chaudhry, S.; Racanelli, M. SOI technology for front end applications. In Proceedings of the IEEE International Conference on Microwaves, Communications, Antennas and Electronic Systems (COMCAS), Tel Aviv, Israel, 2–4 November 2015; pp. 1–3. [Google Scholar]

- Tagro, Y.; Lecavelier des Etangs-Levallois, A.; Poulain, L.; Lepilliet, S.; Gloria, D.; Raynaud, C.; Dubois, E.; Danneville, F. High frequency noise potentialities of reported CMOS 65 nm SOI technology on flexible substrate. In Proceedings of the IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Santa Clara, CA, USA, 16–18 January 2012; pp. 89–92. [Google Scholar]

- Lecavelier des Etangs-Levallois, A.; Lesecq, M.; Danneville, F.; Tagro, Y.; Lepilliet, S.; Hoel, V.; Troadec, D.; Gloria, D.; Raynaud, C.; Dubois, E. Radio-frequency and low noise characteristics of SOI technology on plastic for flexible electronics. Solid-State Electron. 2013, 90, 73–78. [Google Scholar] [CrossRef]

- Philippe, J.; Lecavelier des Etangs-Levallois, A.; Berthome, M.; Robillard, J.F.; Gaquiere, C.; Danneville, F.; Gloria, D.; Raynaud, C.; Dubois, E. Application-oriented performance of RF CMOS technologies on flexible substrates. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 15.7.1–15.7.4. [Google Scholar]

- Philippe, J.; Bhaskar, A.; Okada, E.; Braud, F.; Robillard, J.F.; Danneville, F.; Raynaud, C.; Gloria, D.; Dubois, D. Thermal Analysis of Ultimately-Thinned-and-Transfer-Bonded CMOS on Mechanically Flexible Foils. IEEE J. Electron Devices Soc. 2019, 7, 973–978. [Google Scholar] [CrossRef]

- Lecavelier des Etangs-Levallois, A.; Chen, Z.; Lesecq, M.; Lepilliet, S.; Tagro, Y.; Danneville, F.; Robillard, J.F.; Hoel, V.; Troadec, D.; Gloria, D.; et al. A converging route towards very high frequency, mechanically flexible, and performance stable integrated electronics. J. Appl. Phys. 2013, 113, 153701. [Google Scholar] [CrossRef]

- Lecavelier des Etangs-Levallois, A.; Dubois, E.; Lesecq, M.; Danneville, F.; Poulain, L.; Tagro, Y.; Lepilliet, S.; Gloria, D.; Raynaud, C.; Troadec, D. 150-GHz RF SOI-CMOS technology in ultrathin regime on organic substrate. IEEE Electron Device Lett. 2011, 32, 1510–1512. [Google Scholar] [CrossRef]

- Cheng, J.; Liu, C.S.; Shang, S.; Liu, D.; Perrie, W.; Dearden, G.; Watkins, K. A review of ultrafast laser materials micromachining. J. Opt. Laser Technol. 2013, 46, 88–102. [Google Scholar] [CrossRef]

- Leyder, S.; Grojo, D.; Delaporte, P.; Marine, W.; Sentis, M.; Utéza, O. Non-linear absorption of focused femtosecond laser pulses at 1.3 μm inside silicon: Independence on doping concentration. J. Appl. Surface Sci. 2013, 278, 13–18. [Google Scholar] [CrossRef]

- Ghosh, A. The 5G mmWave Radio Revolution. Microw. J. 2016, 59, 22–36. [Google Scholar]

- Bhaskar, A.; Philippe, J.; Braud, F.; Okada, E.; Avramovic, V.; Robillard, J.F.; Durand, C.; Gloria, D.; Gaquiere, C.; Dubois, E. Large-area femtosecond laser milling of silicon employing trench analysis, paper submitted. J. Opt. Laser Technol. 2021, 138, 106866. [Google Scholar] [CrossRef]

- Bhaskar, A. Substrate Engineering Using Laser Micromachining for Improvement of RF Devices and Systems Integrated in SOI-CMOS Technology. Ph.D. Thesis, University of Lille, Lille, France, 2019. [Google Scholar]

- Gianesello, F.; Monroy, A.; Vialla, V.; Canderle, E.; Bertrand, G.; Buczko, M.; Coly, M.; Nowakowski, J.; Revil, N.; Rolland, L.; et al. Highly linear and sub 120 fs Ron × Coff 130 nm RF SOI technology targeting 5G carrier aggregation RF switches and FEM SOC. In Proceedings of the Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Austin, TX, USA, 24–27 January 2016; pp. 9–12. [Google Scholar]

- Bhaskar, A.; Philippe, J.; Avramovic, V.; Braud, F.; Robillard, J.F.; Durand, C.; Gloria, D.; Gaquiere, C.; Dubois, E. Substrate engineering of inductors on SOI for improvement of Q-factor and application in LNA. IEEE J. Electron Devices Soc. 2020, 8, 959–969. [Google Scholar] [CrossRef]

- Dubois, E.; Larrieu, G.; Valentin, R.; Breil, N.; Danneville, F. Introduction to Schottky-Barrier MOS Architectures: Concept, Challenges, Material Engineering and Device Integration. In Nanoscale CMOS: Innovative Materials, Modeling and Characterization; Balestra, F., Ed.; ISTE Ltd.: London, UK, 2010; Chapter 5; pp. 157–204. [Google Scholar]

- Tung, R.T. Recent advances in Schottky barrier concepts. Mater. Sci. Eng. 2001, R35, 1–138. [Google Scholar] [CrossRef]

- Li, X.; Zhang, Y. Flipping the CMOS Switch. IEEE Microw. Mag. 2010, 11, 86–96. [Google Scholar] [CrossRef]

- Zhang, Z.; Zhang, G.; Yu, K.; Lin, J.; Huang, L. Effects and contrasts of silicon-on-insulator floating-body and body-contacted field-effect transistors to the design of high-performance antenna switches. IET Microw. Antennas Propag. 2016, 10, 507–516. [Google Scholar] [CrossRef]

- Bhaskar, A.; Philippe, J.; Berthome, M.; Okada, E.; Robillard, J.F.; Gloria, D.; Gaquière, C.; Dubois, E. Large-area femtosecond laser ablation of Silicon to create membrane with high performance CMOS-SOI RF functions. In Proceedings of the IEEE Electronic System-Integration Technology Conference (ESTC), Dresden, Germany, 18–21 September 2018; pp. 1–6. [Google Scholar]

- Choi, P.; Goswami, S.; Radhakrishna, U.; Khanna, D.; Boon, C.C.; Lee, H.S.; Antoniadis, D.; Peh, L.S. A 5.9-GHz Fully Integrated GaN Frontend Design With Physics-Based RF Compact Model. IEEE Trans. Microw. Theory Tech. 2015, 63, 1163–1173. [Google Scholar] [CrossRef]

- Yu, B.; Ma, K.; Meng, F.; Yeo, K.S.; Shyam, P.; Zhang, S.; Verma, P.R. DC-30 GHz DPDT switch matrix design in high resistivity trap-rich SOI. IEEE Trans. Electron Devices 2017, 64, 3548–3554. [Google Scholar] [CrossRef]

- Yu, B.; Ma, K.; Meng, F.; Yeo, K.S.; Shyam, P.; Zhang, S.; Verma, P.R. Ultra-Wideband Low-Loss Switch Design in High-Resistivity Trap-Rich SOI With Enhanced Channel Mobility. IEEE Trans. Microw. Theory Tech. 2017, 65, 3937–3949. [Google Scholar] [CrossRef]

- Kazemi Esfeh, B.; Rack, M.; Makovejev, S.; Allibert, F.; Raskin, J.P. A SPDT RF Switch Small- and Large-Signal Characteristics on TR-HR SOI Substrates. IEEE J. Electron Devices Soc. 2018, 6, 543–550. [Google Scholar] [CrossRef]

| Reference | No. of Fingers | dif (µm) | W (µm) | Wfinger (µm) |

|---|---|---|---|---|

| CPL-A | 6 | 18.3 | 269.7 | 10.7 |

| CPL-B | 8 | 11.3 | 269.7 | 10.7 |

| Reference | ΔS21 (dB) (HR-SOI) | ΔS21 (dB) (TR-SOI) | ||

|---|---|---|---|---|

| 20 MHz | 5 GHz | 20 MHz | 5 GHz | |

| CPL-A | 15 | 6.8 | 10.7 | 7.5 |

| CPL-B | 13 | 5.2 | 8.9 | 5.2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bhaskar, A.; Philippe, J.; Okada, E.; Braud, F.; Robillard, J.-F.; Durand, C.; Gianesello, F.; Gloria, D.; Gaquière, C.; Dubois, E. Substrate-Induced Dissipative and Non-Linear Effects in RF Switches: Probing Ultimate Performance Based on Laser-Machined Membrane Suspension. Electronics 2022, 11, 2333. https://doi.org/10.3390/electronics11152333

Bhaskar A, Philippe J, Okada E, Braud F, Robillard J-F, Durand C, Gianesello F, Gloria D, Gaquière C, Dubois E. Substrate-Induced Dissipative and Non-Linear Effects in RF Switches: Probing Ultimate Performance Based on Laser-Machined Membrane Suspension. Electronics. 2022; 11(15):2333. https://doi.org/10.3390/electronics11152333

Chicago/Turabian StyleBhaskar, Arun, Justine Philippe, Etienne Okada, Flavie Braud, Jean-François Robillard, Cédric Durand, Frédéric Gianesello, Daniel Gloria, Christophe Gaquière, and Emmanuel Dubois. 2022. "Substrate-Induced Dissipative and Non-Linear Effects in RF Switches: Probing Ultimate Performance Based on Laser-Machined Membrane Suspension" Electronics 11, no. 15: 2333. https://doi.org/10.3390/electronics11152333

APA StyleBhaskar, A., Philippe, J., Okada, E., Braud, F., Robillard, J.-F., Durand, C., Gianesello, F., Gloria, D., Gaquière, C., & Dubois, E. (2022). Substrate-Induced Dissipative and Non-Linear Effects in RF Switches: Probing Ultimate Performance Based on Laser-Machined Membrane Suspension. Electronics, 11(15), 2333. https://doi.org/10.3390/electronics11152333