An 8-Gbps, Low-Jitter, Four-Channel Transmitter with a Fractional-Spaced Feed-Forward Equalizer

Abstract

:1. Introduction

2. Top Architecture

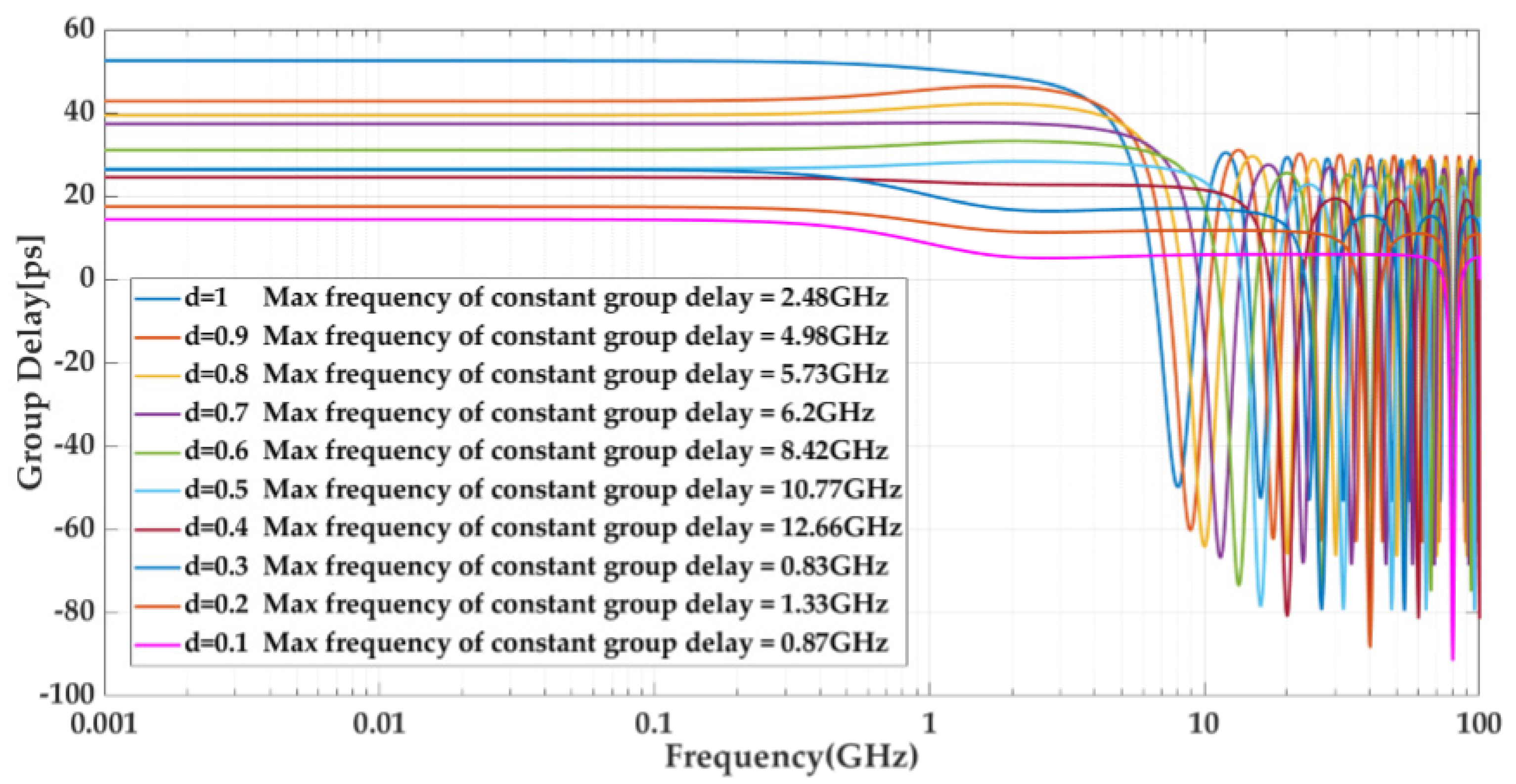

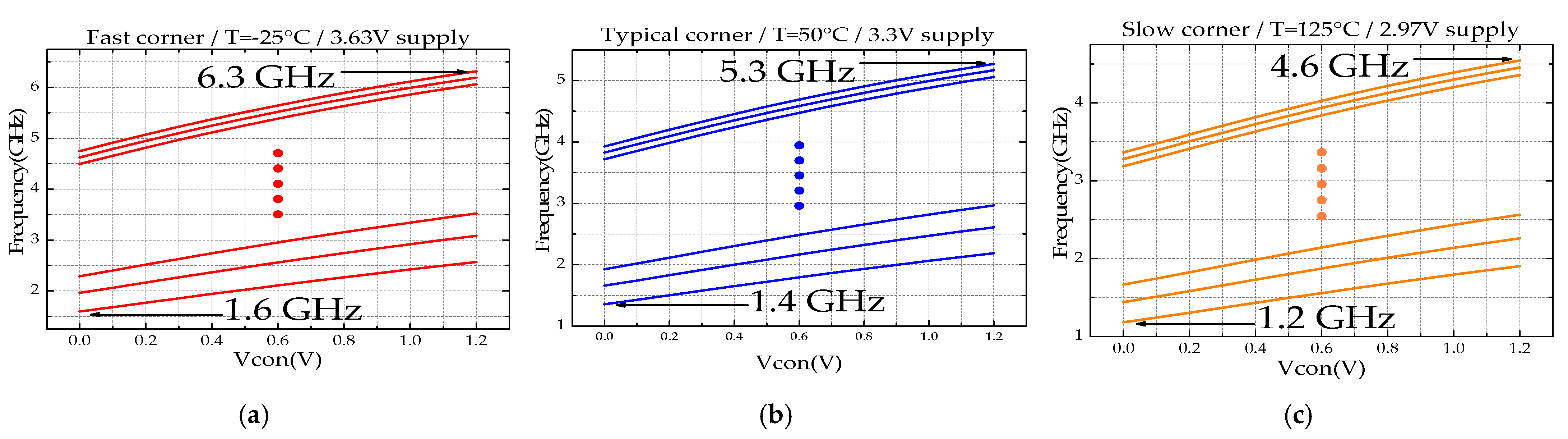

3. PLL Circuit Implementation

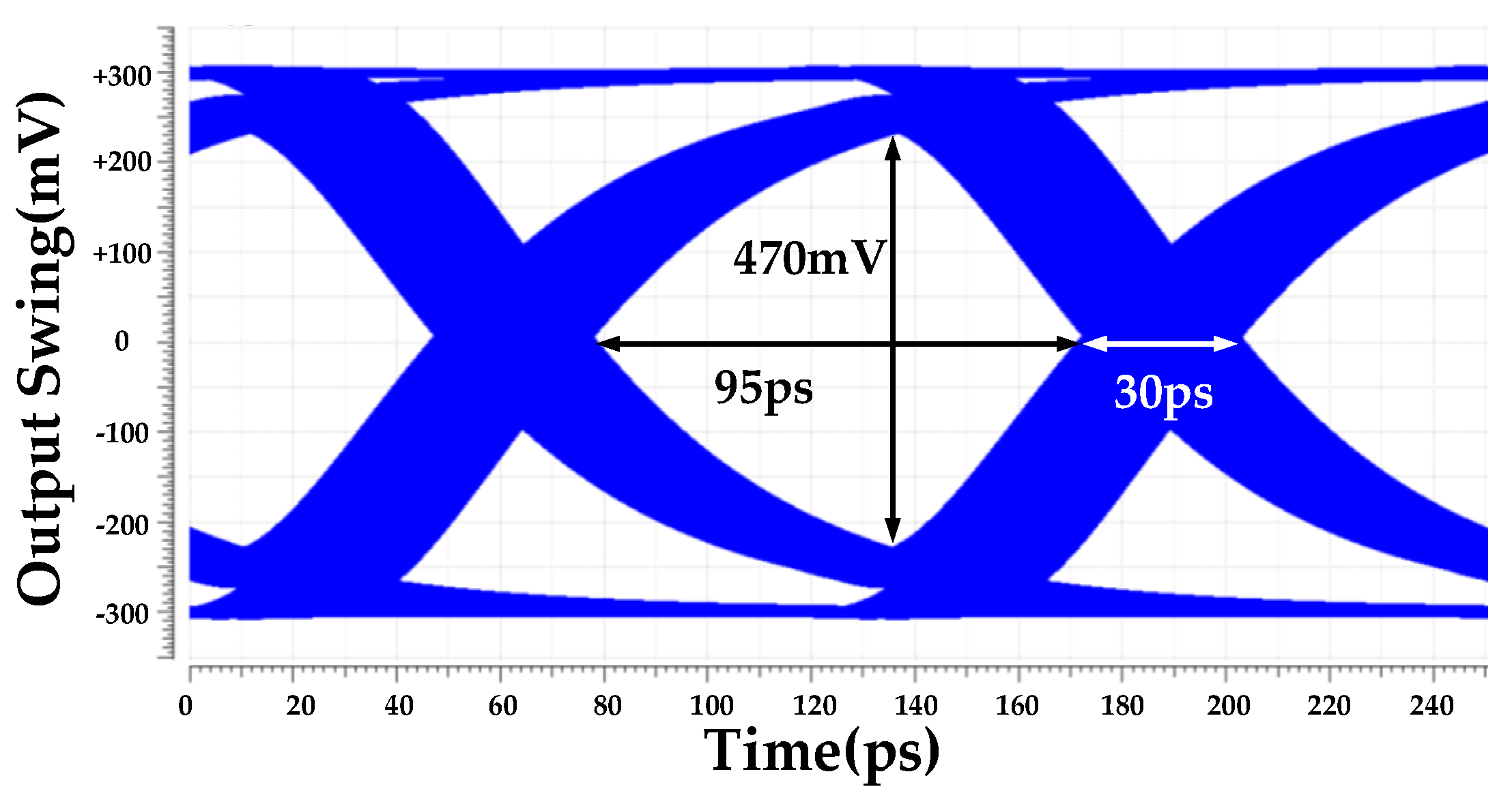

4. Driver Circuit Implementation

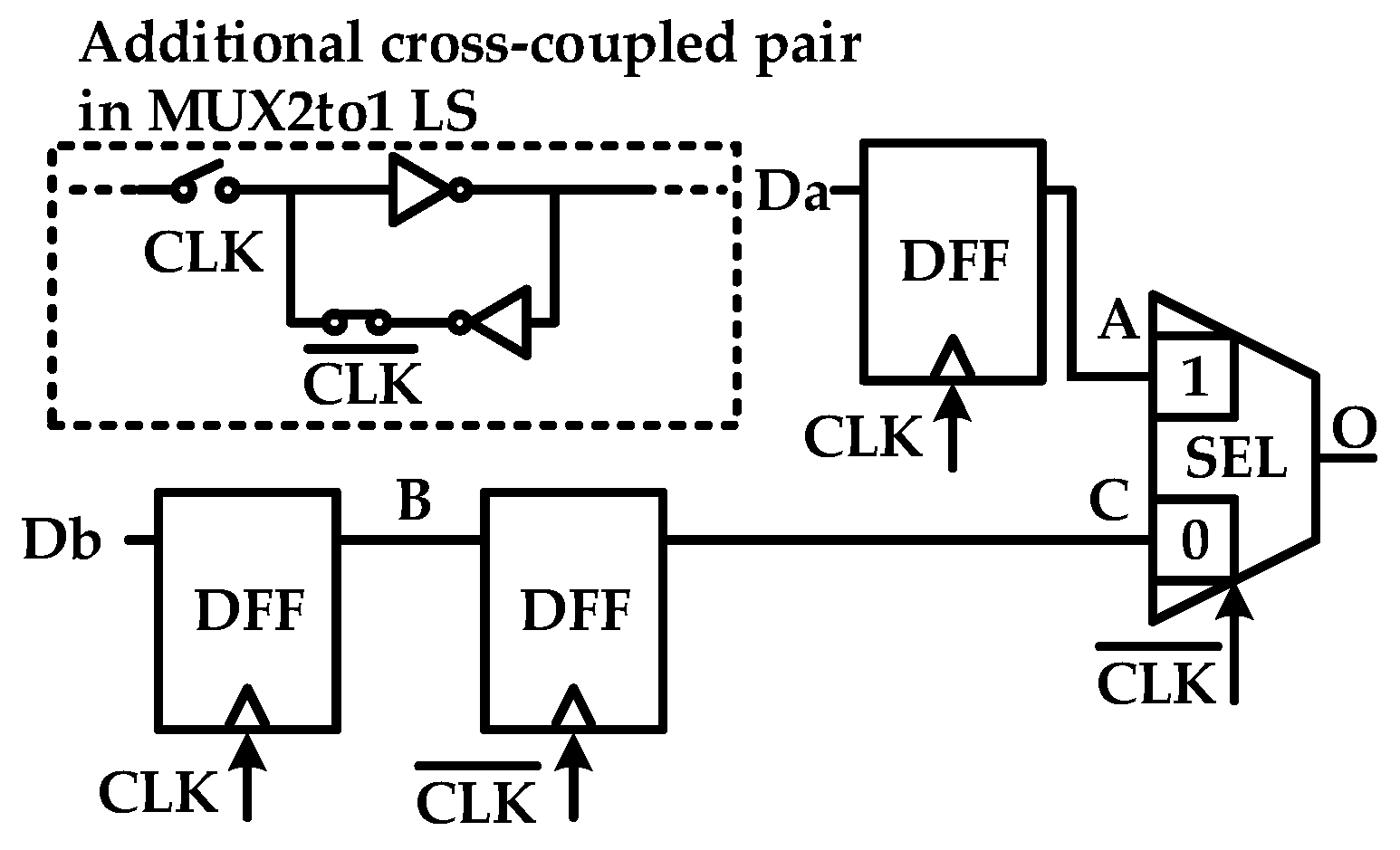

4.1. MUXs

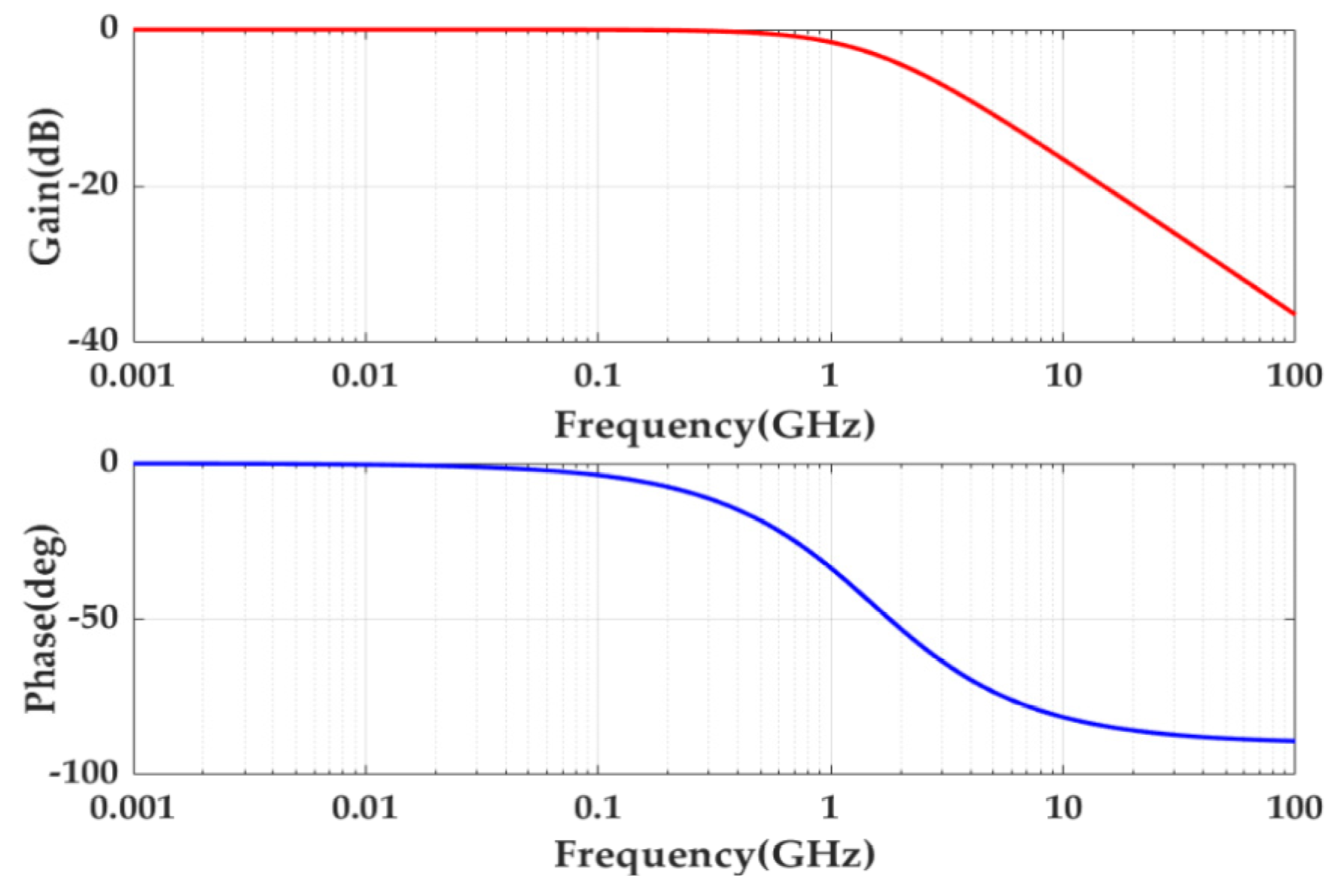

4.2. Clock FDC Architecture

4.3. Output Driver Circuit

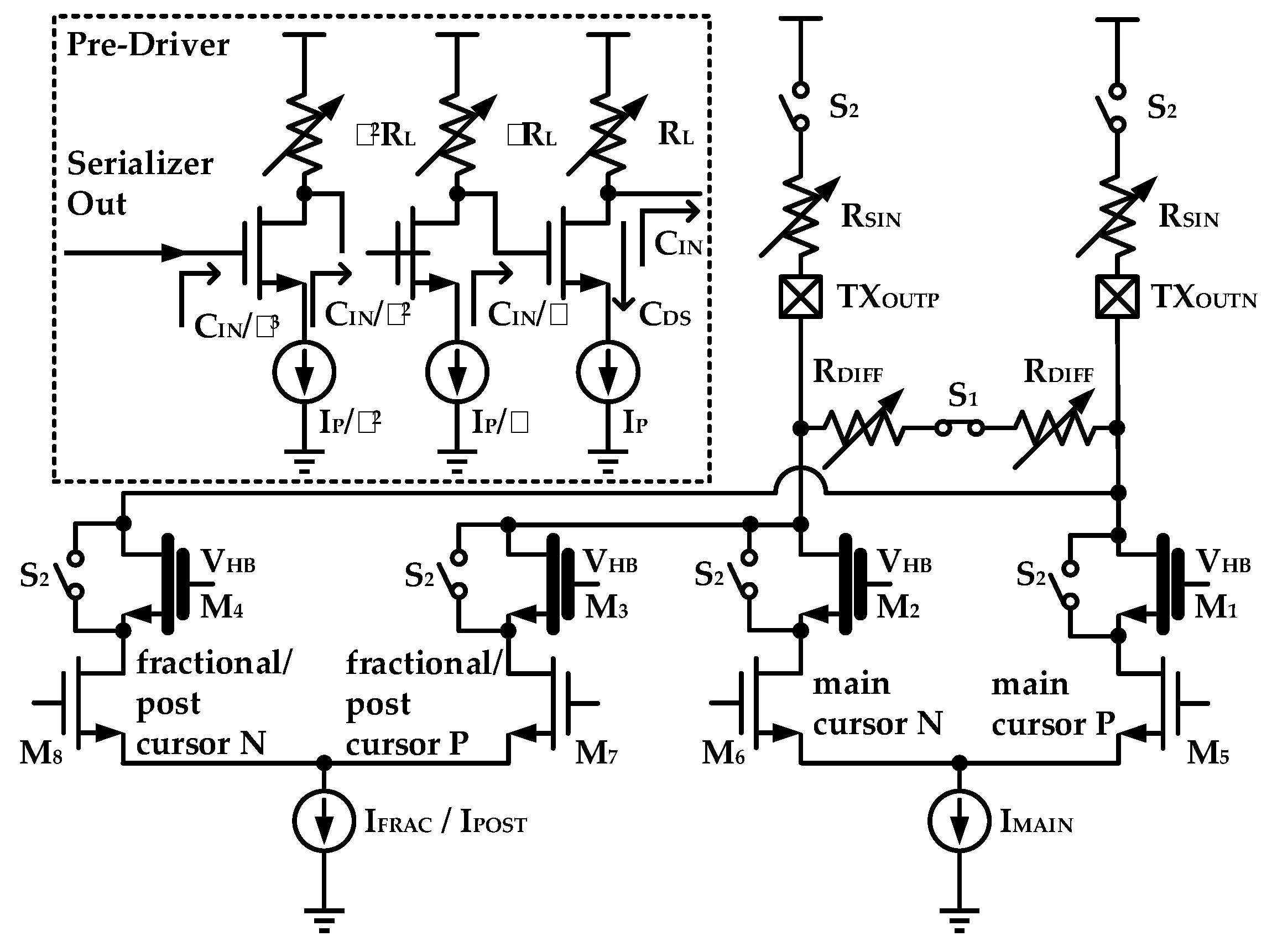

4.3.1. Predriver Circuit

4.3.2. Reconfigurable Output Driver Circuit

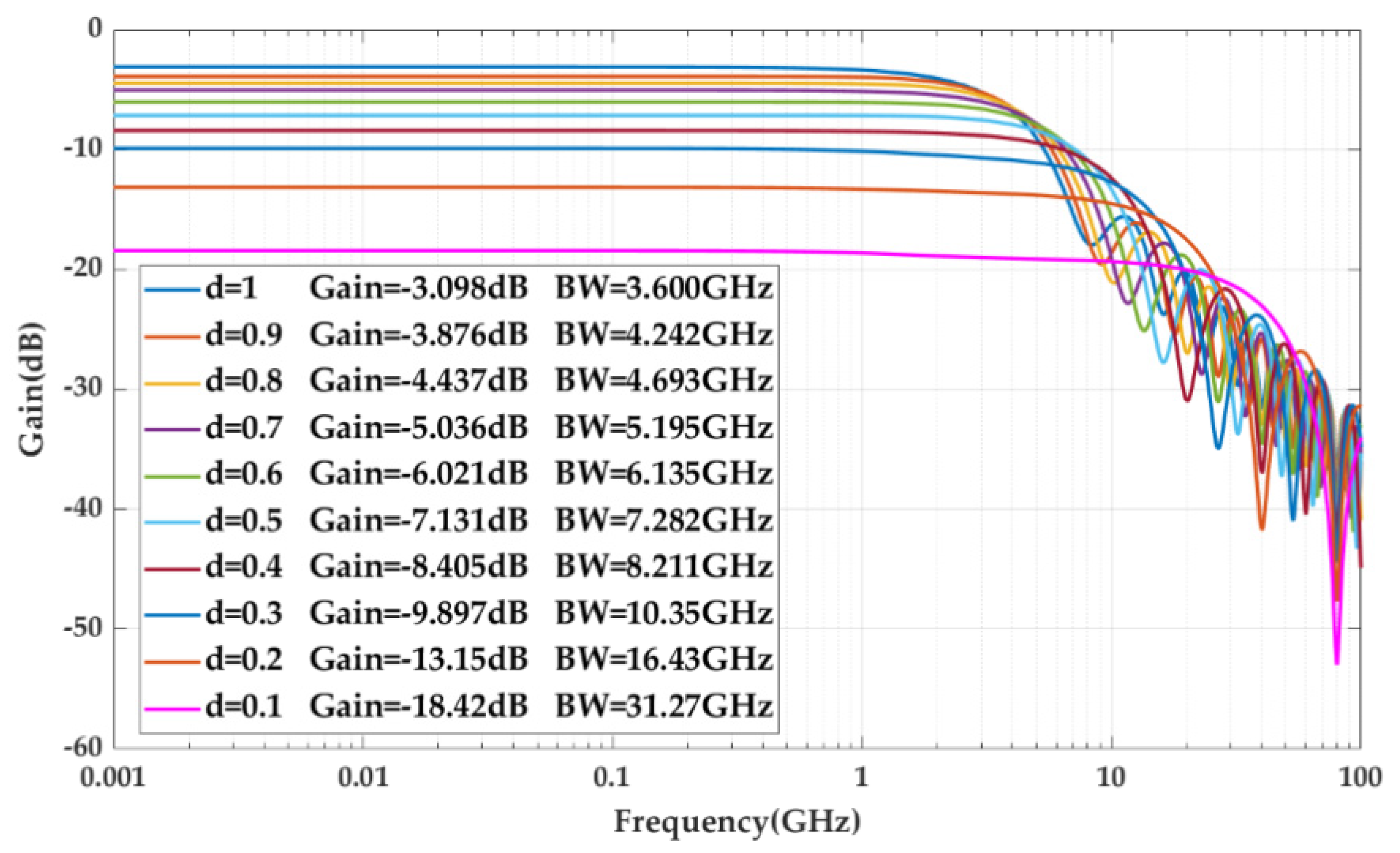

4.3.3. Three-Tap Fractional-Spaced FFE

5. Simulation Results and Discussions

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Choi, Y.H.; Seong, K.; Kim, B.; Sim, J.Y.; Park, H.J. All-synthesizable 6Gbps voltage-mode transmitter for serial link. In Proceedings of the 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), Toyama, Japan, 7–9 November 2016; IEEE: Toyama, Japan, 2016; pp. 245–248. [Google Scholar]

- Hyun, C.; Ko, H.; Chae, J.H.; Park, H.; Kim, S. A 20Gb/s dual-mode PAM4/NRZ single-ended transmitter with RLM compensation. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; IEEE: Sapporo, Japan, 2019; pp. 1–4. [Google Scholar]

- Ma, S.; Yu, H.; Gu, Q.J.; Ren, J. A 5–10-Gb/s 12.5-mW source synchronous I/O interface with 3-D flip chip package. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 66, 555–568. [Google Scholar] [CrossRef]

- Kwon, D.H.; Kim, M.; Kim, S.G.; Choi, W.Y. A low-power 40-Gb/s pre-emphasis PAM-4 transmitter with toggling serializers. IEEE Trans. Circuits Syst. II Express Br. 2020, 67, 430–434. [Google Scholar] [CrossRef]

- Wang, Z.; Choi, M.; Lee, K.; Park, K.; Liu, Z.; Biswas, A.; Han, J.; Du, S.; Alon, E. An Output Bandwidth Optimized 200-Gb/s PAM-4 100-Gb/s NRZ Transmitter With 5-Tap FFE in 28-nm CMOS. IEEE J. Solid-State Circuits 2021, 57, 21–31. [Google Scholar] [CrossRef]

- Geng, X.; Tian, Y.; Xiao, Y.; Ye, Z.; Xie, Q.; Wang, Z. A 25.8 GHz integer-N PLL with time-amplifying phase-frequency detector achieving 60 fs rms jitter, −52.8 dB FoM J, and Robust lock acquisition performance. In Proceedings of the 2022 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2022; IEEE: San Francisco, CA, USA, 2022; pp. 388–390. [Google Scholar]

- Sun, D.; Ding, R.; Bu, F.; Lu, S.; Liang, H.; Zhou, R.; Liu, S.; Zhu, Z. A Type-II Dual-Path PLL With Reference-Spur Suppression. IEEE Trans. Microw. Theory Tech. 2022, 70, 2280–2289. [Google Scholar] [CrossRef]

- Cai, C.; Zheng, X.; Chen, Y.; Wu, D.; Luan, J.; Lu, D.; Zhou, L.; Wu, J.; Liu, X. A 1.55-to-32-Gb/s four-lane transmitter with 3-tap feed forward equalizer and shared PLL in 28-nm CMOS. Electronics 2021, 10, 1873. [Google Scholar] [CrossRef]

- Bandarupalli, J.D.; Gautam, R.; Saxena, S. A reconfigurable 0.1–10 Gb/s voltage-mode transmitter with 0.2–1 V output swing. IEEE Solid State Circuits Lett. 2019, 2, 53–56. [Google Scholar] [CrossRef]

- Wang, T.; Zhou, M.; Liu, J.; Wang, Z.; Mo, J.; Chen, H.; Yu, F. A highly linear 10 Gb/s MOS current mode logic driver with large output voltage swing based on an active inductor. IEICE Electron. Express 2020, 17, 20200160. [Google Scholar] [CrossRef]

- Bai, X.; Zhao, J.; Zuo, S.; Zhou, Y. A 1.89 mW/Gbps SST transmitter with three-tap FFE and impedance calibration. IEICE Electron. Express 2019, 16, 20190356. [Google Scholar] [CrossRef] [Green Version]

- Norimatsu, T.; Kogo, K.; Komori, T.; Kohmu, N.; Yuki, F.; Kawamoto, T. A 100-Gbps 4-lane transceiver for 47-dB loss copper cable in 28-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3433–3443. [Google Scholar] [CrossRef]

- Peng, P.J.; Chen, Y.T.; Lai, S.T.; Huang, H.E. A 112-Gb/s PAM-4 Voltage-Mode Transmitter With Four-Tap Two-Step FFE and Automatic Phase Alignment Techniques in 40-nm CMOS. IEEE J. Solid-State Circuits 2020, 56, 2123–2131. [Google Scholar] [CrossRef]

- Momtaz, A.; Green, M.M. An 80 mW 40 Gb/s 7-tap T/2-spaced feed-forward equalizer in 65 nm CMOS. IEEE J. Solid-State Circuits 2010, 45, 629–639. [Google Scholar] [CrossRef]

- Dickson, T.O.; Ainspan, H.A.; Meghelli, M. A 1.8 pJ/b 56Gb/s PAM-4 transmitter with fractionally spaced FFE in 14nm CMOS. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 118–119. [Google Scholar]

- Guo, R.; Lu, Z.; Hu, S.; Yu, Q.; Rong, L.; Liu, Y. Design and verification of a charge pump in local oscillator for 5G applications. Electronics 2021, 10, 1009. [Google Scholar] [CrossRef]

- Chen, J.; Zhang, W.; Sun, Q.; Liu, L. An 8–12.5-GHz LC PLL with dual VCO and noise-reduced LDO regulator for multilane multiprotocol SerDes in 28-nm CMOS technology. Electronics 2021, 10, 1686. [Google Scholar] [CrossRef]

- Zou, W.; Ren, D.; Zou, X. A wideband low-jitter PLL with an optimized ring-VCO. IEICE Electron. Express 2020, 17, 20190703. [Google Scholar] [CrossRef] [Green Version]

- Chen, Y.; Gong, J.; Staszewski, R.B.; Babaie, M. A fractional-N digitally intensive PLL achieving 428-fs jitter and <-54-dBc spurs under 50-mVpp supply ripple. IEEE J. Solid-State Circuits 2021, 57, 1749–1764. [Google Scholar] [CrossRef]

- Park, K.; Oh, T. 12 Gbit/s three-tap FFE half-rate transmitter with low jitter clock buffering scheme. Electron. Lett. 2019, 55, 1078–1080. [Google Scholar] [CrossRef]

- Fiedler, A.; Krishnan, S. A scalable 7.0-Gb/s multi-lane NRZ transceiver with a 1/10th-rate forwarded clock in 0.13 um CMOS. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 1 May 2016; pp. 2330–2333. [Google Scholar]

- Zheng, X.; Ding, H.; Zhao, F.; Wu, D.; Zhou, L.; Wu, J.; Lv, F.; Wang, J.; Liu, X. A 50–112-Gb/s PAM-4 transmitter with a fractional-spaced FFE in 65-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 1864–1876. [Google Scholar] [CrossRef]

- Ding, H.; Zheng, X.; Wu, D.; Zhou, L.; Wu, J.; Lv, F.; Wang, J.; Liu, X. A 112-Gb/s PAM-4 Transmitter With a 2-Tap Fractional-Spaced FFE in 65-nm CMOS. IEEE Solid State Circuits Lett. 2019, 2, 195–198. [Google Scholar] [CrossRef]

- Buckwalter, J.F.; Hajimiri, A. Analysis and equalization of data-dependent jitter. IEEE J. Solid-State Circuits 2006, 41, 607–620. [Google Scholar] [CrossRef] [Green Version]

- Yoon, K.; Park, H.; Choi, Y.; Sim, J.; Choi, J.; Kim, C. A 4.5 Gb/s/pin transceiver with hybrid inter-symbol interference and far-end crosstalk equalization for next-generation high-bandwidth memory interface. Electron. Lett. 2022, 58, 420–422. [Google Scholar] [CrossRef]

| Process | Supply Voltage (V) | Temperature (°C) | Valid Eye Height 1 | Eye Width (UI) |

|---|---|---|---|---|

| Typical | −25 | 0.81 | 0.76 | |

| 1.2 | 50 | 0.78 | 0.76 | |

| 125 | 0.74 | 0.74 | ||

| Fast | −25 | 0.83 | 0.77 | |

| 1.32 | 50 | 0.79 | 0.76 | |

| 125 | 0.78 | 0.76 | ||

| Slow | −25 | 0.75 | 0.72 | |

| 1.08 | 50 | 0.72 | 0.72 | |

| 125 | 0.68 | 0.71 |

| This Work 1 | [1] 2 | [2] 2 | [9] 2 | [11] 2 | |

|---|---|---|---|---|---|

| CMOS Technology (nm) | 55 | 65 | 65 | 65 | 55 |

| Data Rate (Gbps) | 8 | 6 | 10 | 10 | 8 |

| Power 3 (mW) | 29.2 | 33.6 | 72.0 | 36.0 | 15.1 |

| Energy Efficiency 4 (mW/Gbps) | 3.65 | 5.60 | 7.20 | 3.60 | 1.89 |

| Eye Width | 0.71 | 0.65 | 0.70 | 0.58 | 0.52 |

| Valid Eye Height | 0.68 | 0.32 | 0.63 | 0.35 | 0.52 |

| FFE Tap | 3 | 2 | 4 | 2 | 3 |

| Type of FFE | Fractional-spaced | Baud-spaced | Baud-spaced | Baud-spaced | Baud-spaced |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, Y.; Yang, H.; Chen, W.; Yang, Z.; Qiao, S. An 8-Gbps, Low-Jitter, Four-Channel Transmitter with a Fractional-Spaced Feed-Forward Equalizer. Electronics 2022, 11, 1768. https://doi.org/10.3390/electronics11111768

Huang Y, Yang H, Chen W, Yang Z, Qiao S. An 8-Gbps, Low-Jitter, Four-Channel Transmitter with a Fractional-Spaced Feed-Forward Equalizer. Electronics. 2022; 11(11):1768. https://doi.org/10.3390/electronics11111768

Chicago/Turabian StyleHuang, Yibin, Haohan Yang, Wenya Chen, Zhong Yang, and Shushan Qiao. 2022. "An 8-Gbps, Low-Jitter, Four-Channel Transmitter with a Fractional-Spaced Feed-Forward Equalizer" Electronics 11, no. 11: 1768. https://doi.org/10.3390/electronics11111768

APA StyleHuang, Y., Yang, H., Chen, W., Yang, Z., & Qiao, S. (2022). An 8-Gbps, Low-Jitter, Four-Channel Transmitter with a Fractional-Spaced Feed-Forward Equalizer. Electronics, 11(11), 1768. https://doi.org/10.3390/electronics11111768