A Compact Transformer-Based E-Band CMOS Power Amplifier with Enhanced Efficiencies of 15.6% PAE1dB and 6.5% PAE at 6 dB Power Back-Off

Abstract

:1. Introduction

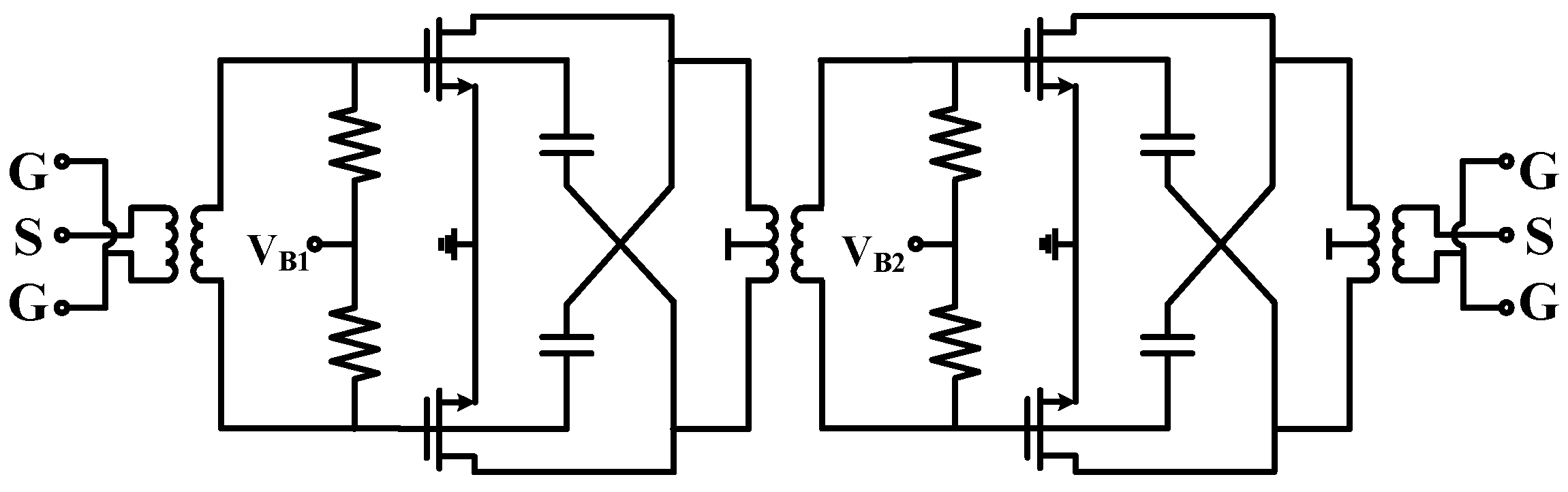

2. E-Band PA Circuit Topology

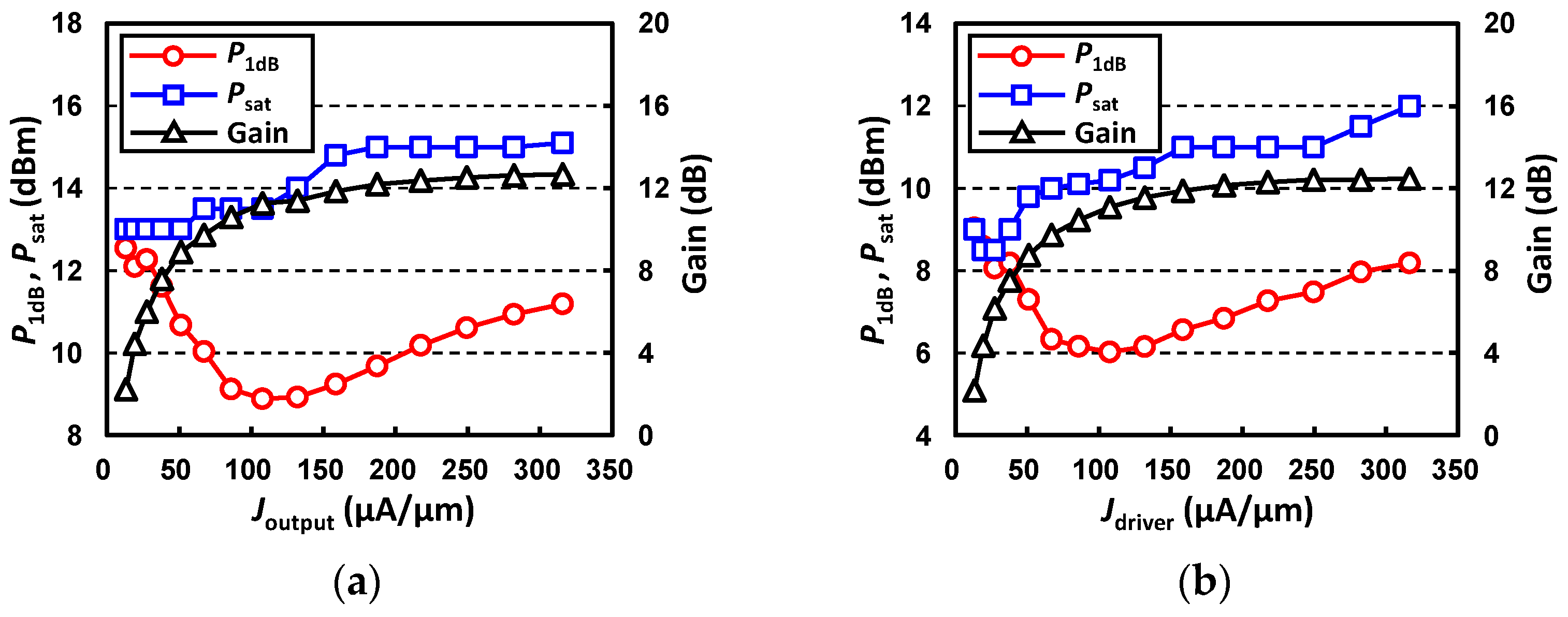

3. PA Circuit Design with Transformer-Based Matching Network

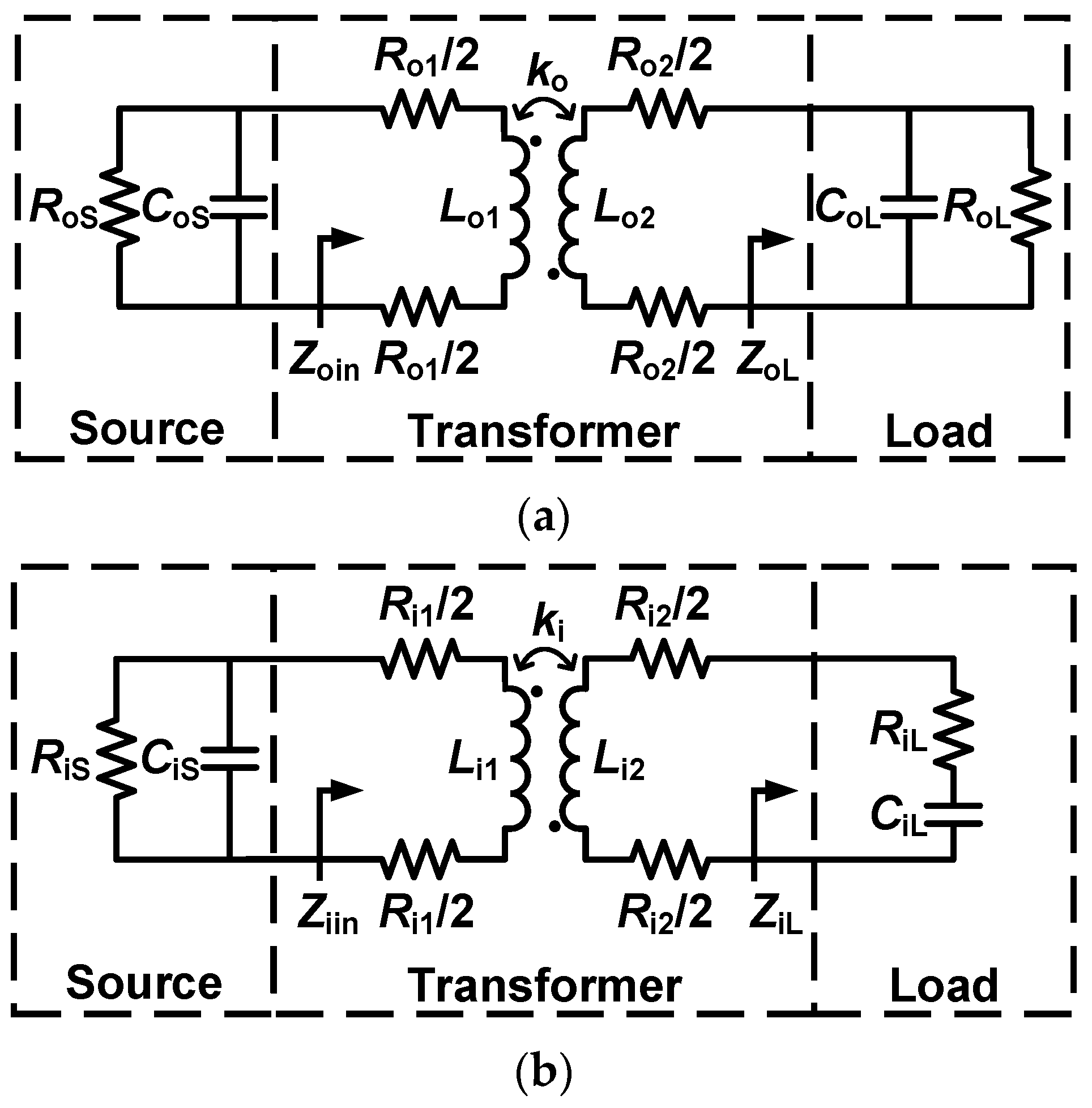

3.1. Impedance Formulations for TMN

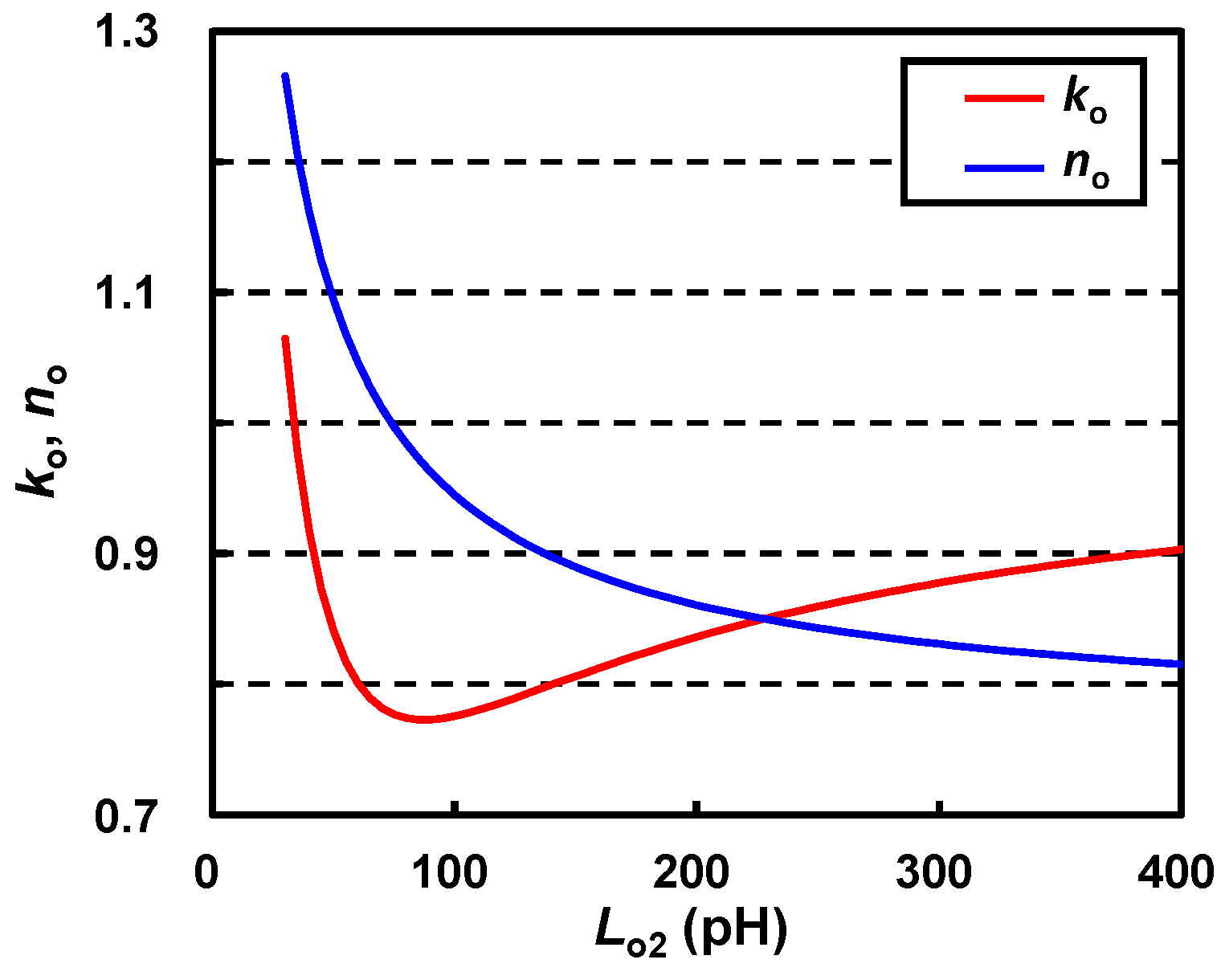

3.2. Design of Output Matching Network

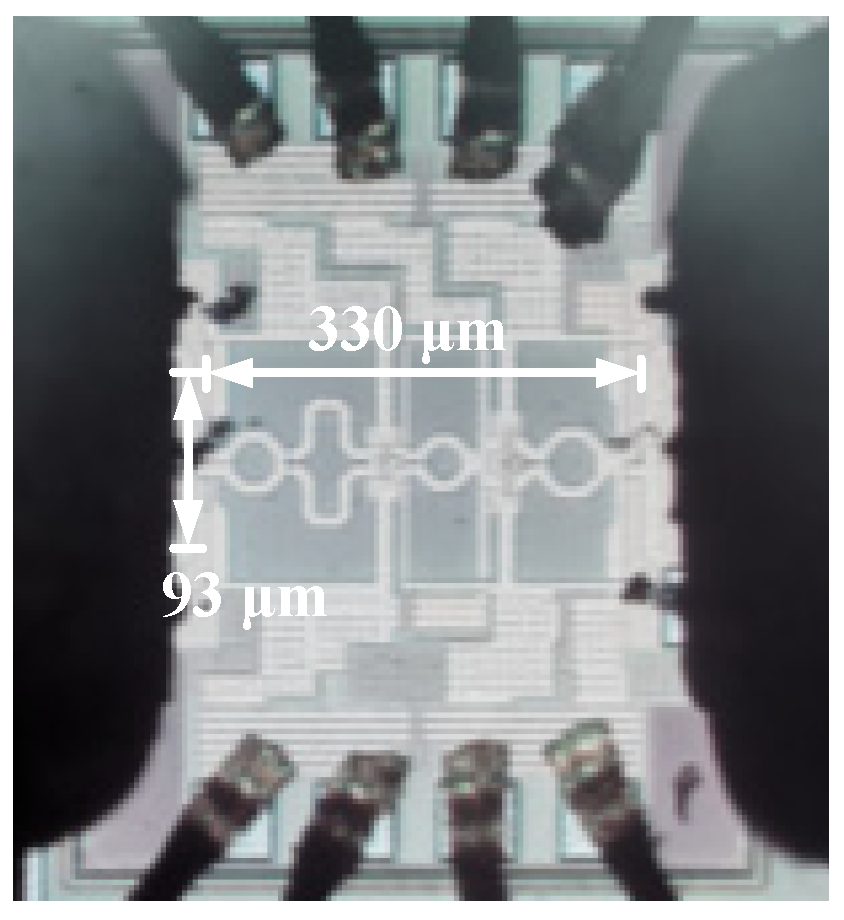

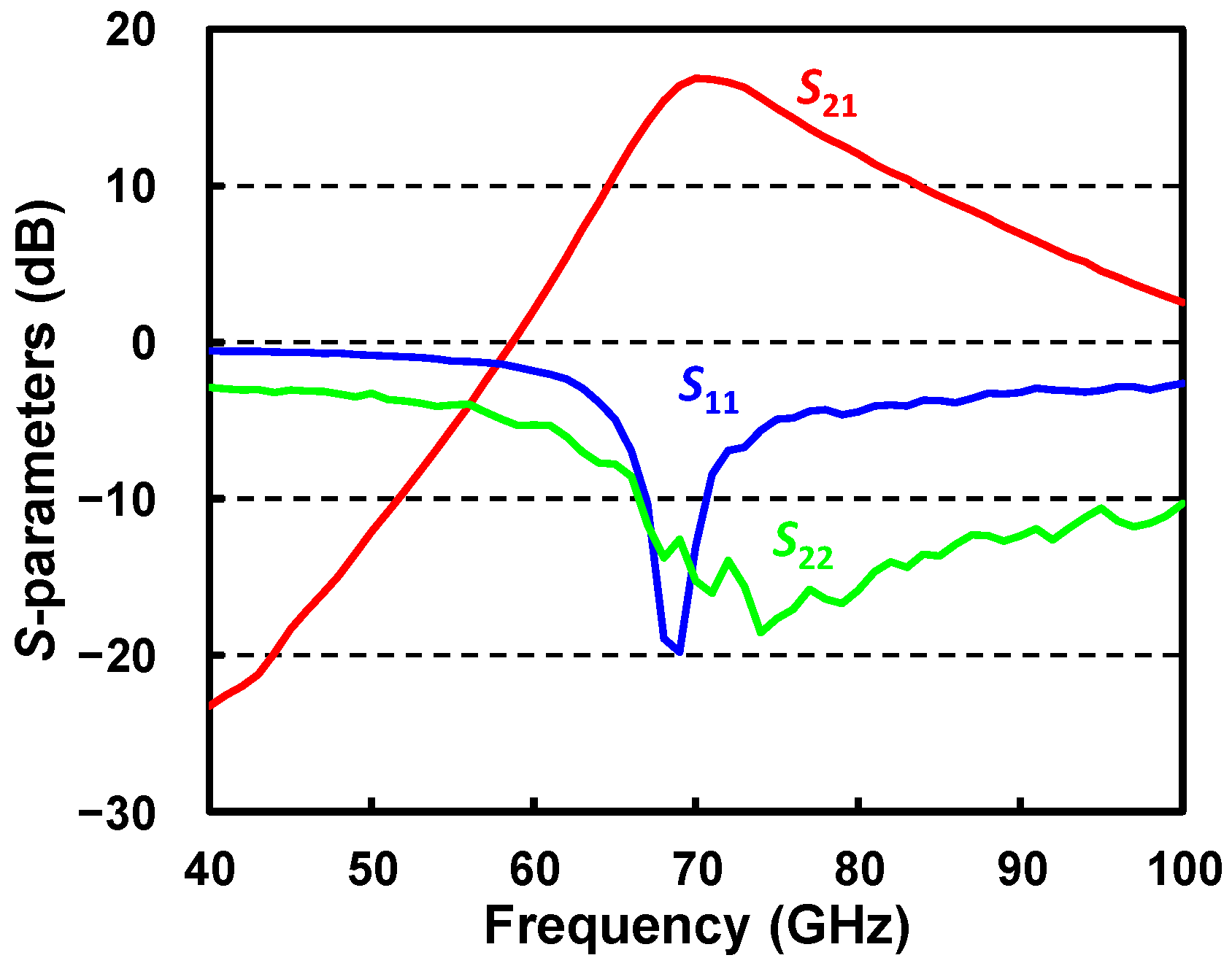

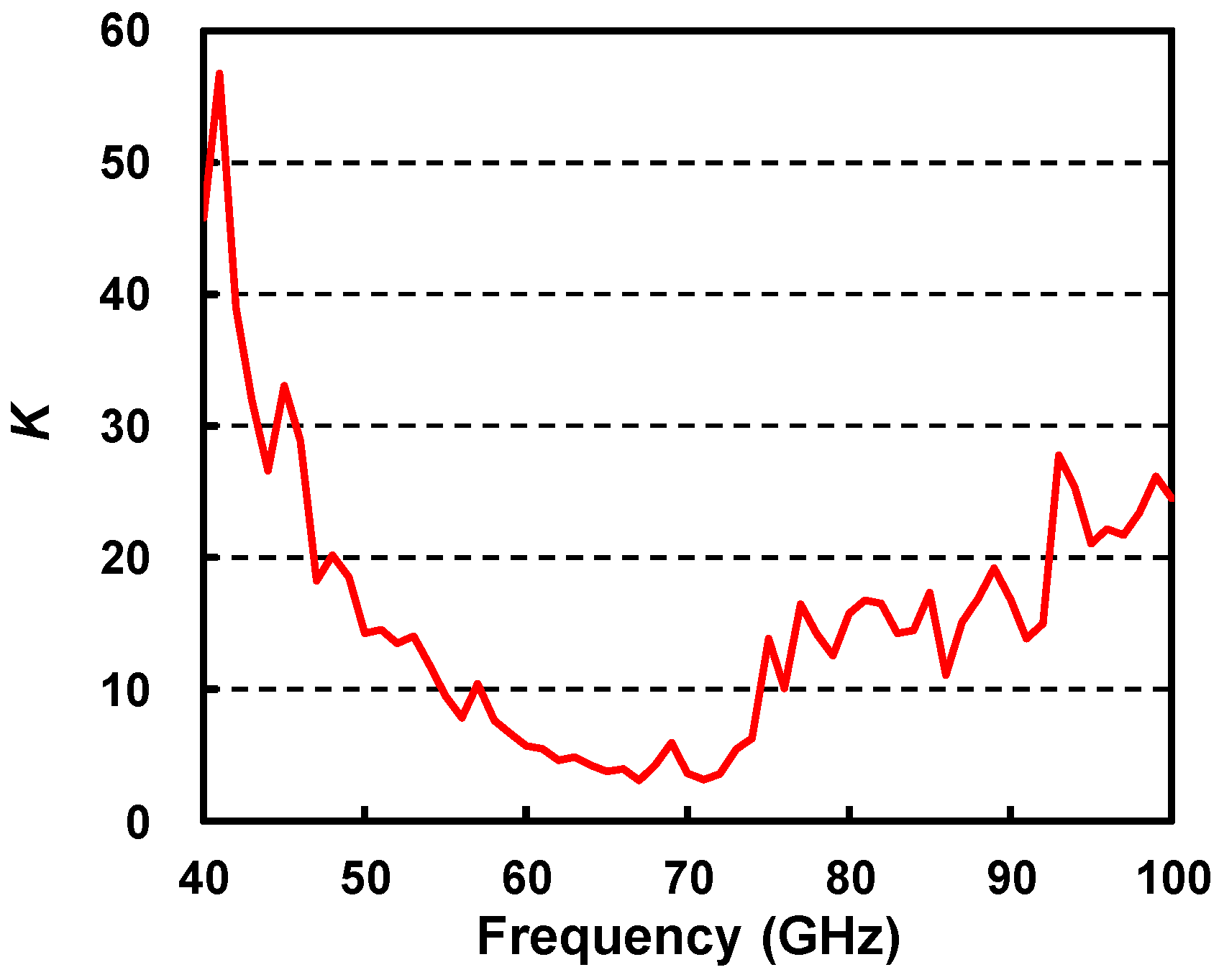

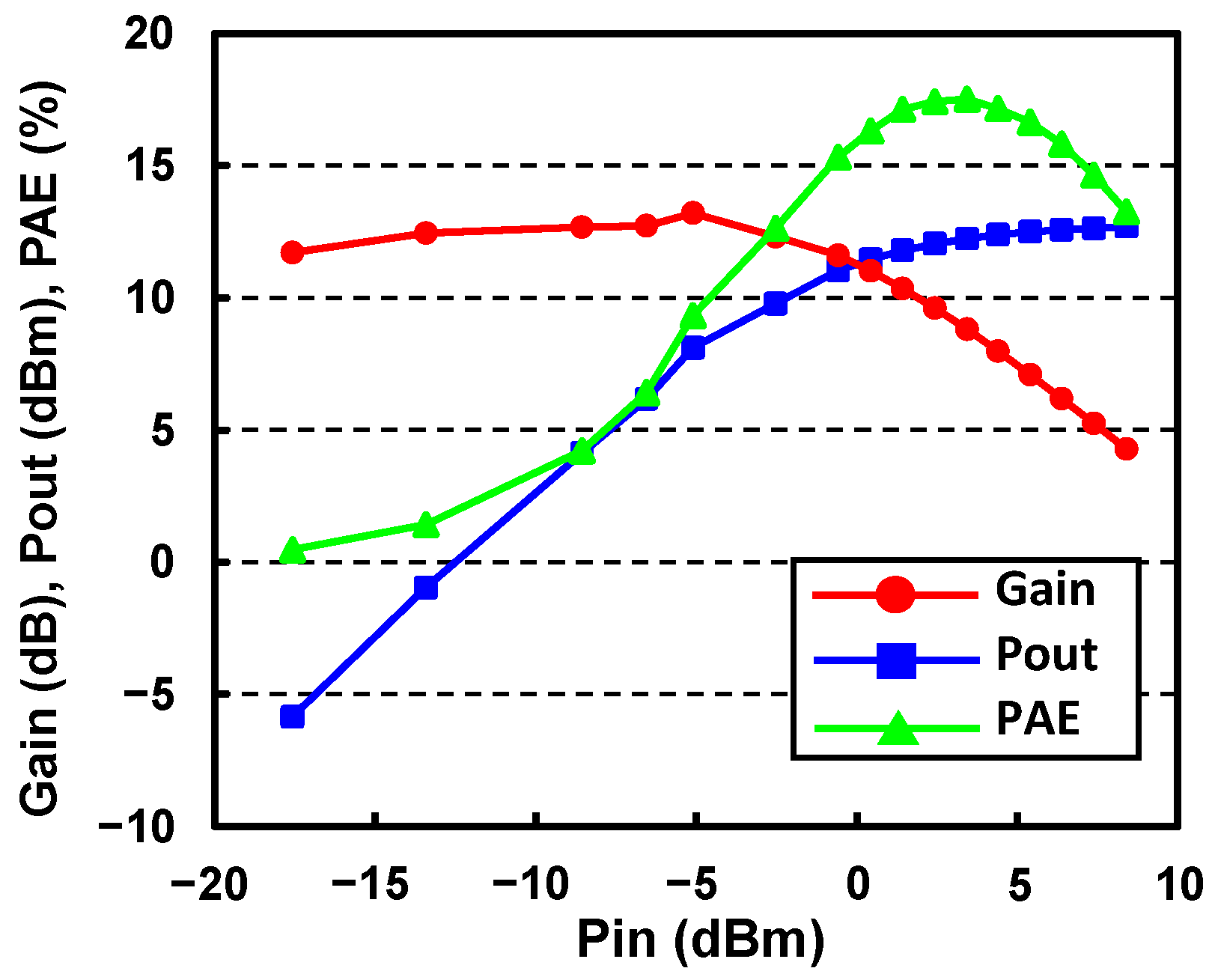

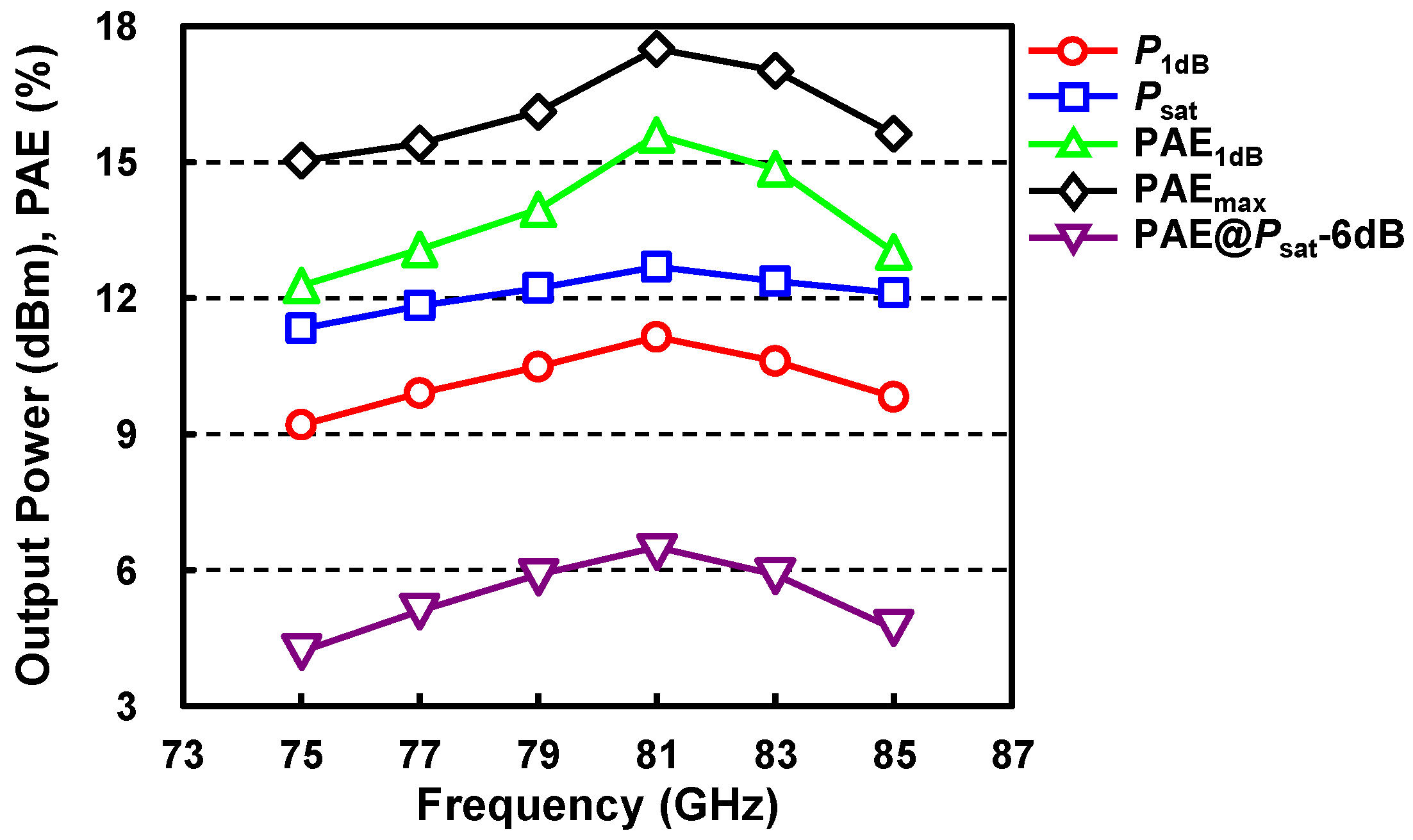

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chen, L.; Zhang, L.; Zhang, L.; Wang, Y. A Compact E-Band PA with 22.37% PAE 14.29 dBm Output Power and 26 dB Power Gain with Efficiency Enhancement at Power Back-off. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium, Boston, MA, USA, 2–4 June 2019; pp. 183–186. [Google Scholar]

- Celik, U.; Reynaert, P. An E-Band Compact Power Amplifier for Future Array-Based Backhaul Networks in 22 nm FD-SOI. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium, Boston, MA, USA, 2–4 June 2019; pp. 187–190. [Google Scholar]

- Callender, S.; Pellerano, S.; Hull, C. An E-Band Power Amplifier with 26.3% PAE and 24-GHz Bandwidth in 22-nm FinFET CMOS. IEEE J. Solid-State Circuits 2019, 54, 1266–1273. [Google Scholar] [CrossRef]

- Callender, S.; Pellerano, S.; Hull, C. A 73GHz PA for 5G Phased Arrays in 14nm FinFET CMOS. In Proceedings of the 2017 IEEE Radio Frequency Integrated Circuits Symposium, Honolulu, HI, USA, 4–6 June 2017; pp. 402–405. [Google Scholar]

- Chen, L.; Zhang, L.; Wang, Y.; Yu, Z. A Compact E-Band Power Amplifier with Gain-Boosting and Efficiency Enhancement. IEEE Trans. Microw. Theory Tech. 2020, 68, 4620–4630. [Google Scholar] [CrossRef]

- Zhao, J.; Rahimi, E.; Svelto, F.; Mazzanti, A. A SiGe BiCMOS E-Band Power Amplifier with 22% PAE at 18dBm OP1dB and 8.5% at 6 dB Back-Off Leveraging Current Clamping in a Common-Base Stage. In Proceedings of the 2017 IEEE International Solid State Circuits Conference, San Francisco, CA, USA, 5–9 February 2017; pp. 42–43. [Google Scholar]

- Ye, W.; Ma, K.; Yeo, K.; Zou, Q. A 65 nm CMOS Power Amplifier with Peak PAE above 18.9% From 57 to 66 GHz Using Synthesized Transformer-Based Matching Network. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2533–2543. [Google Scholar] [CrossRef]

- Zhao, D.; Reynaert, P. A 60-GHz Dual-Mode Class AB Power Amplifier in 40-nm CMOS. IEEE J. Solid-State Circuits 2013, 48, 2323–2337. [Google Scholar] [CrossRef]

- Zhao, D.; Reynaert, P. An E-Band Power Amplifier with Broadband Parallel-Series Power Combiner in 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2015, 63, 683–690. [Google Scholar] [CrossRef]

- Wagner, E.; Rebeiz, G. Single and Power-Combined Linear E-Band Power Amplifiers in 0.12-μm SiGe with 19-dBm Average Power 1-GBaud 64-QAM Modulated Waveforms. IEEE Trans. Microw. Theory Tech. 2019, 67, 1531–1543. [Google Scholar] [CrossRef]

- Kaymaksut, E.; Zhao, D.; Reynaert, P. Transformer-Based Doherty Power Amplifiers for mm-Wave Applications in 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2015, 63, 1186–1192. [Google Scholar] [CrossRef]

- Zhao, D.; Kulkarni, S.; Reynaert, P. A 60-GHz Outphasing Transmitter in 40-nm CMOS. IEEE J. Solid-State Circuits 2012, 47, 3172–3183. [Google Scholar] [CrossRef]

- Hookari, M.; Roshani, S.; Roshani, S. High-efficiency balanced power amplifier using miniaturized harmonics suppressed coupler. Int. J. RF Microw. Comput.-Aided Eng. 2020, 30, e22252. [Google Scholar] [CrossRef]

- Yu, C.; Feng, J.; Zhao, D. A 28-GHz CMOS Broadband Single-Path Power Amplifier with 17.4-dBm P-1dB for 5G Phased-Array. In Proceedings of the 44th European Solid-State Circuits Conference (ESSCIRC), Dresden, Germany, 3–6 September 2018; pp. 38–41. [Google Scholar]

- Park, B.; Jin, S.; Jeong, D.; Kim, J.; Cho, Y.; Moon, K.; Kim, B. Highly Linear mm-Wave CMOS Power Amplifier. IEEE Trans. Microw. Theory Tech. 2016, 64, 4535–4544. [Google Scholar] [CrossRef]

- Nocera, C.; Papotto, G.; Cavarra, A.; Ragonese, E.; Palmisano, G. A 13.5-dBm 1-V Power Amplifier for W-Band Automotive Radar Applications in 28-nm FD-SOI CMOS Technology. IEEE Trans. Microw. Theory Tech. 2021, 69, 1654–1660. [Google Scholar] [CrossRef]

- Mosalam, H.; Xiao, W.; Pan, Q. A 50-82 GHz broadband cascode-based power amplifier in 40 nm CMOS. Int. J. Electron. Commun. 2021, 137, 153824. [Google Scholar] [CrossRef]

- Xi, T.; Huang, S.; Guo, S.; Gui, P.; Huang, D.; Chakraborty, S. High-Efficiency E-Band Power Amplifiers and Transmitter Using Gate Capacitance Linearization in a 65-nm CMOS Process. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 234–238. [Google Scholar] [CrossRef]

- Khalaf, K.; Vidojkovic, V.; Long, J.; Wambacq, P. A 6x-Oversampling 10GS/s 60GHz Polar Transmitter with 15.3% Average PA Efficiency in 40nm CMOS. In Proceedings of the 44th European Solid-State Circuits Conference (ESSCIRC), Graz, Austria, 14–18 September 2015; pp. 348–351. [Google Scholar]

| Ref. Year | Tech. | Freq. (GHz) | Supply Voltage (V) | Num. of Stages | Gain (dB) | P1dB (dBm) | Psat (dBm) | PAE1dB (%) | PAEmax (%) | PAE@Psat- 6 dB (%) | Core Area (mm2) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| [2], 2019 | 22 nm FD-SOI | 76 | 2 | 2 | 17.8 | 13.3 | 17.8 | 8.1 * | 17.3 | 4.3 * | 0.02 |

| [3], 2019 | 22 nm Fin-FET | 75 | 1 | 2 | 16.6 | 5.7 | 12.8 | 11.6 | 26.3 | - | 0.054 |

| [5], 2020 | 65 nm CMOS | 73 | 1.2 | 3 | 26–31 | 12.0 | 14.3 | 13.3 | 22.4 | 5.6 | 0.025 |

| [16], 2021 | 28 nm FD-SOI | 77 | 1 | 3 | 26.5 | 10.0 | 13.5 | 8.0 * | 14.5 | - | 0.15 |

| [17], 2021 | 40 nm CMOS | 70 | 2 | 2 | 10.9 | 10.8 | 14.0 | 11.0 | 15.0 | 4.0 * | 0.075 |

| [18], 2017 | 65 nm CMOS | 75 | 1.3 | 3 | 21.4 | 14.6 | 17.3 | 11.2 * | 18.9 | 5.0 | 0.09 |

| [19], 2015 | 28 nm CMOS | 60 | 0.9 | 3 | 24.3 | 7.4 | 10.8 | - | 22.4 ** | 5.3 * | 0.18 |

| This work | 40 nm CMOS | 81 | 1 | 2 | 12.5 | 11.2 | 12.7 | 15.6 | 17.5 | 6.5 | 0.031 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wei, Z.; Huang, F.; Zhang, Y.; Tang, X.; Jiang, N. A Compact Transformer-Based E-Band CMOS Power Amplifier with Enhanced Efficiencies of 15.6% PAE1dB and 6.5% PAE at 6 dB Power Back-Off. Electronics 2022, 11, 1679. https://doi.org/10.3390/electronics11111679

Wei Z, Huang F, Zhang Y, Tang X, Jiang N. A Compact Transformer-Based E-Band CMOS Power Amplifier with Enhanced Efficiencies of 15.6% PAE1dB and 6.5% PAE at 6 dB Power Back-Off. Electronics. 2022; 11(11):1679. https://doi.org/10.3390/electronics11111679

Chicago/Turabian StyleWei, Zhennan, Fengyi Huang, Youming Zhang, Xusheng Tang, and Nan Jiang. 2022. "A Compact Transformer-Based E-Band CMOS Power Amplifier with Enhanced Efficiencies of 15.6% PAE1dB and 6.5% PAE at 6 dB Power Back-Off" Electronics 11, no. 11: 1679. https://doi.org/10.3390/electronics11111679

APA StyleWei, Z., Huang, F., Zhang, Y., Tang, X., & Jiang, N. (2022). A Compact Transformer-Based E-Band CMOS Power Amplifier with Enhanced Efficiencies of 15.6% PAE1dB and 6.5% PAE at 6 dB Power Back-Off. Electronics, 11(11), 1679. https://doi.org/10.3390/electronics11111679