Two-Path 77-GHz PA in 28-nm FD-SOI CMOS for Automotive Radar Applications

Abstract

:1. Introduction

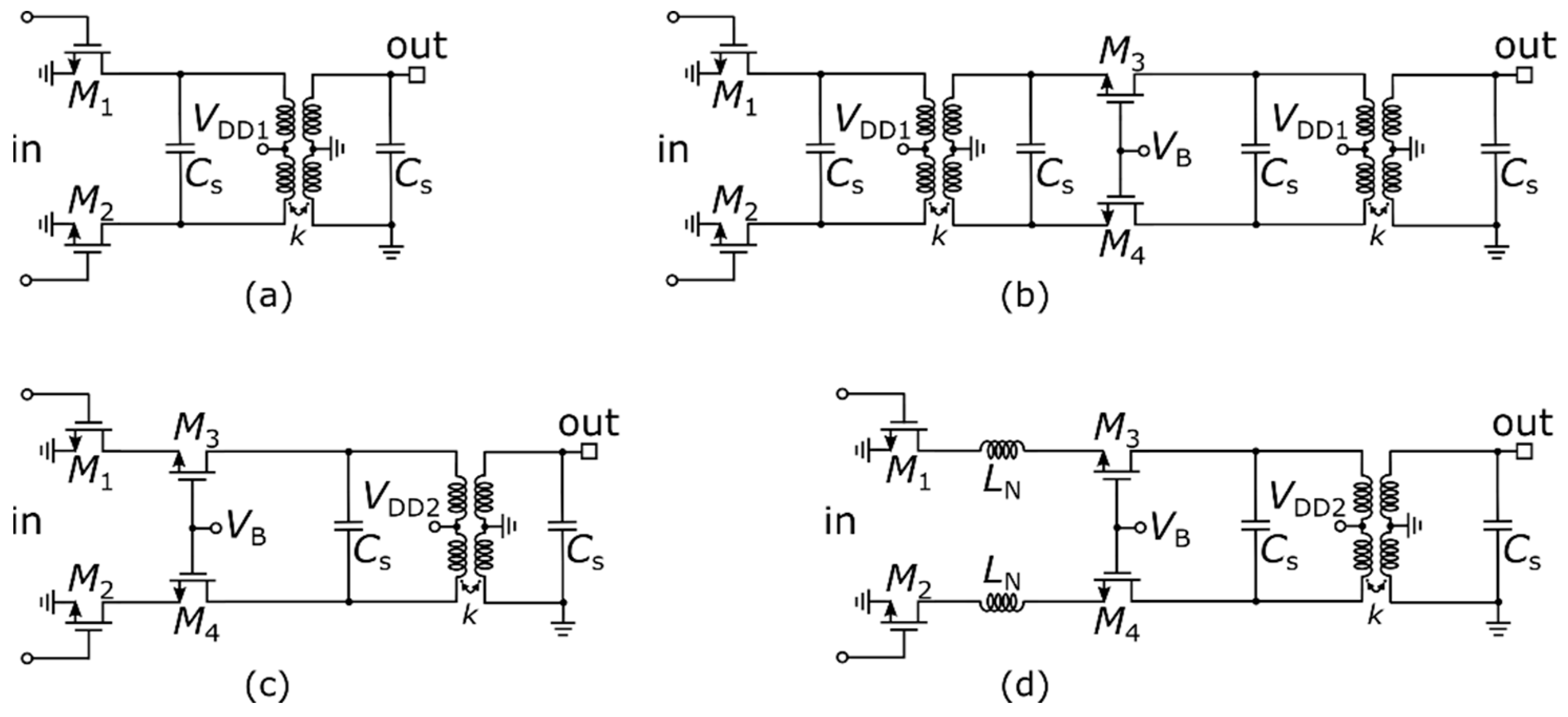

2. Power Stage Architecture

3. Circuit Description

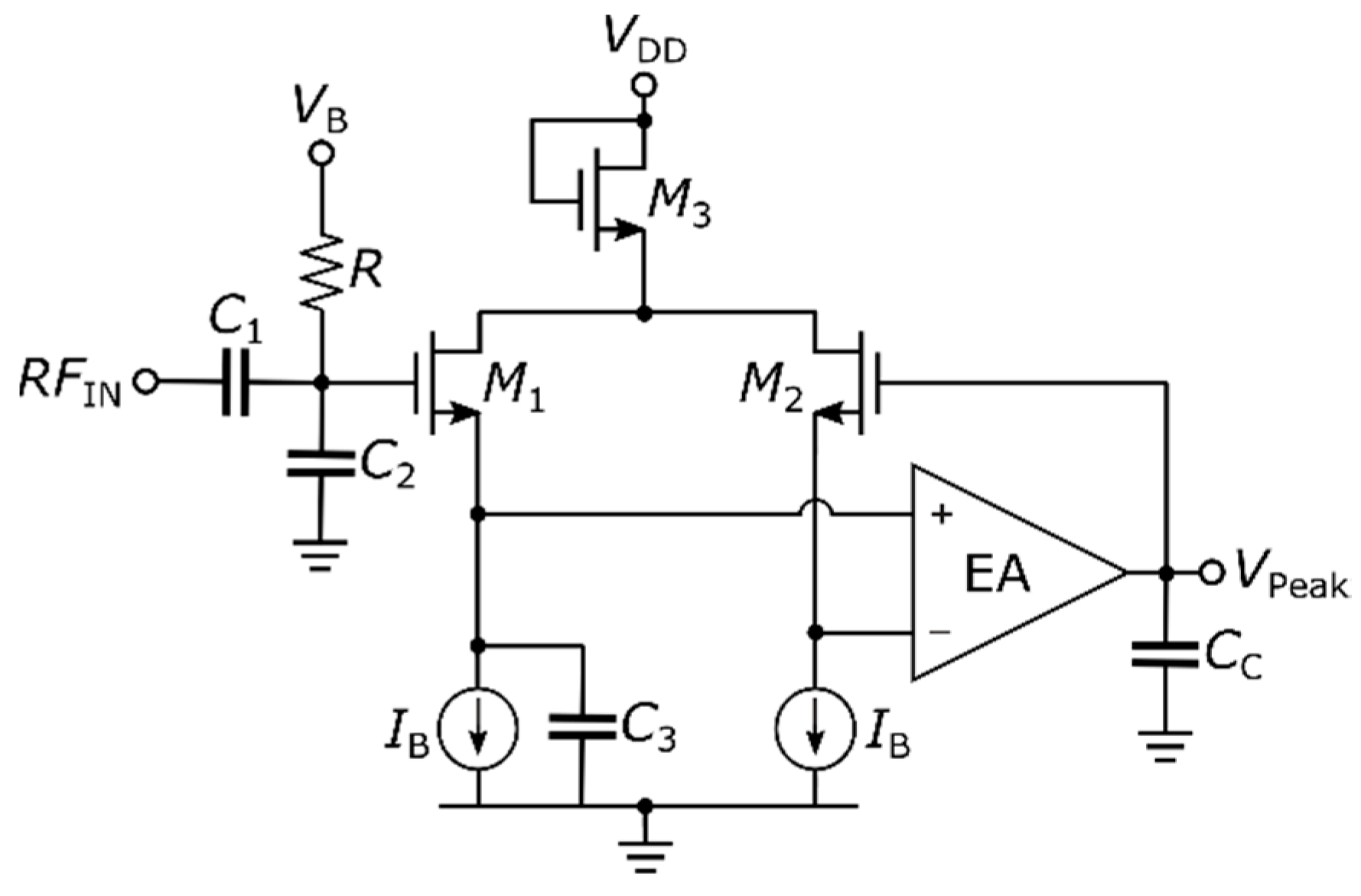

3.1. Power Amplifier Design

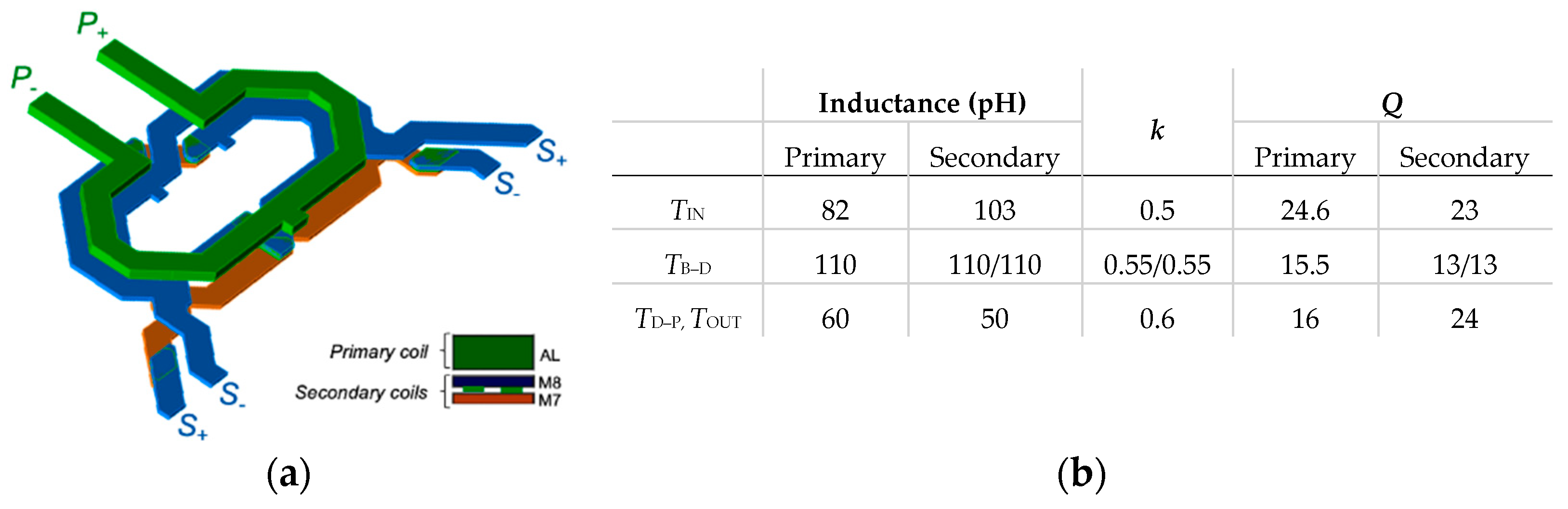

3.2. Mm-Wave Transformer Design

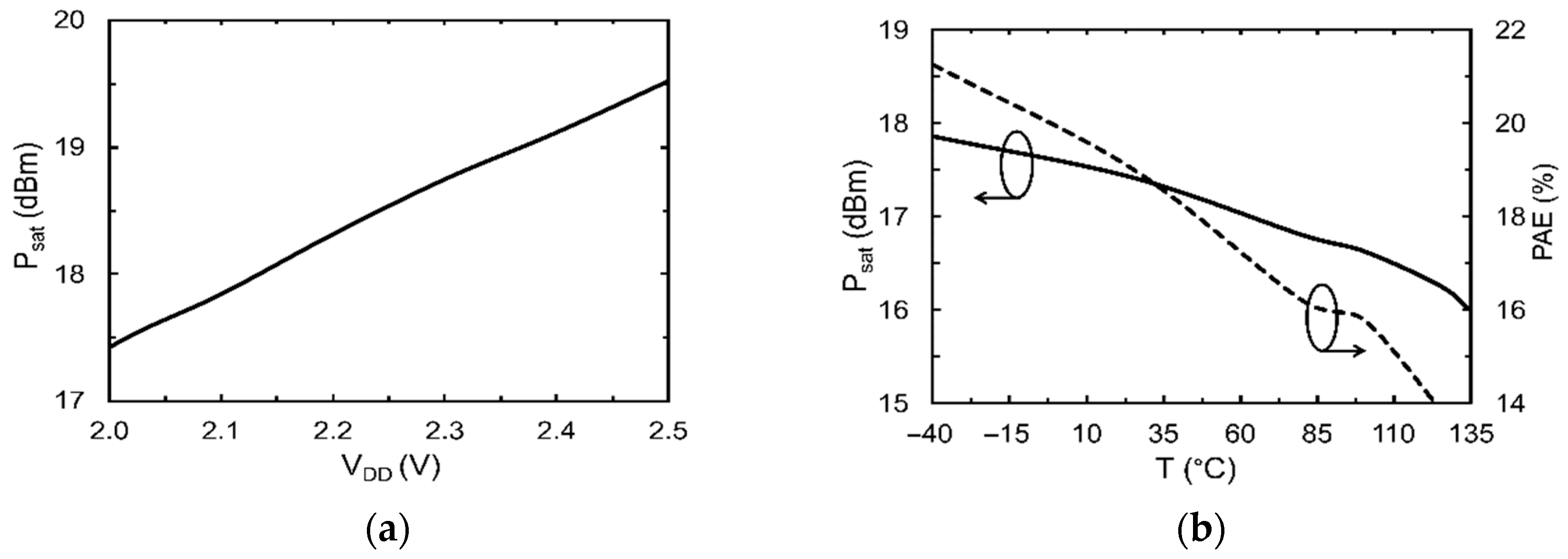

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Hasch, J.; Topak, E.; Schnabel, R.; Zwick, T.; Weigel, R.; Waldschmidt, C. Millimeter-wave technology for automotive radar sensors in the 77 GHz frequency band. IEEE Trans. Microw. Theory Tech. 2012, 60, 845–860. [Google Scholar] [CrossRef]

- Giannini, V.; Goldenberg, M.; Eshraghi, A.; Maligeorgos, J.; Lim, L.; Lobo, R.; Welland, D.; Chow, C.K.; Dornbusch, A.; Dupuis, T.; et al. A 192-virtual-receiver 77/79 GHz GMSK code-domain MIMO radar system-on-chip. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 164–166. [Google Scholar]

- Ginsburg, B.P.; Subburaj, K.; Samala, S.; Ramasubramanian, K.; Singh, J.; Bhatara, S.; Murali, S.; Breen, D.; Moallem, M.; Dandu, K.; et al. A multimode 76-to-81 GHz automotive radar transceiver with autonomous monitoring. In Proceedings of the 2018 IEEE International Solid—State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 158–160. [Google Scholar]

- Nocera, C.; Cavarra, A.; Ragonese, E.; Palmisano, G.; Papotto, G. Down-converter solutions for 77-GHz automotive radar sensors in 28-nm FD-SOI CMOS technology. In Proceedings of the 2018 IEEE International Solid—State Circuits Conference—(ISSCC), Prague, Czech Republic, July 2018; pp. 153–156. [Google Scholar]

- Papotto, G.; Nocera, C.; Finocchiaro, A.; Parisi, A.; Cavarra, A.; Castorina, A.; Ragonese, E.; Palmisano, G. A 27-mW W-band radar receiver with effective leakage suppression in 28-nm FD-SOI CMOS CMOS. IEEE Trans. Microw. Theory Tech. 2021, 69, 4132–4141. [Google Scholar] [CrossRef]

- Nocera, C.; Papotto, G.; Cavarra, A.; Ragonese, E.; Palmisano, G. A 13.5-dBm 1-V power amplifier for W-band automotive radar applications in 28-nm FD-SOI CMOS technology. IEEE Trans. Microw. Theory Tech. 2021, 69, 1654–1660. [Google Scholar] [CrossRef]

- To, K.H.; Trivedi, V.P. A 76-81 GHz transmitter with 10 dBm output power at 125 °C for automotive radar in 65 nm bulk CMOS. In Proceedings of the 2011 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 19–21 September 2011; pp. 1–4. [Google Scholar]

- Xi, T.; Huang, S.; Guo, S.; Gui, P.; Zhang, J.; Choi, W.; Huang, D.; O Kenneth, K.; Fan, Y. A new compact high-efficiency mm-wave power amplifier in 65 nm CMOS process. In Proceedings of the 2015 IEEE MTT-S International Microwave Symposium, Phoenix, AZ, USA, 17–22 May 2015; pp. 1–4. [Google Scholar]

- Jia, H.; Kuang, L.; Zhu, W.; Wang, Z.; Ma, F.; Wang, Z.; Chi, B. A 77 GHz frequency doubling two-path phased-array FMCW transceiver for automotive radar. IEEE J. Solid-State Circuits 2016, 51, 2299–2311. [Google Scholar] [CrossRef]

- Trinh, V.-S.; Park, J.-D. A 16.3 dBm 14.1% PAE 28-dB gain W-Band power amplifier with inductive feedback in 65-nm CMOS. IEEE Microw. Wirel. Comp. Lett. 2020, 30, 193–196. [Google Scholar] [CrossRef]

- Chen, L.; Zhang, L.; Wang, Y. A 26.4-dB gain 15.82-dBm 77-GHz CMOS power amplifier with 15.9% PAE using transformer-based quadrature coupler network. IEEE Microw. Wirel. Comp. Lett. 2020, 30, 78–81. [Google Scholar] [CrossRef]

- Zhao, D.; Reynaert, P. A 60-GHz Dual-Mode class AB power amplifier in 40-nm CMOS. IEEE J. Solid-State Circuits 2013, 48, 2323–2337. [Google Scholar] [CrossRef]

- Cathelin, A. Fully depleted silicon on insulator devices CMOS: The 28-nm node is the perfect technology for analog, RF, mmW, and mixed-signal system-on-chip integration. IEEE Solid-State Circuits Mag. 2017, 4, 18–26. [Google Scholar] [CrossRef]

- Giammello, V.; Ragonese, E.; Palmisano, G. A transformer-coupling current-reuse SiGe HBT power amplifier for 77-GHz automotive radar. IEEE Trans. Microw. Theory Tech. 2012, 60, 1676–1683. [Google Scholar] [CrossRef]

- Zhang, R.; Zhu, Y. An X-band CMOS push-pull power amplifier with capacitive neutralization for high linearity and high efficiency applications. In Proceedings of the 2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), China, Hangzhou, 25–28 October 2016; pp. 1543–1545. [Google Scholar]

- Cavarra, A.; Nocera, C.; Papotto, G.; Ragonese, E.; Palmisano, G. Transformer design for 77-GHz down-converter in 28-nm FD-SOI CMOS technology. In Applications in Electronics Pervading Industry, Environment and Society—ApplePies (Lecture Notes in Electrical Engineering); Springer: Pisa, Italy, 2019; Volume 550, pp. 195–201. [Google Scholar]

- Kaymaksut, E.; Zhao, D.; Reynaert, P. Transformer-based doherty power amplifiers for mm-wave applications in 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2015, 63, 1186–1192. [Google Scholar] [CrossRef]

- Pan, D.; Duan, Z.; Sun, L.; Guo, S.; Cheng, L.; Gui, P. A 76-81 GHz CMOS PA with 16-dBm PSAT and 30-dB amplitude control for MIMO automotive radars. In Proceedings of the ESSCIRC 2019-IEEE 45th European Solid State Circuits Conference (ESSCIRC), Cracow, Poland, 23–26 September 2019; pp. 329–332. [Google Scholar]

- Lin, Y.; Lin, Y.; Gao, J.; Lan, K. High gain and high PAE 68~94 GHz CMOS power amplifier using miniature zero-degree four-way current combiner. In Proceedings of the 2018 IEEE Radio and Wireless Symposium (RWS), Anaheim, CA, USA, 15–18 January 2018; pp. 125–128. [Google Scholar]

- Xue, Y.; Shi, C.; Chen, G.; Chen, J.; Zhang, R. Two W-band wideband CMOS mmw PAs for automotive radar transceivers. In Proceedings of the 2020 IEEE/MTT-S International Microwave Symposium (IMS), Los Angeles, CA, USA, 4–6 August 2020; pp. 1109–1112. [Google Scholar]

- Oh, J.; Ku, B.; Hong, S. A 77-GHz CMOS power amplifier with a parallel power combiner based on transmission-line transformer. IEEE Trans. Microw. Theory Tech. 2013, 61, 2662–2669. [Google Scholar] [CrossRef]

- Yao, T.; Gordon, M.Q.; Tang, K.K.W.; Yau, K.H.K.; Yang, M.-T.; Schvan, P.; Voinigescu, S.P. Algorithmic design of CMOS LNAs and PAs for 60-GHz radio. IEEE J. Solid-State Circuits 2007, 42, 1044–1057. [Google Scholar] [CrossRef]

| Ref. | Tech. | Amplifier Topology | Power Combining | Peak Detector | Freq [GHz] | Psat [dBm] | PN [dBm] | G [dB] | PAE [%] | VDD [V] | Pdc [W] | Core Die Size [mm2] | FoM * |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| [17] | 40-nm CMOS | Doherty with Cascode amplifier | 4-path | n.a | 77 | 20 | 17.5 | 20 | 12 | 1.5 | 0.8 | 0.19 | 7115 |

| [18] | 65-nm CMOS | 2-Cascode | 2-path | n.a | 77 | 12 | 12 | 25 | 4.2 | 1.8 | 0.35 | 0.34 | 1248 |

| [19] | 90-nm CMOS | 1-CS+ 1-Cascode | 4-path | n.a | 77 | 12.2 | 9.7 | 24.1 | 17.3 | 2.4 | 0.09 | 0.73 | 4375 |

| [20] | 55-nm CMOS | 2-Cascode | 2-path | n.a | 77 | 15 | 15 | 15 | 8 | 2.5 | n.a | 0.21 | 474 |

| [2] | 65-nm CMOS | 4-CS | 2-path | n.a | 77 | 15.4 | 15.4 | 24.4 | 10.4 | 1 | 0.33 | - | 5889 |

| [21] | 65-nm CMOS | 2-Cascode | 2-path | n.a | 77 | 15.8 | 15.8 | 21 | 15.2 | 2 | 0.25 | 0.21 | 4313 |

| ThisWork | 28-nm CMOS | 1-Cascode+ 1-CS +1-Cascode | 2-path | a | 77 | 17.4 | 17.4 | 28 | 19 | 2 | 0.3 | 0.15 | 39,060 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nocera, C.; Papotto, G.; Palmisano, G. Two-Path 77-GHz PA in 28-nm FD-SOI CMOS for Automotive Radar Applications. Electronics 2022, 11, 1289. https://doi.org/10.3390/electronics11081289

Nocera C, Papotto G, Palmisano G. Two-Path 77-GHz PA in 28-nm FD-SOI CMOS for Automotive Radar Applications. Electronics. 2022; 11(8):1289. https://doi.org/10.3390/electronics11081289

Chicago/Turabian StyleNocera, Claudio, Giuseppe Papotto, and Giuseppe Palmisano. 2022. "Two-Path 77-GHz PA in 28-nm FD-SOI CMOS for Automotive Radar Applications" Electronics 11, no. 8: 1289. https://doi.org/10.3390/electronics11081289

APA StyleNocera, C., Papotto, G., & Palmisano, G. (2022). Two-Path 77-GHz PA in 28-nm FD-SOI CMOS for Automotive Radar Applications. Electronics, 11(8), 1289. https://doi.org/10.3390/electronics11081289