Compact CMOS Wideband Instrumentation Amplifiers for Multi-Frequency Bioimpedance Measurement: A Design Procedure

Abstract

:1. Introduction

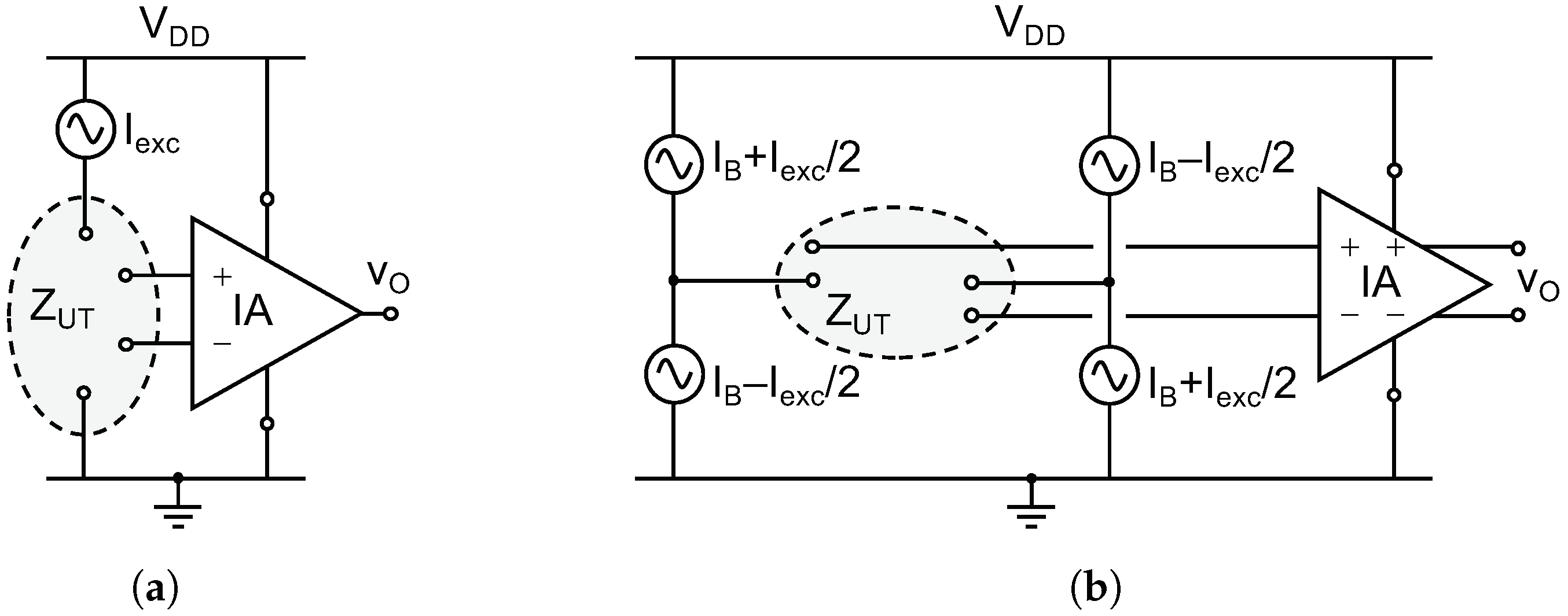

2. Principle of Operation

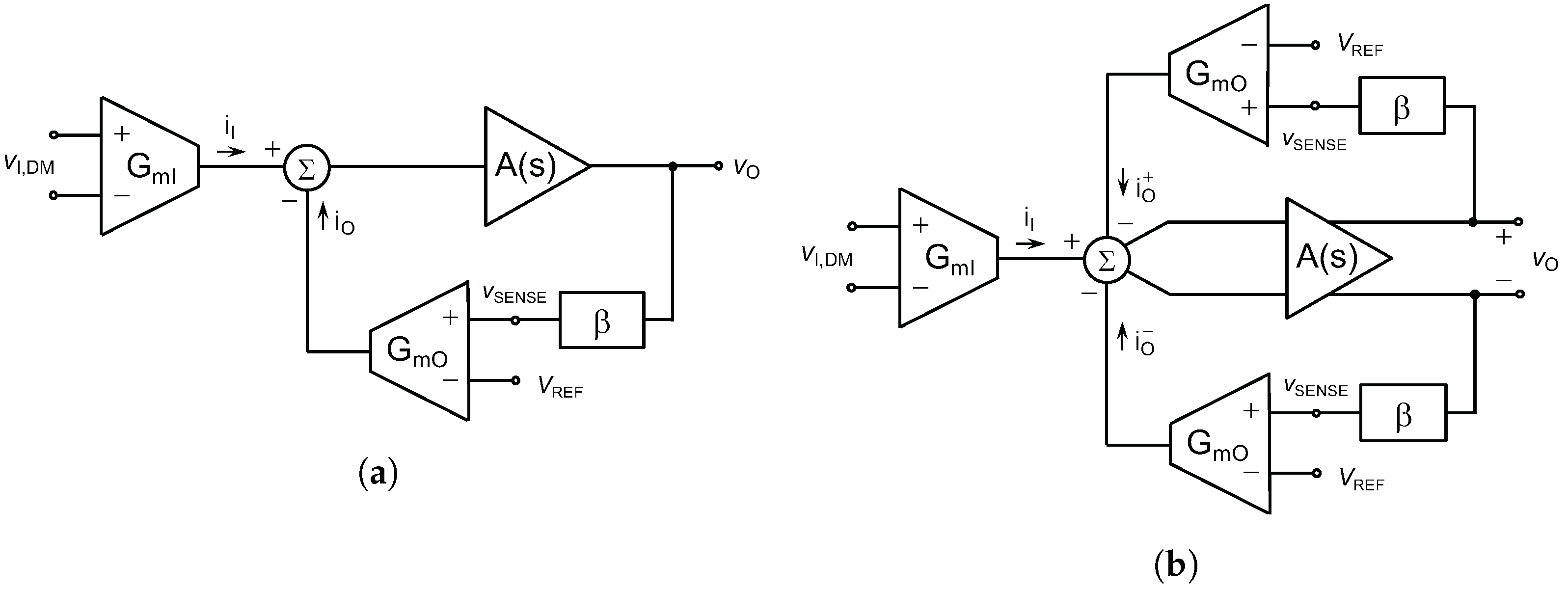

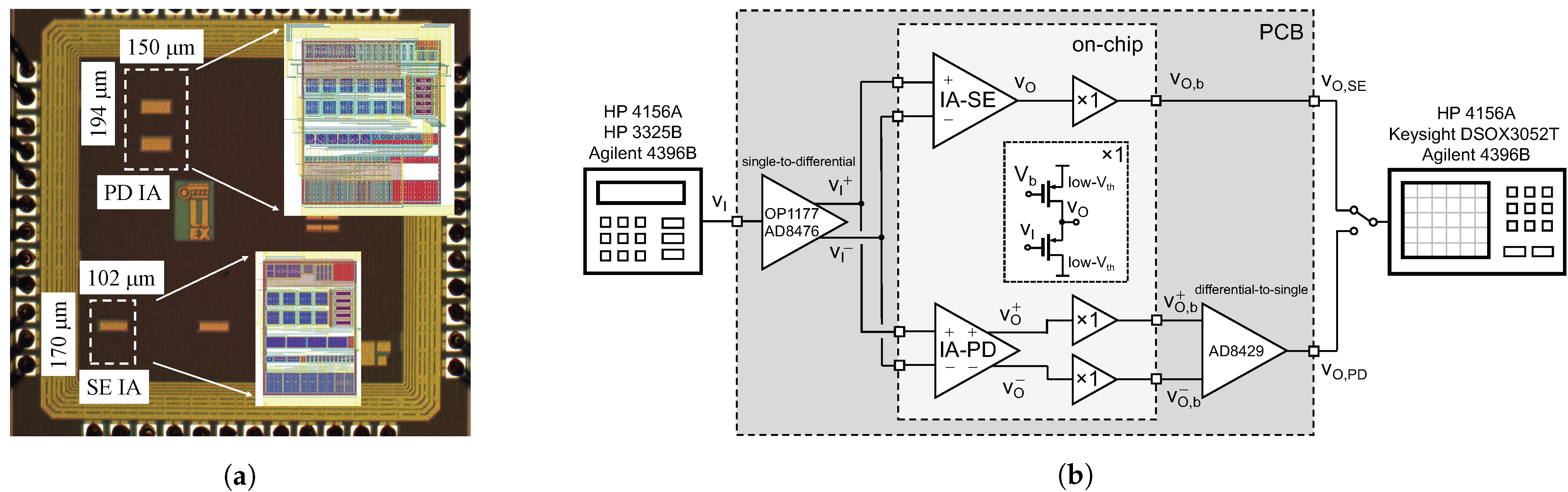

2.1. Block Diagram

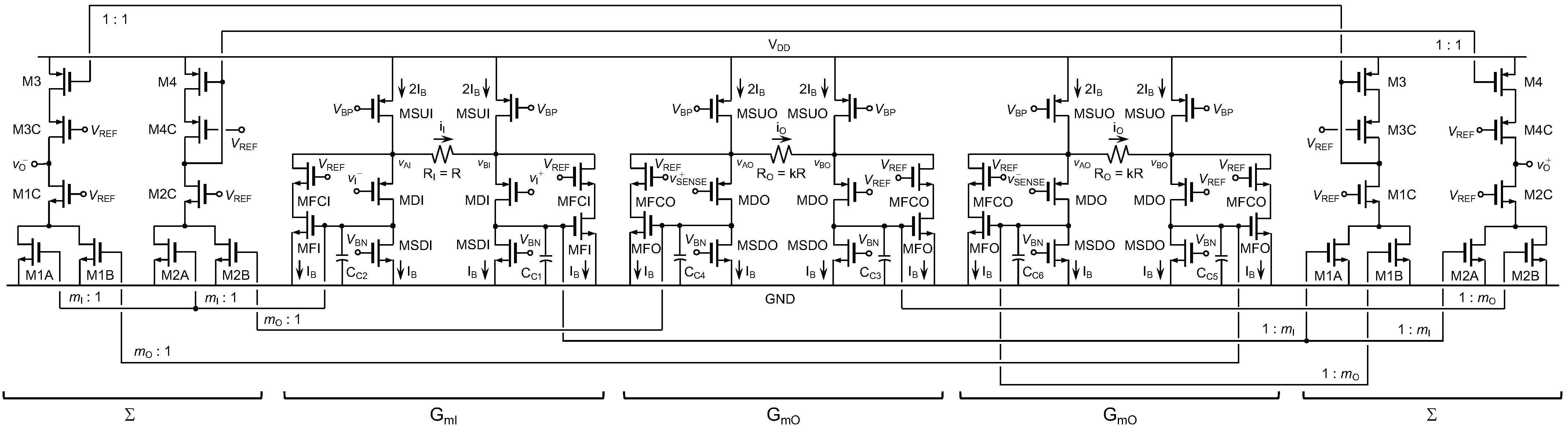

2.2. Transistor Level Implementation

3. Design Guidelines

3.1. Theoretical Analysis

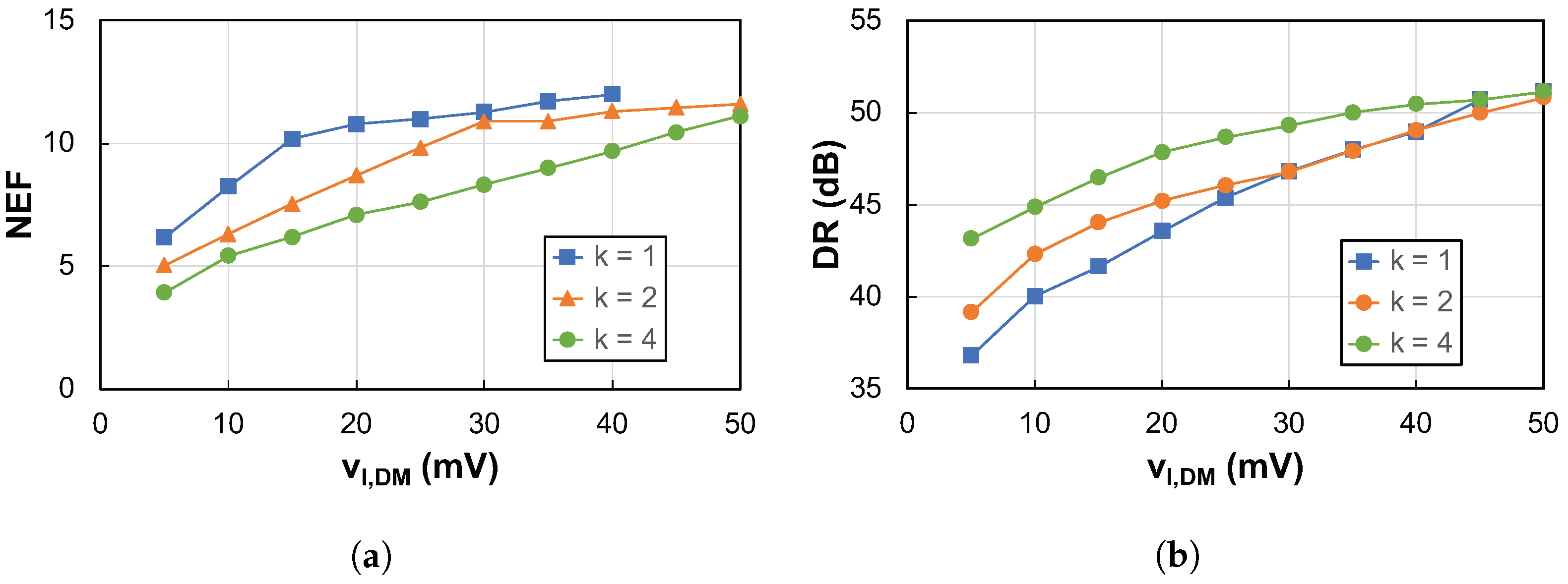

3.2. Design Space

3.3. Design Procedure

- Determine the combinations of the design parameters that lead to the desired value of and provide the same BW.

- Select an option for and set the value of the source degeneration resistor R in view of the responses of , BW, CMRR and the noise.

- Fix the value of the input DM signal range, .

- Find the value of the biasing current that leads to according to (14). This value can be refined by means of simulations establishing an objective criterion, such as obtaining 1% of THD when is applied.

- Determine the value of that leads to a phase margin of 60º for the feedback loop around .

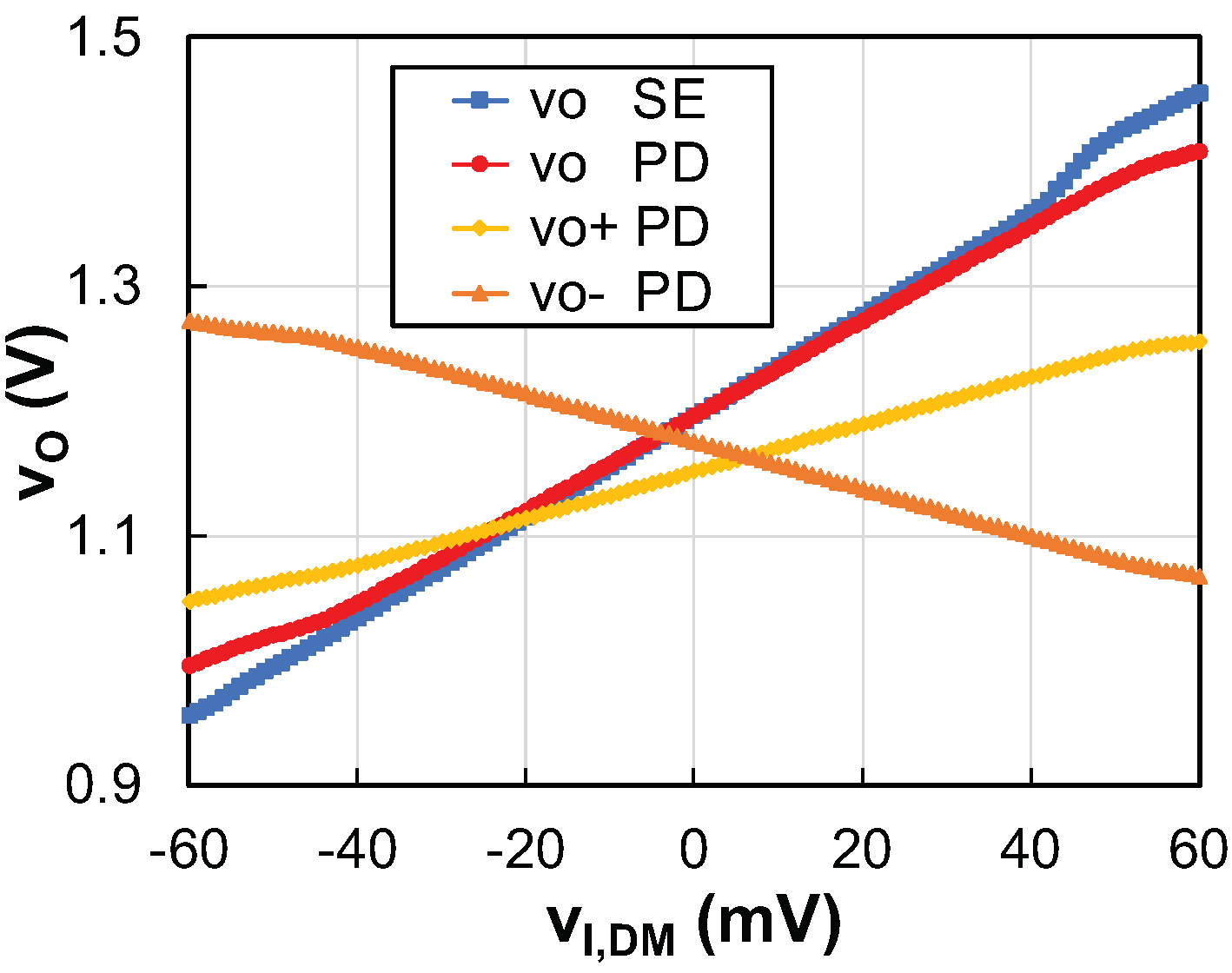

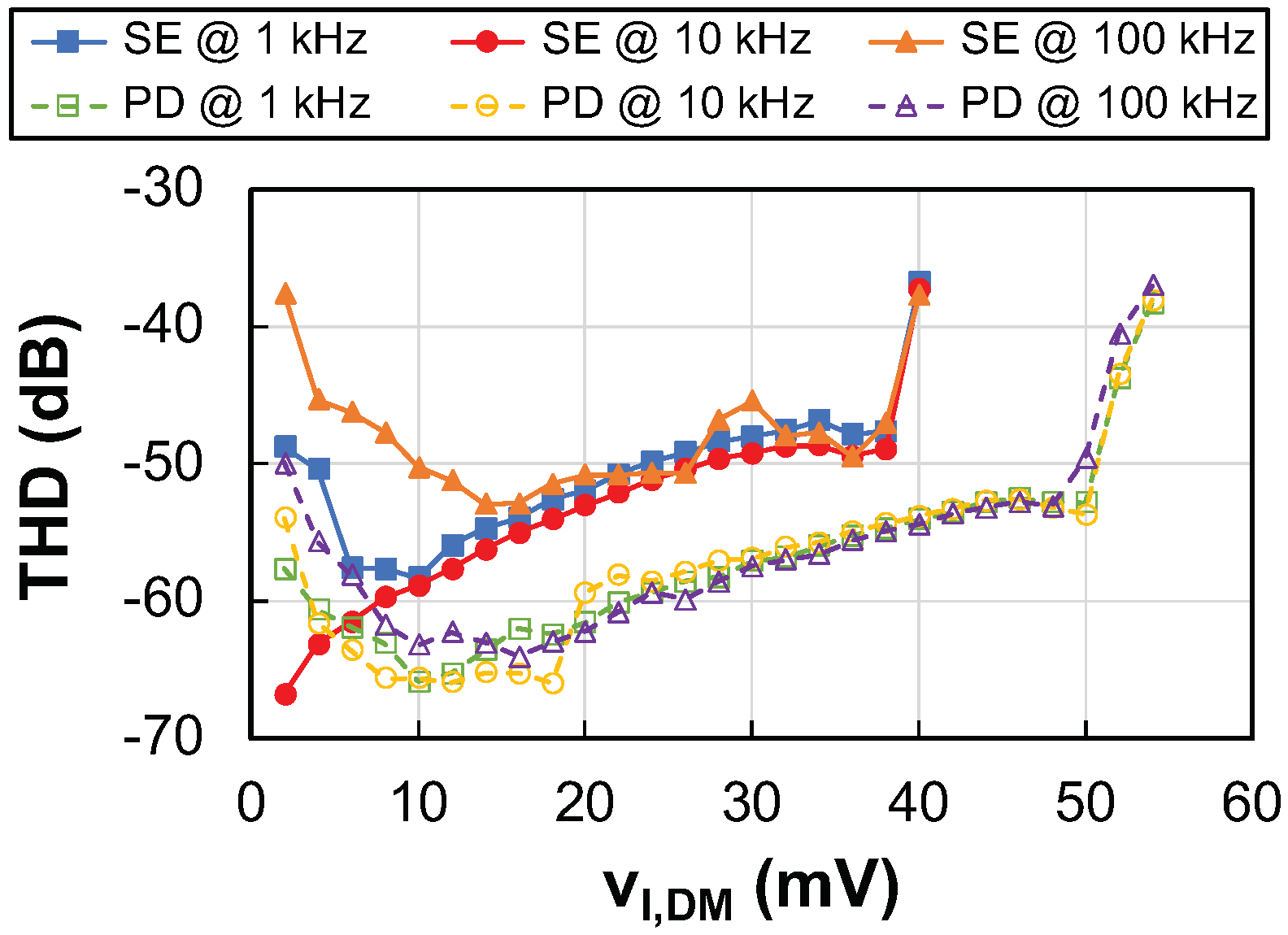

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Grimnes, S.; Martinsen, V.G. Bioimpedance and Bioelectricity Basics, 3rd ed.; Academic Press: Cambridge, MA, USA, 2015. [Google Scholar]

- Brokaw, A.P.; Timko, M.P. An improved monolithic instrumentation amplifier. IEEE J. Solid-State Circuits 1975, 10, 417–423. [Google Scholar] [CrossRef]

- Huijsing, J.H. Instrumentation amplifiers: A comparative study on behalf of monolithic integration. IEEE Trans. Instrum. Meas. 1976, IM-25, 227–231. [Google Scholar] [CrossRef]

- Hamstra, G.H.; Peper, A.; Grimbergen, C.A. Low-power, low-noise instrumentation amplifier for phisiological signals. Med. Biol. Eng. Comput. 1984, 22, 272–274. [Google Scholar] [CrossRef] [PubMed]

- Steyaert, M.S.J.; Sansen, W.M.C. A micropower low-noise monolithic instrumentation amplifier for medical purposes. IEEE J. Solid-State Circuits 1987, 22, 1163–1168. [Google Scholar] [CrossRef]

- van den Dool, B.J.; Huijsing, J.K. Indirect current feedback instrumentation amplifier with a common-mode input range that includes the negative rail. IEEE J. Solid-State Circuits 1993, 28, 743–749. [Google Scholar] [CrossRef] [Green Version]

- Martins, R.; Selberherr, S.; Vaz, F.A. A CMOS IC for portable EEG acquisition systems. IEEE Trans. Instrum. Meas. 1998, 47, 1191–1196. [Google Scholar] [CrossRef]

- Harrison, R.R.; Charles, C. A low-power low-noise CMOS amplifier for neural recording applications. IEEE J. Solid-State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Spinelli, E.M.; Martinez, N.; Mayosky, M.A.; Pallas-Areny, R. A novel fully differential biopotential amplifier with DC suppression. IEEE Trans. Biomed. Eng. 2004, 51, 1444–1448. [Google Scholar] [CrossRef]

- Zhao, Y.Q.; Demosthenous, A.; Bayford, R.H. A CMOS instrumentation amplifier for wideband bioimpedance spectroscopy systems. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems, Kos, Greece, 21–24 May 2006; pp. 5079–5082. [Google Scholar]

- Yazicioglu, R.F.; Merken, P.; Puers, R.; Van Hoof, C. A 60 μW 60 nV/√Hz readout front-end for portable biopotential acquisition systems. IEEE J. Solid-State Circuits 2007, 42, 1100–1110. [Google Scholar] [CrossRef]

- Denison, T.; Consoer, K.; Santa, W.; Avestruz, A.; Cooley, J.; Kelly, A. A 2 μW 100 nV/√Hz chopper-stabilized instrumentation amplifier for chronic measurement of neural field potentials. IEEE J. Solid-State Circuits 2007, 42, 2934–2945. [Google Scholar] [CrossRef]

- Schaffer, V.; Snoeij, M.F.; Ivanov, M.V.; Trifonov, D.T. A 36 V programmable instrumentation amplifier with sub-20 μV offset and a CMRR in excess of 120 dB at all gain settings. IEEE J. Solid-State Circuits 2009, 44, 2036–2046. [Google Scholar] [CrossRef]

- Ramos, J.; Ausín, J.L.; Torelli, G. A 1-MHz analog front-end for a wireless bioelectrical impedance sensor. In Proceedings of the International Conference on PhD Research in Microelectronics and Electronics (PRIME), Berlin, Germany, 18–21 July 2010; pp. 1–4. [Google Scholar]

- Worapishet, A.; Demosthenous, A.; Liu, X. A CMOS instrumentation amplifier with 90-dB CMRR at 2-MHz using capacitive neutralization: Analysis, design considerations, and implementation. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 699–710. [Google Scholar] [CrossRef]

- Fan, Q.; Sebastiano, F.; Huijsing, J.H.; Makinwa, K.A.A. A 1.8 μW 60 nV/√ Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes. IEEE J. Solid-State Circuits 2011, 46, 1534–1543. [Google Scholar] [CrossRef]

- Muller, R.; Gambini, S.; Rabaey, J.M. A 0.013 mm2, 5 μW , DC-coupled neural signal acquisition IC with 0.5 V supply. IEEE J. Solid-State Circuits 2012, 47, 232–243. [Google Scholar] [CrossRef]

- Ramos, J.; Ausín, J.L.; Duque-Carrillo, J.F.; Torelli, G. Wideband low-power current-feedback instrumentation amplifiers for bioelectrical signals. In Proceedings of the International Multi-Conference on Systems, Signals and Devices, Chemnitz, Germany, 20–23 March 2012; pp. 1–5. [Google Scholar]

- Abdelhalim, K.; Jafari, H.M.; Kokarovtseva, L.; Velazquez, J.L.P.; Genov, R. 64-channel UWB wireless neural vector analyzer SOC with a closed-loop phase synchrony-triggered neurostimulator. IEEE J. Solid-State Circuits 2013, 48, 2494–2510. [Google Scholar] [CrossRef]

- Ong, G.T.; Chan, P.K. A power-aware chopper-stabilized instrumentation amplifier for resistive Wheatstone bridge sensors. IEEE Trans. Instrum. Meas. 2014, 63, 2253–2263. [Google Scholar] [CrossRef]

- Van Helleputte, N.; Konijnenburg, M.; Pettine, J.; Jee, D.; Kim, H.; Morgado, A.; Van Wegberg, R.; Torfs, T.; Mohan, R.; Breeschoten, A.; et al. A 345 μW multi-sensor biomedical SoC with bio-impedance, 3-channel ECG, motion artifact reduction, and integrated DSP. IEEE J. Solid-State Circuits 2015, 50, 230–244. [Google Scholar] [CrossRef]

- Worapishet, A.; Demosthenous, A. Generalized analysis of random common-mode rejection performance of CMOS current feedback instrumentation amplifiers. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2137–2146. [Google Scholar] [CrossRef]

- Wu, J.; Law, M.; Mak, P.; Martins, R.P. A 2-μW 45-nV/√Hz readout front end with multiple-chopping active-high-pass ripple reduction loop and pseudofeedback DC servo loop. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 351–355. [Google Scholar] [CrossRef]

- Das, D.M.; Srivastava, A.; Ananthapadmanabhan, J.; Ahmad, M.; Baghini, M.S. A novel low-noise fully-differential CMOS instrumentation amplifier with 1.88 noise efficiency factor for biomedical and sensor applications. Microelectron. J. 2016, 53, 35–44. [Google Scholar] [CrossRef]

- Chandrakumar, H.; Marković, D. A high dynamic-range neural recording chopper amplifier for simultaneous neural recording and stimulation. IEEE J. Solid-State Circuits 2017, 52, 645–656. [Google Scholar] [CrossRef]

- Chang, C.; Zahrai, S.A.; Wang, K.; Xu, L.; Farah, I.; Onabajo, M. An analog front-end chip with self-calibrated input impedance for monitoring of biosignals via dry electrode-skin interfaces. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 2666–2678. [Google Scholar] [CrossRef]

- Rezaeiyan, Y.; Zamani, M.; Shoaei, O.; Serdjin, W.A. A 0.5 μA/channel front-end for implantable and external ambulatory ECG recorders. Microelectron. J. 2018, 74, 79–85. [Google Scholar] [CrossRef] [Green Version]

- Eldeeb, M.A.; Ghallab, Y.H.; Ismail, Y.; El-Ghitani, H. A 0.4-V miniature CMOS current mode instrumentation amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 261–265. [Google Scholar] [CrossRef]

- Safari, L.; Minaei, S.; Ferri, G.; Stornelli, V. A low-voltage low-power instrumentation amplifier based on supply current sensing technique. AEU—Int. J. Electron. Commun. 2018, 91, 125–131. [Google Scholar] [CrossRef]

- Avoli, M.; Centurelli, F.; Monsurrò, P.; Scotti, G.; Trifiletti, A. Low power DDA-based instrumentation amplifier for neural recording applications in 65 nm CMOS. AEU—Int. J. Electron. Commun. 2018, 92, 30–35. [Google Scholar] [CrossRef]

- Nasserian, M.; Peiravi, A.; Moradi, F. A fully-integrated 16-channel EEG readout front-end for neural recording applications. AEU—Int. J. Electron. Commun. 2018, 94, 109–121. [Google Scholar] [CrossRef]

- Lee, C.; Song, J. A chopper stabilized current-feedback instrumentation amplifier for EEG acquisition applications. IEEE Access 2019, 7, 11565–11569. [Google Scholar] [CrossRef]

- Carrillo, J.M.; Domínguez, M.A.; Pérez-Aloe, R.; Duque-Carrillo, J.F.; de la Cruz, C.A. CMOS low-voltage indirect current feedback instrumentation amplifiers with improved performance. In Proceedings of the 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Genoa, Italy, 27–29 November 2019; pp. 262–265. [Google Scholar]

- Psychalinos, C.; Minaei, S.; Safari, L. Ultra low-power electronically tunable current-mode instrumentation amplifier for biomedical applications. AEU—Int. J. Electron. Commun. 2020, 117, 153120. [Google Scholar] [CrossRef]

- Carrillo, J.M.; Domínguez, M.A.; Pérez-Aloe, R.; de la Cruz Blas, C.A.; Duque-Carrillo, J.F. Low-power wide-bandwidth CMOS indirect current feedback instrumentation amplifier. AEU—Int. J. Electron. Commun. 2020, 123, 153299. [Google Scholar] [CrossRef]

- Kwon, Y.; Kim, H.; Kim, J.; Han, K.; You, D.; Heo, H.; Cho, D.i.; Ko, H. Fully differential chopper-stabilized multipath current-feedback instrumentation amplifier with R-2R DAC offset adjustment for resistive bridge sensors. Appl. Sci. 2020, 10, 63. [Google Scholar] [CrossRef] [Green Version]

- Han, K.; Kim, H.; Kim, J.; You, D.; Heo, H.; Kwon, Y.; Lee, J.; Ko, H. A 24.88 nV/√Hz Wheatstone bridge readout integrated circuit with chopper-stabilized multipath operational amplifier. Appl. Sci. 2020, 10, 399. [Google Scholar] [CrossRef] [Green Version]

- Corbacho, I.; Carrillo, J.M.; Ausín, J.L.; Domínguez, M.A.; Duque-Carrillo, J.F. Unitary vs. resistive feedback in CMOS two-stage indirect current feedback instrumentation amplifiers. In Proceedings of the 2020 27th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Glasgow, UK, 23–25 November 2020; pp. 1–4. [Google Scholar]

- Matthus, C.D.; Buhr, S.; Kreißig, M.; Ellinger, F. High gain and high bandwidth fully differential difference amplifier as current sense amplifier. IEEE Trans. Instrum. Meas. 2021, 70, 1–11. [Google Scholar] [CrossRef]

- Pérez-Bailón, J.; Sanz-Pascual, M.T.; Calvo, B.; Medrano, N. Wide-band compact 1.8 V-0.18 μm CMOS analog front-end for impedance spectroscopy. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 764–768. [Google Scholar] [CrossRef]

- Pérez-Bailón, J.; Calvo, B.; Medrano, N. 1.0 V-0.18 μm CMOS tunable low pass filters with 73 dB DR for on-chip sensing acquisition systems. Electronics 2021, 10, 563. [Google Scholar] [CrossRef]

- Ashayeri, M.; Yavari, M. A front-end amplifier with tunable bandwidth and high value pseudo resistor for neural recording implants. Microelectron. J. 2022, 119, 105333. [Google Scholar] [CrossRef]

- Corbacho, I.; Carrillo, J.M.; Ausín, J.L.; Domínguez, M.A.; Duque-Carrillo, J.F. 0.8-V CMOS Gm-C bandpass filter for electrical bioimpedance spectroscopy. In Proceedings of the 2021 28th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Dubai, United Arab Emirates, 28 November–1 December 2021; pp. 1–4. [Google Scholar]

| Option | k | ||

|---|---|---|---|

| #1 | 4 | 1 | 1 |

| #2 | 2 | 1 | 1/2 |

| #3 | 1 | 1 | 1/4 |

| Device | SE (m/m) | PD (m/m) | Device | SE (m/m) | PD (m/m) |

|---|---|---|---|---|---|

| MDI | 200/1 | 200/1 | MDO | 200/1 | 200/1 |

| MFI | 320/0.5 | 80/0.5 | MFO | 80/0.5 | 80/0.5 |

| MFCI | 20/0.5 | 20/0.5 | MFCO | 20/0.5 | 20/0.5 |

| MSDI | 16/1 | 16/1 | MSDO | 16/1 | 16/1 |

| MSUI | 48/1 | 48/1 | MSUO | 48/1 | 48/1 |

| M1A, M2A | 320/0.5 | 80/0.5 | M1B, M2B | 80/0.5 | 80/0.5 |

| M1C | 20/0.5 | 20/0.5 | M2C | 20/0.5 | 20/0.5 |

| M3, M4 | 30/0.5 | 30/0.5 | M3C, M4C | 60/0.5 | 60/0.5 |

| Parameter | SE Simulated | SE Measured | PD Simulated | PD Measured |

|---|---|---|---|---|

| Voltage gain (V/V) | 3.85 ± 0.35 | 4.28 ± 0.13 | 3.92 ± 0.05 | 3.70 ± 0.13 |

| Voltage gain error (%) | −3.7 | 7.0 | −1.9 | −7.5 |

| BW (MHz) | 6.6 | 5.2 | 8.2 | 8.0 |

| Output offset voltage (mV) | 0.35 ± 80.76 | ±5.69 | 0.24 ± 80.61 | ±5.62 |

| @ 1 kHz (mV) | 53 | 39 | 54 | 53 |

| @ 10 kHz (mV) | 53 | 39 | 54 | 53 |

| @ 100 kHz (mV) | 52 | 39 | 54 | 53 |

| / (V/s) | 6.0/13.6 | 6.7/13.4 | 10.3/10.3 | 10.9/9.4 |

| CMRR @ DC (dB) | 86.6 ± 14.7 | 72.2 | 85.5 ± 9.8 | 80.6 |

| CMRR @ BW (dB) | 63.4 ± 10.6 | 33.5 | 65.2 ± 6.2 | 41.2 |

| [100 Hz-BW ] () | 70.9 | 85.0 | 72.7 | 92.0 |

| (A) | 137.4 | 139.0 | 216.1 | 219.3 |

| NEF | 12.5 | 23.5 | 14.4 | 26.3 |

| DR (dB) | 54.5 | 50.2 | 54.4 | 52.2 |

| Parameter | [13] JSSC’09 | [15] TCAS-I’11 | [18] IMCSSD’12 | [35] IJEC’20 | [40] TCAS-II’21 | This Work SE | This Work PD |

|---|---|---|---|---|---|---|---|

| Technology | 0.35-m CMOS | 0.35-m CMOS | 0.35-m CMOS | 0.35-m CMOS | 0.18-m CMOS | 0.18-m CMOS | 0.18-m CMOS |

| Technique | V-to-I I-to-V | LCF | LCF | ICF | -TI | ICF | ICF |

| Results | Meas. | Meas. | Sim. | Sim. | Sim. | Meas. | Meas. |

| V (V) | 36 | 3 | 2 | 3 | 1.8 | 1.8 | 1.8 |

| I (A) | 3000 | 285 | 240 | 250.6 | 162 | 139.0 | 219.3 |

| Gain (dB) | −18/42 | 34 | 8 | 34 | 0/40 | 12.6 | 11.4 |

| BW (MHz) | 2.0 | 2.0 | 4.0 | 7.6 | 6.7 × 10/87.0 | 5.2 | 8.0 |

| CMRR (dB) | 120 | >90 @ DC | 80 @ 1 MHz | 99.5 @ DC | 164.4 @ 100 kHz | 72.2 @ DC | 80.6 @ DC |

| THD (dB) @ (m) | N.A. | −56.2 @ 10 | N.A. | −57.4 @ 10 | N.A. | −52.0 @ 20 | −61.6 @ 20 |

| (mV) | N.A. | 30 | N.A. | 8 | N.A. | 39 | 53 |

| () | 283 | 16 | 36 | 32.4 | N.A. | 85.0 | 92.0 |

| Area (mm) | 8.64 | 0.068 | 0.037 | — | 0.0569 | 0.0173 | 0.0291 |

| NEF | 423.1 | 5.9 | 10.8 | 7.2 | N.A. | 23.5 | 26.3 |

| DR (dB) | N.A. | 65.5 | N.A. | 47.9 | N.A. | 50.2 | 52.2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Corbacho, I.; Carrillo, J.M.; Ausín, J.L.; Domínguez, M.Á.; Pérez-Aloe, R.; Duque-Carrillo, J.F. Compact CMOS Wideband Instrumentation Amplifiers for Multi-Frequency Bioimpedance Measurement: A Design Procedure. Electronics 2022, 11, 1668. https://doi.org/10.3390/electronics11111668

Corbacho I, Carrillo JM, Ausín JL, Domínguez MÁ, Pérez-Aloe R, Duque-Carrillo JF. Compact CMOS Wideband Instrumentation Amplifiers for Multi-Frequency Bioimpedance Measurement: A Design Procedure. Electronics. 2022; 11(11):1668. https://doi.org/10.3390/electronics11111668

Chicago/Turabian StyleCorbacho, Israel, Juan M. Carrillo, José L. Ausín, Miguel Á. Domínguez, Raquel Pérez-Aloe, and Juan Francisco Duque-Carrillo. 2022. "Compact CMOS Wideband Instrumentation Amplifiers for Multi-Frequency Bioimpedance Measurement: A Design Procedure" Electronics 11, no. 11: 1668. https://doi.org/10.3390/electronics11111668

APA StyleCorbacho, I., Carrillo, J. M., Ausín, J. L., Domínguez, M. Á., Pérez-Aloe, R., & Duque-Carrillo, J. F. (2022). Compact CMOS Wideband Instrumentation Amplifiers for Multi-Frequency Bioimpedance Measurement: A Design Procedure. Electronics, 11(11), 1668. https://doi.org/10.3390/electronics11111668