Receiver Analog Front-End Cascading Transimpedance Amplifier and Continuous-Time Linear Equalizer for Signals of 5 to 30 Gb/s

Abstract

:1. Introduction

2. Design Consideration

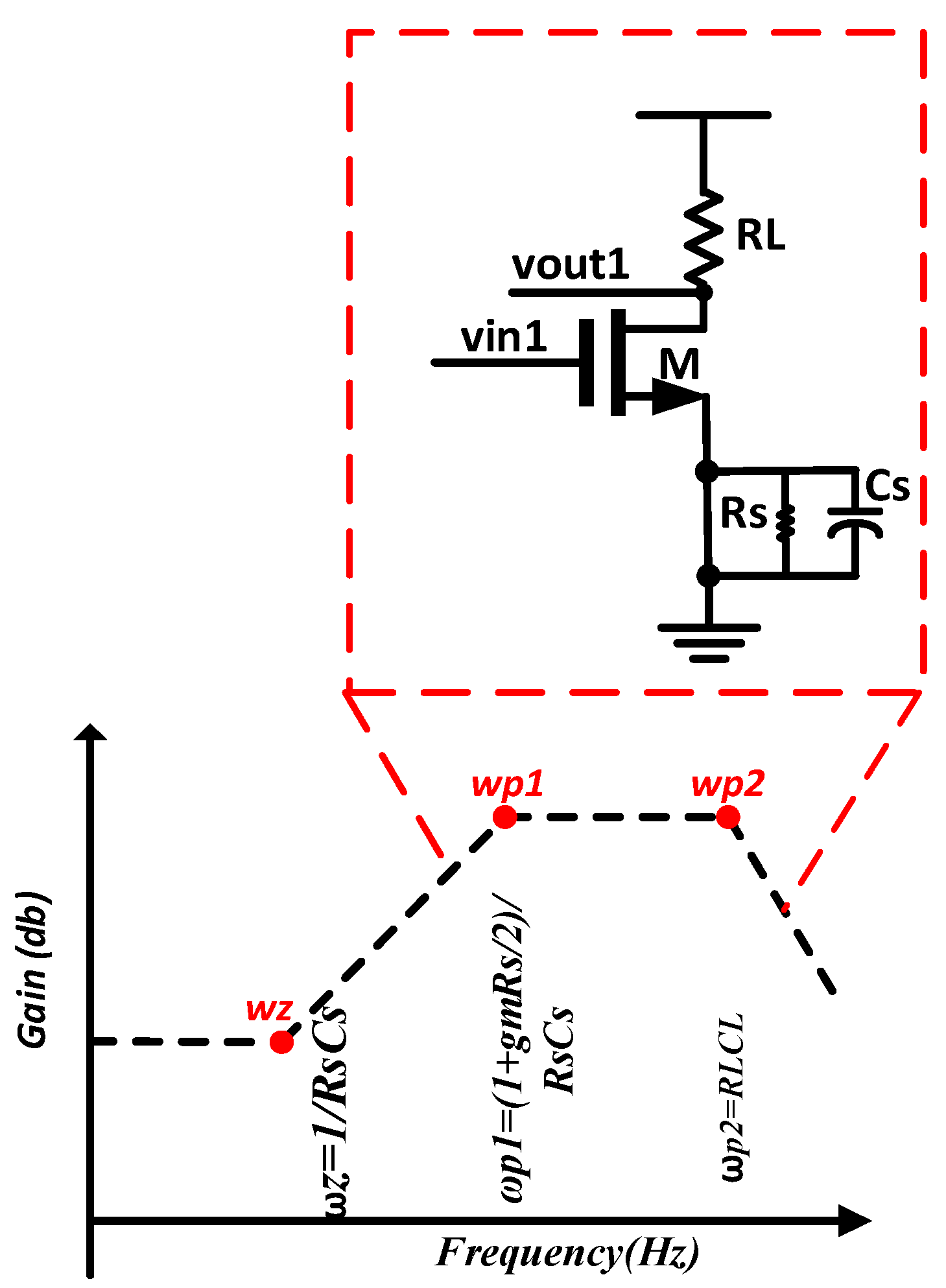

2.1. CTLE

2.2. Proposed Continous-Time Linear Equalizer

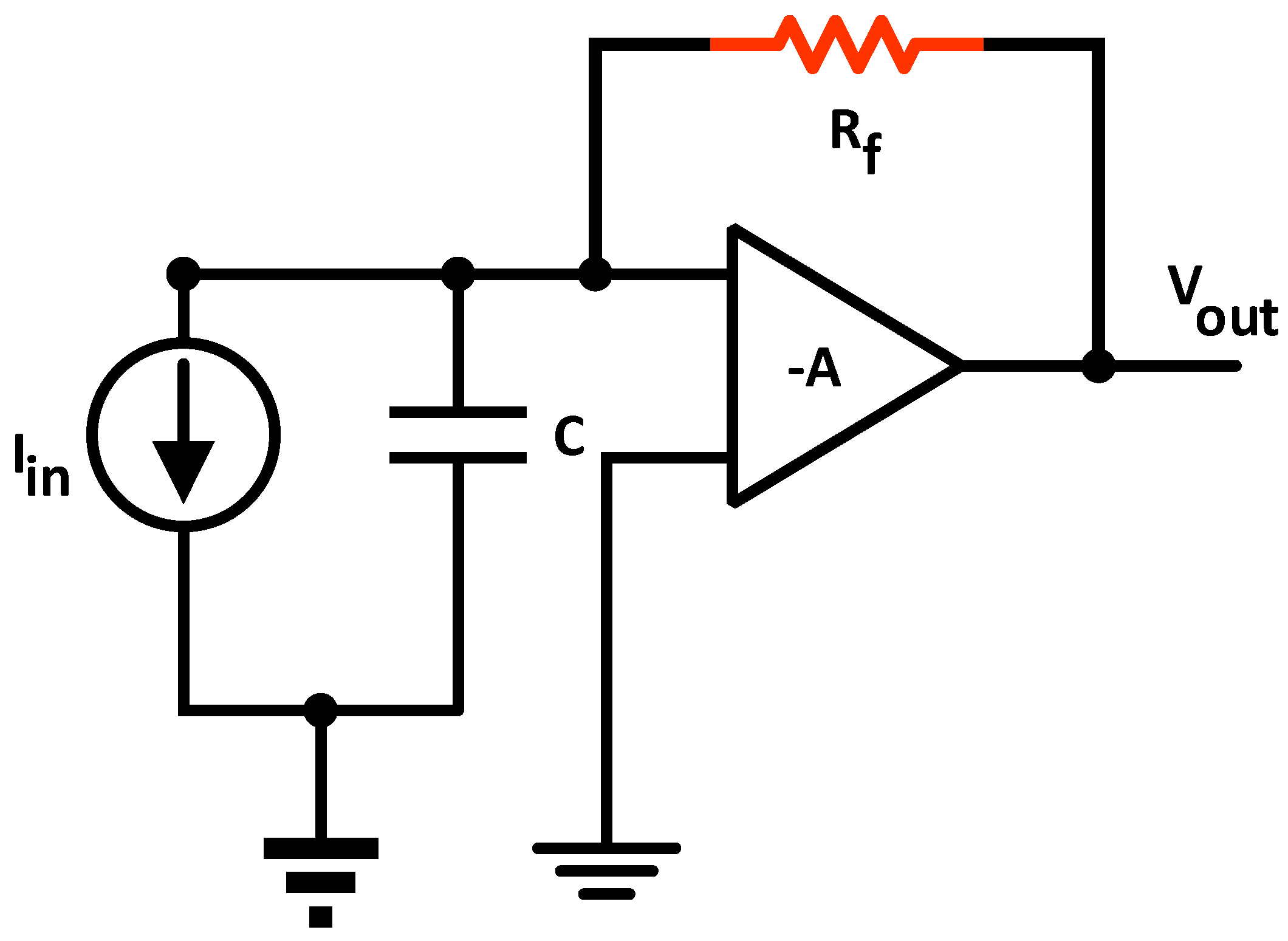

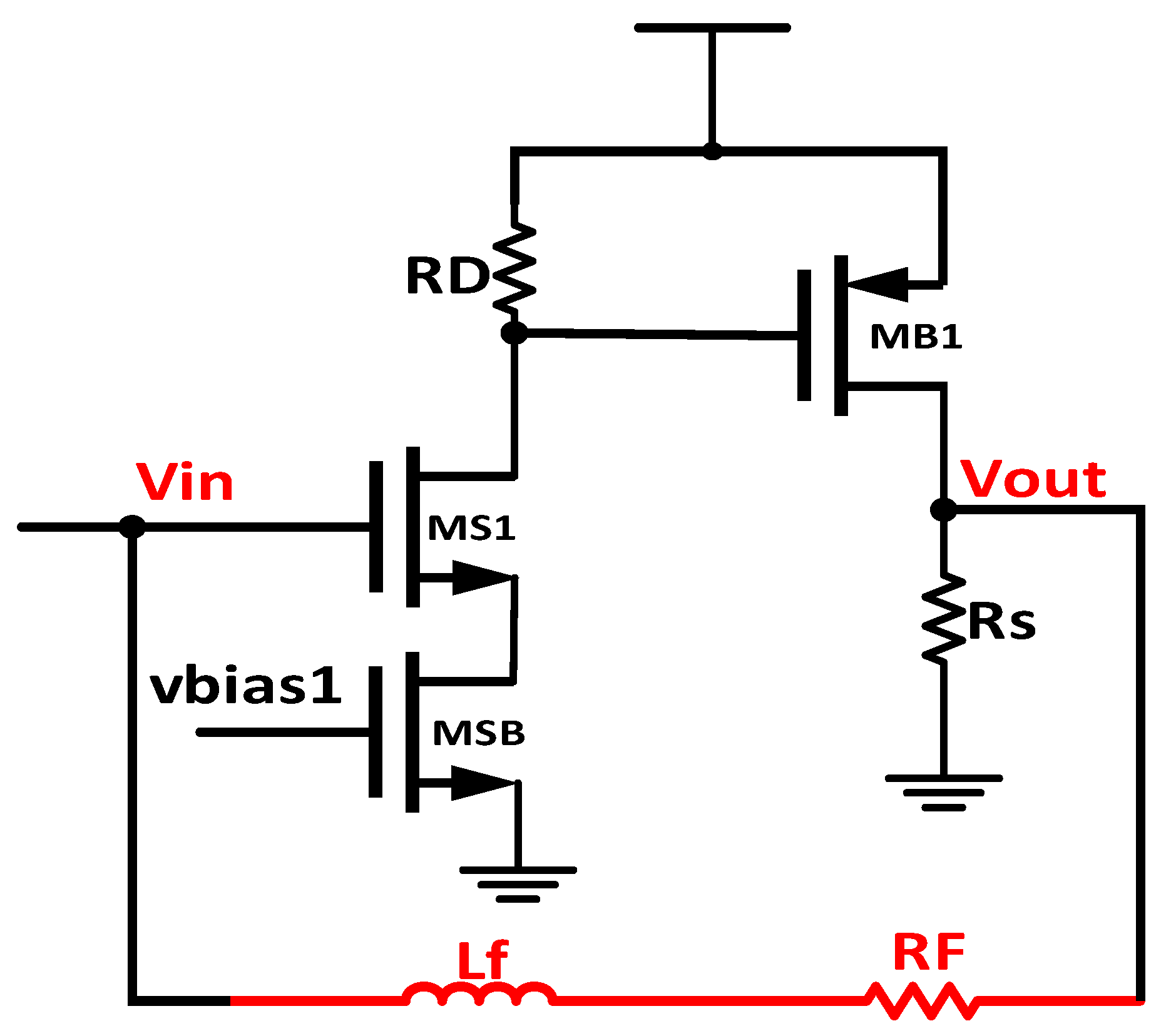

2.3. TIA

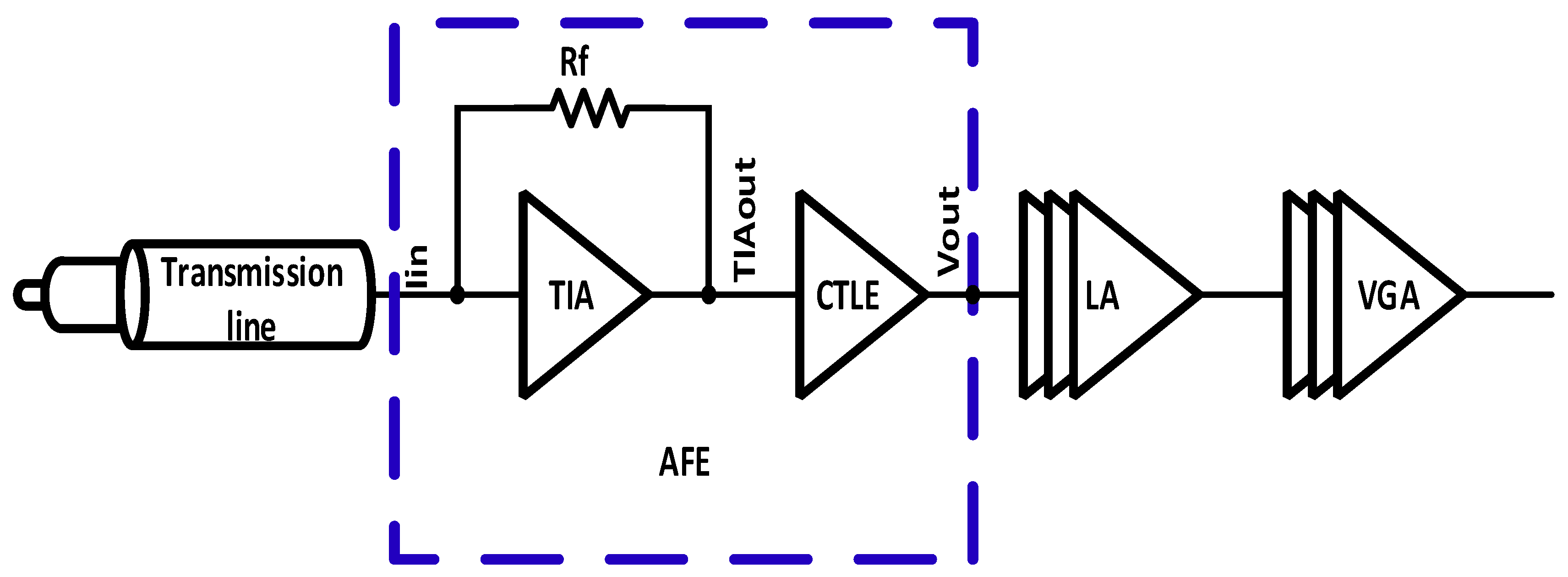

2.4. Reciever AFE Architecture

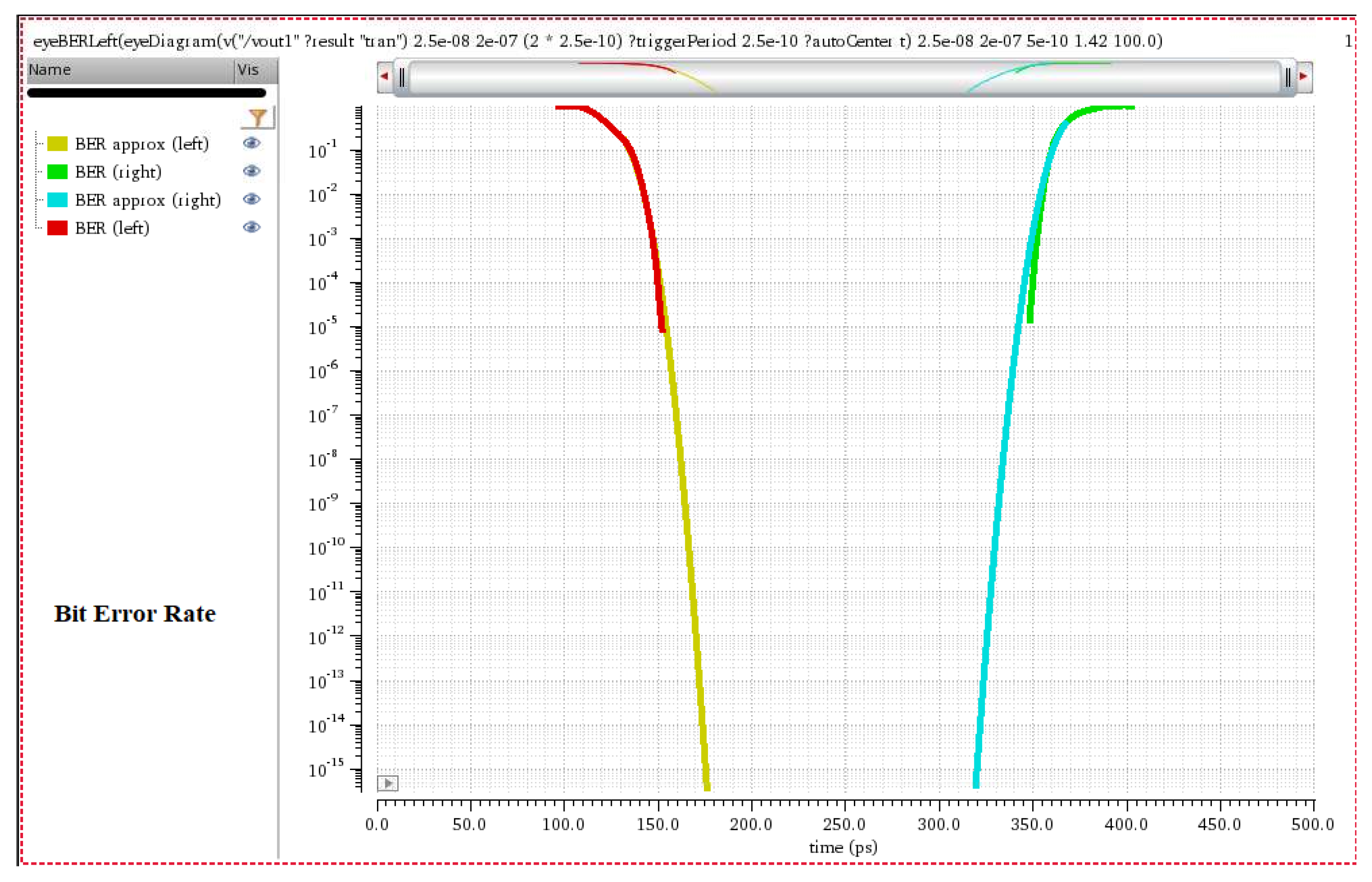

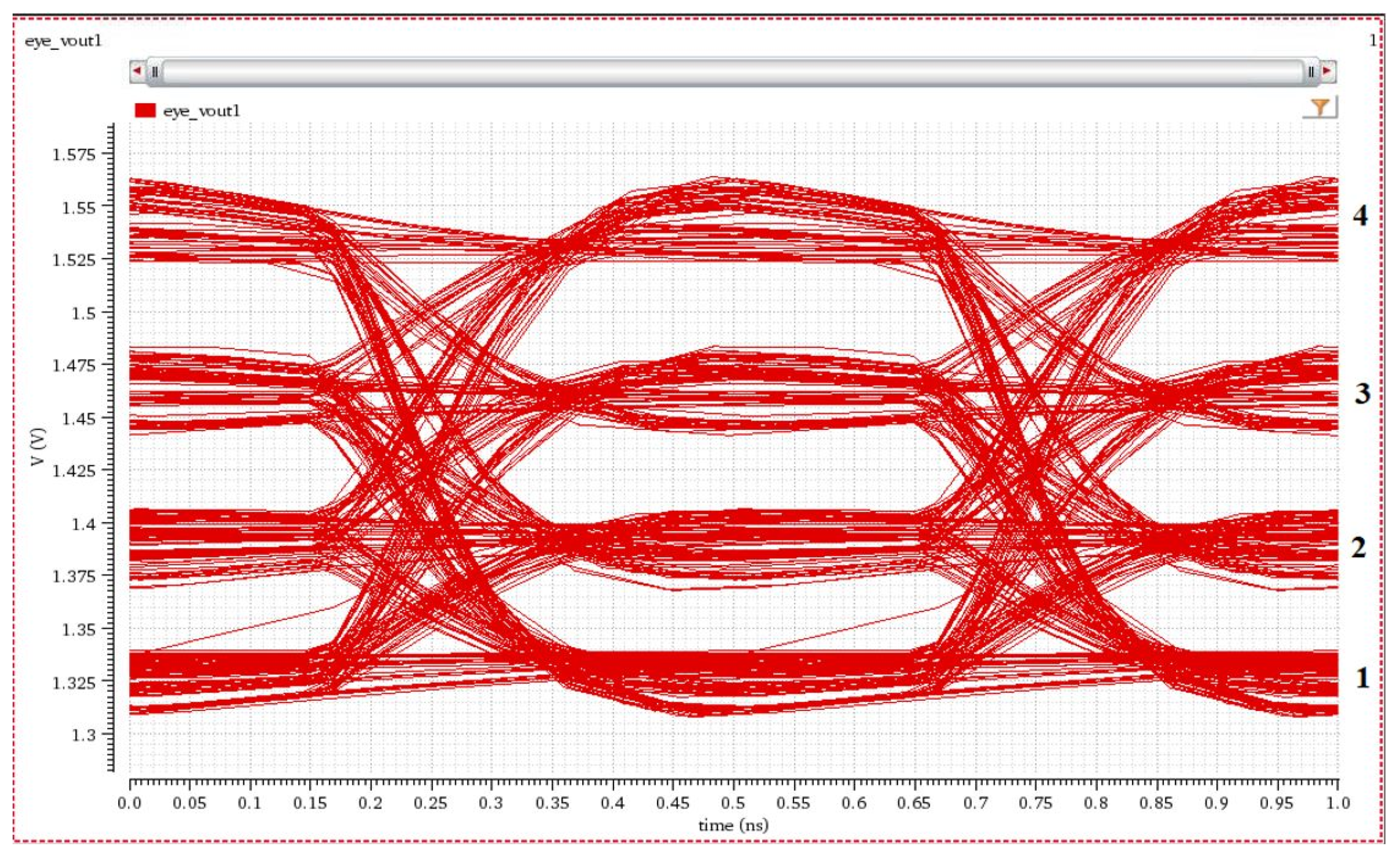

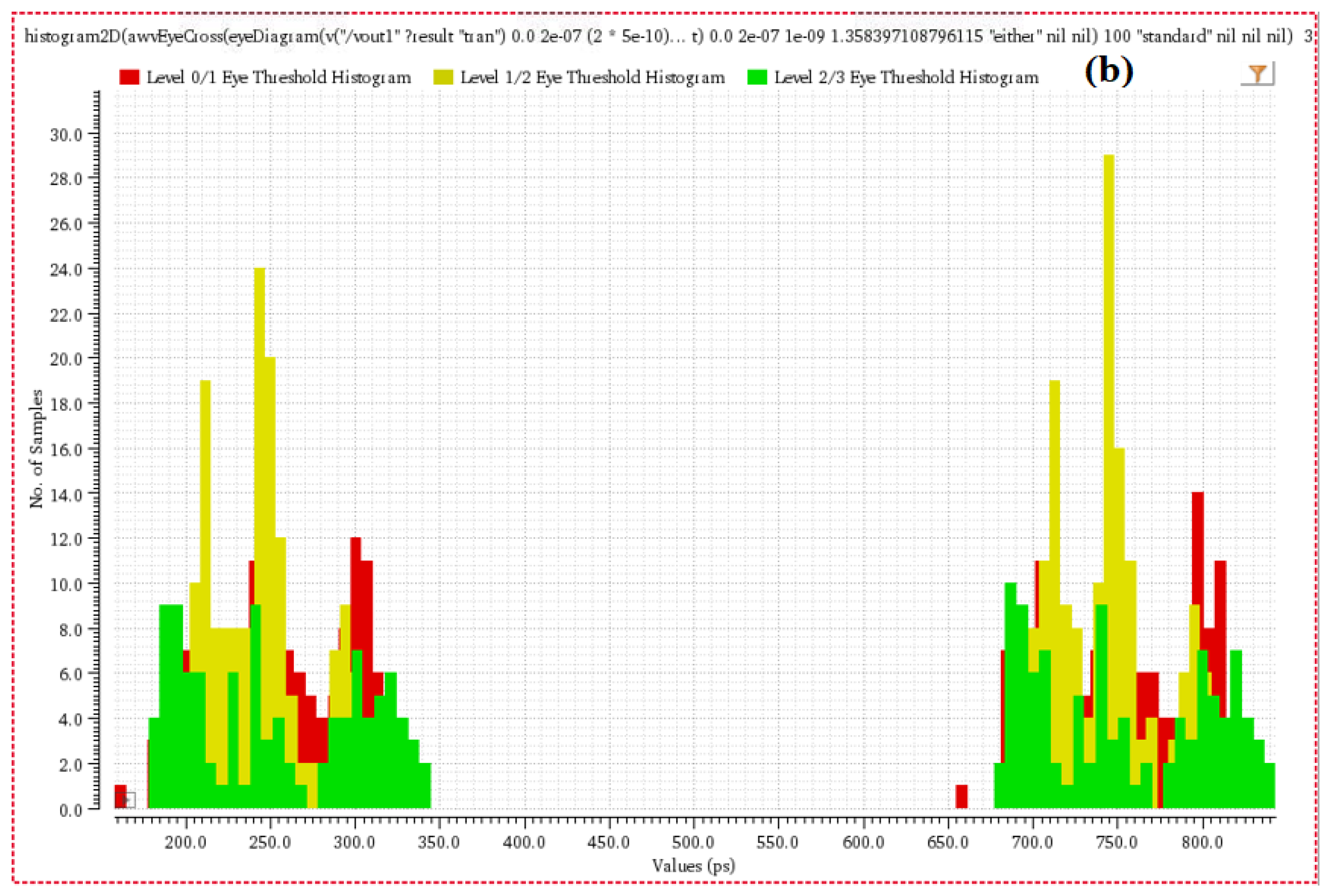

3. Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kimura, H.; Aziz, P.; Jing, P.; Sinha, A.; Narayan, R.; Gao, H.; Jing, P.; Hom, G.; Liang, A.; Zhang, E.; et al. A 28 Gb/s 560 mW Multi-Standard SerDes with Single-Stage Analog Front-End and 14-Tap Decision Feedback Equalizer in 28 nm CMOS. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; Volume 49, pp. 3091–3103. [Google Scholar]

- Takemoto, T.; Yamashita, H.; Yazaki, T.; Chujo, N.; Lee, Y.; Matsuoka, Y. A 4 25-to-28 Gb/s 4.9 mW/Gb/s 9.7 dBm high-sensitivity optical receiver based on 65 nm CMOS for board-to-board interconnects. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 118–119. [Google Scholar]

- Kim, M.; Bae, J.; Ha, U.; Yoo, H.J. A 24-mW 28-Gb/s wireline receiver with low-frequency equalizing CTLE and 2-tap speculative DFE. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 1610–1613. [Google Scholar]

- Parikh, S.; Kao, T.; Hidaka, Y.; Jiang, J.; Toda, A.; Mcleod, S.; Walker, W.; Koyanagi, Y.; Shibuya, T.; Yamada, J. A 32 Gb/s wireline receiver with a low-frequency equalizer, CTLE and 2-Tap DFE in 28 nm CMOS. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 28–29. [Google Scholar]

- Kim, J.; Buckwalter, J.F. A 40-Gb/s optical transceiver front-end in 45 nm SOI CMOS. IEEE J. Solid-State Circuits 2012, 47, 615–626. [Google Scholar] [CrossRef]

- Säckinger, E. Broadband Circuits for Optical Fiber Communication; Wiley: New York, NY, USA, 2005. [Google Scholar]

- Lee, J. A 20-Gb/s Adaptive Equalizer in 0.13-um CMOS Technology. IEEE J. Solid-State Circuits 2006, 41, 2058–2066. [Google Scholar] [CrossRef]

- Zheng, K.; Frans, Y.; Chang, K.; Murmann, B. A 56 Gb/s 6 mW 300 um2 inverter-based CTLE for short-reach PAM2 applications in 16 nm CMOS. In Proceedings of the 2018 IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 8–11 April 2018; pp. 1–4. [Google Scholar]

- Hyun, C.; Ko, H.; Chae, J.; Park, H.; Kim, S. A 20 Gb/s Dual-Mode PAM4/NRZ Single-Ended Transmitter with RLM Compensation. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–4. [Google Scholar]

- Roshan-Zamir, A.; Elhadidy, O.; Yang, H.; Palermo, S. A Reconfigurable 16/32 Gb/s Dual-Mode NRZ/PAM4 SerDes in 65-nm CMOS. IEEE J. Solid-State Circuits 2017, 52, 2430–2447. [Google Scholar] [CrossRef]

- Komatsu, Y.; Shinmyo, A.; Kato, S.; Funabashi, M.; Hatooka, K.; Fujita, M.; Tanaka, K.; Yamasaki, A.; Fukuda, K. A 0.25–27-Gb/s PAM4/NRZ Transceiver with Adaptive Power CDR and Jitter Analysis. IEEE J. Solid-State Circuits 2019, 54, 2802–2811. [Google Scholar] [CrossRef]

- Lee, J.; Chiang, P.; Peng, P.; Chen, L.; Weng, C. Design of 56 Gb/s NRZ and PAM4 SerDes Transceivers in CMOS Technologies. IEEE J. Solid-State Circuits 2015, 50, 2061–2073. [Google Scholar] [CrossRef]

- Lee, J.; Chen, M.; Wang, H. Design and Comparison of Three 20-Gb/s Backplane Transceivers for Duobinary, PAM4, and NRZ Data. IEEE J. Solid-State Circuits 2008, 43, 2120–2133. [Google Scholar] [CrossRef] [Green Version]

- Razavi, B. The Transimpedance Amplifier [A Circuit for All Seasons]. IEEE Solid-State Circuits Mag. 2019, 11, 10–97. [Google Scholar] [CrossRef]

- Wang, J.; Pan, Q.; Qin, Y.; Chen, X.; Hu, S.; Bai, R. A fully-integrated 25 Gb/s low-noise TIA+CDR optical receiver designed in 40nm-CMOS. In Proceedings of the IEEE Transactions on Circuits and Systems II: Express Briefs, Tainan, Taiwan, 27 June 2019; pp. 67–68. [Google Scholar]

- Lee, J.; Lee, K.; Kim, H.; Kim, B.; Park, K.; Jeong, D. A 0.1-pJ/b/dB 1.62-to-10.8-Gb/s Video Interface Receiver with Jointly Adaptive CTLE and DFE Using Biased Data-Level Reference. IEEE J. Solid-State Circuits 2020, 55, 2186–2195. [Google Scholar] [CrossRef]

- Lin, Y.T.; Chen, H.C.; Wang, T.; Lin, Y.S.; Lu, S.S. S. 3–10-GHz ultra-wideband low-noise amplifier utilizing miller effect and inductive shunt-shunt feedback technique. IEEE Trans. Microw. Theory Techn. 2007, 55, 1832–1843. [Google Scholar] [CrossRef]

- Choi, J.-S.; Hwang, M.-S.; Jeong, D.-K. A 0.18-um CMOS 3.5-Gb/s continuous-time adaptive cable equalizer using enhanced low-frequency gain control method. IEEE J. Solid-State Circuits 2004, 39, 419–425. [Google Scholar] [CrossRef]

- Li, D.; Minoia, G.; Repossi, M.; Baldi, D.; Temporiti, E.; Mazzanti, A. A low-noise design technique for high-speed CMOS optical receivers. IEEE J. Solid-State Circuits 2014, 49, 1437–1447. [Google Scholar] [CrossRef]

- Li, C.; Palermo, S. A low-power 26-GHz transformer-based regulated cascode SiGe BiCMOS transimpedance amplifier. IEEE J. Solid-State Circuits 2013, 48, 1264–1275. [Google Scholar] [CrossRef]

- Galal, S.; Razavi, B. 10-Gb/s limiting amplifier and laser/modulator driver in 0.18-m CMOS technology. IEEE J. Solid-State Circuits 2003, 38, 2138–2146. [Google Scholar] [CrossRef]

- Hsiao, J.; Jhou, D.; Lee, T. A 10-Gb/s equalizer with digital adaptation. In Proceedings of the 2017 International SoC Design Conference (ISOCC), Seoul, Korea, 5–8 November 2017; pp. 38–39. [Google Scholar]

- Chen, K.-Y.; Chen, W.-Y.; Liu, S.-I. A 0.035-pJ/bit/dB 20-Gb/s adaptive linear equalizer with an adaptation time of 2.68 μs. IEEE Trans. Circuits Syst. II Exp. Briefs 2017, 64, 645–649. [Google Scholar] [CrossRef]

- Raj, M.; Monge, M.; Emami, A. Amodelingg and nonlinear equalization technique for a 20 Gb/s 0.77 pJ/b VCSEL transmitter in 32 nm SOI CMOS. IEEE J. Solid-State Circuits 2016, 51, 1734–1743. [Google Scholar] [CrossRef]

- Kim, J.; Pak, J.S.; Cho, J.; Song, E.; Cho, J.; Kim, H.; Song, T.; Lee, J.; Lee, H.; Park, K.; et al. High-Frequency Scalable Electrical Model and Analysis of a Through Silicon Via (TSV). IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 181–195. [Google Scholar] [CrossRef]

| Equalization | [9] | [10] | [12] | [13] | This Work |

|---|---|---|---|---|---|

| Data rate (Gbps) | 10 | 16 | 16 | 20 | 5–15 |

| Channel loss (dB)Nyquist | NA | 27.6 | 20.5 | 12 | 16 |

| 0.62 | 0.18 | 0.16 | NA | 0.16 | |

| Supply (V) | 1 | 1.2 | 1.2 | 1.5 | 1.8 |

| Power (mW) | 72 | 173.17 | 173.17 | 100 | 14 |

| Technology | 65 nm | 65 nm | 65 nm | 90 nm | 180 nm |

| Reference | [1] | [4] | [15] | [23] | This Work |

|---|---|---|---|---|---|

| Technology CMOS | 28 nm | 28 nm | 40 nm | 40 nm | 180 nm |

| Power supply | 1.5 V | 0.9 V | 1 V | 1.2 V | 1.8 V |

| Equalization | 14-tap CTLE | CTLE+DFE | CTLE | CTLE | CTLE |

| Data rate range (Gbps) | 1.25~28.5 | 32 | 8~10 | 20 | 5~30 |

| Power (mW) | 560 | 240 | 10 | 12.8 | 27 |

| Channel loss (@GHz) | 34 dB@14 | 37 dB@16 | 17 dB@4 | 18 dB@10 | 28 dB@15 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Challayya Naidu, P.V.S.; Lu, C.-W. Receiver Analog Front-End Cascading Transimpedance Amplifier and Continuous-Time Linear Equalizer for Signals of 5 to 30 Gb/s. Electronics 2022, 11, 1546. https://doi.org/10.3390/electronics11101546

Challayya Naidu PVS, Lu C-W. Receiver Analog Front-End Cascading Transimpedance Amplifier and Continuous-Time Linear Equalizer for Signals of 5 to 30 Gb/s. Electronics. 2022; 11(10):1546. https://doi.org/10.3390/electronics11101546

Chicago/Turabian StyleChallayya Naidu, Pragada Venkata Satya, and Chih-Wen Lu. 2022. "Receiver Analog Front-End Cascading Transimpedance Amplifier and Continuous-Time Linear Equalizer for Signals of 5 to 30 Gb/s" Electronics 11, no. 10: 1546. https://doi.org/10.3390/electronics11101546

APA StyleChallayya Naidu, P. V. S., & Lu, C.-W. (2022). Receiver Analog Front-End Cascading Transimpedance Amplifier and Continuous-Time Linear Equalizer for Signals of 5 to 30 Gb/s. Electronics, 11(10), 1546. https://doi.org/10.3390/electronics11101546