Design and Hardware Implementation of an IGBT-Based Half-Bridge Cell for Modular Voltage Source Inverters

Abstract

:1. Introduction

2. A Review on Power Converter Design Methodologies

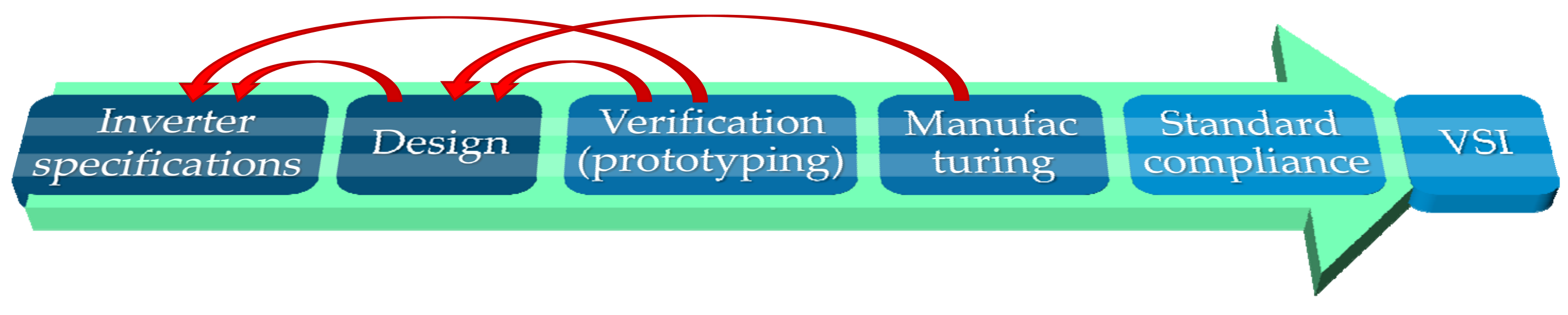

2.1. Traditional Design

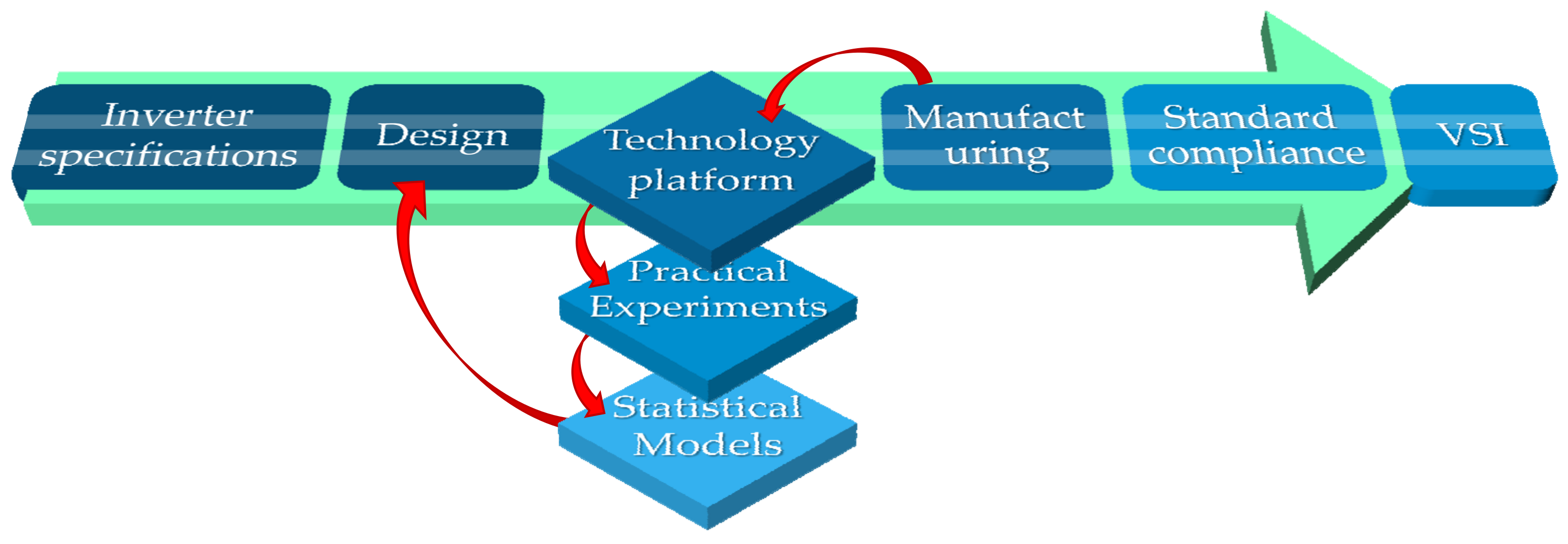

2.2. Design for Reliability

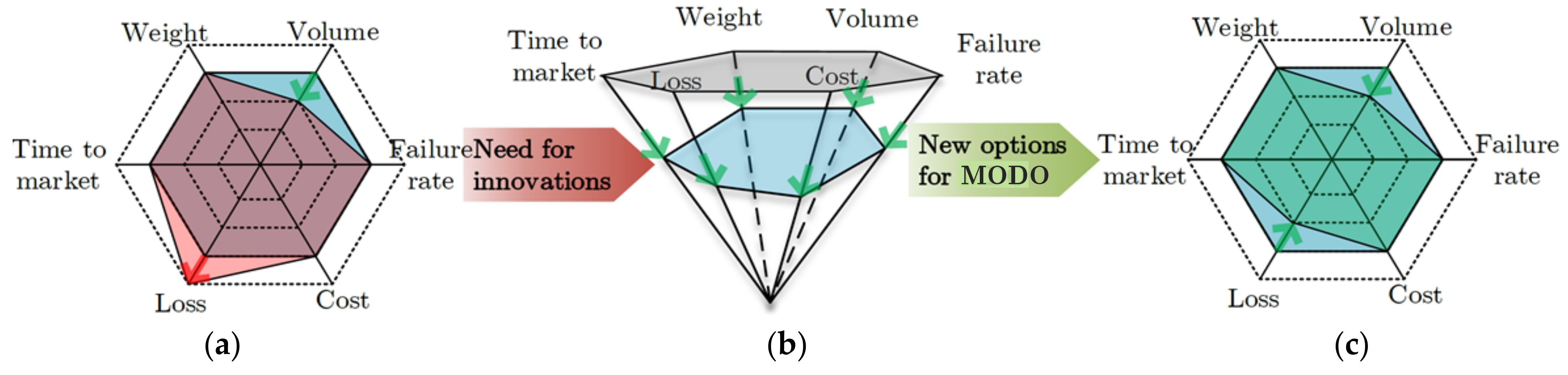

2.3. Multi Objective Design Optimization

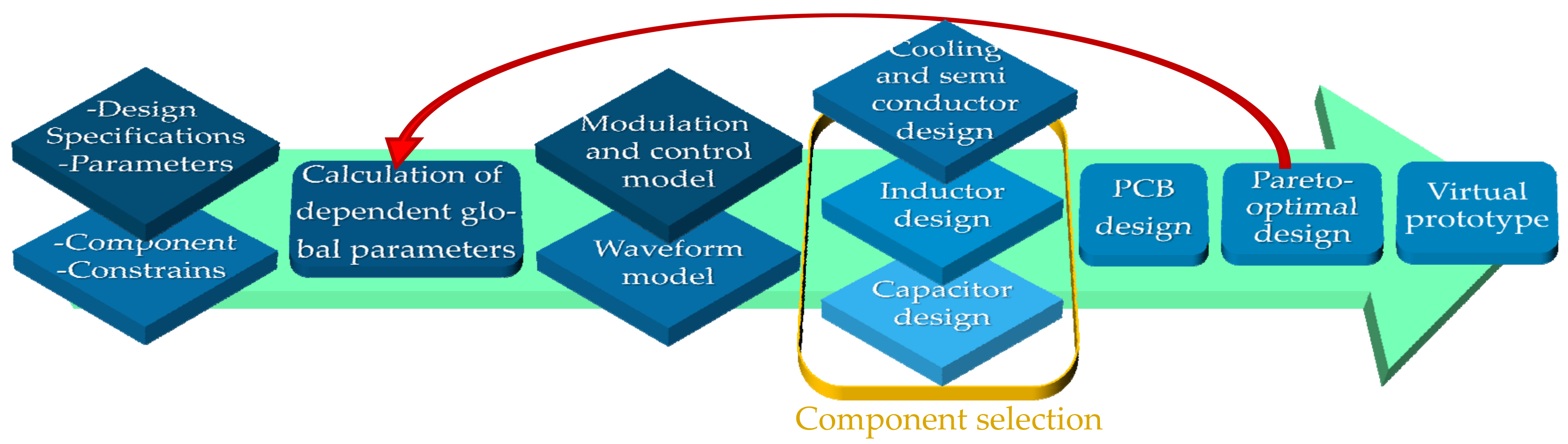

2.4. Automated Design

3. Background

3.1. Development Purpose and Contribution

- Low power generation facilities with renewable sources of different power levels can be found, and it is difficult to obtain different VSIs for each installed power level. Additionally, in case that the installed power is modified, the VSI must also be changed.

- Many times, a VSI of adequate power is not available on the local market and an oversized VSI is installed, resulting in an excessive investment cost.

- Sometimes the VSIs do not comply with local grid regulations and standards (operational issues and/or design issues), which can limit their use [22].

- It is difficult to find single-phase VSIs (with or without interconnection capacity) for small customers/generators (homes, workshops, shops, health centers, rural schools, etc.) than three-phase VSIs for large consumers (industry, electric traction, etc.).

- Researchers and educators still find it expensive to build unconventional converter topologies with commercial hardware for research and teaching purposes.

3.2. Design Considerations

- Low consumption and reduced EMI

- High efficiency and reliability.

- Modularity and reduced size.

- Local grid regulations and international standards.

- Natural convection cooling

4. Design Process

4.1. Specifications and Key Components Selection

4.1.1. DC-Link Capacitance

4.1.2. Power Semiconductor Switches (PSSs)

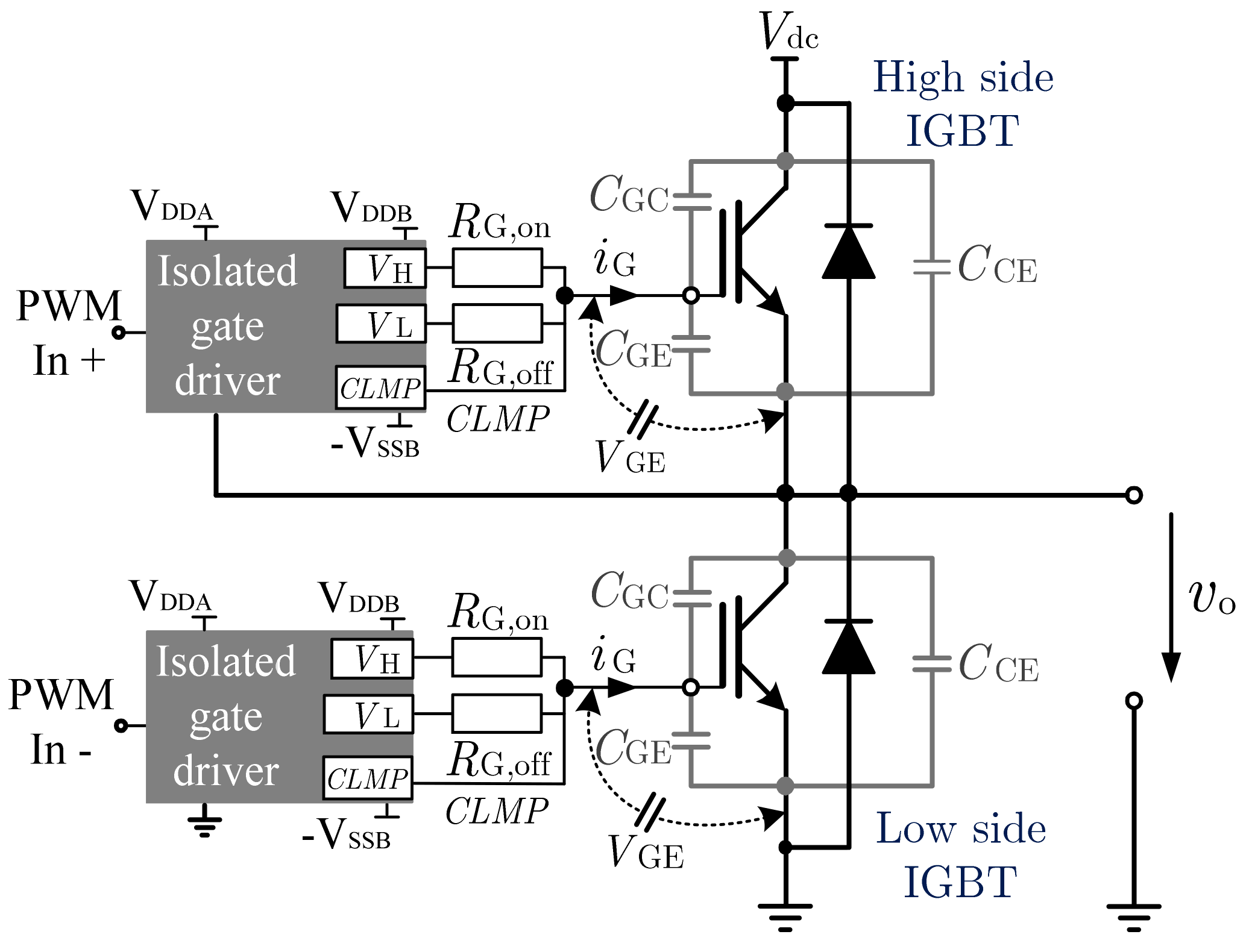

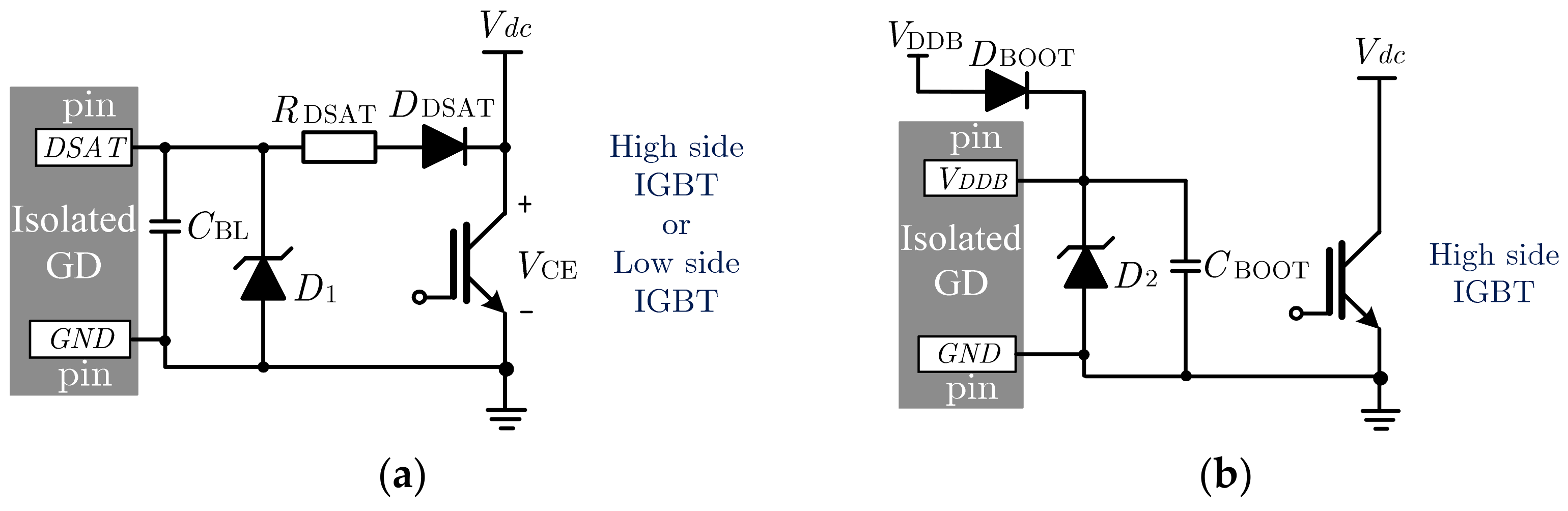

4.1.3. Gate Driver

4.2. Snubber Circuit

4.3. Heat Sink

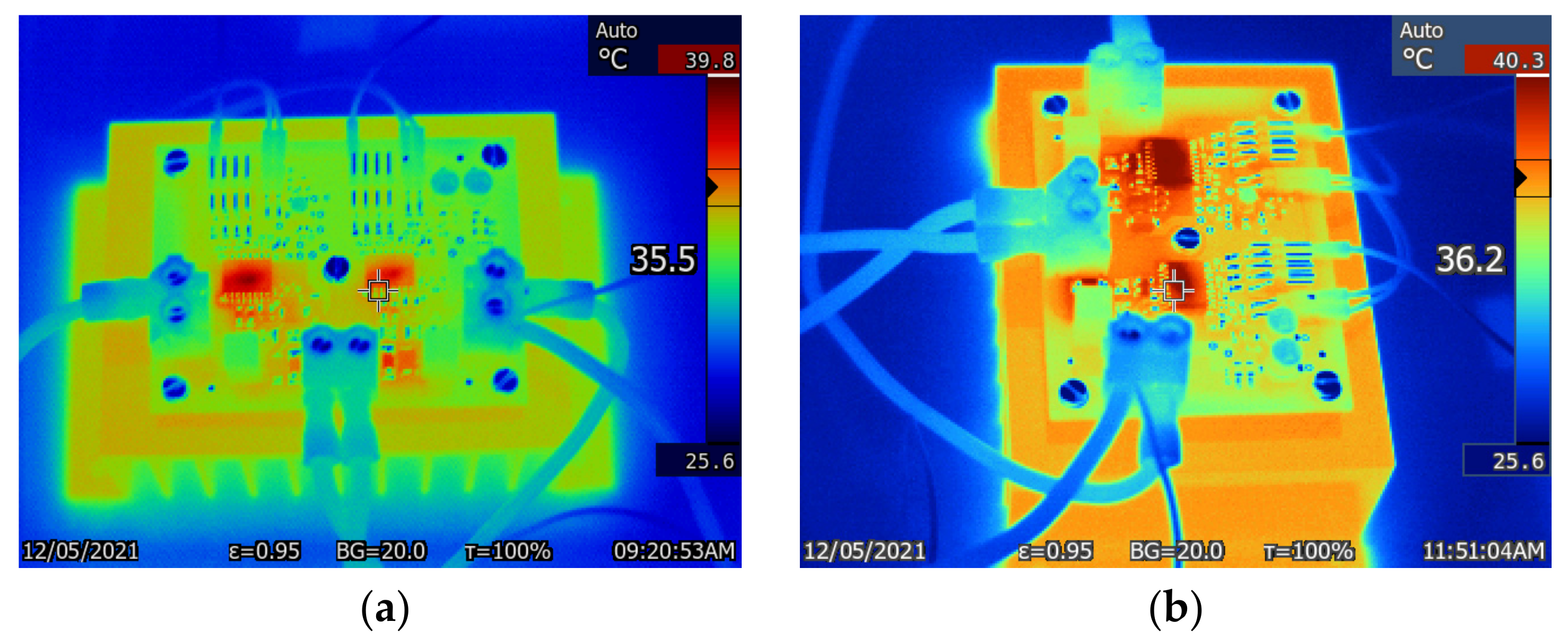

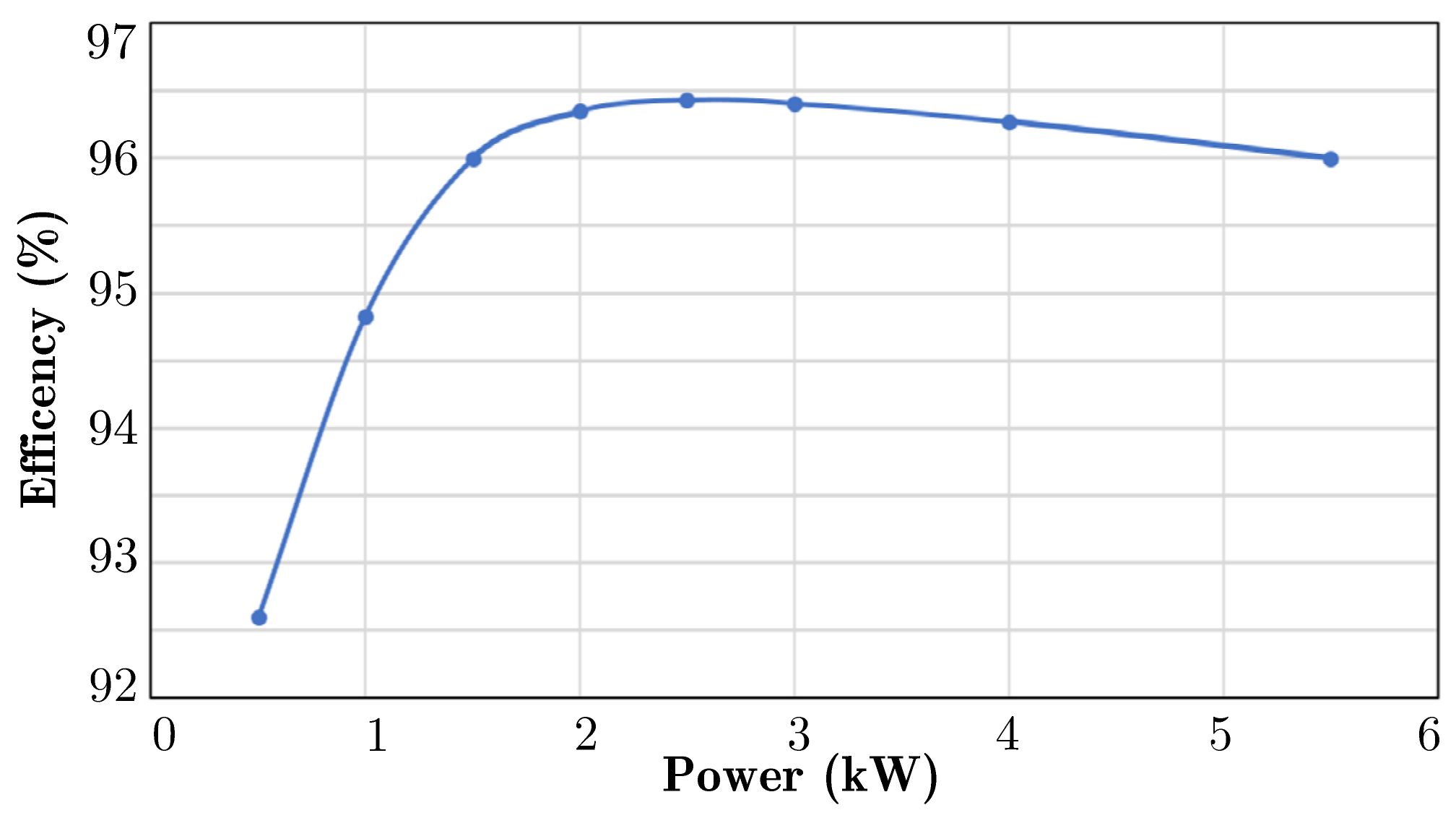

5. Hardware Implementation and Results

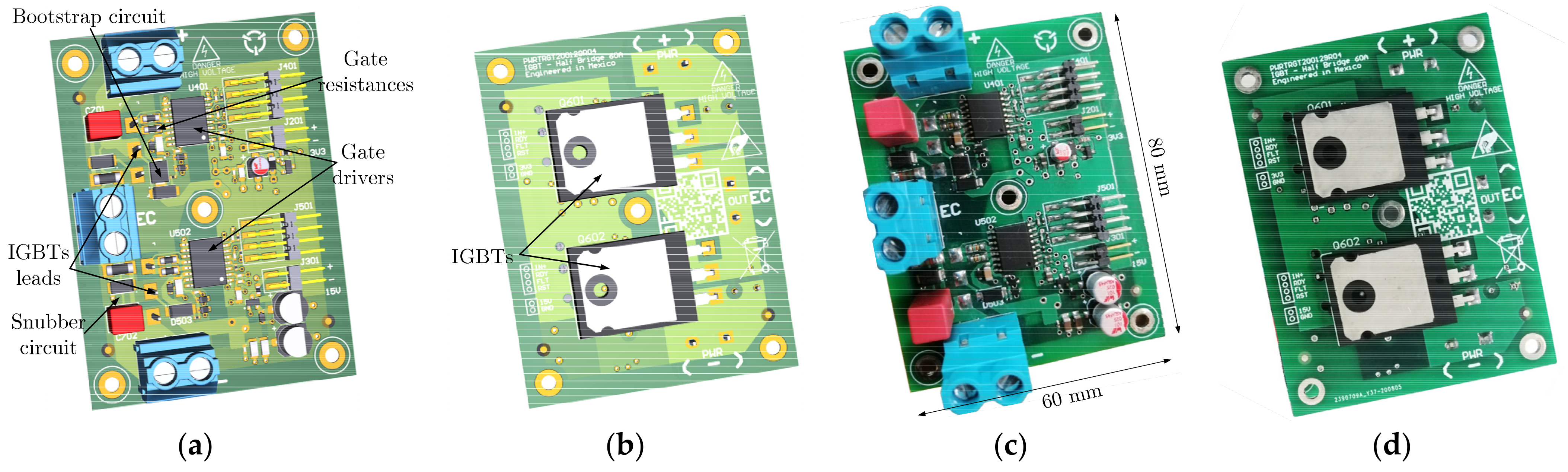

5.1. PCB Design

5.1.1. Standards

5.1.2. Design Considerations for Low Stray Inductance and Reduced EMI

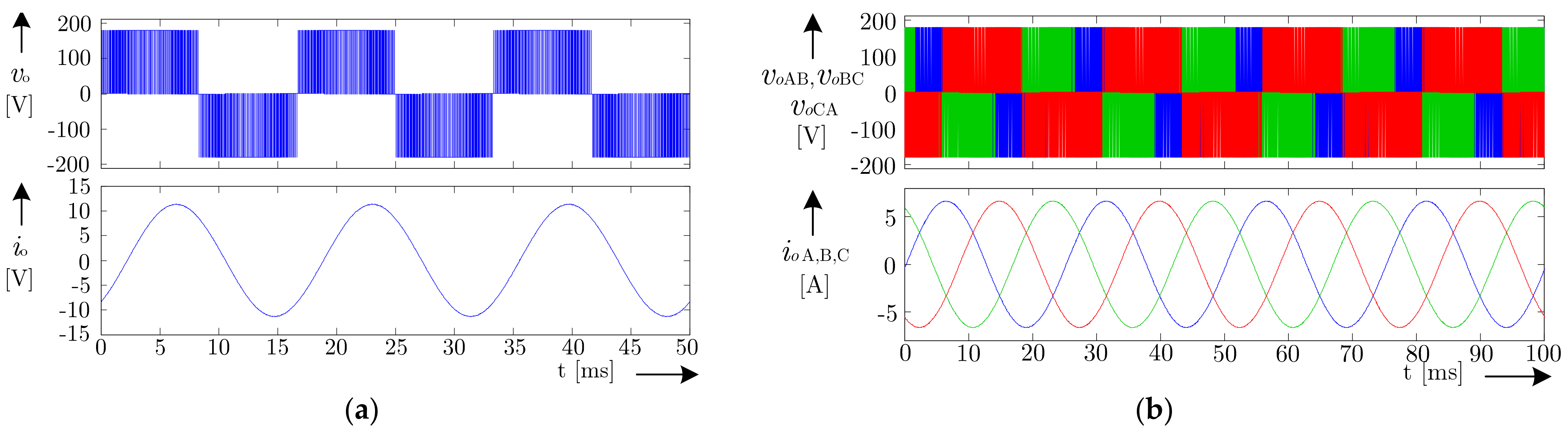

5.2. Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| AC | Alternating current |

| AD | Automated design |

| CAD | Computer-aided design |

| DC | Direct current |

| DFR | Design for reliability |

| EMI | Electromagnetic interference |

| FB | Full bridge |

| GaN-IGBT | Gallium nitride insulated-gate bipolar transistor |

| GD | Gate driver |

| GND | Ground |

| HB | Half-bridge |

| HP | Horsepower |

| IGBT | Insulated-gate bipolar transistor |

| IPC | Institute of printed circuits |

| MLI | Multilevel inverters |

| MODO | Multi objective design optimization |

| MOSFET | Metal-oxide-semiconductor field-effect transistor |

| NOM | Official Mexican standards |

| PCB | Printed circuit board |

| PSS | Power semiconductor switch |

| rms | Root mean square |

| siC-IGBT | Silicon carbide insulated-gate bipolar transistor |

| SPWM | Sinusoidal Pulse-width modulation |

| TD | Traditional design |

| THD | Total harmonic distortion |

| VSI | Voltage-source inverter |

References

- Trzynadlowski, A.M. Introduction to Modern Power Electronics, 2nd ed.; Wiley: Hoboken, NJ, USA, 2010; pp. 269–3086. [Google Scholar]

- Rashid, M.H. Power Electronics Handbook. In Devices, Circuits, and Applications, 3rd ed.; Elsevier: Pensacola, FL, USA, 2015; pp. 357–360. [Google Scholar]

- Kolar, J.W. Power electronic design 4.0. In In Proceedings of the Workshop at the ECPE Design Automation Expert Discussion, Zurich, Switzerland, 19 July 2019. [Google Scholar]

- Marques Cardoso, A.J. Power electronics design methods and automation in the digital era: Evolution of design automation tools. IEEE Power Electron. Mag. 2020, 7, 36–40. [Google Scholar] [CrossRef]

- Nami, A.; Liang, J.; Dijkhuizen, F.; Demetriades, G.D. Modular multilevel converters for HVDC applications: Review on converter cells and functionalities. IEEE Trans. Power Electron. 2015, 30, 18–36. [Google Scholar] [CrossRef]

- Perez. M.A.; Steffen, B.; Rodriguez, R.; Kouro, S.; Lizana, R. Circuit topologies, modeling, control schemes, and applications of modular multilevel converters. IEEE Trans. Power Electron. 2015, 30, 4–17. [Google Scholar] [CrossRef]

- Hassan, A.; Yang, X.; Che, W.; Houran, M.A. A state of the art of the multilevel inverters with reduced count components. Electronics 2020, 9, 1924. [Google Scholar] [CrossRef]

- Buttay, C.; Martin, C.; Morel, F.; Caillaud, R.; Le Leslé, J.; Mrad, R.; Degrenne, N.; Mollov, S. Application of the PCB-embedding technology in power electronics–state of the art and proposed development. In Proceedings of the Second International Symposium on 3D Power Electronics Integration and Manufacturing (3D-PEIM), College Park, MD, USA, 25–27 June 2018; pp. 1–10. [Google Scholar]

- Software Engineering Center (IPA/SEC). ESPR Embedded System Development Process. Reference Guide, version 2.0; Information-Technology Promotion Agency: Tokyo, Japan, 2012; pp. 217–227. [Google Scholar]

- Nawawi, A.; Tong, C.F.; Yin, F.; Sakanova, A.; Liu, Y.; Liu, Y.; Kai, M.; See, K.Y.; Tseng, K.-J.; Simanjorang, R.; et al. Design and demonstration of high power density inverter for aircraft applications. IEEE Trans. Ind. Appl. 2017, 53, 1168–1176. [Google Scholar] [CrossRef]

- Lu, H.; Bailey, C.; Yin, C. Design for reliability of power electronics. Microelectron. Reliab. 2009, 49, 1250–1255. [Google Scholar] [CrossRef]

- Wang, H.; Ma, K.; Blaabjerg, F. Design for reliability of power electronic systems. In Proceedings of the 38th Annual Conference IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 33–44. [Google Scholar]

- Wang, H.; Liserre, M.; Blaabjerg, F.; Rimmen, P.P.; Jacobsen, J.B.; Kvisgaard, T.; Landkildehus, J. Transitioning to physics-of-failure as a reliability driver in power electronics. IEEE Trans. Emerg. Sel. Top. Power Electron. 2014, 2, 97–114. [Google Scholar] [CrossRef]

- Raggl, K.; Nussbaumer, T.; Doerig, G.; Biela, J.; Kolar, J.W. Comprehensive design and optimization of a high-power-density single-phase boost PFC. IEEE Trans. Ind. Electron. 2009, 56, 2574–2587. [Google Scholar] [CrossRef]

- Kolar, L.W.; Biela, J.; Waffler, S.; Friedli, T.; Badstuebner, U. Performance trends and limitations of power electronic systems. In Proceedings of the 6th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 16–18 March 2010; pp. 1–20. [Google Scholar]

- Burkart, R.M. Advanced Modeling and Multi-Objective Optimization of Power Electronic Converter Systems. Ph.D. Thesis, ETH, Zurich, Switzerland, 2016. [Google Scholar]

- Mehrabadi, N.R. Power Electronics Design Methodologies with Parametric and Model-Form Uncertainty Quantification. Ph.D. Thesis, Virginia Polytechnic Institute and State University, Blacksburg, VA, USA, 2018. [Google Scholar]

- Bindra, A.; Mantooth, A. Modern tool limitations in design automation: Advancing automation in design tools is gathering momentum. IEEE Power Electron. Mag. 2019, 6, 28–33. [Google Scholar] [CrossRef]

- Voldoire, A.; Schanen, J.-L.; Ferrieux, J.-P.; Derbey, A.; Gautier, C. Three-phase PWM voltage-source-inverter weight optimization for aircraft application using deterministic algorithm. Electronics 2020, 9, 1393. [Google Scholar] [CrossRef]

- Andreta, A.; Lavado Villa, L.; Lembeye, Y.; Crebier, J.C. A novel automated design methodology for power electronics converters. Electronics 2021, 10, 271. [Google Scholar] [CrossRef]

- Bughneda, A.; Salem, M.; Richelli, A.; Ishak, D.; Alatai, S. Review of multilevel inverters for PV energy system applications. Energies 2021, 14, 1585. [Google Scholar] [CrossRef]

- Araujo, S.V.; Zacharias, P.; Mallwitz, R. Highly efficient single-phase transformerless inverters for grid-connected photovoltaic systems. IEEE Trans. Ind. Electron. 2010, 57, 3118–3128. [Google Scholar] [CrossRef]

- Renken, F. The dc-link capacitor current in pulsed single-phase H-bridge inverters. In Proceedings of the EPE Conference, Dresden, Germany, 11–14 September 2005; Volume 10, pp. 1–10. [Google Scholar]

- Vujacic, M.; Hammami, M.; Srndovic, M.; Grandi, G. Theoretical and experimental investigation of switching ripple in the DC-link voltage of single-phase H-bridge PWM Inverters. Energies 2017, 10, 1189. [Google Scholar] [CrossRef]

- Chen, T.; Li, S.; Fahimi, B. Analysis of dc-link voltage ripple in voltage source inverters without electrolytic capacitor. In Proceedings of the IECON Conference, Washington, DC, USA, 20–23 October 2018; pp. 1–8. [Google Scholar]

- Blake, C.; Bull, C. IGBT or MOSFET: Choose Wisely; Data Sheet No. PD60147; International Rectifier: El Segundo, CA, USA, 2005. [Google Scholar]

- Dodge, J.; Hess, J. Advanced Power Technology, Application Note APT0201-IGBT Tutorial. Available online: https://www.microsemi.com/document-portal/doc_view/14696-igbt-tutorial (accessed on 6 August 2021).

- Silicon Labs. An1009: Driving MOSFET and IGBT Switches Using the Si828x. Available online: https://www.skyworksinc.com/-/media/Skyworks/SL/documents/public/application-notes/AN1009-driving-mosfet-and-igbt-switches-using-the-si828x.pdf (accessed on 15 August 2021).

- Lobsiger, Y. Closed-Loop IGBT Gate Drive and Current Balancing Concepts. Ph.D. Thesis, ETH, Zurich, Switzerland, 2014. [Google Scholar]

- Fuji Electric Co. Ltd. Chapter 7 Gate drive circuit design. In Catalog Product Specifications; Fuji Electric Co: Offenbach, Germany, 2016. [Google Scholar]

- Skyworks. Si8285/86: Data Sheet. Available online: https://www.skyworksinc.com/-/media/SkyWorks/SL/documents/public/data-sheets/si8285-86-data-sheet.pdf#unique_8_fig_z55_jqw_m5 (accessed on 5 May 2021).

- Skyworks. AN486: High-Side Bootstrap Design Using ISO Drivers in Power Delivery Systems; Skyworks: Irvine, CA, USA, 2021. [Google Scholar]

- Mora, A.; Juliet, J.; Santander, A.; Lezana, P. Dead-time and semiconductor voltage drop compensation for cascaded H-bridge converters. IEEE Trans. Ind. Electron. 2016, 63, 7833–7842. [Google Scholar] [CrossRef]

- Yamashita, Y.; Furuta, J.; Inamori, S.; Kobayashi, K. Design of RCD snubber considering wiring inductance for MHz-switching of SiC-MOSFET. In Proceedings of the 18th IEEE Workshop on Computers in Power Electronics, Stanford, CA, USA, 9–12 July 2017; pp. 1–6. [Google Scholar]

- Lee, S. How to Select a Heat Sink. Available online: https://www.electronics-cooling.com/1995/06/how-to-select-a-heat-sink/ (accessed on 9 August 2021).

- Künzi, R. Thermal Design of Power Electronics Circuits; CERN Yellow Report CERN-2015-003; CERN: Baden, Switzerland, 2014; pp. 1–7. [Google Scholar]

- IPC. Homepage. Available online: https://www.ipc.org/ (accessed on 7 June 2021).

- Binz, R.; Bracho, R.; Anderson, A.; Coddington, M.H.; Hale, E.T.; Ingram, M.; Martin, M.; Mendoza, C.I.; Normark, B.; Olofsson, M.; et al. A Report on the Implementation of Smart Grids in Mexico NREL/TP-7A40-72699; National Renewable Energy Laboratory: Golden, CO, USA, 2019; pp. 1–128. [Google Scholar]

- Chentian, Z. EMC in Power Electronics and PCB Design. Ph.D. Thesis, Clemson University, Clemson, SC, USA, 2014. [Google Scholar]

- Bondarenko, N. Electromagnetic Compatibility in Power Inverter Design. Ph.D. Thesis, Missouri University of Science and Technology, Rolla, MO, USA, 2015. [Google Scholar]

- Morales-Caporal, R.; Reyes-Galaviz, A.S.; Casco-Vásquez, J.F.; Martínez-Hernández, H.P. Development and implementation of a relay switch based on WiFi technology. In Proceedings of the International Conference on Electrical Engineering, Computing Science and Automatic Control (CCE), Mexico City, Mexico, 11–13 November 2020; pp. 1–6. [Google Scholar]

- STMicroelectronics. PWM Resolution Enhancement Through a Dithering Technique for STM32 Advanced-Configuration, General-Purpose and Lite Timers Application Note AN4507; STMicroelectronics: Geneva, Switzerland, 2017; pp. 1–22. [Google Scholar]

- IEEE Power and Energy Society. Recommended practice and requirements for harmonic control in Electric power systems. In Proceedings of the IEEE Std 519-2014 (Revision of IEEE Std 519-1992), Piscataway, NJ, USA, 11 June 2014; pp. 1–29. [Google Scholar]

- Mercorelli, P.; Kubasiak, N.; Liu, S. Multilevel bridge governor by using model predictive control in wavelet packets for tracking trajectories. In Proceedings of the IEEE International Conference on Robotics and Automation (ICRA), New Orleans, LA, USA, 26 April–1 May 2004; pp. 4079–4084. [Google Scholar]

- Chang, E.-C.; Cheng, C.-A.; Wu, R.-C. Robust optimal tracking control of a full-bridge DC-AC converter. Appl. Sci. 2021, 11, 1211. [Google Scholar]

| Name | Symbol | Value |

|---|---|---|

| Grid phase voltage (rms) | vs | 120 V ± 10% |

| DC-link voltage | Vdc | 50–180 V |

| Grid frequency | fs | 60 Hz |

| Inverter maximal output current | Io | 35 A |

| Maximum output power | Pm | 6 kW |

| Inverter output frequency | fo | 0–60 Hz |

| Inverter switching frequency | fSW | 10 kHz |

| Symbol | Datasheet Values | Calculated Values | Units |

|---|---|---|---|

| IGBT APT80GA60LD40 (Vce = 600 V, Ic = 75 A at TC = 100 °C) | |||

| , QG | 230, 78 | nC | |

| Cies = [CGE + CGC], Coes = [CGC + CCE], Cres = CGC | 6390, 580, 63 | pF | |

| td(on), td(off), trise, tfall | 23, 158, 31, 132 | ns | |

| RθJC (IGBT), RθJC (diode) | 0.2, 0.67 | °C/W | |

| PD | 625 (TC = 25 °C) | 259.740 (TC = 100 °C) | W |

| TJ, TSTG | −55 to 150 | °C | |

| Isolated Gate Driver si8285 | |||

| Common Mode Transient Immunity | 125 | 25MAX | kV/µs |

| VDDA, VDDB, −VSSB | 3.0–5.5, 10.0–30.0, 10.0–30.0 | V | |

| R0G,on, R0G,off, RDSAT | 2.48, 0.86, 100 | Ω | |

| RG,on, RG,off | 0–10, 0–10 (VDDB = 15 V) | 10, 8.2 | Ω |

| DDSAT D1 DBOOT D2 | ES1J for 600 V - - - | STTH112A for 1200 V MMSZ5242BS-7-F for 12 V, STTH2L06UFY for 600 V MM3Z16VT1G for 16 V | |

| CBL, CBOOT | 390, - | 0.22, 1 | µF |

| iG | iG,on 2.8, iG,off 3.4 (VDDB = 15 V) | A | |

| PD | 410 (when TJ − TA = 25 °C) | 245.9 (when TJ − TA = 15 °C) | mW |

| TJ, TA | 150MAX, −40 to 125 | 100, 25 | °C |

| Name | Symbol | Calculated Value | Selected Value by Tests |

|---|---|---|---|

| Total parasitic inductance of the circuit | Ls | - | 687.835 nH |

| Drain current at turn-off | Ioff_MAX | 40 A | - |

| Peak surge voltage | VPS | 250 V | - |

| Snubber capacitor (Film capacitor, 400 V) | CSNUB | 224.60 nF | 150 nF |

| Snubber resistance (MELF, 500 V) | RSNUB | 193.58 Ω | 150 Ω |

| Snubber Diode (Ultra-fast, 600 V) | DSNUB | - | MURS260T3G |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Morales-Caporal, R.; Pérez-Cuapio, J.F.; Martínez-Hernández, H.P.; Cortés-Maldonado, R. Design and Hardware Implementation of an IGBT-Based Half-Bridge Cell for Modular Voltage Source Inverters. Electronics 2021, 10, 2549. https://doi.org/10.3390/electronics10202549

Morales-Caporal R, Pérez-Cuapio JF, Martínez-Hernández HP, Cortés-Maldonado R. Design and Hardware Implementation of an IGBT-Based Half-Bridge Cell for Modular Voltage Source Inverters. Electronics. 2021; 10(20):2549. https://doi.org/10.3390/electronics10202549

Chicago/Turabian StyleMorales-Caporal, Roberto, José F. Pérez-Cuapio, Haydee P. Martínez-Hernández, and Raúl Cortés-Maldonado. 2021. "Design and Hardware Implementation of an IGBT-Based Half-Bridge Cell for Modular Voltage Source Inverters" Electronics 10, no. 20: 2549. https://doi.org/10.3390/electronics10202549

APA StyleMorales-Caporal, R., Pérez-Cuapio, J. F., Martínez-Hernández, H. P., & Cortés-Maldonado, R. (2021). Design and Hardware Implementation of an IGBT-Based Half-Bridge Cell for Modular Voltage Source Inverters. Electronics, 10(20), 2549. https://doi.org/10.3390/electronics10202549