A CMOS Active Rectifier with Time Domain Technique to Enhance PCE

Abstract

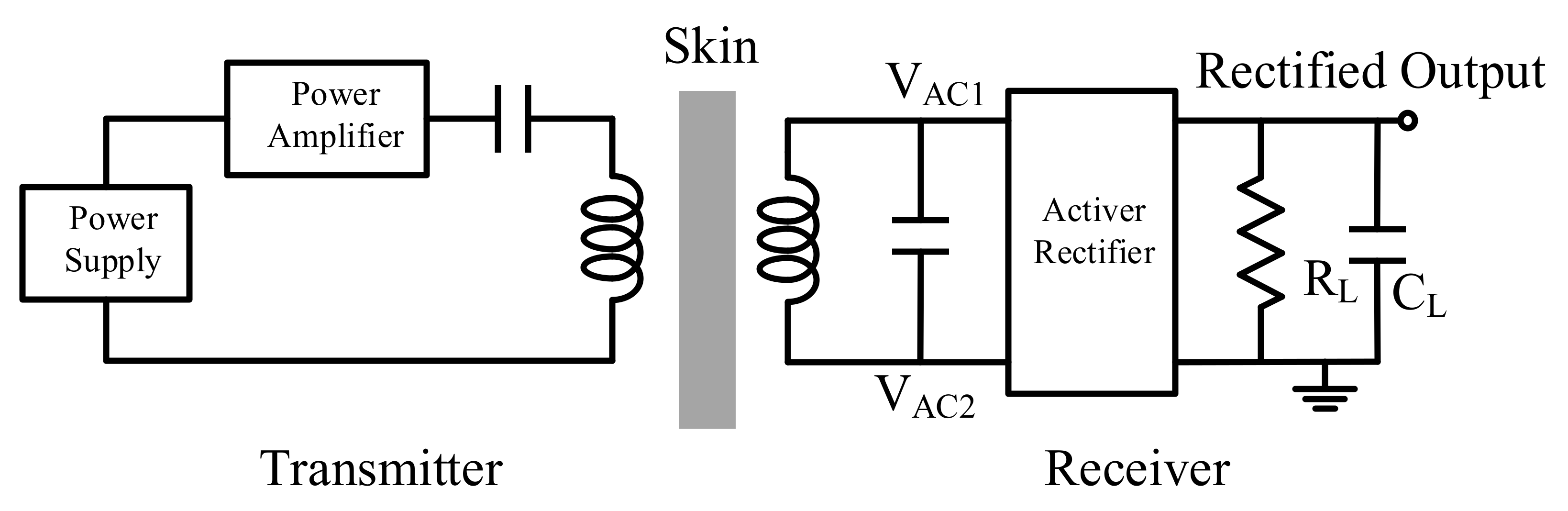

1. Introduction

- The proposed circuit is well-suited for a wide range of input voltage and loading resistors.

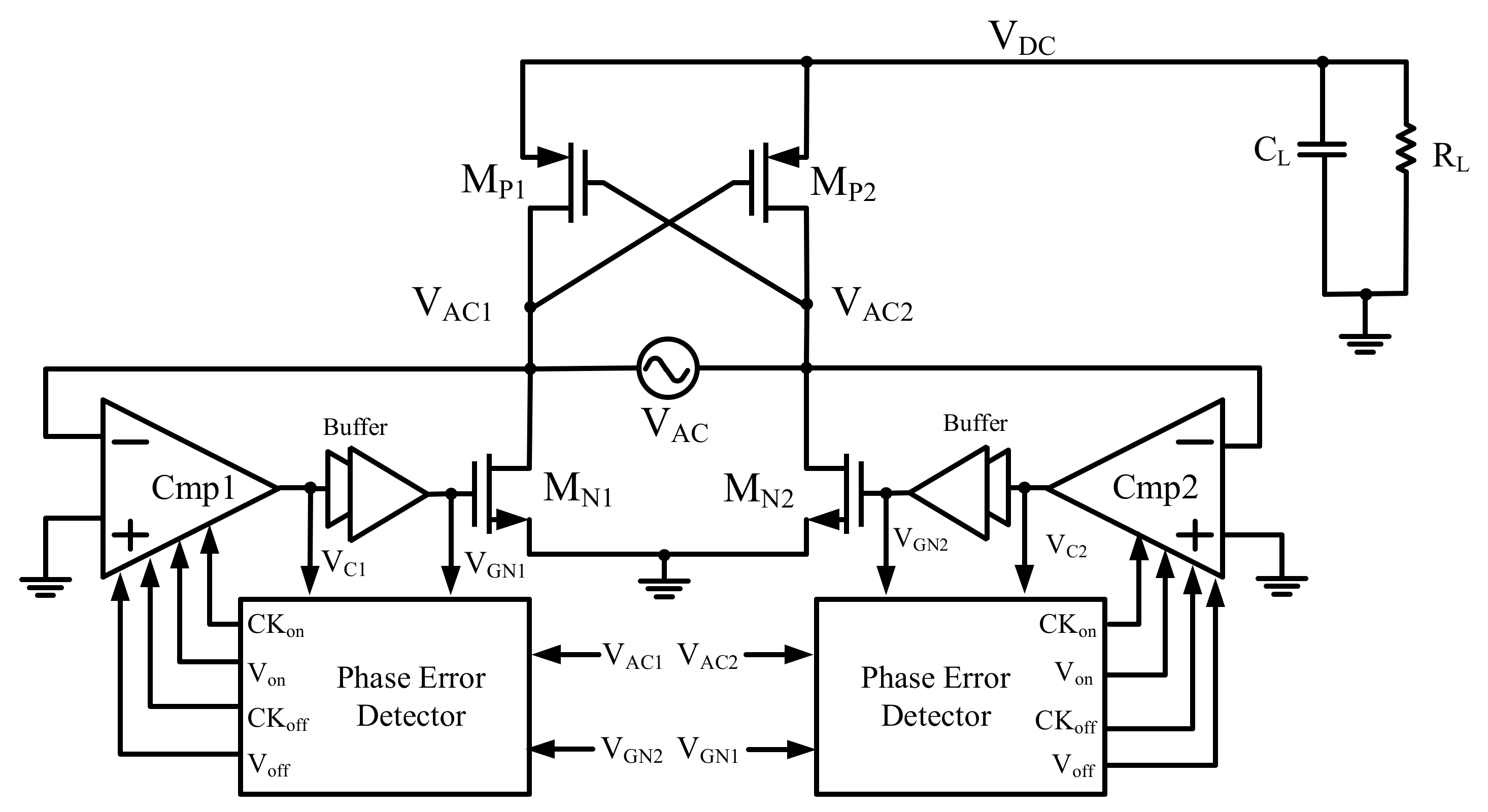

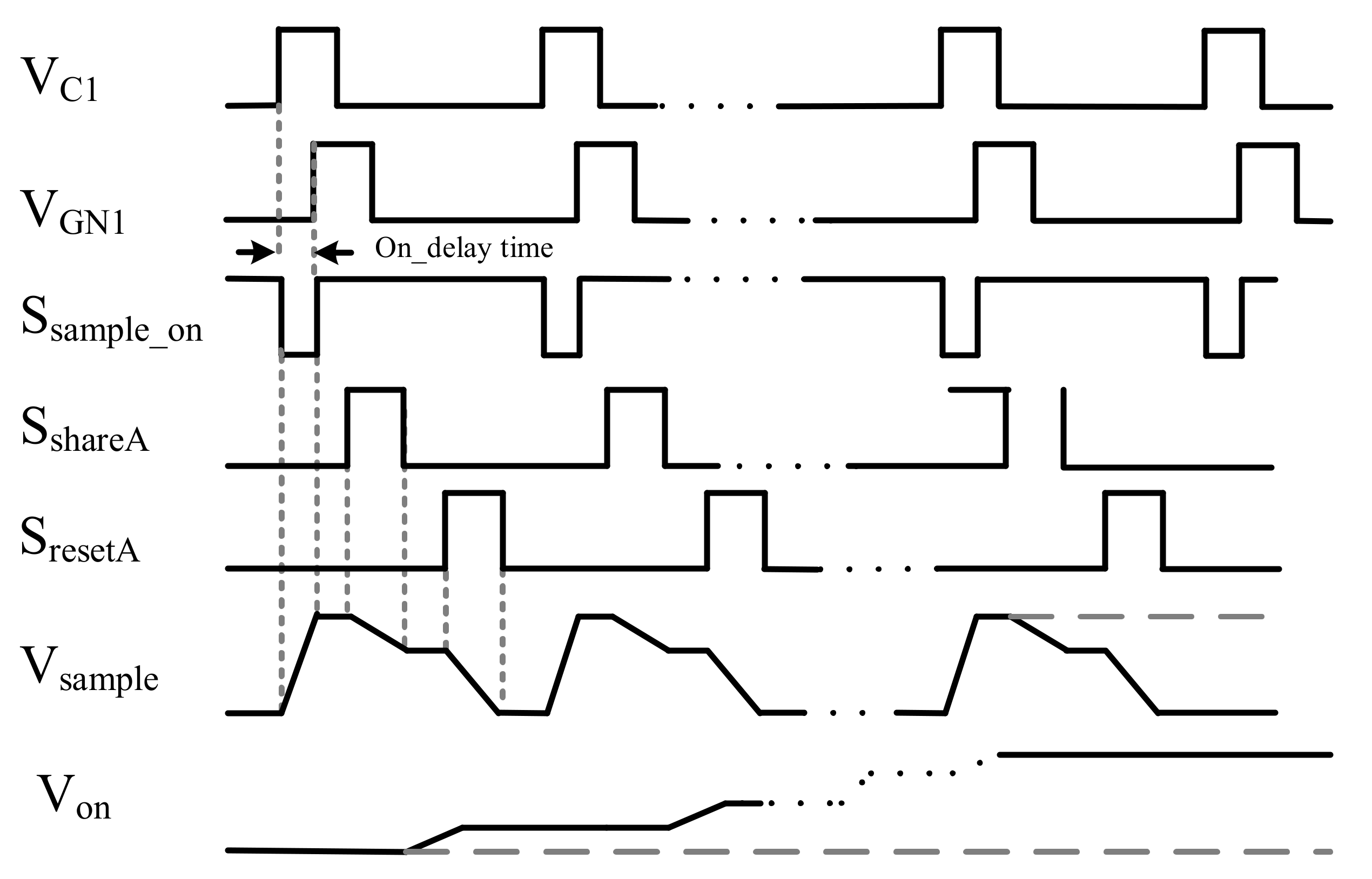

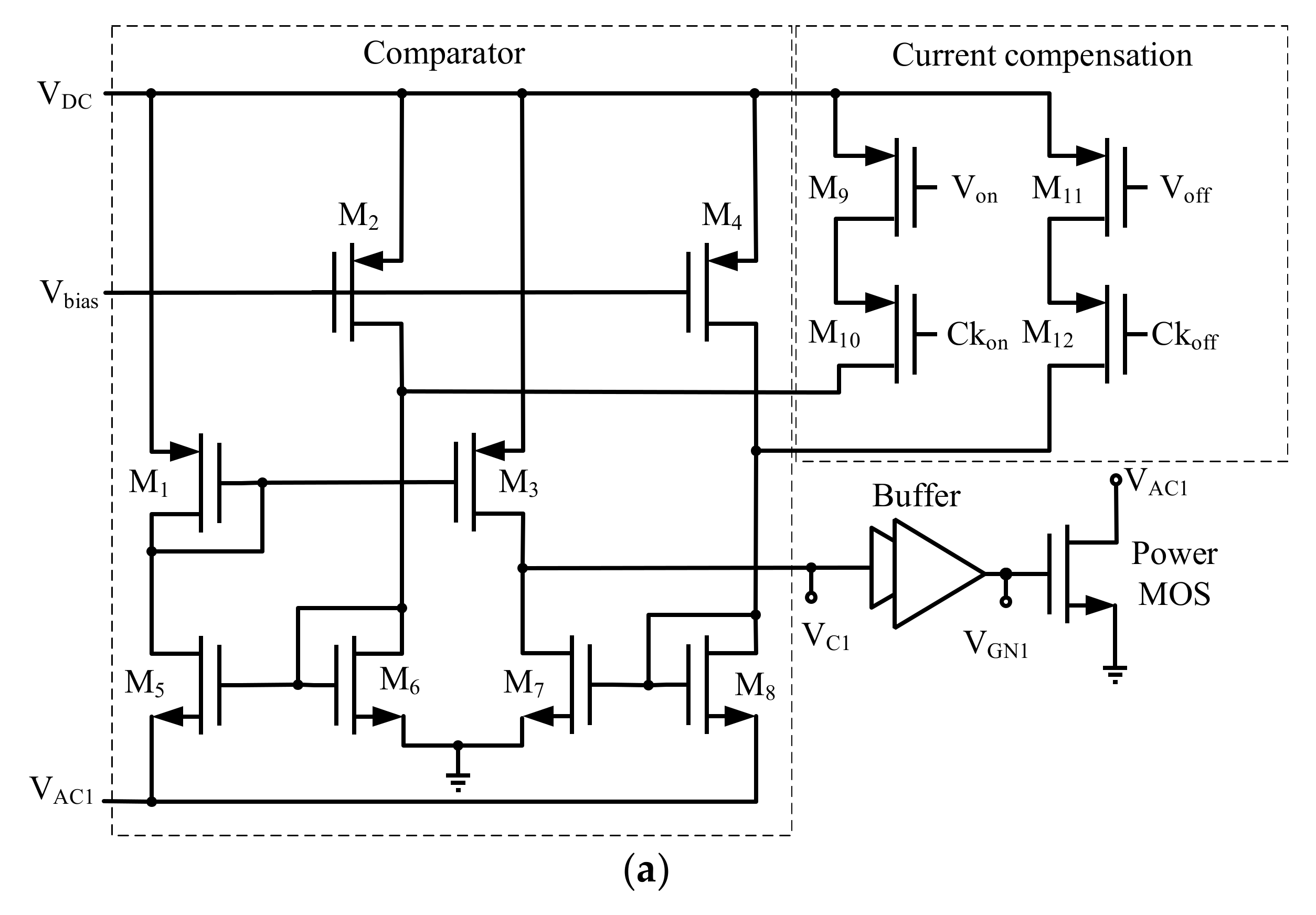

- A phase error detector is proposed to detect the phase difference induced by the buffers. The phase difference is converted to voltage and adaptively tracks the on/off delay time in the rectifier with variable input voltage.

- This technique can effectively overcome the problem of varied delay time by the buffer in different input voltages.

- The advantages of our circuits are with high resolution for accuracy-compensated phase difference between input and output buffer. It can generate the desired pulse to turn on/off the power MOS.

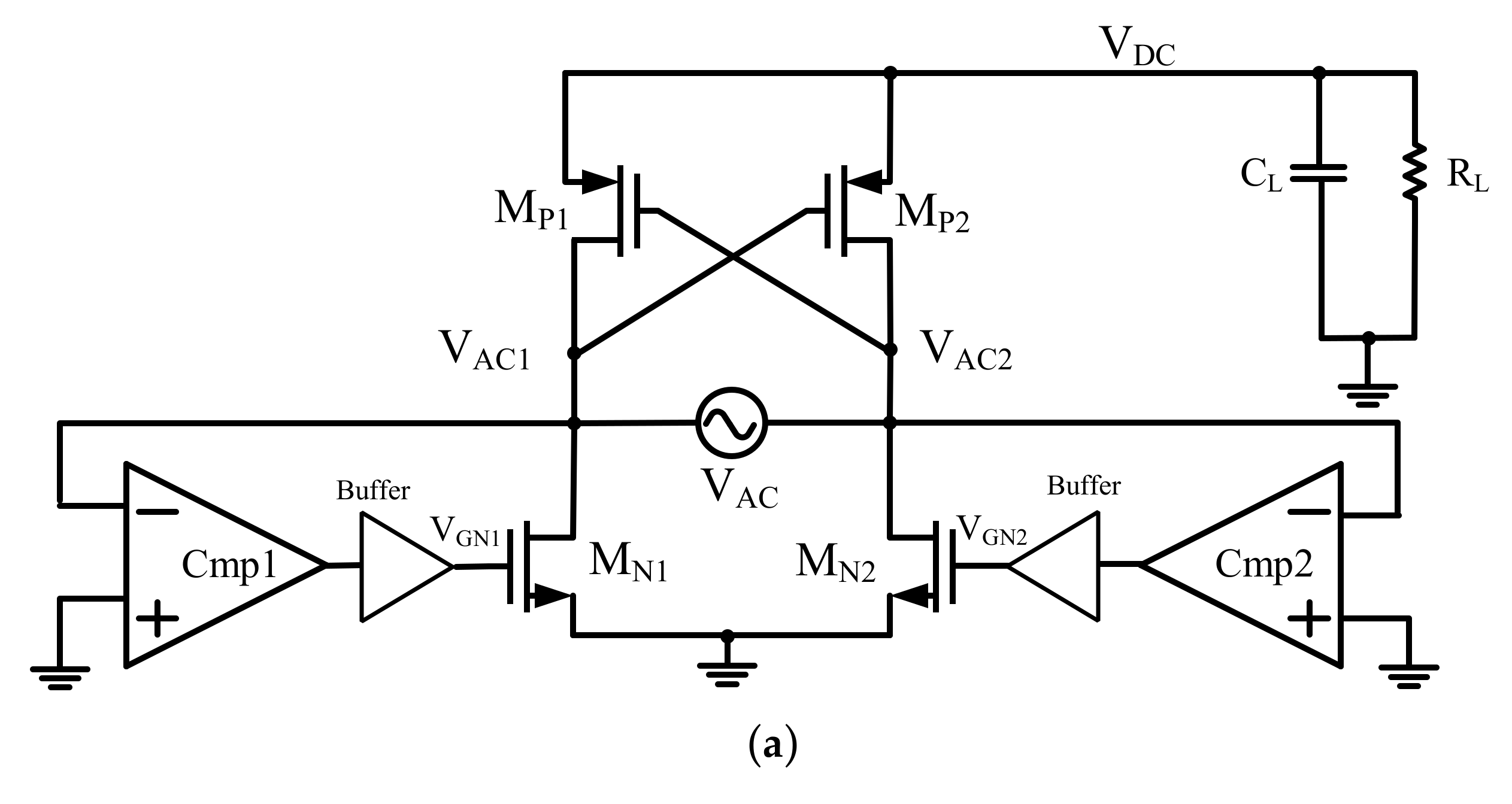

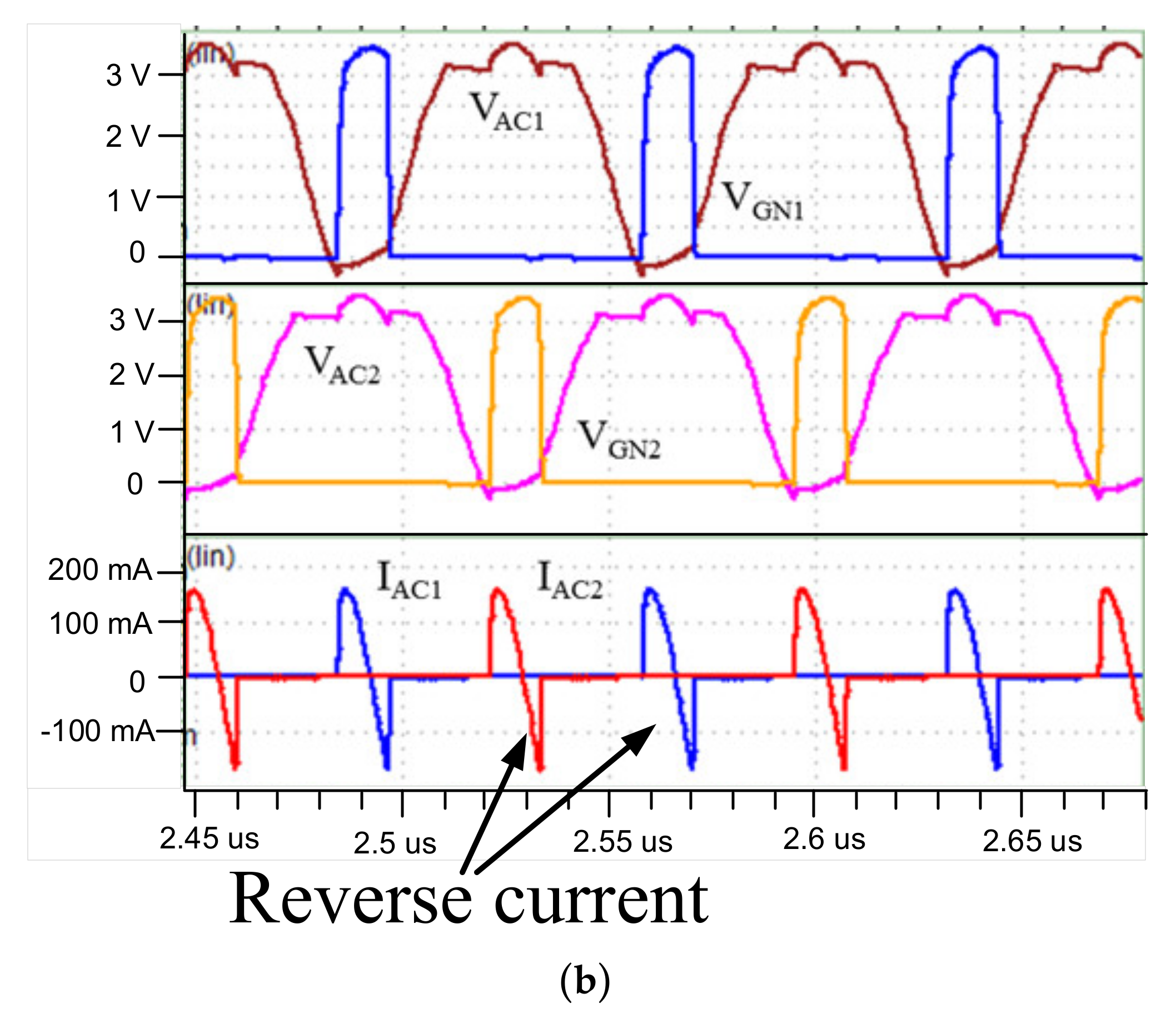

2. Proposed Circuit

2.1. Phase Error Detector

2.2. Comparator Circuit

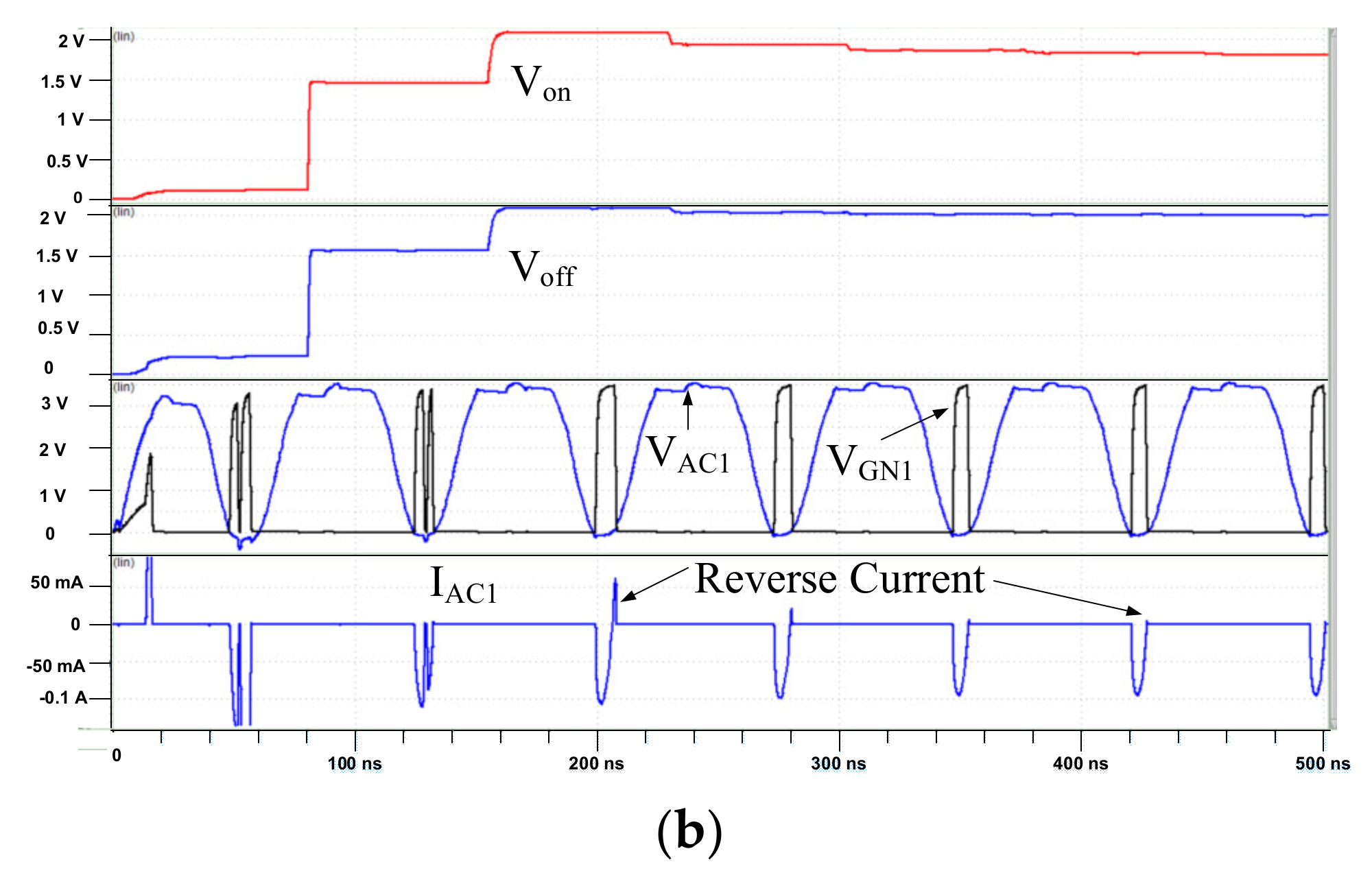

2.3. PCE Analysis and Considerations

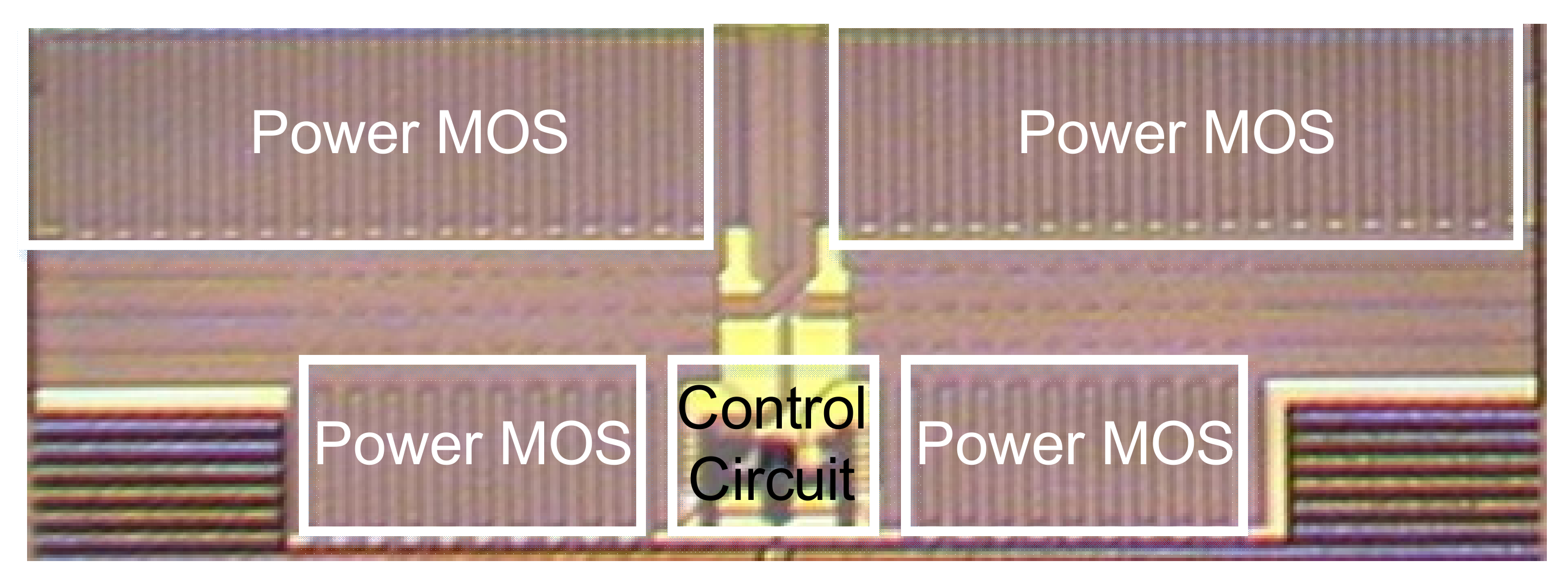

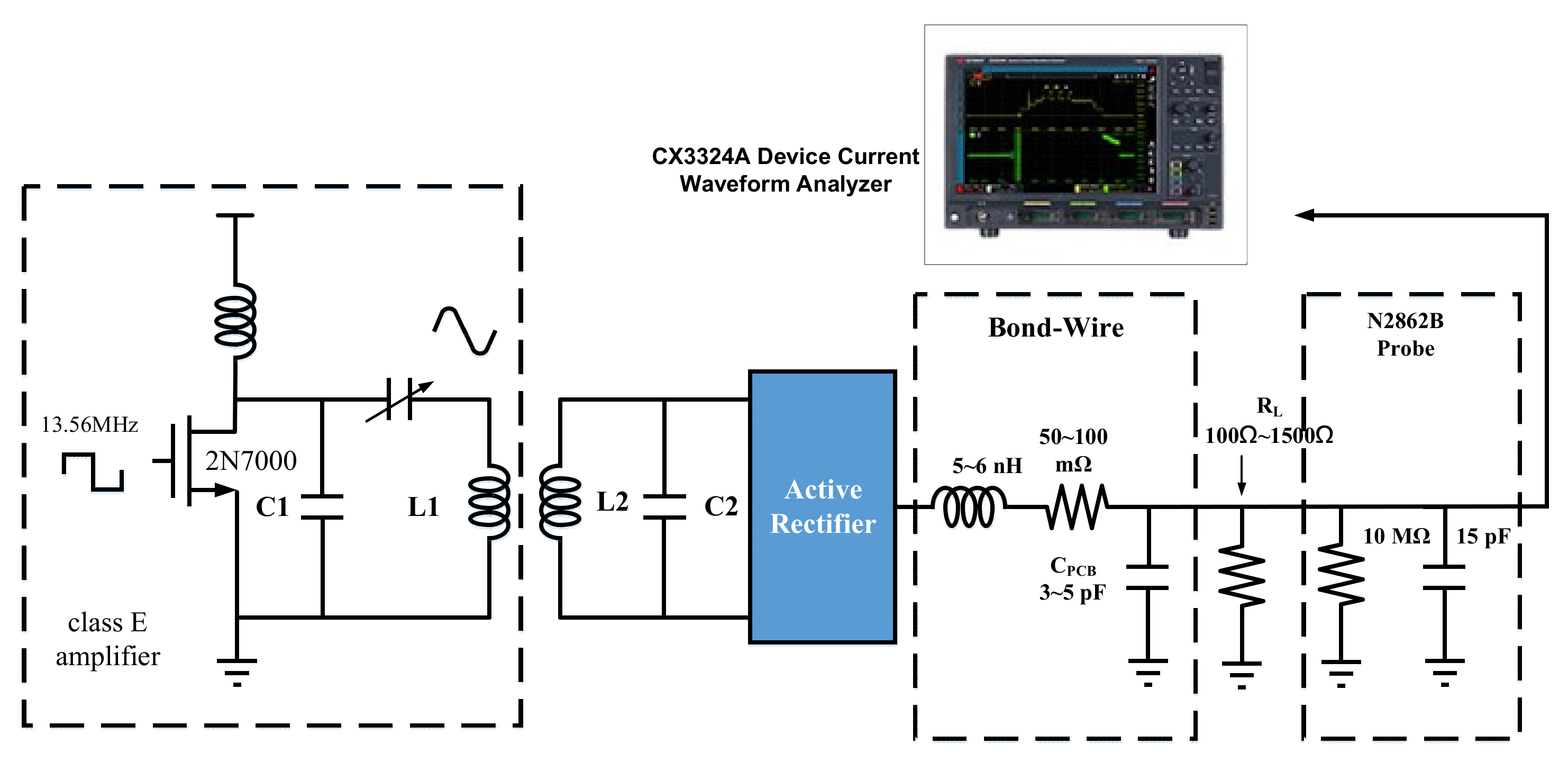

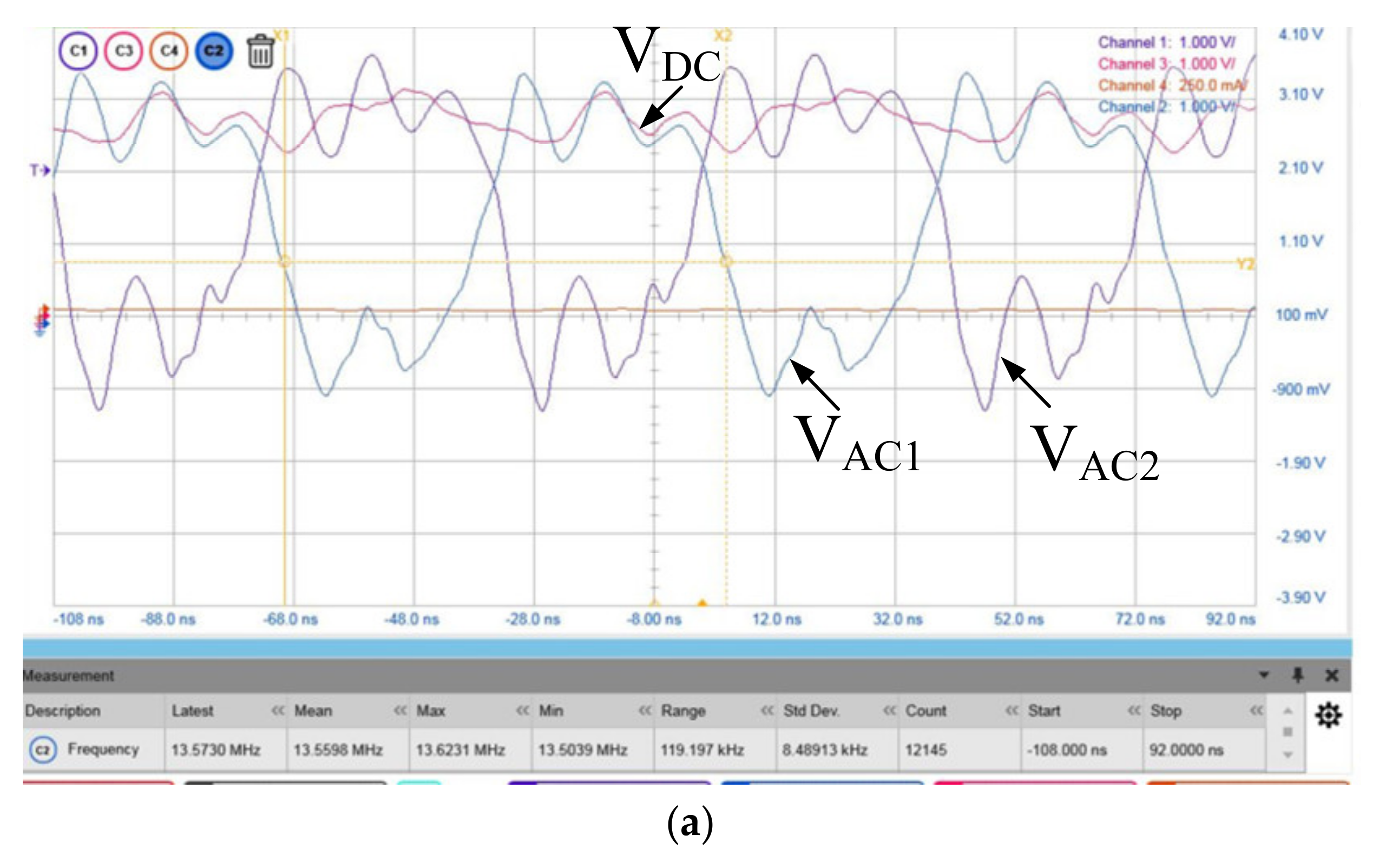

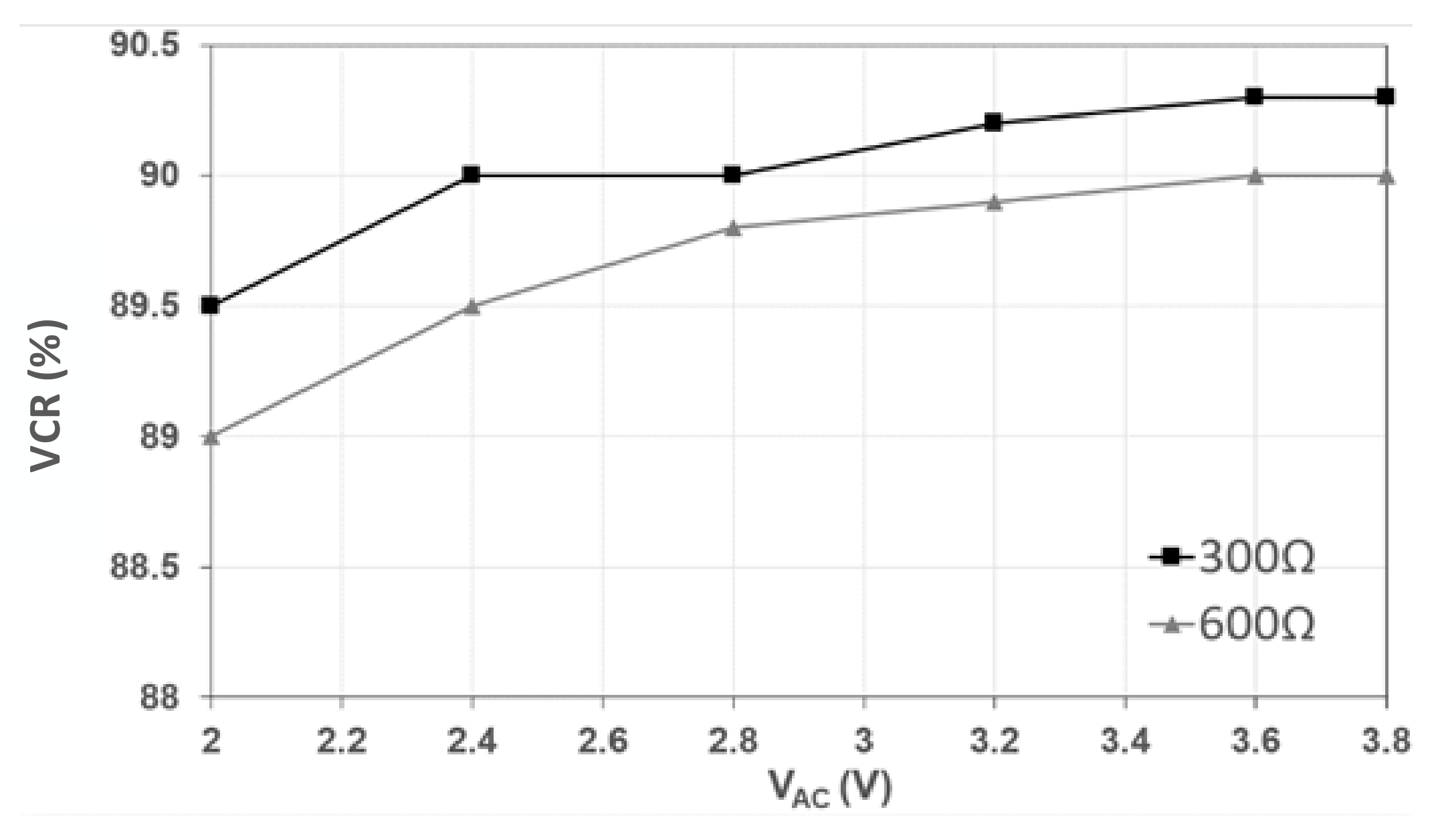

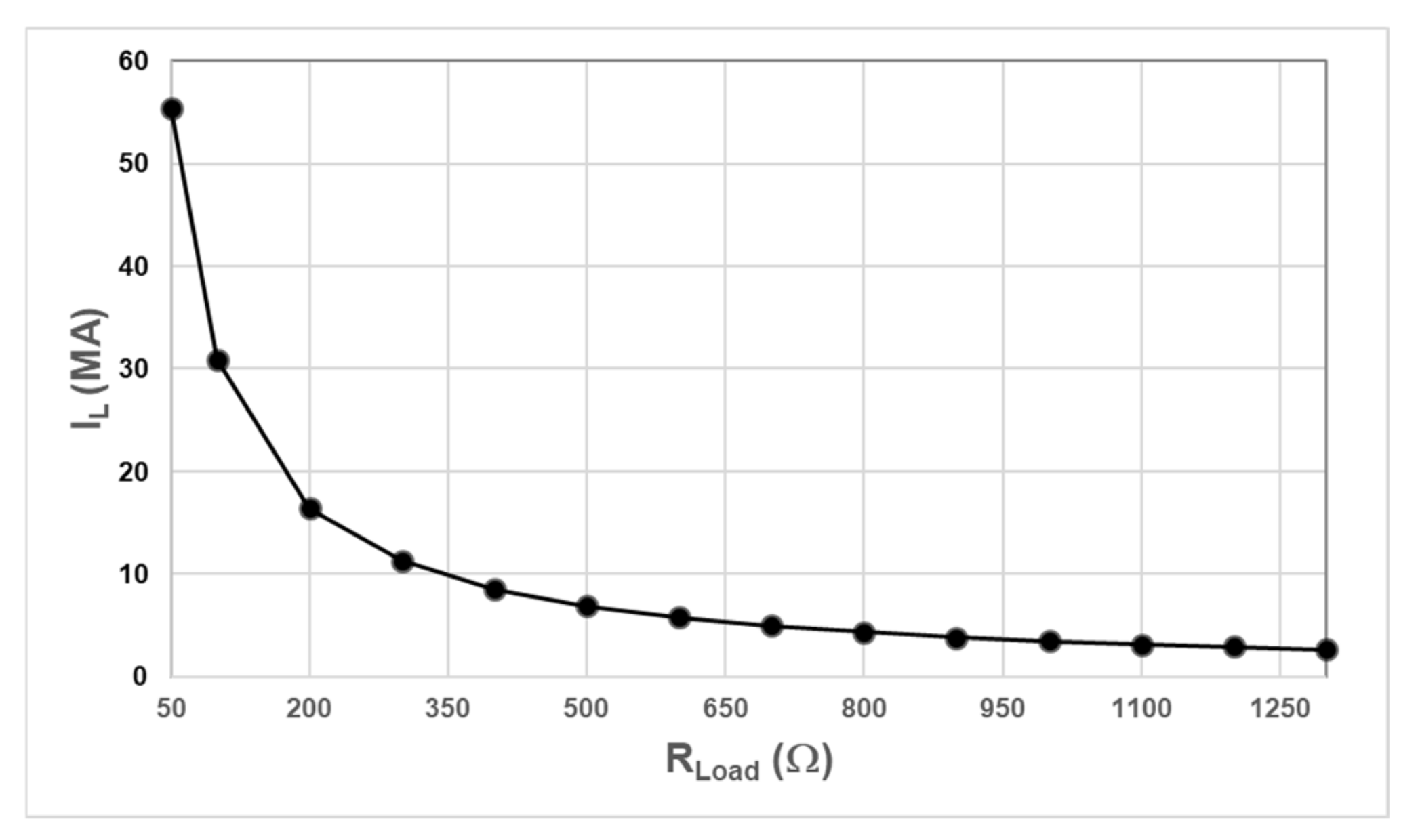

3. Measurement Results

4. Conclusions

Funding

Acknowledgments

Conflicts of Interest

References

- Campi, T.; Cruciani, S.; Palandrani, F.; De Santis, V.; Hirata, A.; Feliziani, M. Wireless Power Transfer Charging System for AIMDs and Pacemakers. IEEE Trans. Microw. Theory Tech. 2016, 64, 633–642. [Google Scholar] [CrossRef]

- Akin, T.; Najafi, K.; Bradley, R.M. A wireless implantable multichannel digital neural recording system for a microm-achined sieve electrode. IEEE J. Solid State Circuits 1998, 33, 109–118. [Google Scholar] [CrossRef]

- Bhatti, P.T.; Wise, K.D. A 32-Site 4-Channel High-Density Electrode Array for a Cochlear Prosthesis. IEEE J. Solid State Circuits 2006, 41, 2965–2973. [Google Scholar] [CrossRef]

- Rothermel, A.; Liu, L.; Pour Aryan, N.; Fischer, M.; Wuenschmann, J.; Kibbel, S.; Harscher, A. A CMOS Chip with Active Pixel Array and Specific Test Features for Subretinal Implantation. IEEE J. Solid State Circuits 2008, 44, 290–300. [Google Scholar] [CrossRef]

- Rana, M.M.; Xiang, W.; Wang, E.; Li, X.; Choi, B.J. Internet of Things Infrastructure for Wireless Power Transfer Systems. IEEE Access 2018, 6, 19295–19303. [Google Scholar] [CrossRef]

- Kao, S. An Active Rectifier with Time-Domain Delay Compensation to Enhance the Power Conversion Efficiency. World Academy of Science, Engineering and Technology. Int. J. Energy Power Eng. 2019, 13, 168–173. [Google Scholar]

- Lu, Y.; Ki, W. A 13.56 MHz CMOS Active Rectifier with Switched-Offset and Compensated Biasing for Biomedical Wireless Power Transfer Systems. IEEE Trans. Biomed. Circuits Syst. 2014, 8. [Google Scholar] [CrossRef] [PubMed]

- Li, X.; Tsui, C.-Y.; Ki, W.-H. A 13.56 MHz Wireless Power Transfer System with Reconfigurable Resonant Regulating Rectifier and Wireless Power Control for Implantable Medical Devices. IEEE J. Solid State Circuits 2015, 50, 978–989. [Google Scholar] [CrossRef]

- Huang, C.; Kawajiri, T.; Ishikuro, H. A Near-Optimum 13.56 MHz CMOS Active Rectifier with Circuit-Delay Real-Time Calibrations for High-Current Biomedical Implants. IEEE J. Solid State Circuits 2016, 51, 1797–1809. [Google Scholar] [CrossRef]

- Cheng, L.; Ki, W.; Lu, Y.; Yim, T. Adaptive On/Off Delay-Compensated Active Rectifiers for Wireless Power Transfer Systems. IEEE J. Solid State Circuits 2016, 51, 712–723. [Google Scholar]

- Xue, Z.; Fan, S.; Li, D.; Zhang, L.; Gou, W.; Geng, L. A 13.56 MHz, 94.1% Peak Efficiency CMOS Active Rectifier with Adaptive Delay Time Control for Wireless Power Transmission Systems. IEEE J. Solid State Circuits 2019, 54, 1744–1754. [Google Scholar] [CrossRef]

- Fuh, J.; Hsieh, S.-K.; Yang, F.-B.; Chen, P.-H. A 13.56MHz power-efficient active rectifier with digital offset compensation for implantable medical devices. In Proceedings of the 2016 IEEE Wireless Power Transfer Conference (WPTC); Institute of Electrical and Electronics Engineers (IEEE): New York, NY, USA, 2016; pp. 1–3. [Google Scholar]

- Cheng, L.; Ge, X.; Hu, L.; Yao, Y.; Ki, W.-H.; Tsui, C.-Y. A 40.68-MHz Active Rectifier with Hybrid Adaptive On/Off Delay-Compensation Scheme for Biomedical Implantable Devices. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 67, 516–525. [Google Scholar] [CrossRef]

- Li, C.-A.; Lee, W.-E.; Lu, C.-H.; Lin, S.-Y.; Lin, T.-H. A Single-Comparator Active Rectifier with Auto-Calibration in 0.18-μm CMOS. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS); Institute of Electrical and Electronics Engineers (IEEE): New York, NY, USA, 2020; pp. 1–4. [Google Scholar]

- Ma, Y.; Cui, K.; Ye, Z.; Sun, Y.; Fan, X. A 13.56-MHz Active Rectifier with SAR-Assisted Coarse-Fine Adaptive Digital Delay Compensation for Biomedical Implantable Devices. IEEE Solid State Circuits Lett. 2020, 3, 122–125. [Google Scholar] [CrossRef]

- Rashidi, A.; Laursen, K.; Hosseini, S.; Huynh, H.; Moradi, F. An Implantable Ultrasonically Powered System for Optoge-netic Stimulation with Power-Efficient Active Rectifier and Charge-Reuse Capability. IEEE Tran. Biomed. Circuits Syst. 2019, 13, 1362–1371. [Google Scholar] [CrossRef]

- Erfani, R.; Marefat, F.; Mohseni, P. A 1–10MHz Frequency-Aware CMOS Active Rectifier with Dual-Loop Adaptive Delay Compensation and >230 mW Output Power for Capacitively Powered Biomedical Implants. In Proceedings of the 2019 IEEE Custom Integrated Circuits Conference (CICC); Institute of Electrical and Electronics Engineers (IEEE): New York, NY, USA, 2019; pp. 1–4. [Google Scholar]

- Cha, H.-K.; Park, W.-T.; Je, M. A CMOS Rectifier with a Cross-Coupled Latched Comparator for Wireless Power Transfer in Biomedical Applications. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 409–413. [Google Scholar] [CrossRef]

| Simulation Result | |||

|---|---|---|---|

| Corner | Temperature (°C) | PCE (%) | VCR (%) |

| TT | 27 | 92.5% | 92.5% |

| SS | 100 | 88.7% | 90.6% |

| FF | 0 | 92.6% | 92.6% |

| Parameters | [18] TCASII’12 | [9] JSSC’16 | [11] JSSC’19 | This Work |

|---|---|---|---|---|

| Technology (μm) | 0.18 | 0.18 | 0.18 | 0.18 |

| Frequency (MHz) | 13.56 | 13.56 | 13.56 | 13.56 |

| Input Amp.(V) | 0.9–2 | 1.3–2.5 | 1.0–2.5 | 1.8–3.6 |

| Output Amp.(V) | 0.45–1.78 | 1.24–2.44 | 0.928–2.37 | 1.62–3.35 |

| Pout (Max. mW) | 3.2 | 248.1 | 34.1 | 109 |

| VCR (%) | 82–89 ) | 91.7–95.2 ) | 92.8–97.5 ) | 89–90.3 ) |

| PCE (%) | 60–81.9 ) | 91.3–94.6 ) | 82.6–94.1 ) | 83–90.3 ) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kao, S.-K. A CMOS Active Rectifier with Time Domain Technique to Enhance PCE. Electronics 2021, 10, 1450. https://doi.org/10.3390/electronics10121450

Kao S-K. A CMOS Active Rectifier with Time Domain Technique to Enhance PCE. Electronics. 2021; 10(12):1450. https://doi.org/10.3390/electronics10121450

Chicago/Turabian StyleKao, Shao-Ku. 2021. "A CMOS Active Rectifier with Time Domain Technique to Enhance PCE" Electronics 10, no. 12: 1450. https://doi.org/10.3390/electronics10121450

APA StyleKao, S.-K. (2021). A CMOS Active Rectifier with Time Domain Technique to Enhance PCE. Electronics, 10(12), 1450. https://doi.org/10.3390/electronics10121450