Abstract

Approximate computing can considerably improve energy efficiency by mitigating the accuracy requirements of calculations in error resilient application programming, such as machine learning, audio–video signal processing, data mining, and search engines. In this study, we propose an approximate divider for dynamic energy-quality scaling, which involves a trade-off between accuracy and latency. Previous approximate dividers for dynamic energy-quality scaling are well-configured, but lack energy-quality scalability. The key is to create a more accurate dynamic approximate divider while extending the limits of accuracy to maximize energy efficiency and meet various accuracy requirements. The proposed divider, called the accuracy scalable approximate divider based on restoring division (ASAD-RD), uses restoring division to significantly improve the error of the approximate divider and to use less latency. For the 8-bit division, SAADI, the previous design, has an average accuracy of 90.78% to 98.77%; however, ASAD-RD can improve the accuracy between 95.2% and 99.23% and hardly requires additional power consumption. Furthermore, for the same target accuracy, ASAD-RD requires fewer cycle iterations than SAADI. Thus, ASAD-RD requires lower energy than SAADI and can operate as an energy-efficient approximate divider.

1. Introduction

Energy efficiency is a key component of a computer system. Approximate computing is a type of design that can improve the energy efficiency of a system [1]. Traditionally, arithmetic operations were considered to always produce accurate results and were designed to pursue accurate computational results in computer design. However, accuracy may not always be a priority when considering energy efficiency in arithmetic operations [2]. Some applications pursue perfectly accurate computations, while others may require only adequate accuracy and seek more computational speed or power consumption [3]. Applications such as machine learning, video signal processing, searching, and data mining do not require complete accuracy [4]. In such cases, pursuing perfectly accurate computation can waste energy. Approximate computing is a new approach to improve the energy efficiency of these applications [5]. Approximate computing using an adder [6], multiplier [7], or divider [8] can improve energy efficiency by saving power or latency while meeting the results of appropriate accuracy.

So far, many approximate computing designs have been presented, and these designs have been proven to benefit from performance improvement and power savings by causing minor errors. Furthermore, many approximate divider designs have been proposed [9,10,11,12]. However, previously proposed approximation dividers do not meet the applications’ various accuracy requirements and are limited in that they provide only a single level of accuracy. In addition, the accuracy requirement for arithmetic operations is not constant because the impact of approximation to the final quality at the application level is highly input-dependent [13], and the application-level quality requirements may also change over time. Therefore, in order to meet the quality requirements of the application, an approximate divider is required that enables dynamic quality scaling. SAADI has the advantage of being able to dynamically control the accuracy and latency, which helps to overcome the shortcomings of the previous approximate dividers [14].

Herein, we propose an approximate divider design that enhances the dynamic energy quality scalability with fewer errors. The accuracy scalable approximate divider based on restoring division (ASAD-RD) is based on the previous approximate divider, SAADI [14], which performs division by multiplying the dividend and the approximate reciprocal of the divisor and then repeats the process of the approximation of the reciprocal of the divisor. According to the iteration process, accuracy gradually increases, which enables SAADI to obtain a trade-off between latency and accuracy. Applications can use SAADI to perform high-accuracy division by increasing the time and power consumption or improving energy efficiency while reducing accuracy. Energy-efficient arithmetic operations have long been a challenge for researchers to derive better performance from limited resources in computer systems. Compared with SAADI [14], ASAD-RD is based on a novel idea. It is a hybrid method of SAADI and other division algorithms for improving the accuracy and reducing the repetition process of the approximate division. In the process of approximate division, a restoring division is performed at the beginning of SAADI to reduce the occurrence of truncation errors in the multiplicative division. As a result, the proposed design can meet more stringent accuracy requirements that cannot be reached by SAADI and can benefit from power or performance.

The remainder of the paper is organized as follows: Section 2 presents related works and explains the motivations of our study. The proposed approximate divider is introduced in Section 3. It elaborates on the algorithm and architecture with error compensation. Section 4 presents a complete analysis of accuracy and latency and a comparison with a conventional scalable accuracy approximate divider (e.g., SAADI), followed by conclusions in Section 5.

2. Related Works

Researchers have developed and proposed various approximate arithmetic units to improve the energy efficiency of arithmetic operations. Among them, approximate dividers have been studied relatively more recently than other arithmetic units, such as the adder [6] and multiplier [7]. An approximate divider called AAXD [9] normalizes the operands to remove leading zeros and uses only a few numbers of the most relevant bits. The truncated dividend is then divided by the truncated divisor using a narrow width divider. The dividend and divisor are then compared to prevent overflow. Accuracy is predetermined by the partition width of AAXD, which cannot be adjusted dynamically. An approximate divider design presented in [15] reduces power consumption and circuit complexity. It is designed with a simple structure consisting of three approximate subtractor cells that leads to performance improvement and power reduction. However, the accuracy is also determined at the design level. Therefore, the requirements of the application cannot be met dynamically. PLApp [10], TruncApp [11], and SEERAD [12] are examples of multiplicative dividers, where the reciprocal of the divisor is obtained first and then subsequently multiplied by the dividend. In PLApp, the reciprocal is approximated using a fragmented linear function and rounding. In TruncApp, the reciprocal is obtained by simple bit manipulations such as inversion, truncation, and concatenation. In SEERAD, the reciprocal is approximated using a table indexed by the upper bits of the divisor. For all three designs, the accuracy is determined at design time and cannot be configured at runtime. SAADI [14] is an example of an approximation divider, which can dynamically scale accuracy at runtime. It is also a multiplicative divider, but in the approximation process of the reciprocal of the divisor, repeated operations are performed using the Taylor series. Here, the accuracy is determined by the number of iterations, and the truncation errors are accumulated during the iteration process. As a result, there is a limitation of accuracy that cannot be solved no matter how many times a repeated operation is performed. For error compensation of SAADI, Reference [16] reference could not be subject. proposed the idea that the approximate quotient is multiplied by a constant in a Look-up Table indexed by the number of iterations. However, the error compensation after approximation may not be achieved properly due to the truncation caused by the limit of divider width. Therefore, we propose the idea of changing the input, not the error compensation of the output.

3. Proposed Approximate Divider

In this section, we introduce our divider design, ASAD-RD, and the algorithm of the divider and hardware implementation. We analyze the error compensation and improvement in accuracy.

3.1. Proposed Approximate Division

The proposed design, ASAD-RD, is a combination of a multiplicative division algorithm that obtains the reciprocal of the divisor first and then multiplies the dividend and uses the restoring division algorithm that provides accurate computational results. We explain the basics of the restoring division algorithm [17,18] and the multiplicative division algorithm [19].

First, we describe the basics of restoring division. In restoring division, register R contains the remainder and register Q the quotient. An n bit dividend is loaded in Q, and the divisor is loaded in register M. The value of the register is initially maintained at zero; this is register R whose value is restored during the iteration. For example, the dividend is 190, the divisor 11, and the bits 8. Subsequently, R is 0, M 11, and Q 190.

Subsequently, the content of the registers R and Q is shifted to the left as if they are a single unit, such as .

Subsequently, , if , , and the value of R is restored. Else .

The process of the first step is over. Once this process is iterated n times, where n is the width of the divider, the restoring division is finished, and the register Q contains the quotient 17, while R contains the remainder of three. The remainder R and divisor M are the new inputs of multiplicative division as a dividend A and divisor B.

Next, we describe the basics of the multiplicative division. A and B can be represented in a normalized form as:

where and . During normalization, a and b are truncated to n bits. Subsequently, the quotient Q of division is:

where is the reciprocal of b, i.e., . Instead of computing directly, it can be expressed as a multiplication of a and . For energy-efficient division, the exact reciprocal is not required. Therefore, an approximation reciprocal with acceptable accuracy is required. We address this by the approximation of the reciprocal based on the Taylor series expansion. More specifically, the Taylor series expansion of is:

where . It always converges because for normalized b such that . The approximate reciprocal can be obtained by adding up the first few low-order terms. If higher accuracy is required, more order terms can be added to gradually improve accuracy. However, this also improves latency. This trade-off can be used for applications depending on the required accuracy and latency restriction [14]. Let denote the t-th order approximation of , such that:

Finally, the t-th order approximate quotient is then obtained as:

Subsequently, we get two quotients, Q and . The sum of Q and is the final quotient of the proposed approximate divider.

Table 1 shows the result of and the error of SAADI and ASAD-RD. In the multiplicative division of each divider, the divisor B is 11, and b is . Therefore, the initial normalization and two’s complement conversion produce . Since the first iteration, the approximate reciprocal is . In the case of SAADI, the dividend A is 190, and the quotient is 15.5000, which is the approximate quotient of SAADI. By contrast, in the case of ASAD-RD, because restoring division was executed first, dividend A becomes three. Therefore, the quotient of ASAD-RD is 0.1250.

Table 1.

Comparison of the 190/11 division for each divider for 8 bits. ASAD-RD, accuracy scalable approximate divider based on restoring division.

After multiplicative division, adding the restoring division quotient Q to the output of the multiplicative division quotient provides the result of 190/11 by ASAD-RD. Therefore, the final quotient of ASAD-RD is 17 + 0.1250 = 17.1250. The exact quotient is 17.2727; thus, the error rate of ASAD-RD is 0.86%. By contrast, the error rate of SAADI is 10.26%. In the second iteration, and the final quotient of each divider are increased, thus reducing the error rate of SAADI from 10.26% to 3.75% and the error rate of ASAD-RD from 0.86% to 0.13%. However, in more than three iterations, there is no change in the error rate of ASAD-RD because has already converged. As t increases, decreases. If is zero after being truncated from 2n to n bits, will have no effect on the value of . Then, is converged. Thus, the maximum approximate quotient of 190/11 achieved by ASAD-RD is 17.25000 with an error rate of 0.13%. In SAADI, the quotient is converged to 17.1250 with an error rate of 0.86% in four iterations.

Comparing the final quotient of SAADI and ASAD-RD shows that there are differences in the 190/11 division operation. Because restoring division is performed before multiplicative division, the quotient gets a compensated initial value. Thus, the quotient of ASAD-RD has a lower error rate than SAADI for each cycle iteration. Restoring division before the multiplicative division increases the maximum accuracy and reduces the number of cycle iterations for maximum accuracy. More analysis regarding this is provided in Section 4.

3.2. Hardware Architecture

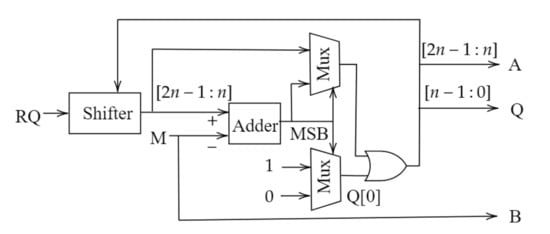

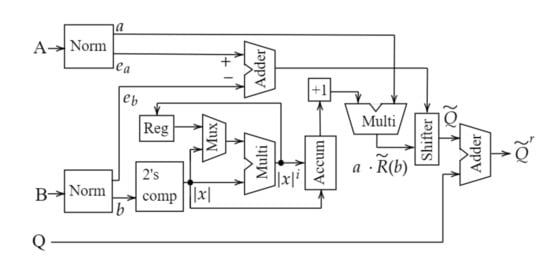

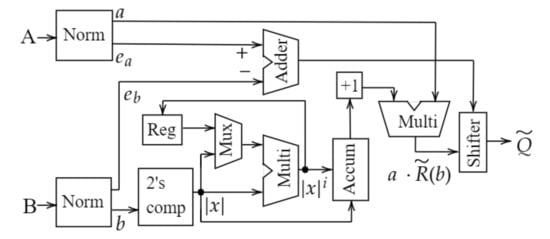

Figure 1 shows the hardware architecture for the restoring division of ASAD-RD, and Figure 2 shows the hardware architecture for the multiplicative division of ASAD-RD. Figure 3 shows the hardware architecture of SAADI. Except for Q and one adder, whose output is the final quotient in the multiplicative division part of ASAD-RD, the hardware architectures of ASAD-RD and SAADI are similar. The proposed design consists of a restoring division part and a multiplicative part. In the restoring division part, if the remainder R, whose initial value is zero, divisor M, and dividend Q are the inputs of ASAD-RD, R and Q are combined as and are shifted one bit left. Subsequently, most n bits of become R. The most significant bit (MSB) of the operation result is the selector of the two multiplexers. If the selector is one, the output of the multiplexers is , and if the selector is zero, and one are the outputs. The architecture consists of a recursive structure in which the output of each multiplexer is returned to its input. This process is repeated for the number of bits of the input. When the restoring division is performed through this process, R, Q, and B are obtained as outputs, and the remainder R and quotient Q have different values from the initial values. However, B receives the value of M, and it remains the initial value. After the restoring division, R and B become the inputs of multiplicative division as a dividend A and divisor B, respectively; in this process, the dividend A gets the value of R. Furthermore, Q is stored and then combined with the results of the multiplicative division to provide the final quotient . This multiplicative division process is the same as the previous design of SAADI. However, for the same operation, the input and output of the multiplicative division are different. Consequently, the existence of the restoring division provides different outputs from the previous design for the same division. Major hardware components for ASAD-RD include one 2n-bit barrel shifter, two n-bit adders, and two 2n bit two to one multiplexers more than those of SAADI. Therefore, ASAD-RD needs as much area as for these components as SAADI, and it is expected that ASAD-RD will consume more power and energy for the same division. The analysis of the power consumption and energy is provided in Section 4.3.

Figure 1.

Hardware architecture of the restoring division of the proposed ASAD-RD.

Figure 2.

Hardware architecture of the multiplicative division of the proposed ASAD-RD.

Figure 3.

Hardware architecture of SAADI [14].

3.3. Error Compensation

In this section, we analyze the errors of SAADI and how the errors can be compensated for in our divider design. The loss of accuracy in SAADI is caused by the following factors:

- : The input operands A and B are truncated to n bits during normalization

- : The approximate reciprocal is the sum of a limited number of terms

- : Each term is computed using an approximate multiplier that truncates 2n bits to n bits

- : The approximate reciprocal is truncated from bits to n bits before being multiplied by a, and the result is truncated to n bits.

The sign of is input-dependent. Truncating A contributes to negative factors of because the truncation results in a smaller dividend, while truncating B has the reverse effect because a smaller divisor produces a larger quotient. The error due to a finite-order approximation () is the runtime-adjustable error factor that we exploit for the trade-off of accuracy and latency such that:

Note that is always negative, and the magnitude decreases as t increases. Because of the accuracy loss in the multiplier (), eventually becomes zero within n cycles. Therefore, the effective range of t for the accuracy-latency trade-off is , considering one additional cycle at the end for . The error induced by the truncation in the multiplier and the accumulator ( and ) is always negative because it results in an under-approximated reciprocal and thus an under-approximated quotient [14].

We attempted to compensate SAADI for its approximate error by adding restoring division to the front of SAADI. This approach can reduce the size of the input of SAADI. A smaller input reduces the truncation error that occurs during normalization, which improves the accuracy by reducing the effect of on the approximate division results. Because restoring division is performed before the multiplicative division, the initial errors of division improve. Thus, the iterations of the approximation process for target accuracy will be reduced. This reduces the number of terms. Subsequently, reduces. In the maximum iteration of the approximation process for the maximum accuracy, as the effect of error factors decreases, a more accurate division is possible beyond the accuracy limit of SAADI. The next section is followed by a performance comparison analysis of the approximate divider with the addition of the restoring division.

4. Comparison and Analysis

We used Intel Quartus Prime Lite tool ver. 18.1 [20] to implement SAADI and ASAD-RD with Verilog hardware description language (HDL) and to evaluate the dividers from the perspective of the trade-off of accuracy, latency, and power consumption. A comparison of our design with that of SAADI is as follows:

- Average cycle iteration counts for maximum accuracy.

- Mean absolute error (MAE) of SAADI and ASAD-RD.

- Power consumption and energy efficiency.

- Required cycle iteration counts for target accuracy.

4.1. Previous Approximate Dividers

Table 2 shows the MAE and power consumption of the previous single cycle designs. AAXD has an MAE of 0.18% at a maximum accuracy level of 16. PLApp also has an MAE of 0.18% at the maximum accuracy level (8,8). On the other hand, TruncApp and SEERAD provide accuracies of 4.3% and 2.42%, respectively, when the accuracy level is four. Compared to TruncApp and SEERAD, AAXD and PLApp appear to have higher accuracy limits. TruncApp and AAXD result in higher accuracy scalability than the others. However, the energy consumption of AAXD at maximum accuracy is significantly higher than that of other dividers. These dividers can provide dynamic accuracy scalability by parameter changes. However, they do not have dynamic accuracy scalability at runtime because the accuracy is determined at design-time. Therefore, the following sections mainly deal with comparisons with SAADI, which has dynamic quality scalability at runtime.

Table 2.

Comparison of previously proposed approximate dividers.

4.2. Accuracy and Latency

In this section, we analyze the errors of the previous design and detail how the errors can be compensated to use the proposed design. Within the range, we first evaluate both dividers for varying runtime parameters with 500,000 random combinations of dividends and divisors. For a fair comparison, the same combinations are supplied to both dividers. As described in Section 3.1, the design parameters of the dividers are n i.e., the number of bits of operands, and t i.e., the cycle iteration count for reciprocal approximation.

Figure 4 shows the average iteration counts of SAADI and ASAD-RD required to reach the maximum accuracy for n = [4, 8, 12, 16]. In both dividers, the maximum number of the effective iteration counts for improved accuracy is . The average number of iteration counts to reach the maximum accuracy is less than for SAADI. For ASAD-RD, it is approximately 0.5 lower than the value for SAADI. In other words, ASAD-RD has the benefit of reducing the iteration count in the same n. Therefore, ASAD-RD can offset the additional latency for maximum accuracy due to the extended hardware for restoring division.

Figure 4.

Average iteration count for maximum accuracy for a varying number of bits.

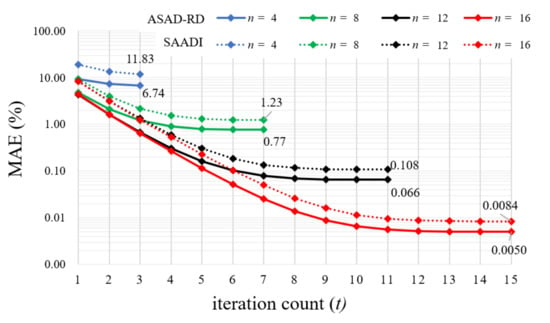

Figure 5 shows the variation of MAE of both dividers after varying n and the iteration count using the log scale. As n is increased, not only the maximum accuracy, but also the speed of improvement increases. For all terms with the same parameter, the proposed design obtains a lower MAE than the previous design. Therefore, ASAD-RD can obtain more accurate results for the same operation. The relation between reduced MAE and energy efficiency is discussed in the following section.

Figure 5.

MAE for varying numbers of bits and iteration counts in SAADI and ASAD-RD.

4.3. Power Consumption

Using the Quartus power analyzer tool [20], we measured the power consumption of the designed models. We adopted the power consumption per cycle as the basic unit for comparison with the previous design.

Table 3 shows the minimum and maximum MAE and power consumption of the first cycle of each divider using n = [4, 8, 12, 16]. For every n, ASAD-RD exhibits an approximately 40% to 50% lower MAE than SAADI. Although ASAD-RD consumes 4.3% to 4.9% more power than SAADI under the same conditions, the additional power consumption is due to the added division process compared with the previous design, in which division occurs only once. Thus, the more the total power consumption due to the increase of cycle iterations, the lower the percentage of additional power consumption in the total. As an example, for the 8 bit division, when only one iteration cycle is performed, the additional power consumption from the added process accounts for 4% of the total power consumption. However, for four iteration cycles, the rate is only 1%.

Table 3.

Comparison of MAE and power consumption for a varying number of bits.

According to Section 4.2, the average number of iterations for maximum accuracy is less than . Then, the average number of iterations of ASAD-RD is approximately 0.5 lower than the previous design. As a result, with the same parameters, the maximum accuracy of ASAD-RD is not only higher than that of the previous design, but also the number of iterations for maximum accuracy is lower. Lower iterations save power, and the amount saved is greater than the additional power consumption due to additional hardware. Therefore, ASAD-RD has advantages over SAADI in power or performance.

Table 4 shows how many iteration counts are required for each divider to reach the target accuracy in n = [4, 8, 12, 16] and the required energy. To compare ASAD-RD with the previous design from the viewpoint of energy, we expressed energy as the number of cycles to reach the target accuracy and the power consumption per cycle. Target accuracy that cannot be achieved due to the divider design limitation is left blank. For the same target accuracy, ASAD-RD, in most cases, performs one to two fewer iterations than SAADI. The proposed design and the previous design have the same cycle structure, and the proposed design has fewer iteration counts. Consequently, ASAD-RD consumes less energy than SAADI for the same target accuracy.

Table 4.

Comparison of required cycles and energy for target accuracy in SAADI and ASAD-RD for a varying number of bits.

Compared to the previous designs in Table 2, dynamically scalable dividers are multi-cycle, which consume relatively more power and energy than the single-cycle designs. However, the previous designs have low accuracy limits and a short range of accuracy scalability. This may result in a lack of performance if the accuracy requirements become strict at runtime. In this case, a multi-cycle divider, as proposed in this study, with large accuracy scalability and a high accuracy limit, which can be expanded at run-time, can be useful.

SAADI has a larger range of dynamic scalable accuracy because of the higher gap between the maximum MAE and minimum MAE. By contrast, ASAD-RD has a smaller range of dynamic scalable accuracy, but can reach a higher target accuracy at the same divider width. For instance, for the 8 bit divider, SAADI cannot reach a target accuracy of 99%, but ASAD-RD can. Thus, the proposed design uses less energy at the same divider width for target accuracy and achieves higher target accuracy with a smaller divider width.

5. Conclusions

Today, energy efficiency is a very important factor in computing and signal processing. This study presents an energy quality scalable approximate divider called ASAD-RD to improve the energy efficiency of systems. The proposed design is based on SAADI and the restoring division algorithm. It is an approximate divider that can control the accuracy and latency by repeating the process of approximating the reciprocal of dividends and has better performance than the previous design. It has been demonstrated that the number of iterations can be set to create a trade-off between latency and accuracy; thus, the required accuracy for the application can be met. For the 8 bit division, SAADI has an average accuracy of 90.78% to 98.77%; however, ASAD-RD can improve the accuracy to 95.22% to 99.23% and hardly requires additional power consumption. However, for 99% target accuracy, SAADI requires an over 12 bit division. However, ASAD-RD can achieve 99% target accuracy using just an 8 bit division. Additionally, for the same target accuracy, ASAD-RD requires fewer cycle iterations than SAADI. Thus, ASAD-RD uses lower energy than SAADI and can operate as an energy-efficient approximate divider.

Author Contributions

Conceptualization Y.K.; methodology J.J.; software J.J.; validation J.J. and Y.K.; investigation J.J.; resources Y.K.; writing, original draft preparation J.J.; writing, review and editing Y.K.; supervision Y.K.; project administration Y.K.; funding acquisition Y.K. All authors read and agreed to the published version of the manuscript.

Funding

This work was supported by the Hongik University new faculty research support fund.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Acknowledgments

This work was supported by the Hongik University new faculty research support fund.

Conflicts of Interest

The authors declare no conflict of interest.

Abbreviations

| MSB | Most significant bit |

| MAE | Mean absolute error |

References

- Chippa, V.K.; Venkataramani, S.; Chakradhar, S.T.; Roy, K.; Raghunathan, A. Approximate computing: An integrated hardware approach. In Proceedings of the 2013 Asilomar Conference on Signals, Systems and Computers, Pacific Grove, CA, USA, 3–6 November 2013; pp. 111–117. [Google Scholar]

- Jiang, H.; Liu, C.; Liu, L.; Lombardi, F.; Han, J. A review, classification, and comparative evaluation of approximate arithmetic circuits. ACM J. Emerg. Technol. Comput. Syst. 2017, 13, 1–34. [Google Scholar] [CrossRef]

- Venkataramani, S.; Chakradhar, S.T.; Roy, K.; Raghunathan, A. Approximate computing and the quest for computing efficiency. In Proceedings of the 2015 52nd ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 8–12 June 2015; pp. 1–6. [Google Scholar]

- Chen, L.; Han, J.; Liu, W.; Lombardi, F. On the design of approximate restoring dividers for error-tolerant applications. IEEE Trans. Comput. 2015, 65, 2522–2533. [Google Scholar] [CrossRef]

- Han, J.; Orshansky, M. Approximate computing: An emerging paradigm for energy-efficient design. In Proceedings of the 2013 18th IEEE European Test Symposium (ETS), Avignon, France, 27–30 May 2013; pp. 1–6. [Google Scholar]

- Gupta, V.; Mohapatra, D.; Park, S.P.; Raghunathan, A.; Roy, K. IMPACT: Imprecise adders for low-power approximate computing. In Proceedings of the IEEE/ACM International Symposium on Low Power Electronics and Design, Fukuoka, Japan, 1–3 August 2011; pp. 409–414. [Google Scholar]

- Hashemi, S.; Bahar, R.I.; Reda, S. DRUM: A dynamic range unbiased multiplier for approximate applications. In Proceedings of the 2015 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Austin, TX, USA, 2–6 November 2015; pp. 418–425. [Google Scholar]

- Jiang, H.; Lombardi, F.; Han, J. Low-power unsigned divider and square root circuit designs using adaptive approximation. IEEE Trans. Comput. 2019, 68, 1635–1646. [Google Scholar] [CrossRef]

- Jiang, H.; Liu, L.; Lombardi, F.; Han, J. Adaptive approximation in arithmetic circuits: A low-power unsigned divider design. In Proceedings of the 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 19–23 March 2018; pp. 1411–1416. [Google Scholar]

- Vaeztourshizi, M.; Kamal, M.; Afzali-Kusha, A.; Pedram, M. An energy-efficient, yet highly-accurate, approximate non-iterative divider. In Proceedings of the International Symposium on Low Power Electronics and Design, Seattle, WA, USA, 23–25 July 2018; pp. 1–6. [Google Scholar]

- Vahdat, S.; Kamal, M.; Afzali-Kusha, A.; Pedram, M.; Navabi, Z. TruncApp: A truncation-based approximate divider for energy efficient DSP applications. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, Switzerland, 15 May 2017; pp. 1635–1638. [Google Scholar]

- Zendegani, R.; Kamal, M.; Fayyazi, A.; Afzali-Kusha, A.; Safari, S.; Pedram, M. SEERAD: A high speed yet energy-efficient rounding-based approximate divider. In Proceedings of the 2016 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 14–18 March 2016; pp. 1481–1484. [Google Scholar]

- Raha, A.; Raghunathan, V. Towards full-system energy-accuracy tradeoffs: A case study of an approximate smart camera system. In Proceedings of the 54th Annual Design Automation Conference 2017, Austin, TX, USA, 18–22 June 2017; pp. 1–6. [Google Scholar]

- Behroozi, S.; Li, J.; Melchert, J.; Kim, Y. SAADI: A scalable accuracy approximate divider for dynamic energy-quality scaling. In Proceedings of the 24th Asia and South Pacific Design Automation Conference, Tokyo, Japan, 21–24 January 2019; pp. 481–486. [Google Scholar]

- Chen, T.W.; Ikeda, M. Design and implementation of low-power hardware architecture with single-cycle divider for on-line clustering algorithm. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 2165–2176. [Google Scholar] [CrossRef]

- Melchert, J.; Behroozi, S.; Li, J.; Kim, Y. SAADI-EC: A quality-configurable approximate divider for energy efficiency. IEEE Trans. Very Large Scale Integr. Syst. 2019, 27, 2680–2692. [Google Scholar] [CrossRef]

- Robertson, J.E. A new class of digital division methods. IRE Trans. Electron. Comput. 1958, EC-7, 218–222. [Google Scholar] [CrossRef]

- Aggarwal, N.; Asooja, K.; Verma, S.S.; Negi, S. An improvement in the restoring division algorithm (Needy Restoring Division Algorithm). In Proceedings of the 2009 2nd IEEE International Conference on Computer Science and Information Technology, Beijing, China, 8–11 August 2009; pp. 246–249. [Google Scholar]

- Obermann, S.F.; Flynn, M.J. Division algorithms and implementations. IEEE Trans. Comput. 1997, 46, 833–854. [Google Scholar] [CrossRef]

- Intel. Quartus Prime Lite Edition 18.1. Available online: https://fpgasoftware.intel.com/18.1/?edition=lite (accessed on 10 July 2020).

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).