A Recent Progress of Spintronics Devices for Integrated Circuit Applications

Abstract

1. Introduction

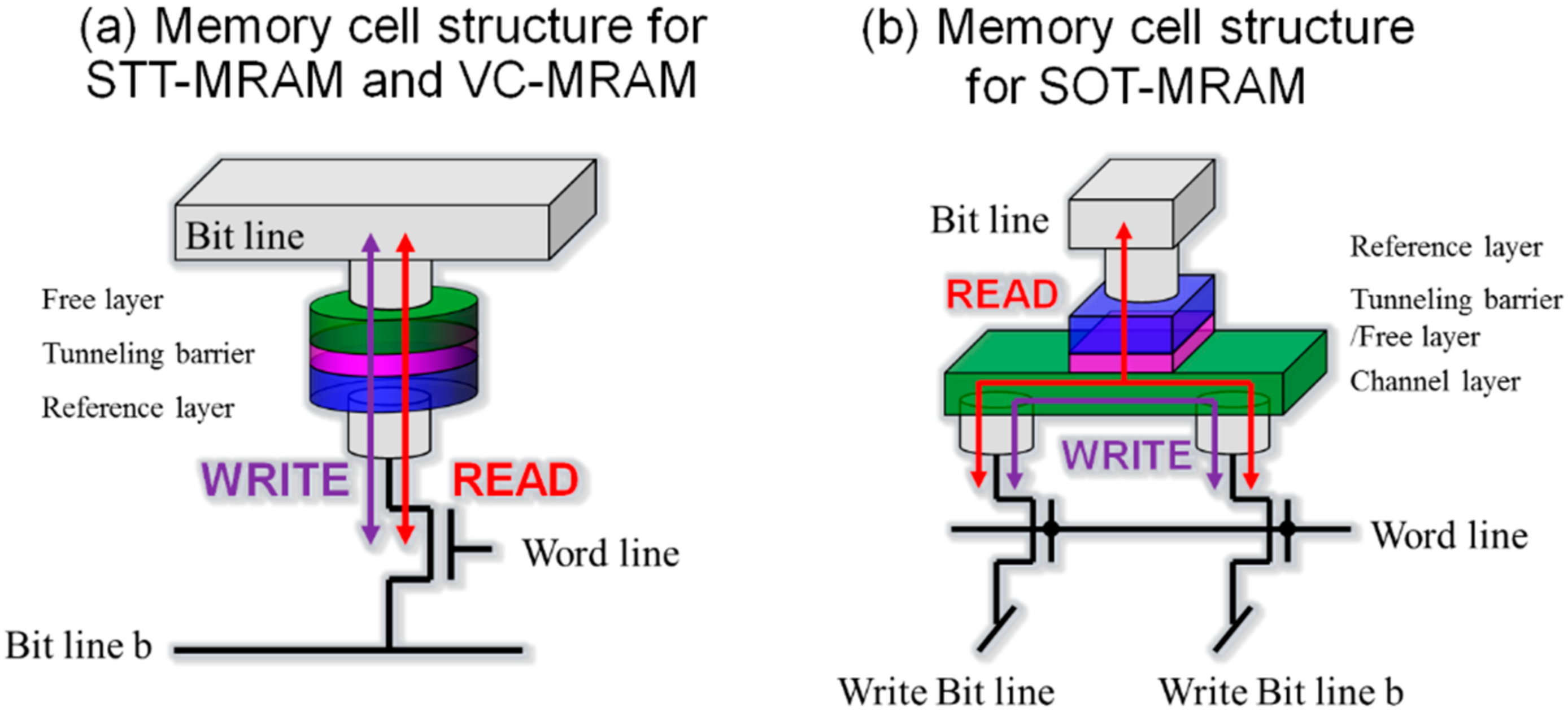

2. Benchmarking Results for STT-MRAM, SOT-MRAM, and E-Field MRAM

3. Review for Recent Progress of STT-MRAM, SOT-MRAM, and E-Field MRAM

3.1. Recent Progress of STT-MRAMs for NV Memory Applications

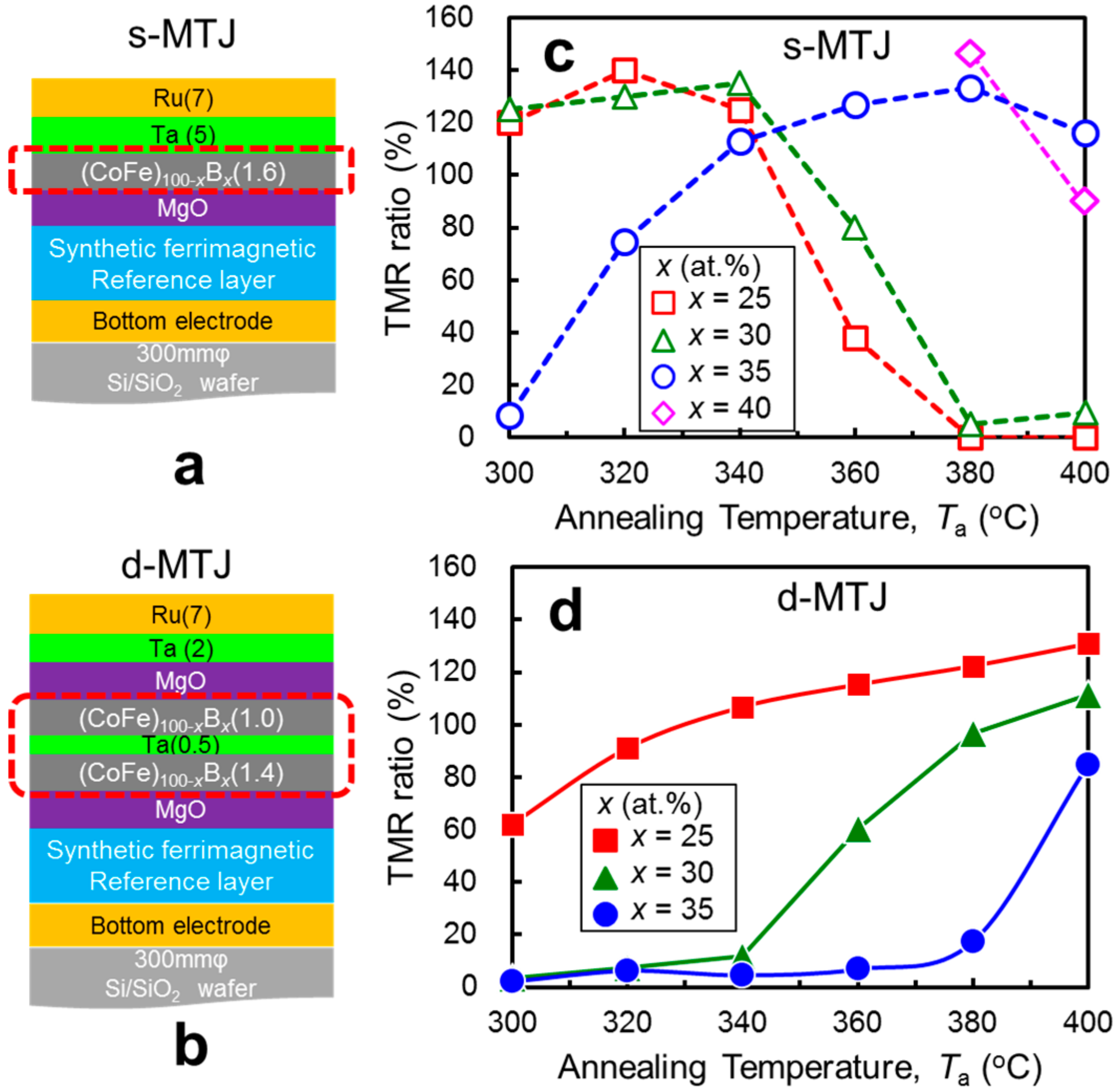

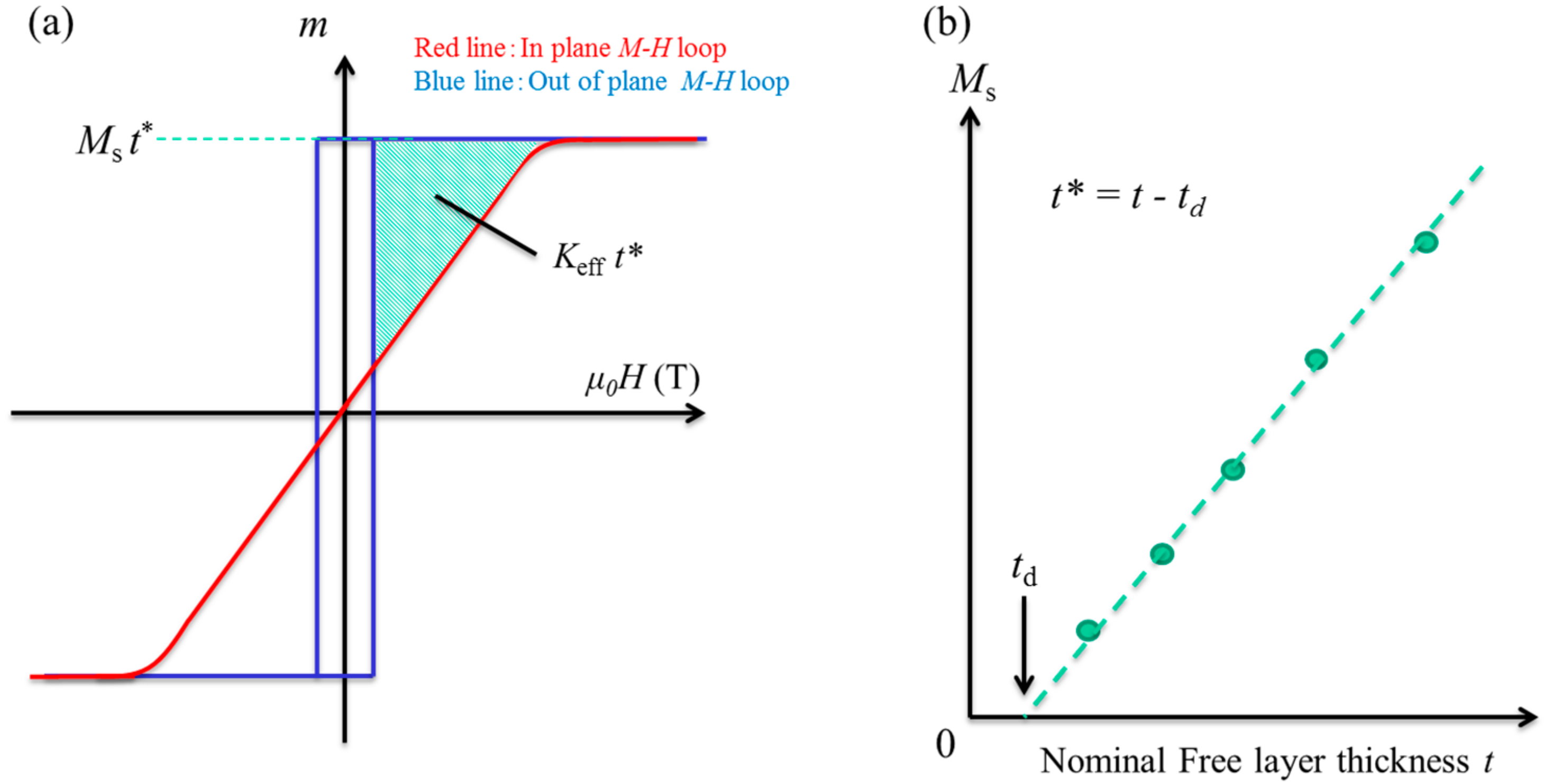

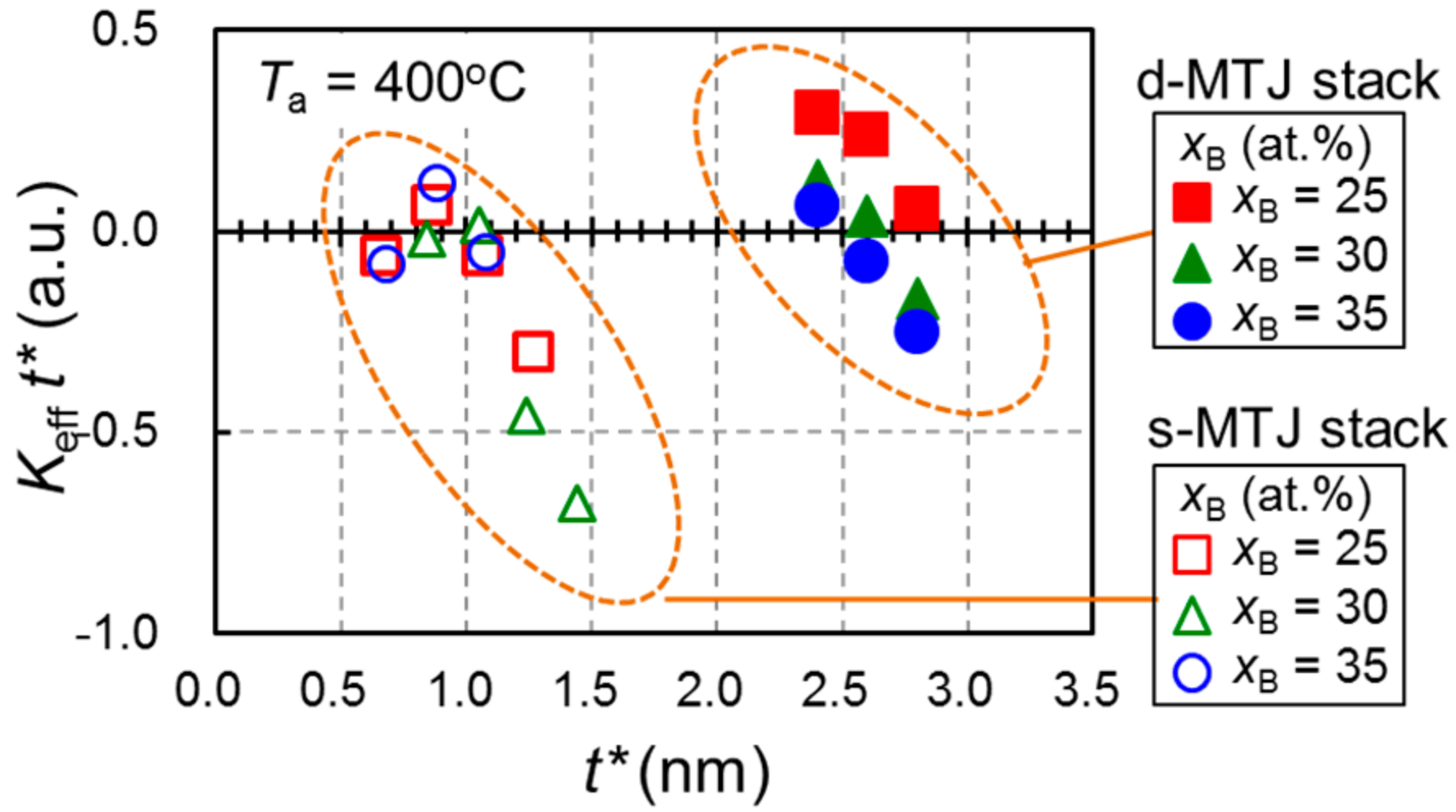

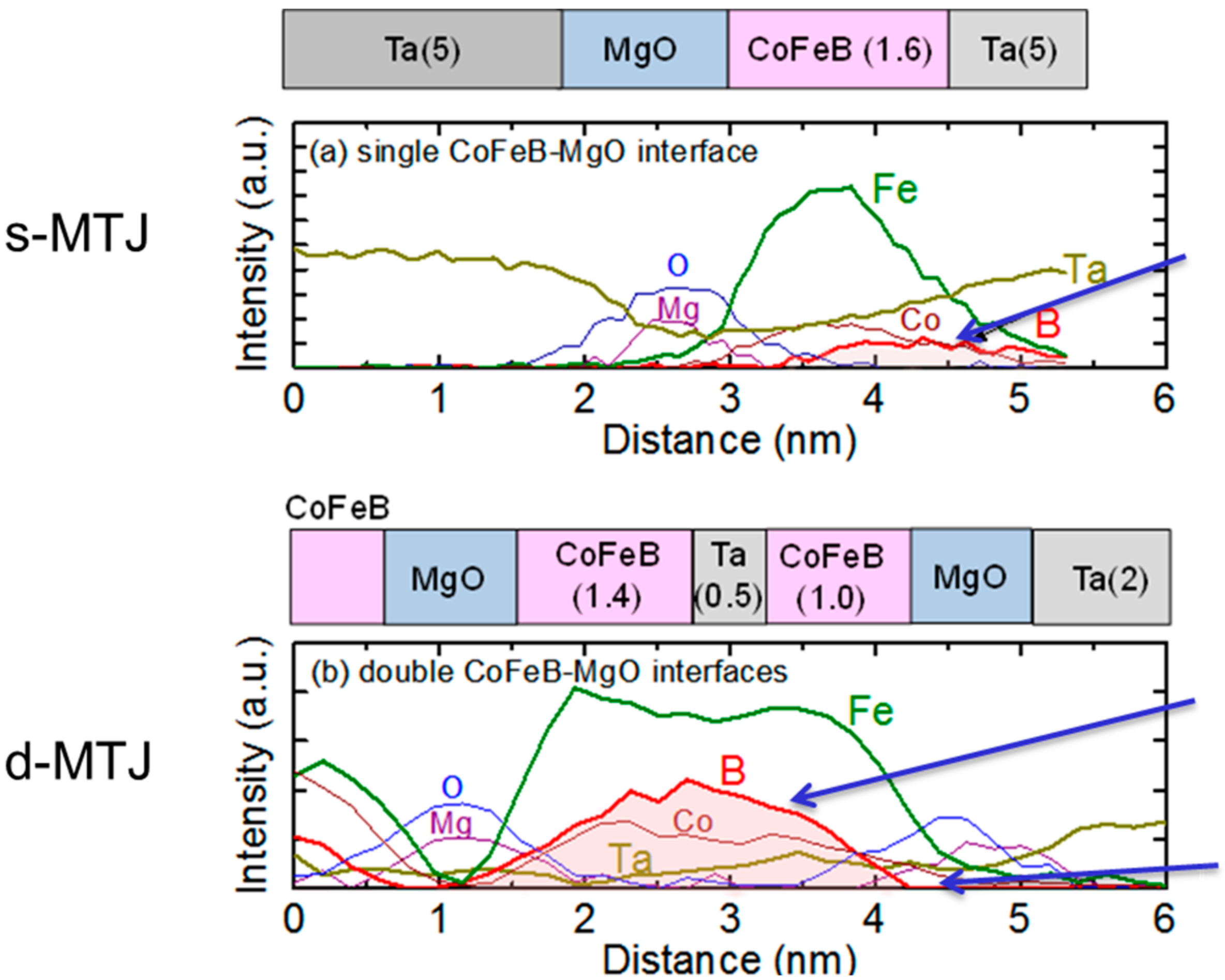

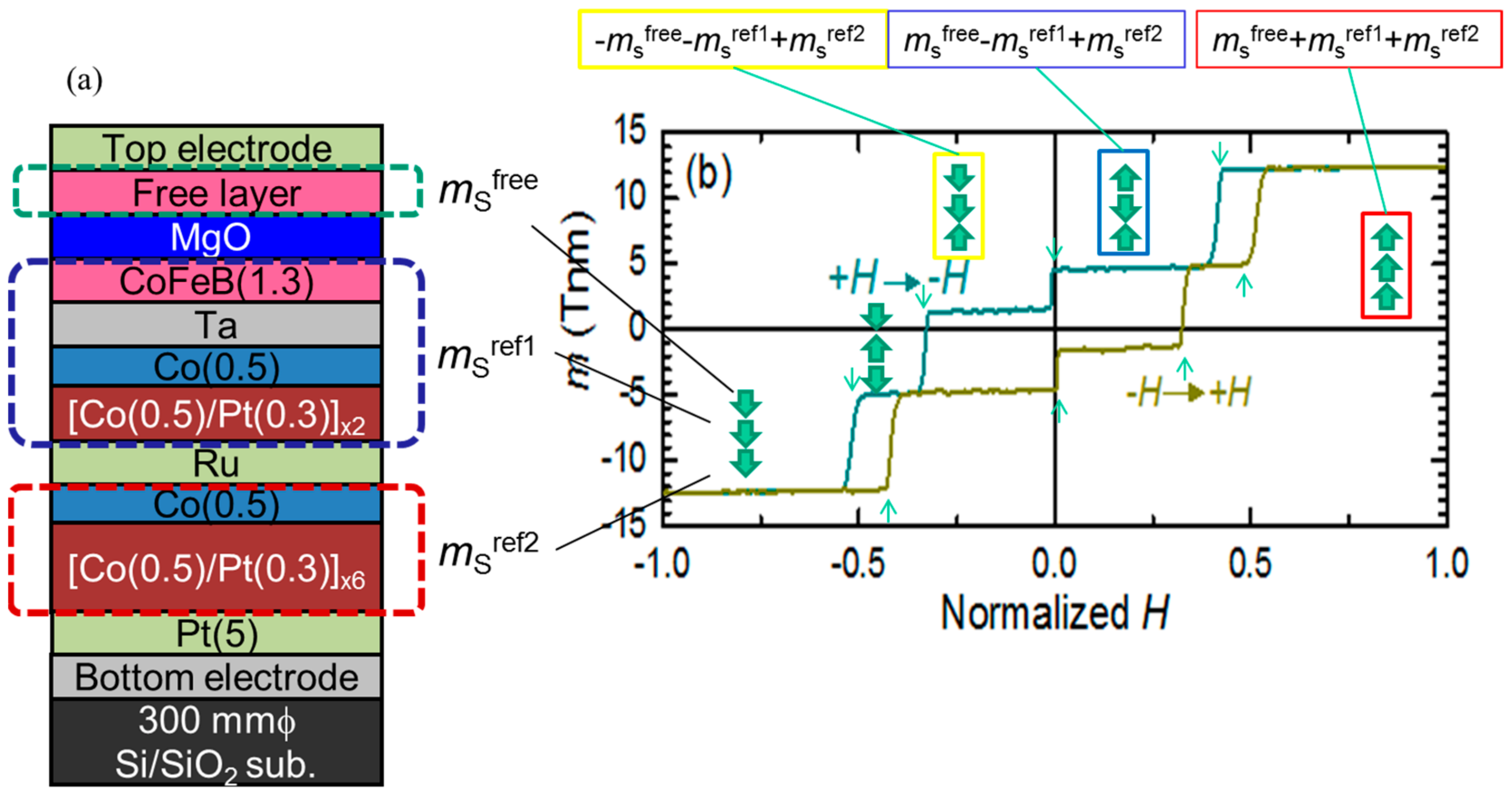

3.1.1. MTJ Design with High Thermal Tolerance for STT-MRAM with CMOS BEOL Process Compatibility

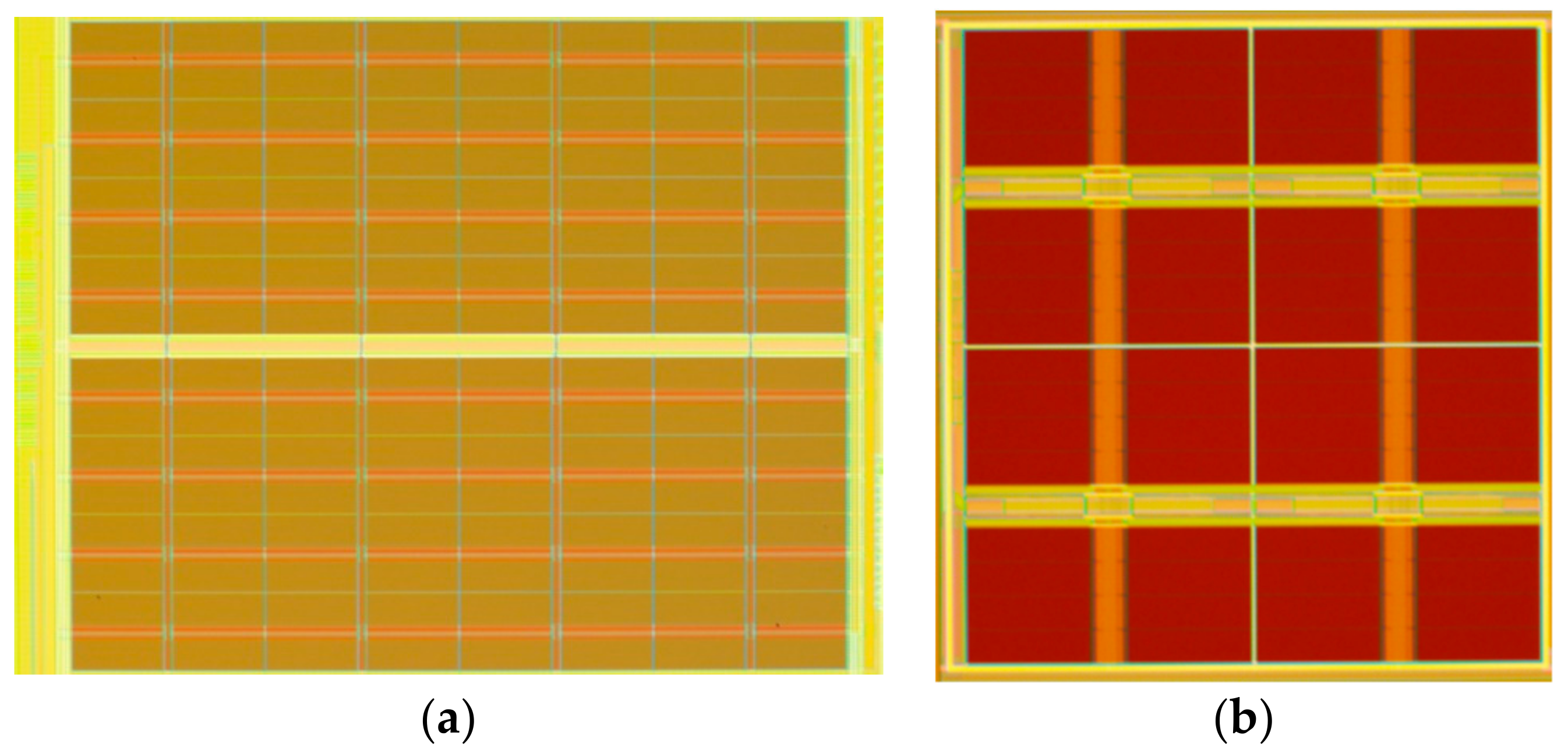

3.1.2. Recent Progress of STT-MRAMs

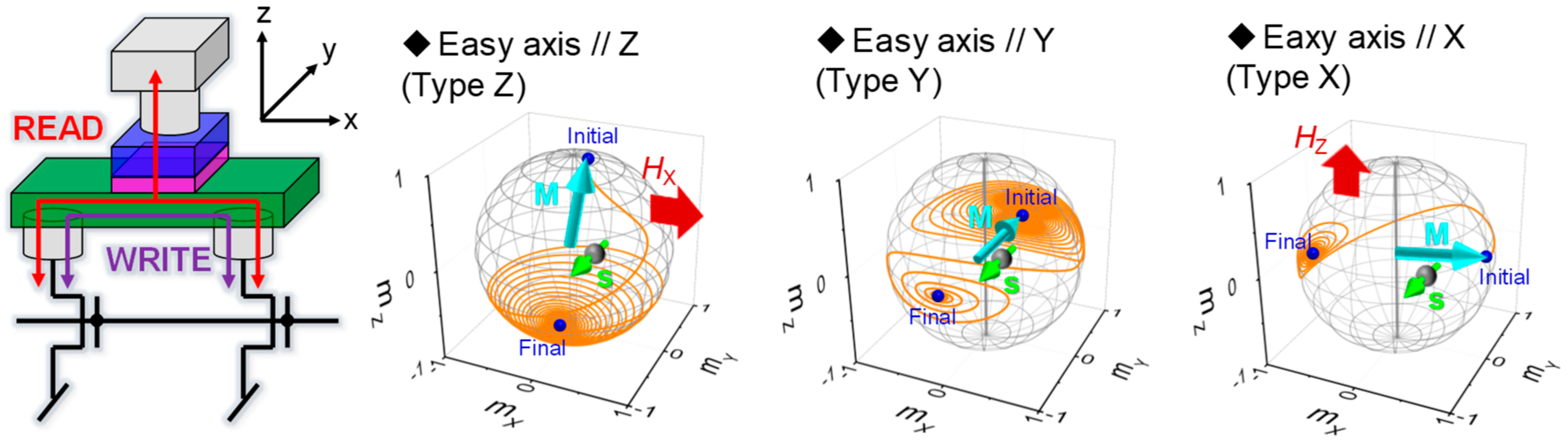

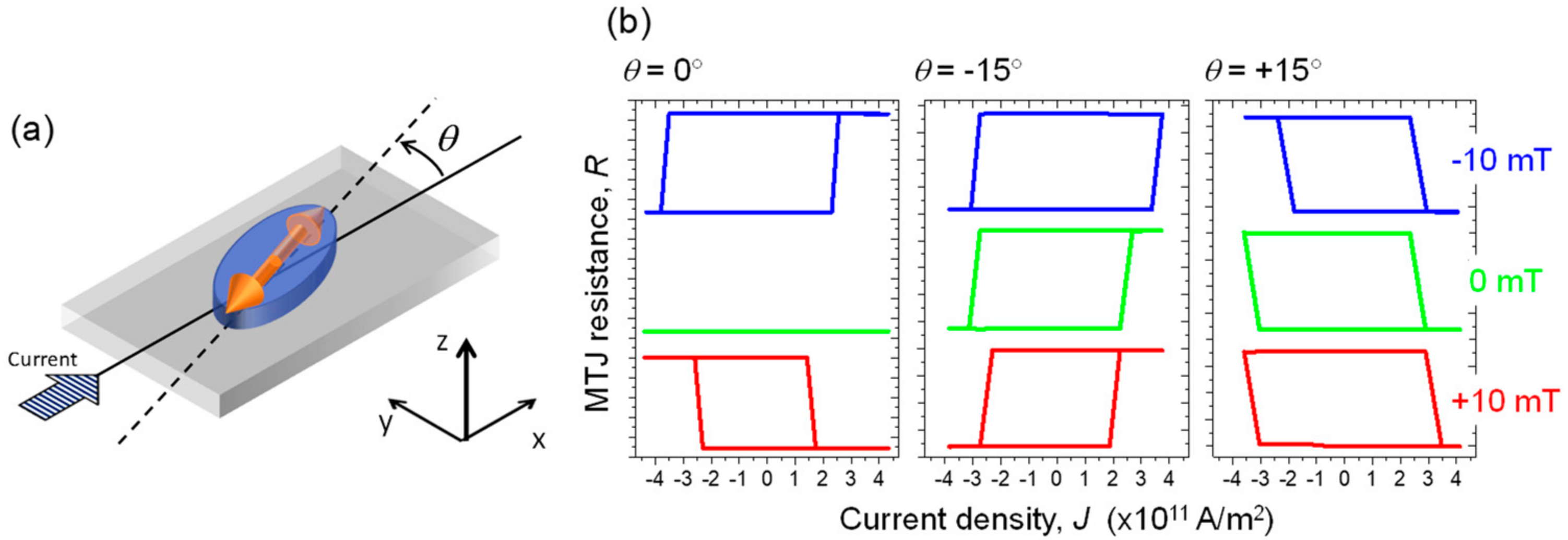

3.2. Progress of SOT-MRAM and Future Issues for NV Memory Applications

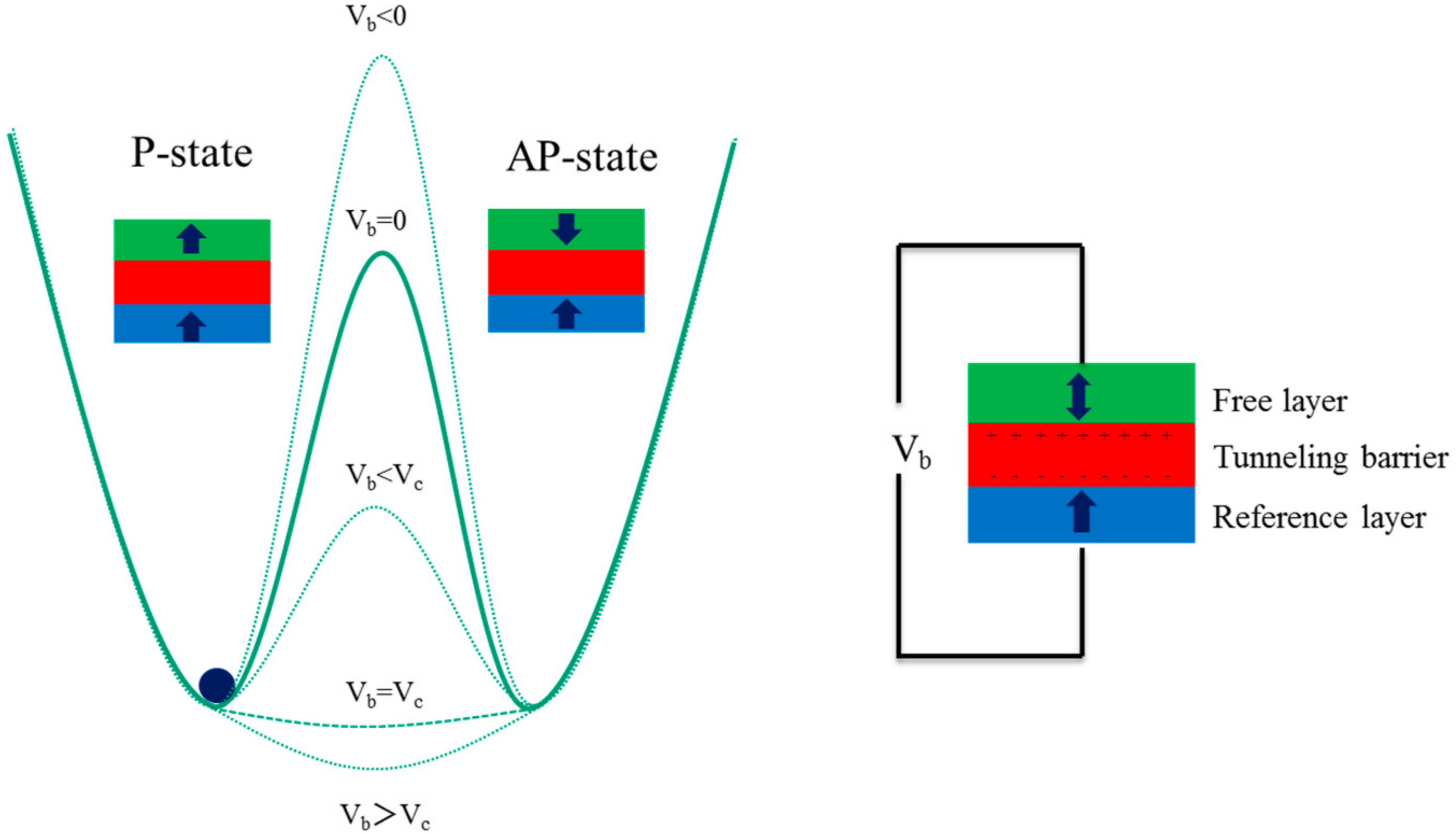

3.3. Progress of VC-MRAM

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Glossary

| BEOL | back-end-of-line |

| MTJ | magnetic tunneling junctions |

| MRAM | magnetic random access memory |

| SOT | spin-orbit torque |

| STT | spin-transfer torque |

| VC | voltage controlled |

References

- Ohno, H.; Endoh, T.; Hanyu, T.; Kasai, N.; Ikeda, S. Magnetic Tunnel Junction for Nonvolatile CMOS Logic. In Proceedings of the 2010 International Electron Devices Meeting 2010, San Francisco, CA, USA, 6–8 December 2010; p. 218. [Google Scholar] [CrossRef]

- Endoh, T.; Koike, H.; Ikeda, S.; Hanyu, T.; Ohno, H. An Overview of Nonvolatile Emerging Memories—Spintronics for Working Memories. IEEE J. Emerg. Sel. Top. Circ. Syst. 2016, 6, 109–119. [Google Scholar] [CrossRef]

- Hanyu, T.; Endoh, T.; Suzuki, D.; Koike, H.; Ma, Y.; Onizawa, N.; Natsui, M.; Ikeda, S.; Ohno, H. Standby-Power-Free Integrated Circuits Using MTJ-Based VLSI Computing. Proc. IEEE 2016, 104, 1844–1863. [Google Scholar] [CrossRef]

- Slonczewski, J.C. Current-driven excitation of magnetic multilayers. J. Magn. Magn. Mater. 1996, 159, L1–L7. [Google Scholar] [CrossRef]

- Berger, L. Emission of spin waves by a magnetic multilayer traversed by a current. Phys. Rev. B 1996, 54, 9353. [Google Scholar] [CrossRef]

- Liu, L.; Pai, C.-F.; Li, Y.; Tseng, H.W.; Ralph, D.C.; Buhrman, R.A. Spin-Torque Switching with the Giant Spin Hall Effect of Tantalum. Science 2012, 336, 555–558. [Google Scholar] [CrossRef] [PubMed]

- Miron, I.M.; Garello, K.; Gaudin, G.; Zermatten, P.J.; Costache, M.V.; Auffret, S.; Bandiera, S.; Rodmacq, B.; Schuhl, A.; Gambardella, P. Perpendicular switching of a single ferromagnetic layer induced by in-plane current injection. Nature 2011, 476, 189–193. [Google Scholar] [CrossRef] [PubMed]

- Chernyshov, A.; Overby, M.; Liu, X.; Furdyna, J.K.; Lyanda-Geller, Y.; Rokhinson, L.P. Evidence for reversible control of magnetization in a ferromagnetic material by means of spin–orbit magnetic field. Nat. Phys. 2009, 5, 656–659. [Google Scholar] [CrossRef]

- Rizal, C.; Moa, B.; Niraula, B.B. Ferromagnetic Multilayers: Magnetoresistance, Magnetic Anisotropy, and Beyond. Magnetochemistry 2016, 2, 22. [Google Scholar] [CrossRef]

- Noguchi, H.; Ikegami, K.; Abe, K.; Fujita, S.; Shiota, Y.; Nozaki, T.; Yuasa, S.; Suzuki, Y. Novel Voltage Controlled MRAM (VCM) with Fast Read/Write Circuits for Ultra Large Last Level Cache. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; p. 4. [Google Scholar]

- Kang, S.H.; Park, C. MRAM: Enabling a Sustainable Device for Pervasive System Architectures and Applications. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; p. 4. [Google Scholar]

- Maurelli, A. Embedded Non Volatile Memories for Automotive applications. In Proceedings of the Short Course of International Electron Devices Meeting, San Francisco, CA, USA, 5–7 December 2017. [Google Scholar]

- Shum, P.D. Embedded MRAM Technology for IoT & Automotive. In Proceedings of the Short Course of International Electron Devices Meeting, San Francisco, CA, USA, 5–7 December 2017. [Google Scholar]

- Ikeda, S.; Miura, K.; Yamamoto, H.; Mizunuma, K.; Gan, H.D.; Endo, M.; Kanai, S.; Hayakawa, J.; Matsukura, F.; Ohno, H. A perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction. Nat. Mater. 2010, 9, 721–724. [Google Scholar] [CrossRef] [PubMed]

- Sato, H.; Yamanouchi, M.; Ikeda, S.; Fukami, S.; Matsukura, F.; Ohno, H. Perpendicular-anisotropy CoFeB-MgO magnetic tunnel junctions with a MgO/CoFeB/Ta/CoFeB/MgO recording structure. Appl. Phys. Lett. 2012, 101, 022414. [Google Scholar] [CrossRef]

- Sato, H.; Enobio, E.C.I.; Yamanouchi, M.; Ikeda, S.; Fukami, S.; Kanai, S.; Matsukura, F.; Ohno, H. Properties of magnetic tunnel junctions with a MgO/CoFeB/Ta/CoFeB/MgO recording structure down to junction diameter of 11 nm. Appl. Phys. Lett. 2014, 105, 062403. [Google Scholar] [CrossRef]

- Sato, H.; Ikeda, S.; Fukami, S.; Honjo, H.; Ishikawa, S.; Yamanouchi, S.; Mizunuma, K.; Matsukura, S.; Ohno, H. Co/Pt multilayer based reference layers in magnetic tunnel junctions for nonvolatile spintronics VLSIs. Jpn. J. Appl. Phys. 2014, 53, 04EM02. [Google Scholar] [CrossRef]

- Honjo, H.; Sato, H.; Ikeda, S.; Sato, S.; Watanabe, T.; Miura, S.; Nasuno, T.; Noguchi, Y.; Yasuhira, M.; Tanigawa, T.; et al. 10 nmf perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction with over 400 °C high thermal tolerance by boron diffusion control. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T160–T161. [Google Scholar] [CrossRef]

- Honjo, H.; Ikeda, S.; Sato, H.; Watanabe, T.; Miura, S.; Nasuno, T.; Noguchi, Y.; Yasuhira, M.; Tanigawa, T.; Koike, H.; et al. Origin of variation of shift field via annealing at 400 °C in a perpendicular-anisotropy magnetic tunnel junction with [Co/Pt]-multilayers based synthetic ferrimagnetic reference layer. AIP Adv. 2017, 7, 055913. [Google Scholar] [CrossRef]

- Honjo, H.; Ikeda, S.; Sato, S.; Nishioka, K.; Watanabe, T.; Miura, S.; Nasuno, T.; Noguchi, Y.; Inoue, H.; Yasuhira, M.; et al. High thermal tolerance synthetic ferrimagnetic reference layer with modified buffer layer by ion irradiation for perpendicular anisotropy magnetic tunnel junctions. In Proceedings of the 2018 IEEE International Magnetic Conference (INTERMAG), Singapore, 23–27 April 2018; p. HC-05. [Google Scholar]

- Ikeda, S.; Koizumi, R.; Sato, H.; Yamanouchi, S.; Miura, K.; Mizunuma, K.; Gan, H.; Matsukura, S.; Ohno, H. Boron Composition Dependence of Magnetic Anisotropy and Tunnel Magnetoresistance in MgO/CoFe(B) Based Stack Structures. IEEE. Trans. Magn. 2012, 48, 3829–3832. [Google Scholar] [CrossRef]

- Watanabe, K.; Ishikawa, S.; Sato, H.; Ikeda, S.; Yamanouchi, S.; Fukami, S.; Matsukura, S.; Ohno, H. Dependence of magnetic properties of MgO/CoFeB/Ta stacks on CoFeB and Ta thicknesses. Jpn. J. Appl. Phys. 2015, 54, 04DM04. [Google Scholar] [CrossRef]

- Miyajima, T.; Ibusuki, T.; Umehara, T.; Sato, M.; Eguchi, S.; Tsukada, M.; Kataoka, Y. Transmission electron microscopy study on the crystallization and boron distribution of CoFeB/MgO/CoFeB magnetic tunnel junctions with various capping layers. Appl. Phys. Lett. 2009, 94, 122501. [Google Scholar] [CrossRef]

- Karthik, S.V.; Takahashi, Y.K.; Ohkubo, T.; Ikeda, S.; Ohno, H. Transmission electron microscopy investigation of CoFeB/MgO/CoFeB pseudospin valves annealed at different temperatures. J. Appl. Phys. 2009, 94, 023920. [Google Scholar] [CrossRef]

- Ikeda, S.; Hayakawa, J.; Lee, Y.M.; Tanikawa, T.; Matsukura, S.; Ohno, H. Tunnel magnetoresistance in MgO-barrier magnetic tunnel junctions with bcc-CoFe(B) and fcc-CoFe free layers. J. Appl. Phys. 2006, 99, 08A907. [Google Scholar] [CrossRef]

- Sinha, J.; Hayashi, M.; Kellock, A.J.; Fukami, S.; Yamanouchi, S.; Sato, H.; Ikeda, S.; Mitani, S.; Yang, S.-H.; Parkin, S.S.P.; et al. Enhanced interface perpendicular magnetic anisotropy in Ta|CoFeB|MgO using nitrogen doped Ta underlayers. Appl. Phys. Lett. 2013, 102, 242405. [Google Scholar] [CrossRef]

- Gan, H.D.; Ikeda, S.; Shiga, W.; Hayakawa, J.; Miura, K.; Yamamoto, H.; Hasegawa, H.; Matsukura, S.; Ohkubo, T.; Hono, K.; et al. Tunnel magnetoresistance properties and film structures of double MgO barrier magnetic tunnel junctions. Appl. Phys. Lett. 2010, 96, 192507. [Google Scholar] [CrossRef]

- Feng, G.; Dijken, S.V.; Feng, J.F.; Coey, J.M.D.; Leo, T.; Smith, D.J. Annealing of CoFeB/MgO based single and double barrier magnetic tunnel junctions: Tunnel magnetoresistance, bias dependence, and output voltage. J. Appl. Phys. 2009, 105, 033916. [Google Scholar] [CrossRef]

- Honjo, H.; Ikeda, S.; Sato, H.; Sato, S.; Watanabe, T.; Miura, S.; Nasuno, T.; Noguchi, Y.; Yasuhira, M.; Tanigawa, T.; et al. Improvement of thermal tolerance of CoFeB-MgO perpendicular-anisotropy magnetic tunnel junctions by controlling boron composition. IEEE. Trans. Magn. 2016, 52, 340110. [Google Scholar] [CrossRef]

- Kodzuka, M.; Ohkubo, T.; Hono, K.; Ikeda, S.; Gan, H.D.; Ohno, H. Effects of boron composition on tunneling magnetoresistance ratio and microstructure of CoFeB/MgO/CoFeB pseudo-spin-valve magnetic tunnel junctions. J. Appl. Phys. 2012, 111, 043913. [Google Scholar] [CrossRef]

- Watanabe, K.; Fukami, S.; Sato, H.; Ikeda, S.; Matsukura, S.; Ohno, H. Annealing temperature dependence of magnetic properties of CoFeB/MgO stacks on different buffer layers. Jpn. J. Appl. Phys. 2017, 56, 0802B2. [Google Scholar] [CrossRef]

- Xu, X.D.; Mukaiyama, K.; Kasai, S.; Ohkubo, T.; Hono, K. Impact of boron diffuision at MgO grain boundaries on magneto-transport properties of MgO/CoFeB/W magnetic tunnel junctions. Acta Mater. 2018, 161, 360–366. [Google Scholar] [CrossRef]

- Iwata-Harms, J.M.; Jan, G.; Liu, H.; Serrano-Guisan, S.; Zhu, J.; Thomas, L.; Tong, R.-Y.; Sunder, V.; Wang, P.-K. High-temperature thermal stability driven by magnetization dilution in CoFeB free layers for spin-transfer-torque magnetic random access memory. Sci. Rep. 2018, 8, 14409. [Google Scholar] [CrossRef] [PubMed]

- Kim, W.; Couet, S.; Swerts, J.; Lin, T.; Tomczak, Y.; Souriau, L.; Tsvetanova, D.; Sankaran, K.; Donadio, G.L.; Crotti, D.; et al. Experimental Observation of Back-Hopping with Reference layer Flipping by High-Voltage Pulse in Perpendicular Magnetic Tunnel Junctions. IEEE. Trans. Magn. 2016, 52, 3401004. [Google Scholar] [CrossRef]

- Goff, A.L.; Garcia, K.; Vernier, N.; Tahmasebi, T.; Cornelissen, S.; Min, T.; Devolder, T. Effect of Ta insertion in Reference Layers of MTJs With Perpendicular Anisotoropy. IEEE Trans. Magn. 2014, 50. [Google Scholar] [CrossRef]

- Goff, A.L.; Soucaille, R.; Tahmasebi, T.; Swerts, J.; Furnemont, A.; Devolder, T. Optimization of top-pinned perpendicular anisotropy tunnel junctions through Ta insertion. Jpn. J. Appl. Phys. 2015, 54, 090302. [Google Scholar] [CrossRef]

- Cuchet, L.; Rodmacq, B.; Auffret, S.; Sousa, R.; Ducruet, C.; Dieny, B. Influence of a Ta spacer on the magnetic and transport properties of perpendicular magnetic tunnel junctions. Appl. Phys. Lett. 2013, 103, 052402. [Google Scholar] [CrossRef]

- Couet, S.; Devolver, T.; Swerts, J.; Mertens, S.; Lin, T.; Liu, E.; Elshocht, S.V.; Kar, G.S. Impact of Ta and W-based spacers in double MgO STT-MRAM free layers on perpendicular anisotoropy and damping. Appl. Phys. Lett. 2017, 111, 152406. [Google Scholar] [CrossRef]

- Lee, D.-Y.; Hong, S.-H.; Lee, S.-E.; Park, J.-G. Dependency of Tunneling-Magnetoresistance Ratio on Nanoscale Spacer Thickness and Material for Double MgO Based Perpendicular-Magnetic-Tunneling-Junction. Nat. Sci. Rep. 2016, 6, 38125. [Google Scholar] [CrossRef] [PubMed]

- Kim, J.-H.; Lee, J.-B.; An, G.-G.; Yang, S.-M.; Chung, W.-S.; Park, H.-S.; Hong, J.-P. Ultrathin W space layer-enabled thermal stability enhancement in a perpendicular MgO/CoFeB/W/CoFeB/MgO recording frame. Nat. Sci. Rep. 2015, 5, 16903. [Google Scholar] [CrossRef] [PubMed]

- Lee, S.-E.; Shim, T.-H.; Park, J.-G. Perpendicular magnetic tunnel junction (p-MTJ) spin-valves designed with a top Co2Fe6B2 free layer and a nanoscale-thick tungsten bridging and capping layer. NPG Asia Mater. 2016, 8, e324. [Google Scholar] [CrossRef]

- Chatterjee, J.; Sousa, R.C.; Perrissin, N.; Auffret, S.; Ducruet, C.; Dieny, B. Enhanced annealing stability and perpendicular magnetic anisotropy in perpendicular magnetic tunnel junctions using W layer. Appl. Phys. Lett. 2017, 110, 202401. [Google Scholar] [CrossRef]

- Choi, J.Y.; Lee, D.-G.; Baek, J.-U.; Park, J.-G. Double MgO-based Perpendicular Magnetic-Tunnel-Junction Spin-valve Structure with a Top Co2Fe6B2 Free Layer using a Single SyAF [Co/Pt]n Layer. Nat. Sci. Rep. 2018, 8, 2139. [Google Scholar] [CrossRef] [PubMed]

- Wang, M.; Cai, W.; Cao, K.; Zhou, J.; Wrona, J.; Peng, S.; Yang, H.; Wei1, J.; Kang, W.; Zhang, Y.; et al. Current-induced magnetization switching in atom thick tungsten engineered perpendicular magnetic tunnel junctions with large tunnel magnetoresistance. Nat. Commun. 2018, 9, 671. [Google Scholar] [CrossRef] [PubMed]

- Winters, H.F.; Coufal, H.J. Influence of energy reflected from the target on thin film characteristics. J. Vac. Sci. Technol. A 1993, 11, 657–663. [Google Scholar] [CrossRef]

- Iwatsubo, S.; Takahashi, T.; Naoe, M. Magnetic properties of Fe films deposited by Ar, Kr, and Xe ion beam sputtering. J. Appl. Phys. 1998, 83, 6667–6669. [Google Scholar] [CrossRef]

- Maeda, Y.; Suzuki, Y.; Sakashima, Y.; Iwata, S.; Kato, S.; Tsunashima, S.; Toyoda, H.; Sugai, I. Effect of sputtering Deposition Process on Magnetic Properties of Magnetic CoPt multilayer. Jpn. J. Appl. Phys. 2008, 47, 7879–7885. [Google Scholar] [CrossRef]

- Honjo, H.; Fukami, S.; Ishihara, K.; Nebashi, R.; Kinoshita, K.; Tokutome, K.; Murahata, M.; Miura, S.; Sakimura, N.; Sugibayashi, T.; et al. Three-terminal magnetic tunneling junction device with perpendicular anisotropy CoFeB sensing layer. J. Appl. Phys. 2014, 115, 17B750. [Google Scholar] [CrossRef]

- Honjo, H.; Ikeda, S.; Sato, H.; Nishioka, K.; Watanabe, T.; Miura, S.; Nasuno, T.; Noguchi, Y.; Yasuhira, M.; Tanigawa, T.; et al. Impact of tungsten sputtering condition on magnetic and transport properties of double-MgO magnetic tunneling junction with CoFeB/W/CoFeB free layer. IEEE Trans. Magn. 2017, 53, 2501604. [Google Scholar] [CrossRef]

- Honjo, H.; Ikeda, S.; Sato, H.; Yasuhira, M.; Endoh, T. Critical role of W insertion layer sputtering condition for reference layer on magnetic and transport properties of perpendicular-anisotropy magnetic tunnel junction. In Proceedings of the Joint MMM and International Magnetic Conference, Washington, DC, USA, 14–18 January 2019. [Google Scholar]

- Ohsawa, T.; Miura, S.; Kinoshita, K.; Honjo, H.; Ikeda, S.; Hanyu, T.; Ohno, H.; Endoh, T. A 1.5nsec/2.1nsec random read/write cycle 1Mb STT-RAM using 6T2MTJ cell with background write for nonvolatile e-memories. In Proceedings of the 2013 Symposium on VLSI Circuits, Kyoto, Japan, 12–14 June 2013; pp. 110–111. [Google Scholar]

- Koike, H.; Miura, S.; Honjo, H.; Watanabe, T.; Sato, H.; Sato, S.; Nasuno, T.; Noguchi, Y.; Yasuhira, M.; Tanigawa, T.; et al. 1T1MTJ STT-MRAM Cell Array Design with an Adaptive Reference Voltage Generator for Improving Device Variation Tolerance. In Proceedings of the 2015 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 17–20 May 2015; pp. 141–144. [Google Scholar] [CrossRef]

- Chung, S.-W.; Kishi, T.; Park, J.W.; Yoshikawa, M.; Park, K.S.; Nagase, T.; Sunouchi, K.; Kanaya, H.; Kim, G.C.; Noma, K.; et al. 4Gbit density STT-MRAM using perpendicular MTJ realized with compact cell structure. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 659–662. [Google Scholar] [CrossRef]

- Kang, S.H. Embedded STT-MRAM for Energy-efficient and Cost-effective Mobile Systems. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 44–45. [Google Scholar] [CrossRef]

- Lee, K.; Yamane, K.; Noh, S.; Naik, V.B.; Yang, H.; Jang, S.H.; Kwon, J.; Behin-Aein, B.; Chao, R.; Lim, J.H.; et al. 22-nm FD-SOI Embedded MRAM with Full Solder Reflow Compatibility and Enhanced Magnetic Immunity. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 183–184. [Google Scholar]

- Lee, Y.K.; Song, Y.; Kim, J.C.; Oh, S.C.; Bae, B.-J.; Lee, S.H.; Le, J.H.; Pi, U.H.; Seo, B.; Jung, H.; et al. Embedded STT-MRAM in 28-nm FDSOI Logic Process for Industrial MCU/IoT Application. In Proceedings of the VLSI Symposium on Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 181–182. [Google Scholar]

- Sato, H.; Watanabe, T.; Koike, H.; Saito, T.; Miura, S.; Honjo, H.; Inoue, H.; Ikeda, S.; Noguchi, Y.; Tanigawa, T.; et al. 1T-1MTJ type embedded STT-MRAM with advanced low-damage and short-failure-free RIE technology down to 32 nmφ MTJ patterning. In Proceedings of the 2018 IEEE International Memory Workshop (IMW), Kyoto, Japan, 13–16 May 2018; pp. 135–138. [Google Scholar] [CrossRef]

- Pai, C.-F.; Liu, L.; Li, Y.; Tseng, H.W.; Ralph, D.C.; Buhrman, R.A. Spin transfer torque devices utilizing the giant spin Hall effect of tungsten. Appl. Phys. Lett. 2012, 101, 122404. [Google Scholar] [CrossRef]

- Yamanouchi, M.; Chen, L.; Kim, J.; Hayashi, M.; Sato, H.; Fukami, S.; Ikeda, S.; Matsukura, F.; Ohno, H. Three terminal magnetic tunnel junction utilizing the spin Hall effect of iridium-doped copper. Appl. Phys. Lett. 2013, 102, 212408. [Google Scholar] [CrossRef]

- Fan, Y.; Upadhyaya, P.; Kou, X.; Lang, M.; Takei, S.; Wang, Z.; Tang, J.; He, L.; Chang, L.T.; Montazeri, M.; et al. Magnetization switching through giant spin-orbit torque in a magnetically doped topological insulator heterostructure. Nat. Mater. 2014, 13, 699–704. [Google Scholar] [CrossRef] [PubMed]

- Akyol, M.; Yu, G.; Alzate, J.G.; Upadhyaya, P.; Li, X.; Wong, K.L.; Ekicibil, A.; Khalili Amiri, P.; Wang, K.L. Current-induced spin-orbit torque switching of perpendicularly magnetized Hf|CoFeB|MgO and Hf|CoFeB|TaOx structures. Appl. Phys. Lett. 2015, 106, 162409. [Google Scholar] [CrossRef]

- Fukami, S.; Zhang, C.; DuttaGupta, S.; Kurenkov, A.; Ohno, H. Magnetization switching by spin-orbit torque in an antiferromagnet-ferromagnet bilayer system. Nat. Mater. 2016, 15, 535–541. [Google Scholar] [CrossRef] [PubMed]

- Oh, Y.W.; Chris Baek, S.H.; Kim, Y.M.; Lee, H.Y.; Lee, K.D.; Yang, C.G.; Park, E.S.; Lee, K.S.; Kim, K.W.; Go, G.; et al. Field-free switching of perpendicular magnetization through spin-orbit torque in antiferromagnet/ferromagnet/oxide structures. Nat. Nanotechnol. 2016, 11, 878–884. [Google Scholar] [CrossRef] [PubMed]

- Fukami, S.; Ohno, H. Magnetization switching schemes for nanoscale three-terminal spintronics devices. Jpn. J. Appl. Phys. 2017, 56, 0802A0801. [Google Scholar] [CrossRef]

- Takeuchi, Y.; Zhang, C.; Okada, A.; Sato, H.; Fukami, S.; Ohno, H. Spin-orbit torques in high-resistivity-W/CoFeB/MgO. Appl. Phys. Lett. 2018, 112, 192408. [Google Scholar] [CrossRef]

- Fukami, S.; Anekawa, T.; Zhang, C.; Ohno, H. A spin-orbit torque switching scheme with collinear magnetic easy axis and current configuration. Nat. Nanotechnol. 2016, 11, 621–625. [Google Scholar] [CrossRef] [PubMed]

- Fukami, S.; Anekawa, T.; Zhang, C.; Ohno, H. A sub-ns three-terminal spin-orbit torque induced switching device. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; p. 2. [Google Scholar]

- Lau, Y.-C.; Hayashi, M. Spin torque efficiency of Ta, W, and Pt in metallic bilayers evaluated by harmonic Hall and spin Hall magnetoresistance measurements. Jpn. J. Applied. Phys. 2017, 56, 0802B5. [Google Scholar] [CrossRef]

- Ohno, H.; Chiba, D.; Matsukura, F.; Omiya, T.; Abe, E.; Dietl, T.; Ohno, Y.; Ohtani, K. Electric-field control of ferromagnetism. Nature 2000, 408, 944–946. [Google Scholar] [CrossRef] [PubMed]

- Chiba, D.; Yamanouchi, M.; Matsukura, F.; Ohno, H. Electrical Manipulation of Magnetization Reversal in a Ferromagnetic Semiconductor. Science 2003, 301, 943–945. [Google Scholar] [CrossRef] [PubMed]

- Chiba, D.; Sawicki, M.; Nishitani, Y.; Nakatani, Y.; Matsukura, F.; Ohno, H. Magnetization vector manipulation by electric fields. Nature 2008, 455, 515–518. [Google Scholar] [CrossRef] [PubMed]

- Chiba, D.; Werpachowska, A.; Endo, M.; Nishitani, Y.; Matsukura, F.; Dietl, T.; Ohno, H. Anomalous Hall Effect in Field-Effect Structures of (Ga,Mn)As. Phys. Rev. Lett. 2010, 104, 106601. [Google Scholar] [CrossRef] [PubMed]

- Weisheit, M.; Fahler, S.; Marty, A.; Souche, Y.; Poinsignon, C.; Givord, D. Electric Field–Induced Modification of Magnetism in Thin-Film Ferromagnets. Science 2007, 315, 349–351. [Google Scholar] [CrossRef] [PubMed]

- Maruyama, T.; Shiota, Y.; Nozaki, T.; Ohta, K.; Toda, N.; Mizuguchi, M.; Tulapurkar, A.A.; Shinjo, T.; Shiraishi, M.; Mizukami, S.; et al. Large voltage-induced magnetic anisotropy change in a few atomic layers of iron. Nat. Nanotechnol. 2009, 4, 158–161. [Google Scholar] [CrossRef] [PubMed]

- Endo, M.; Kanai, S.; Ikeda, S.; Matsukura, F.; Ohno, H. Electric-field effects on thickness dependent magnetic anisotropy of sputtered MgO/Co40Fe40B20/Ta structures. Appl. Phys. Lett. 2010, 96, 212503. [Google Scholar] [CrossRef]

- Zhernenkov, M.; Fitzsimmons, M.R.; Chlistunoff, J.; Majewski, J.; Tudosa, I.; Fullerton, E.E. Electric-field modification of magnetism in a thin CoPd film. Phys. Rev. B 2010, 82, 024420. [Google Scholar] [CrossRef]

- Shiota, Y.; Nozaki, T.; Bonell, F.; Murakami, S.; Shinjo, T.; Suzuki, Y. Induction of coherent magnetization switching in a few atomic layers of FeCo using voltage pulses. Nat. Mater. 2011, 11, 39–43. [Google Scholar] [CrossRef] [PubMed]

- Wang, W.G.; Li, M.; Hageman, S.; Chien, C.L. Electric-field-assisted switching in magnetic tunnel junctions. Nat. Mater. 2011, 11, 64–68. [Google Scholar] [CrossRef] [PubMed]

- Kanai, S.; Yamanouchi, M.; Ikeda, S.; Nakatani, Y.; Matsukura, F.; Ohno, H. Electric field-induced magnetization reversal in a perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction. Appl. Phys. Lett. 2012, 101, 122403. [Google Scholar] [CrossRef]

- Nozaki, T.; Shiota, Y.; Miwa, S.; Murakami, S.; Bonell, F.; Ishibashi, S.; Kubota, H.; Yakushiji, K.; Saruya, T.; Fukushima, A.; et al. Electric-field-induced ferromagnetic resonance excitation in an ultrathin ferromagnetic metal layer. Nat. Phys. 2012, 8, 491–496. [Google Scholar] [CrossRef]

- Kanai, S.; Gajek, M.; Worledge, D.C.; Matsukura, F.; Ohno, H. Electric field-induced ferromagnetic resonance in a CoFeB/MgO magnetic tunnel junction under dc bias voltages. Appl. Phys. Lett. 2014, 105, 242409. [Google Scholar] [CrossRef]

- Okada, A.; Kanai, S.; Yamanouchi, M.; Ikeda, S.; Matsukura, F.; Ohno, H. Electric-field effects on magnetic anisotropy and damping constant in Ta/CoFeB/MgO investigated by ferromagnetic resonance. Appl. Phys. Lett. 2014, 105, 052415. [Google Scholar] [CrossRef]

- Ando, F.; Kakizakai, H.; Koyama, T.; Yamada, K.; Kawaguchi, M.; Kim, S.; Kim, K.J.; Moriyama, T.; Chiba, D.; Ono, T. Modulation of the magnetic domain size induced by an electric field. Appl. Phys. Lett. 2016, 109, 022401. [Google Scholar] [CrossRef]

- Dohi, T.; Kanai, S.; Okada, A.; Matsukura, F.; Ohno, H. Effect of electric-field modulation of magnetic parameters on domain structure in MgO/CoFeB. AIP Adv. 2016, 6, 075017. [Google Scholar] [CrossRef]

- Dohi, T.; Kanai, S.; Matsukura, F.; Ohno, H. Electric-field effect on spin-wave resonance in a nanoscale CoFeB/MgO magnetic tunnel junction. Appl. Phys. Lett. 2017, 111, 072403. [Google Scholar] [CrossRef]

- Kanai, S.; Matsukura, F.; Ohno, H. Electric-field-induced magnetization switching in CoFeB/MgO magnetic tunnel junctions. Jpn. J. Appl. Phys. 2017, 56, 0802A0803. [Google Scholar] [CrossRef]

- Duan, C.G.; Velev, J.P.; Sabirianov, R.F.; Zhu, Z.; Chu, J.; Jaswal, S.S.; Tsymbal, E.Y. Surface magnetoelectric effect in ferromagnetic metal films. Phys. Rev. Lett. 2008, 101, 137201. [Google Scholar] [CrossRef] [PubMed]

- Skowroński, W.; Nozaki, T.; Lam, D.D.; Shiota, Y.; Yakushiji, K.; Kubota, H.; Fukushima, A.; Yuasa, S.; Suzuki, Y. Underlayer material influence on electric-field controlled perpendicular magnetic anisotropy in CoFeB/MgO magnetic tunnel junctions. Phys. Rev. B 2015, 91, 184410. [Google Scholar] [CrossRef]

- Nozaki, T.; Kozioł-Rachwał, A.; Skowroński, W.; Zayets, V.; Shiota, Y.; Tamaru, S.; Kubota, H.; Fukushima, A.; Yuasa, S.; Suzuki, Y. Large Voltage-Induced Changes in the Perpendicular Magnetic Anisotropy of an MgO-Based Tunnel Junction with an Ultrathin Fe Layer. Phys. Rev. Appl. 2016, 5, 044006. [Google Scholar] [CrossRef]

- Nozaki, T.; Kozioł-Rachwał, A.; Tsujikawa, M.; Shiota, Y.; Xu, X.; Ohkubo, T.; Tsukahara, T.; Miwa, S.; Suzuki, M.; Tamaru, S.; et al. Highly efficient voltage control of spin and enhanced interfacial perpendicular magnetic anisotropy in iridium-doped Fe/MgO magnetic tunnel junctions. NPG Asia Mater. 2017, 9, e451. [Google Scholar] [CrossRef]

- Xiang, Q.; Wen, Z.; Sukegawa, H.; Kasai, S.; Seki, T.; Kubota, T.; Takanashi, K.; Mitani, S. Nonlinear electric field effect on perpendicular magnetic anisotropy in Fe/MgO interfaces. J. Phys. D Appl. Phys. 2017, 50, 40LT04. [Google Scholar] [CrossRef]

- Nozaki, T.; Yamamoto, T.; Tamaru, S.; Kubota, H.; Fukushima, A.; Suzuki, Y.; Yuasa, S. Enhancement in the interfacial perpendicular magnetic anisotropy and the voltage-controlled magnetic anisotropy by heavy metal doping at the Fe/MgO interface. APL Mater. 2018, 6, 026101. [Google Scholar] [CrossRef]

- Kanai, S.; Nakatani, Y.; Yamanouchi, M.; Ikeda, S.; Sato, H.; Matsukura, F.; Ohno, H. Magnetization switching in a CoFeB/MgO magnetic tunnel junction by combining spin-transfer torque and electric field-effect. Appl. Phys. Lett. 2014, 104, 212406. [Google Scholar] [CrossRef]

- Yoda, H.; Shimomura, N.; Ohsawa, Y.; Shioiri, S.; Kato, Y.; Inokuchi, T.; Kamiguchi, Y.; Altansargai, B.; Saito, Y.; Koi, K.; et al. Voltage-Control Spintronics Memory (VoCSM) Having Potentials of Ultra-Low Energy-Consumption and High-Density. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar]

| SRAM | STT-MRAM for SRAM | eFlash | STT-MRAM for eFlash | SOT-MRAM | VC-MRAM | |

|---|---|---|---|---|---|---|

| Cell size | 160–200 F2 | 70–100 F2 | 40 F2 | 50–60 F2 | 160 F2 | 50–60 F2 |

| Operation voltage (V) | 0.6–1.2 | 0.6 | ≥10 | 0.6 | 0.6 | 2.2 |

| Write current (A) | 10−5 | 10−5 | 10−5 | 10−5 | 10−4 | 10−5 |

| R/W time (ns) | ≤2/≤2 | 5/10 | 10/20,000 | 25/200 | 5/≤2 | 10/≤2 |

| Retention | Volatile | 1 month | >20 years | 15 years | ≤10 years | 1 month |

| Endurance (cycles) | 1016 | 1014 | 105 | 108 | 1014 | - |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Endoh, T.; Honjo, H. A Recent Progress of Spintronics Devices for Integrated Circuit Applications. J. Low Power Electron. Appl. 2018, 8, 44. https://doi.org/10.3390/jlpea8040044

Endoh T, Honjo H. A Recent Progress of Spintronics Devices for Integrated Circuit Applications. Journal of Low Power Electronics and Applications. 2018; 8(4):44. https://doi.org/10.3390/jlpea8040044

Chicago/Turabian StyleEndoh, Tetsuo, and Hiroaki Honjo. 2018. "A Recent Progress of Spintronics Devices for Integrated Circuit Applications" Journal of Low Power Electronics and Applications 8, no. 4: 44. https://doi.org/10.3390/jlpea8040044

APA StyleEndoh, T., & Honjo, H. (2018). A Recent Progress of Spintronics Devices for Integrated Circuit Applications. Journal of Low Power Electronics and Applications, 8(4), 44. https://doi.org/10.3390/jlpea8040044