An Ultra-Low Power 28 nm FD-SOI Low Noise Amplifier Based on Channel Aware Receiver System Analysis

Abstract

:1. Introduction

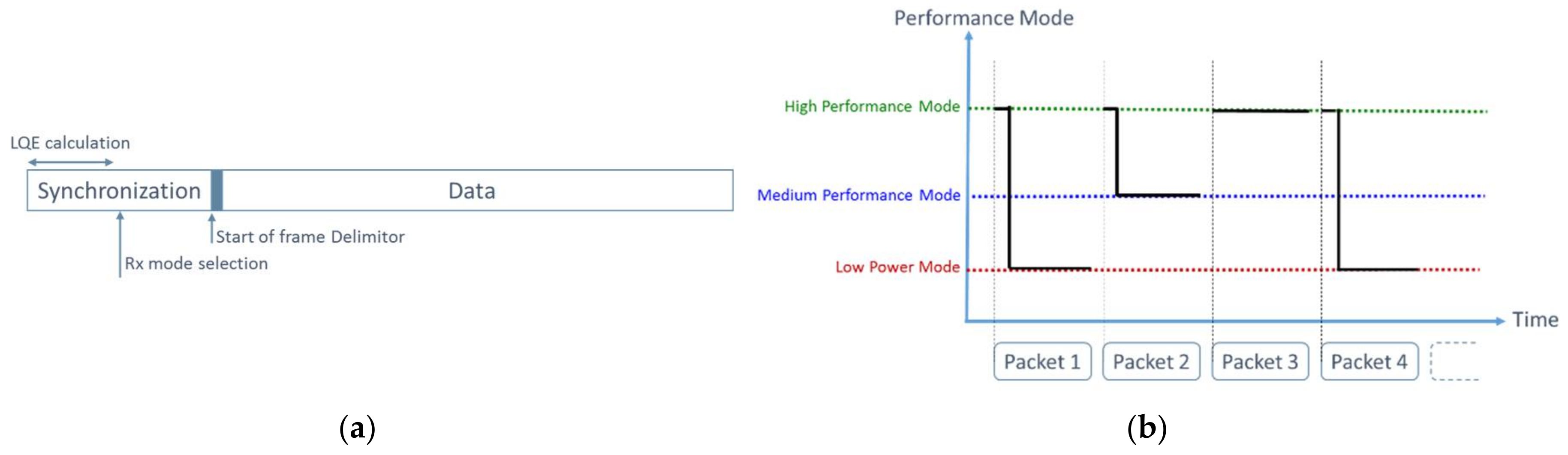

2. Adaptive Receivers for IoT Applications

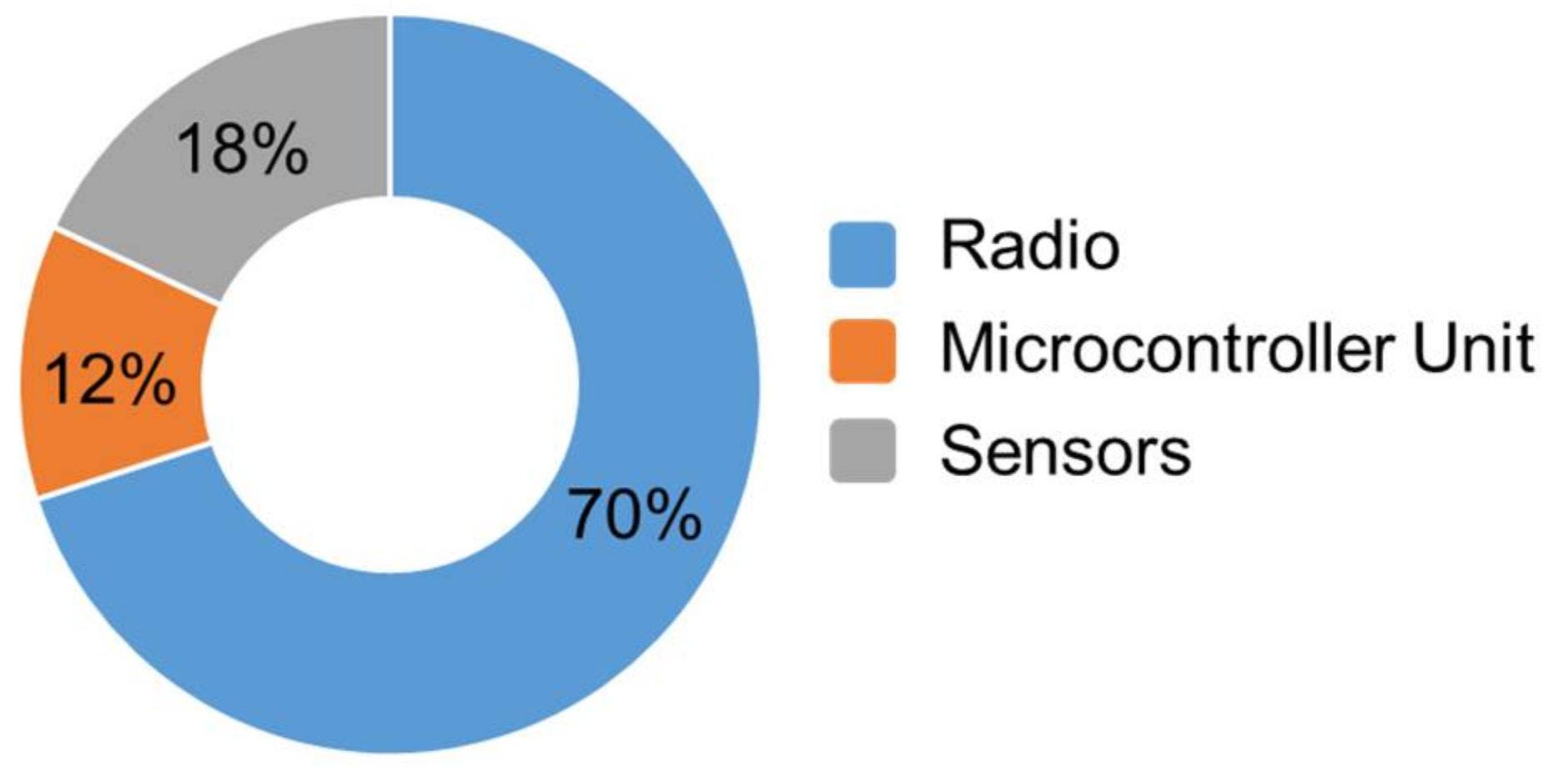

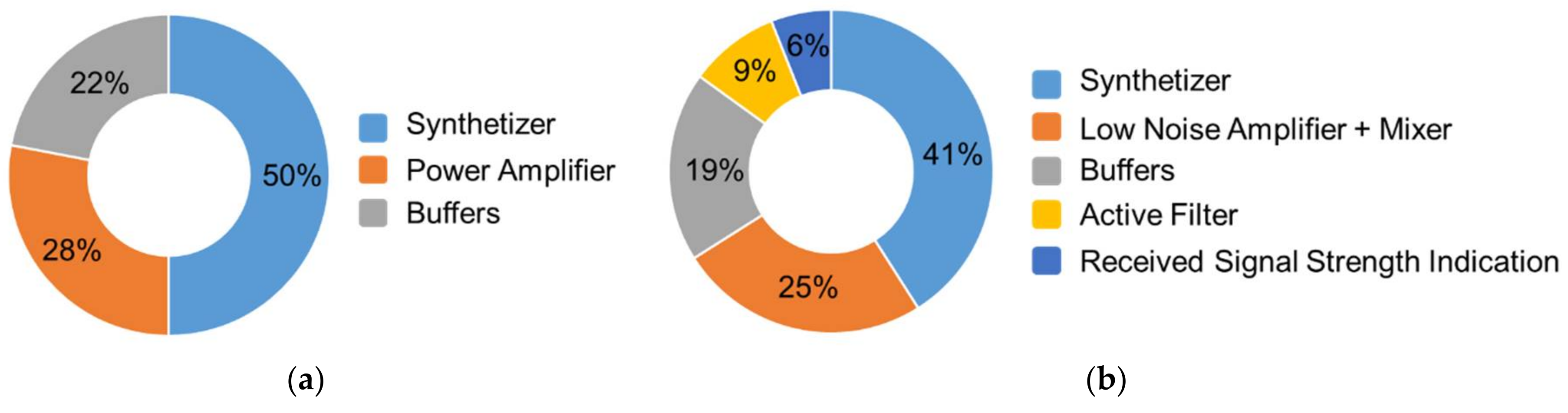

2.1. Motivation

2.2. State of the Art Adaptive Receiver

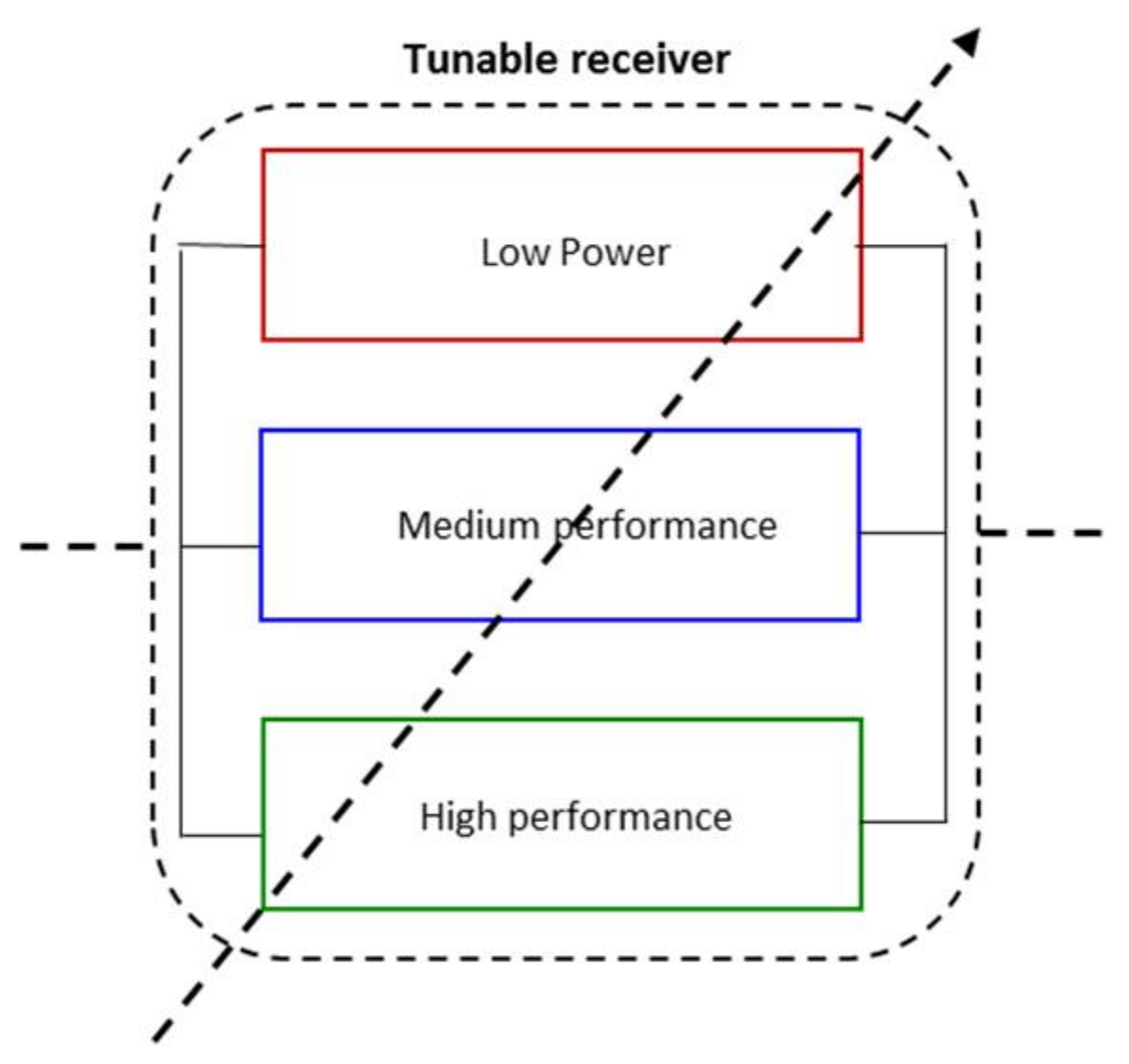

2.3. Proposed Approach

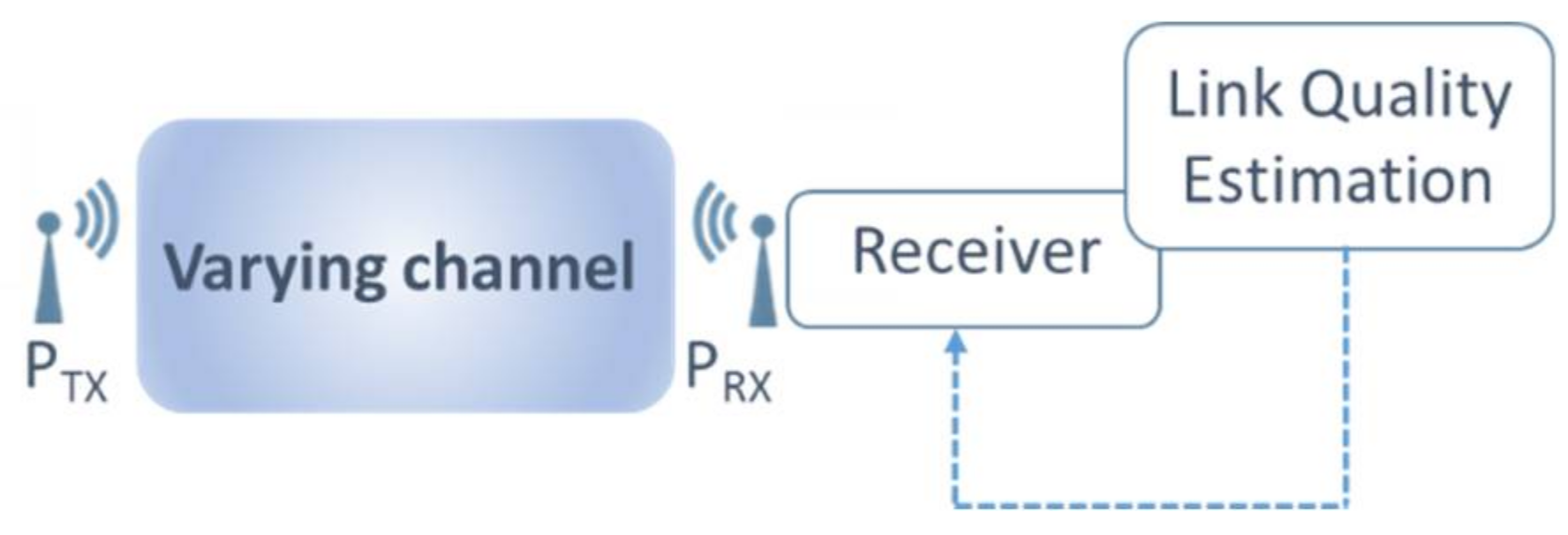

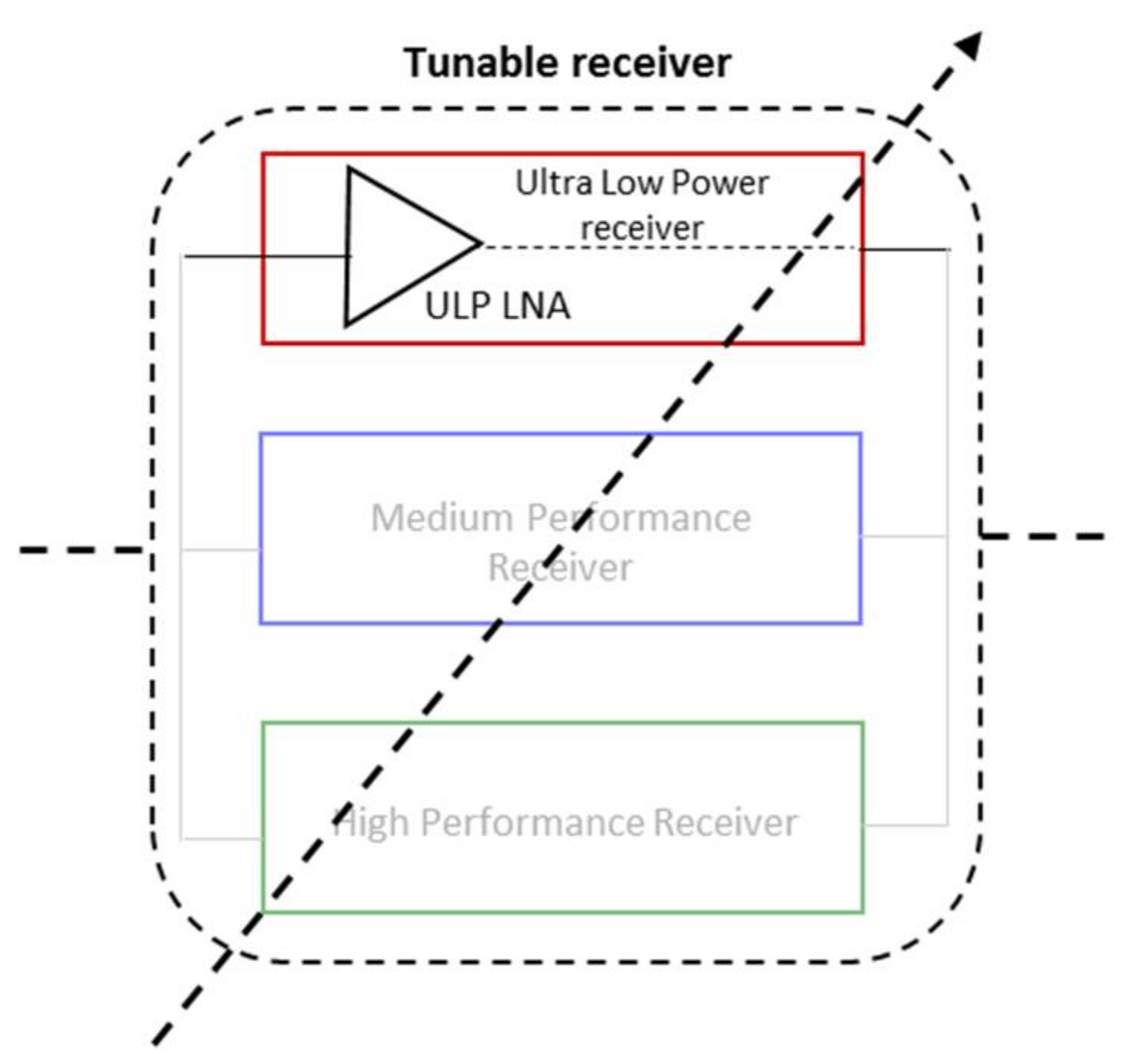

3. Proposed Channel Aware Receiver

3.1. Context of Application

- -

- IEEE 802.15.4 ZigBee standard addressed (ISM Worldwide band at 2.4 GHz);

- -

- Indoor propagation channels without the presence of adjacent blocker;

- -

- Peer-to-peer network arrangements;

- -

- Random and uniform nodes locations distribution in the area;

- -

- Nodes communicate with their nearest neighbor(s);

- -

- Signal suffering from average path-loss attenuation only.

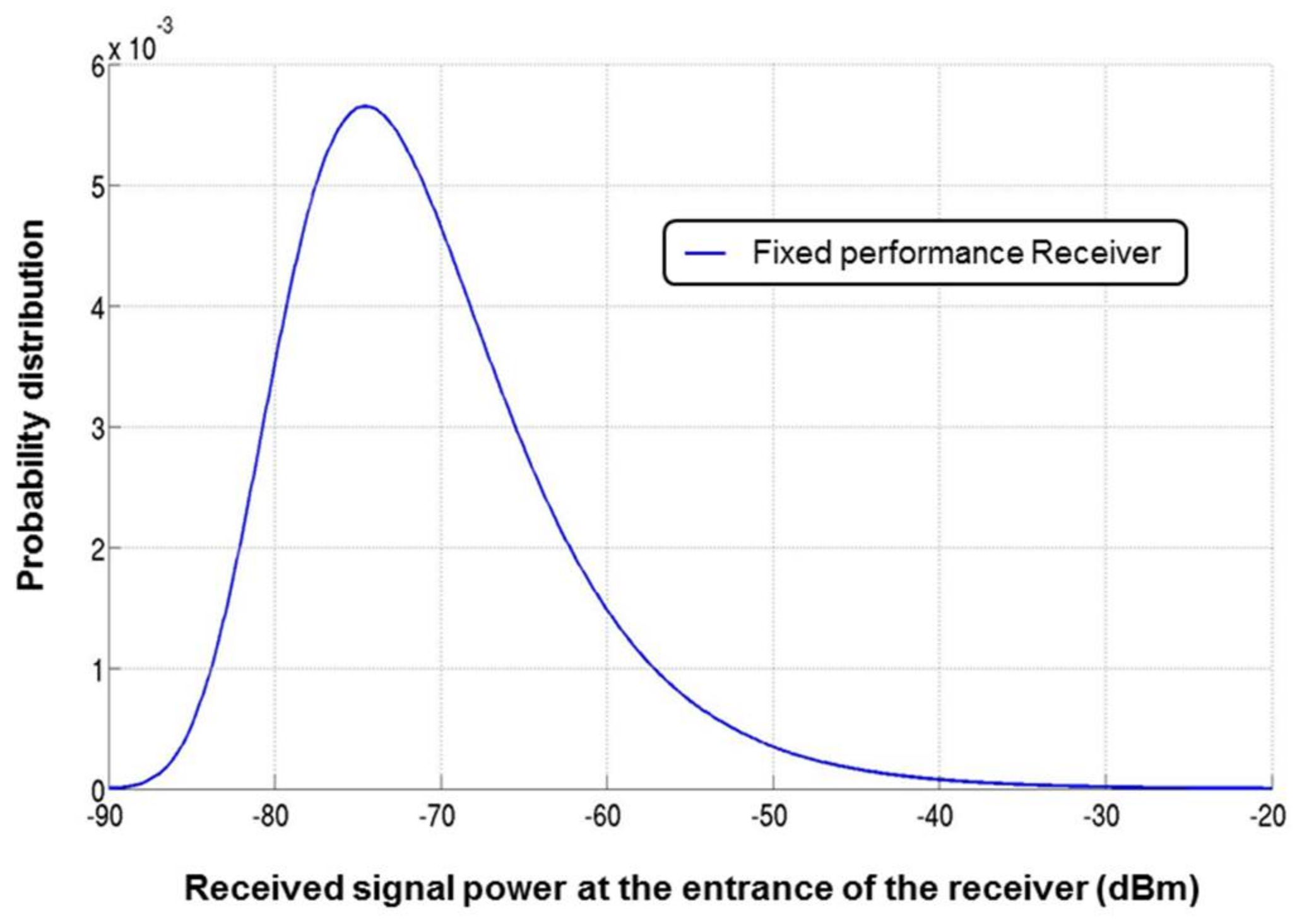

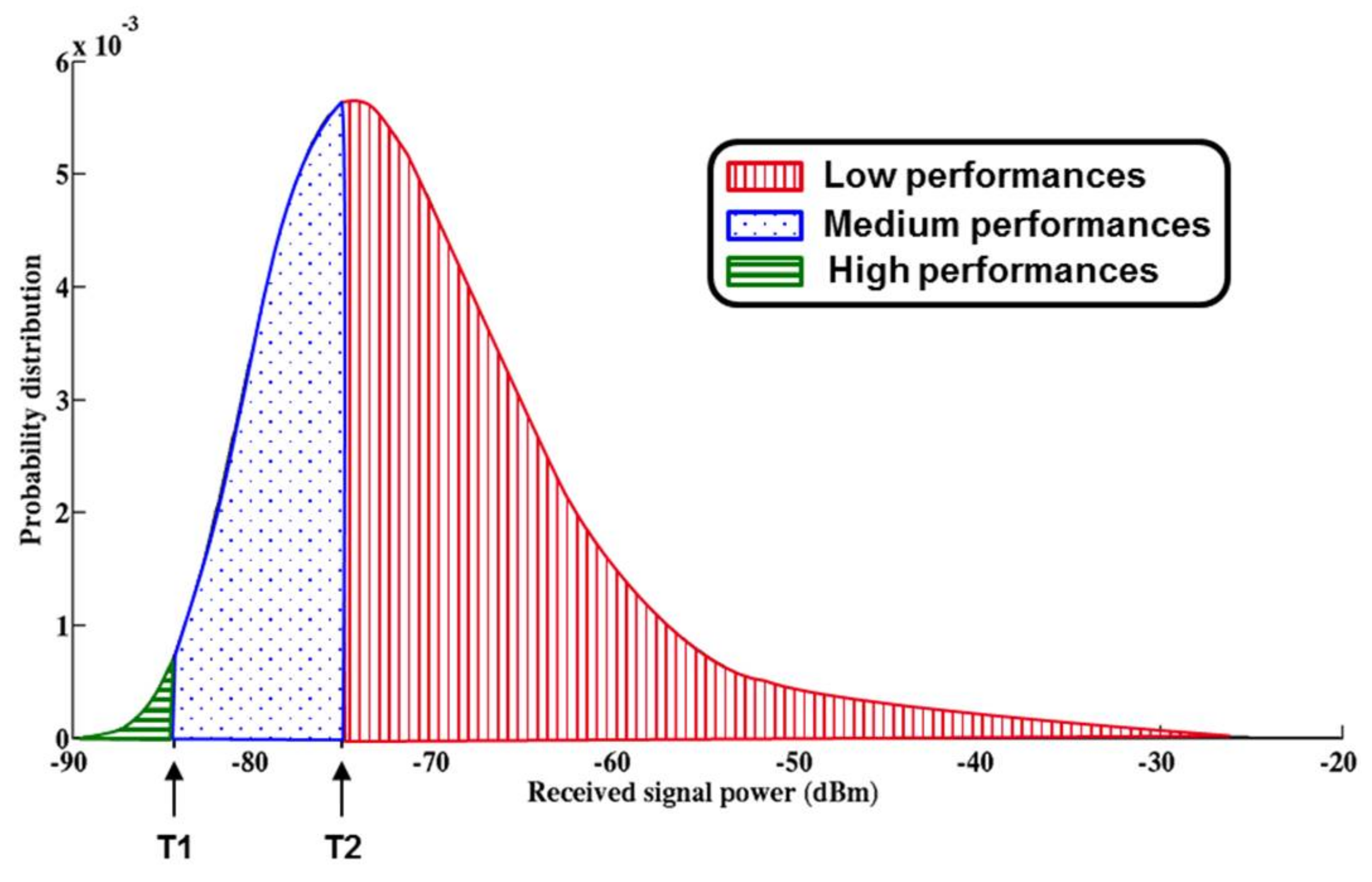

3.2. Probability Distribution of the Received Power

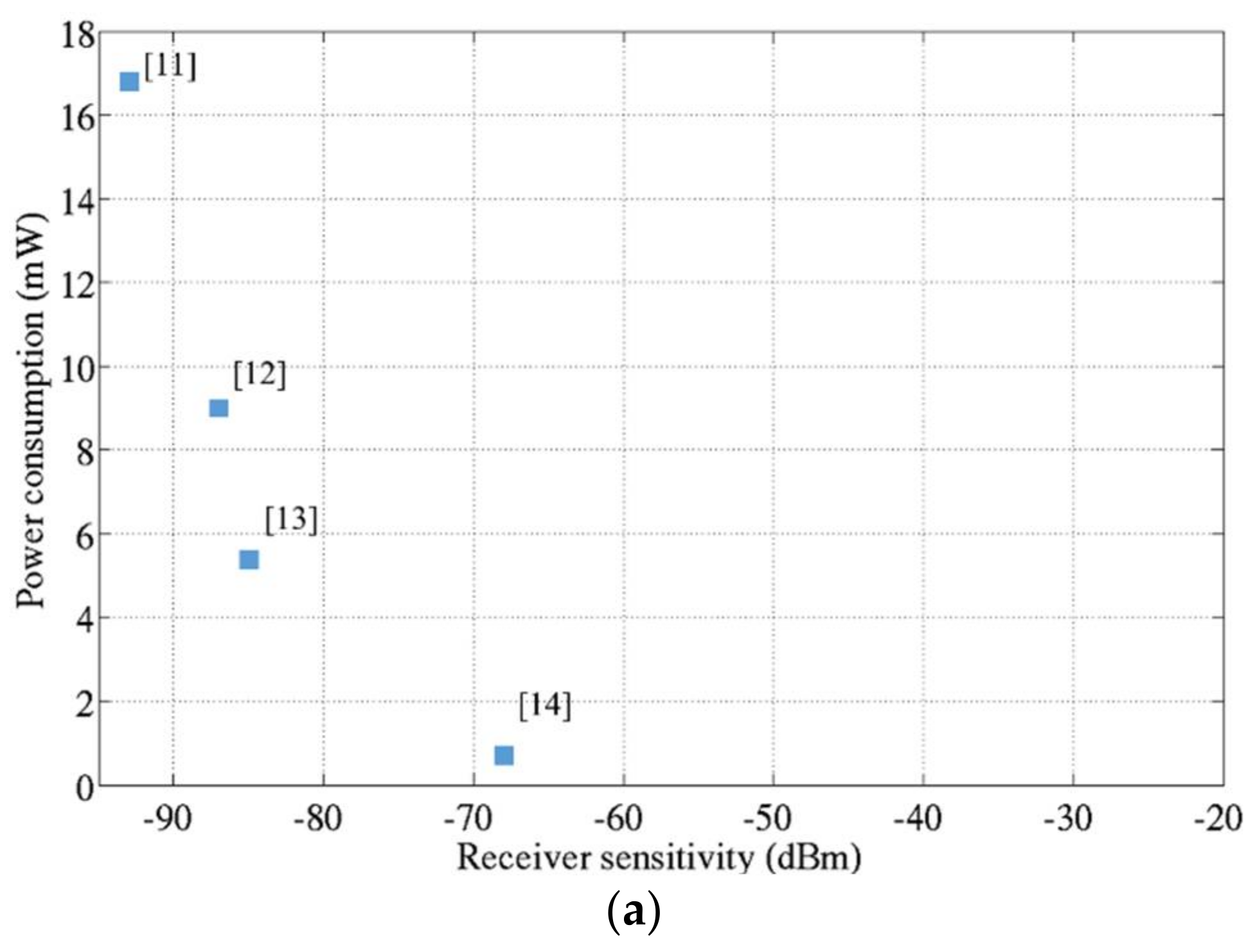

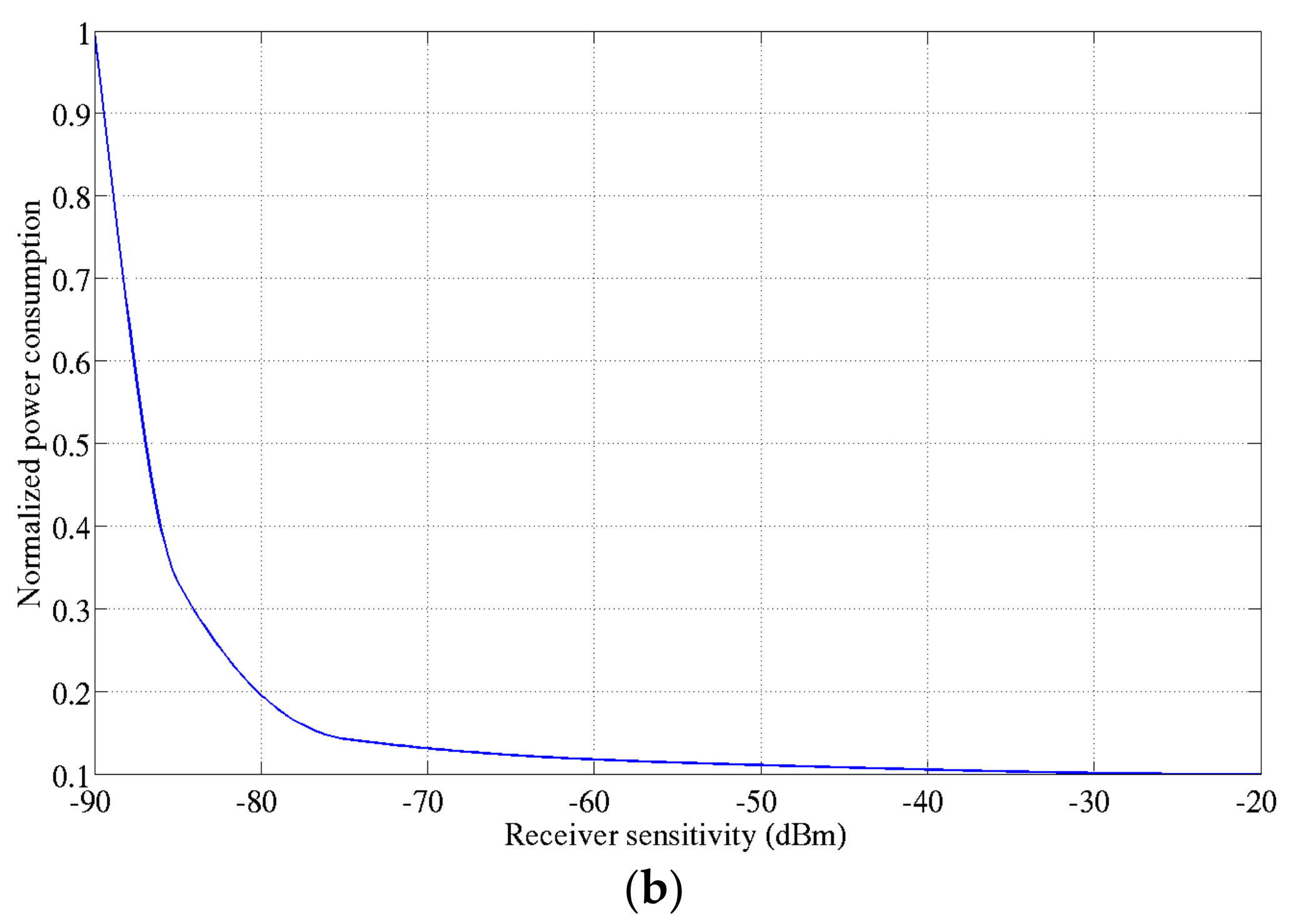

3.3. Approximation of the Sensitivity and Power Consumption of the Receiver

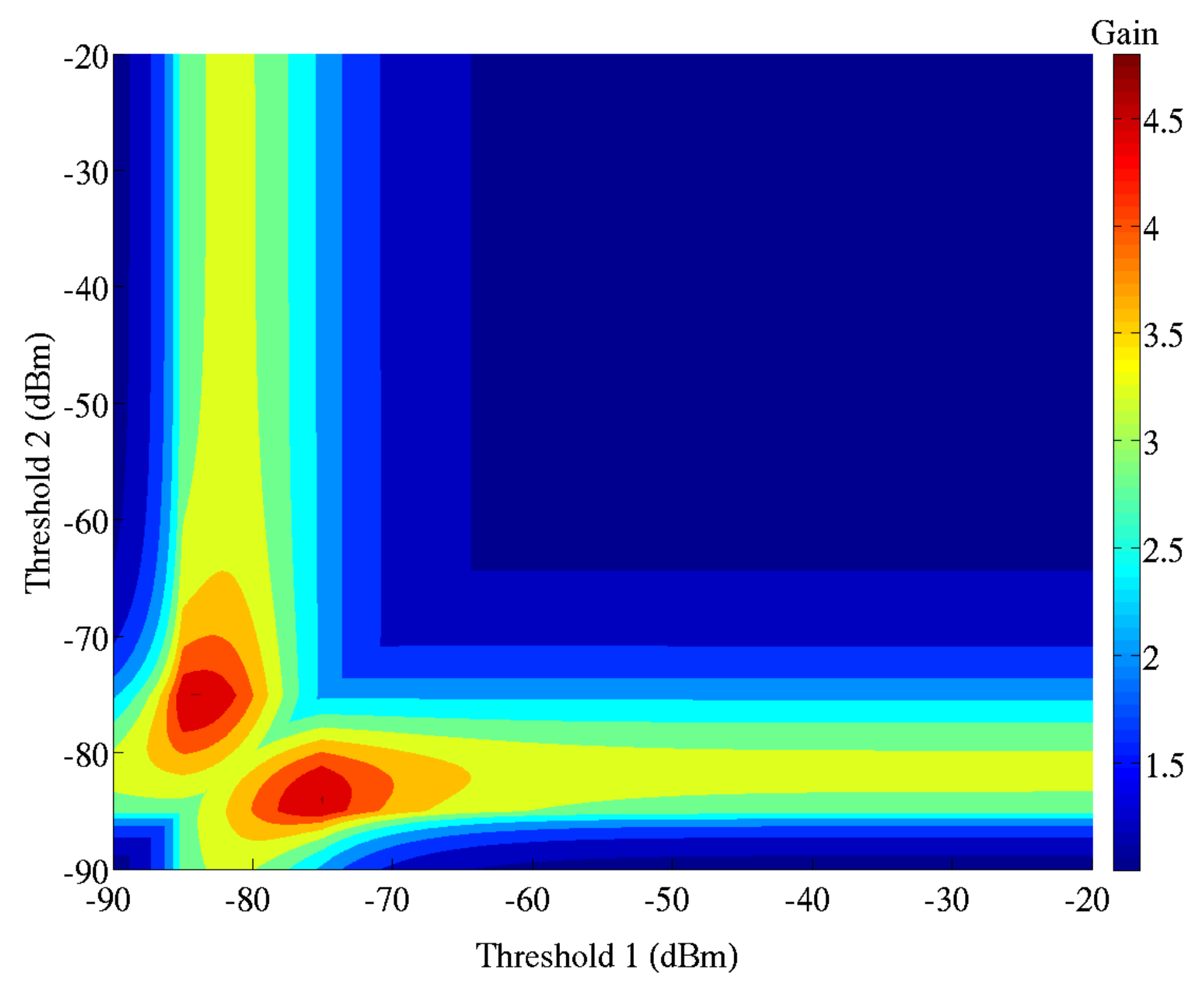

3.4. Optimized Reconfiguration Thresholds

- -

- The low performance mode has to be designed with a power consumption of 2.2 mW. It will be on this state for 76% of its lifetime.

- -

- The medium mode has to be designed with a 5.8 mW of power consumption it will be active for 23% of its lifetime.

- -

- The highest mode is the worst case design, essential to guarantee the QoS but active only 1% of the receiver’s lifetime.

3.5. Design Specifications

4. FD-SOI ULP LNA Design for IoT Applications

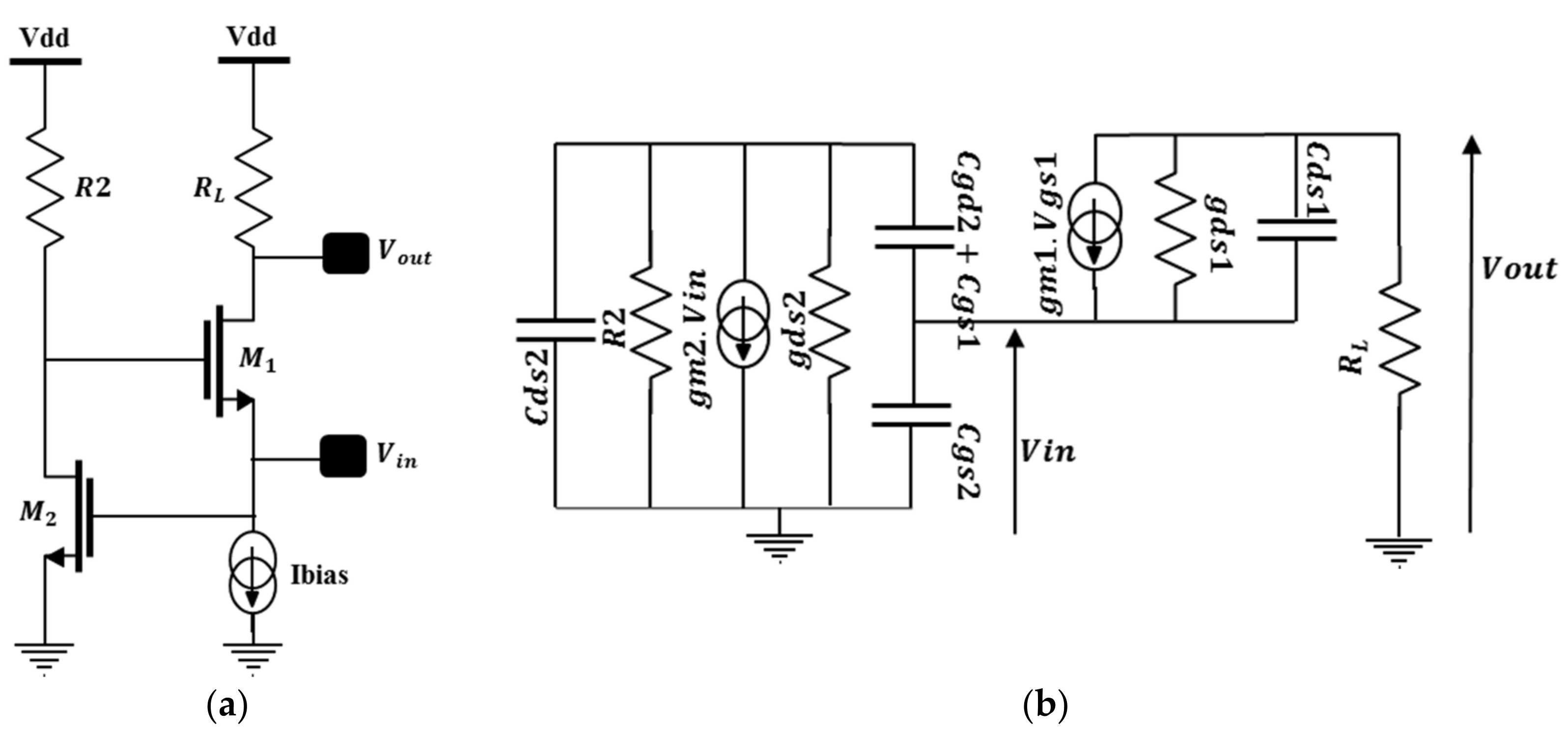

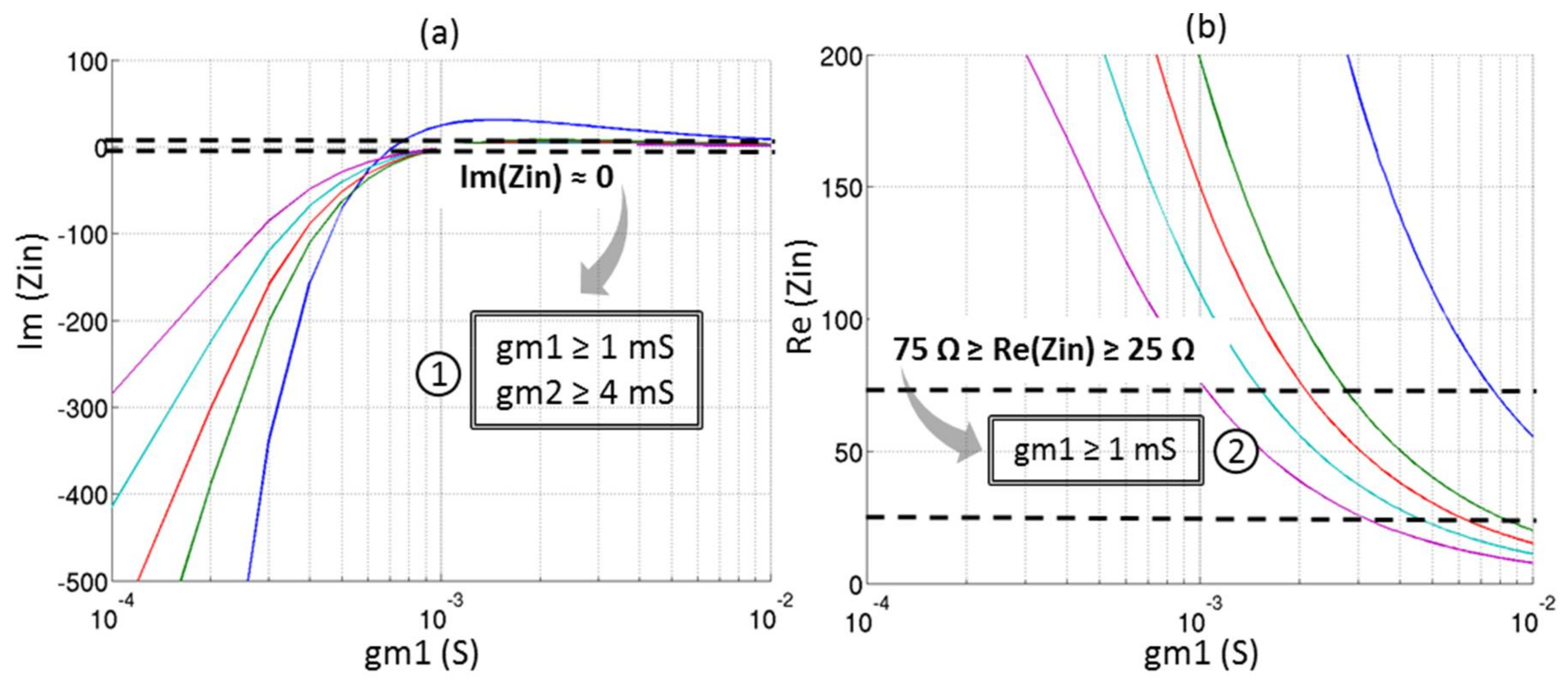

4.1. LNA Topology

- -

- gm1 = 2.5 mS;

- -

- gm2 = 5 mS.

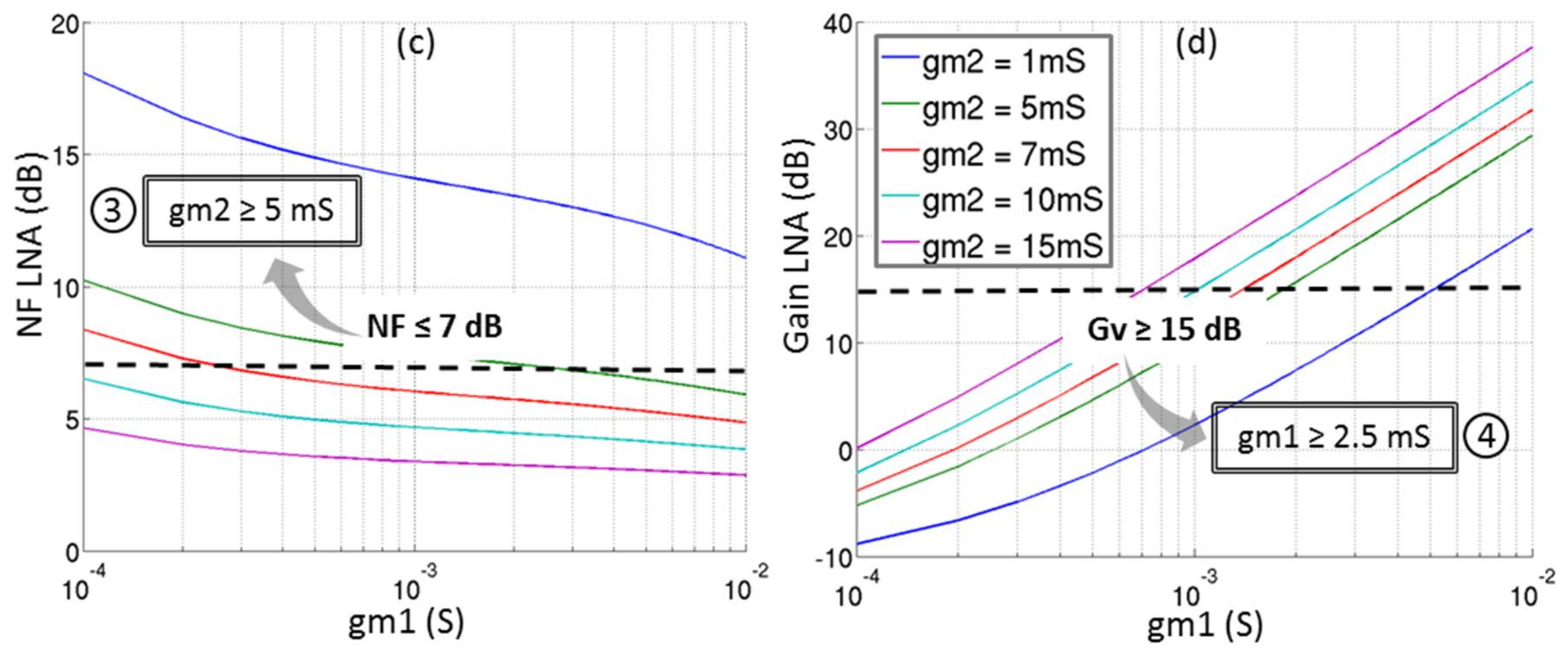

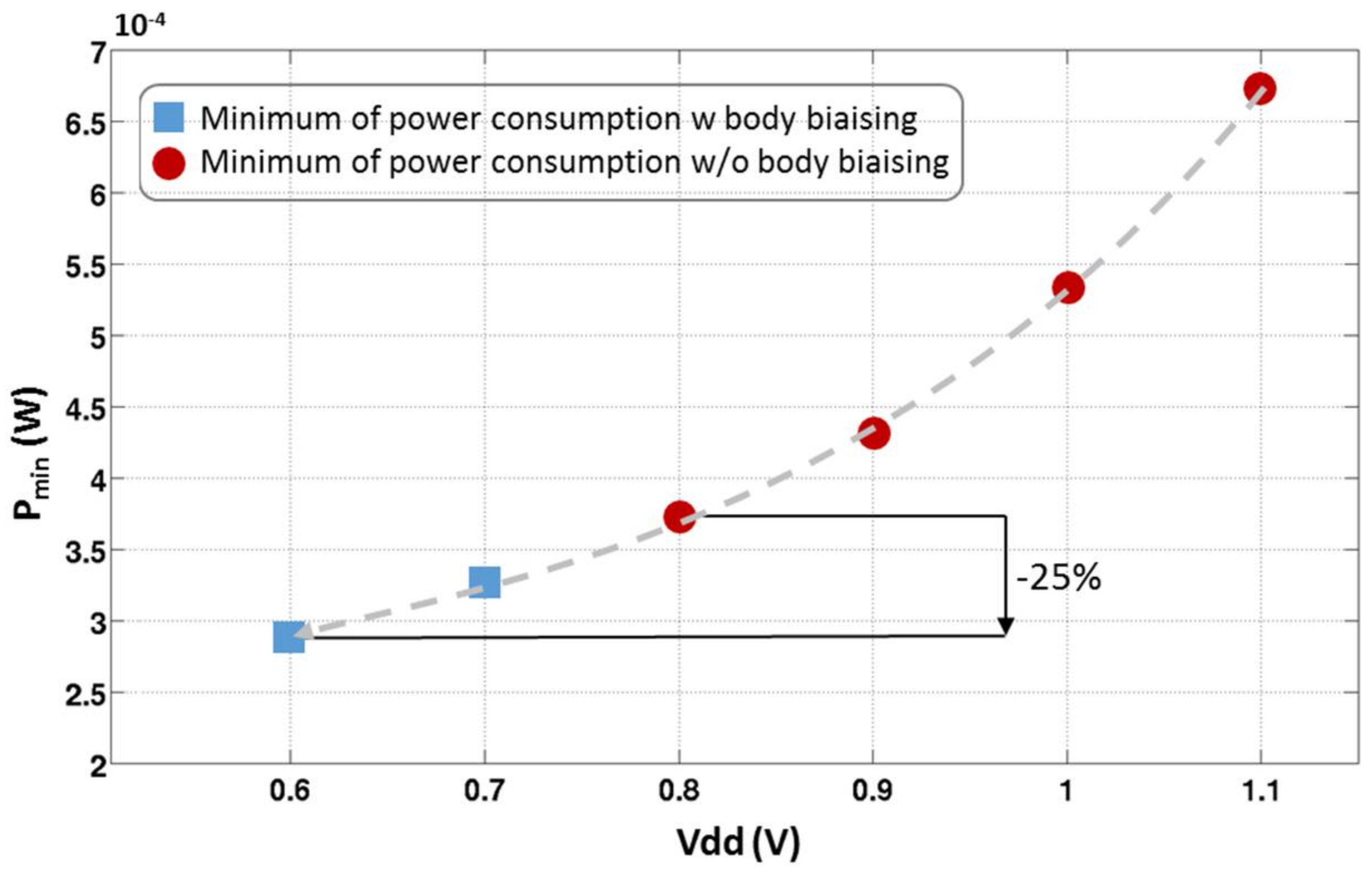

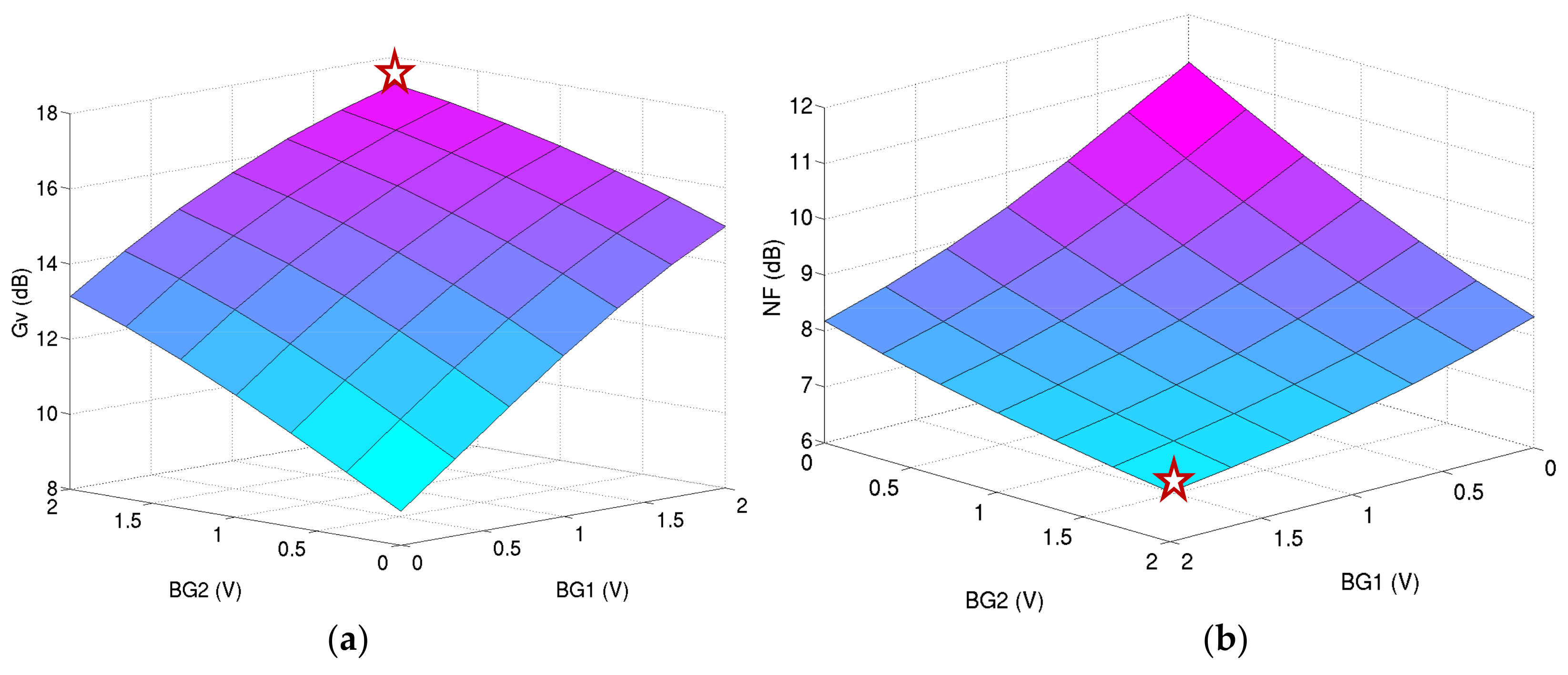

4.2. Body Biasing

- -

- Vgs ≥ Vt;

- -

- Vds ≥ Vgs−Vt.

- -

- BG1 = 2 V;

- -

- BG2 = 2 V; and

- -

- Vdd = 0.6 V.

- -

- S11 = −10.5 dB;

- -

- Gv = 17.5 dB;

- -

- NF = 6.9 dB; and

- -

- Pdc = 300 µW.

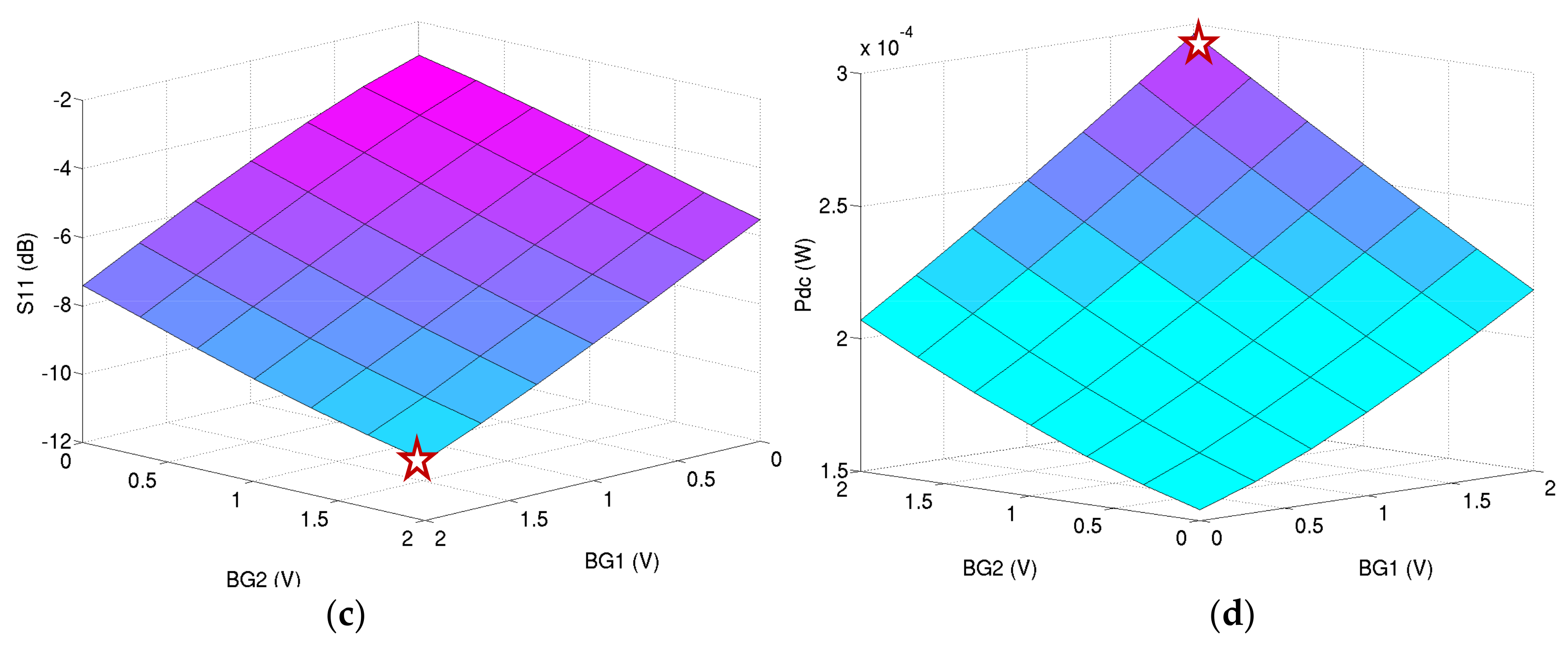

4.3. PVT Degradation Evaluation

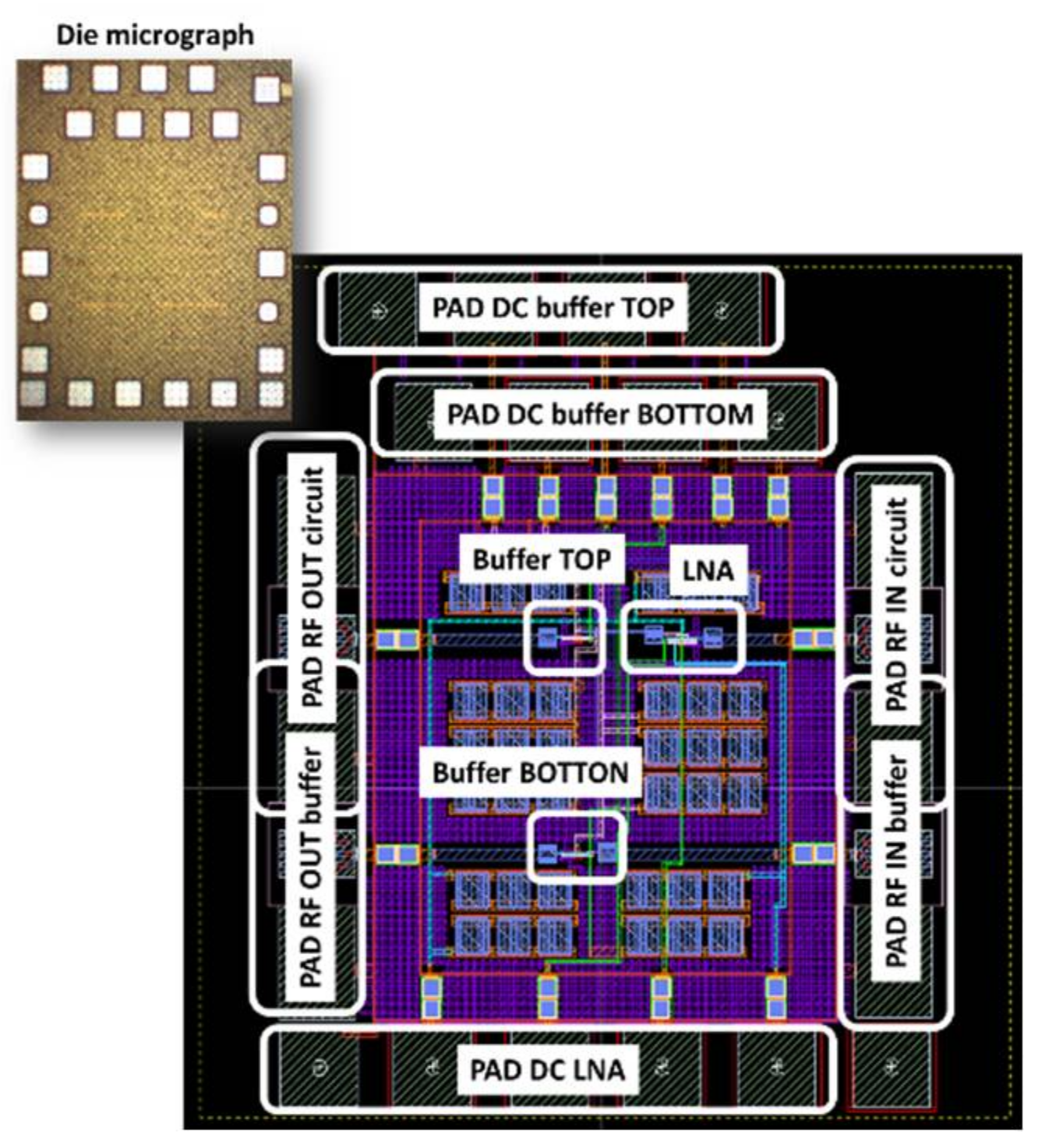

5. Integrated Circuit (IC) Implementation and Measurement Results

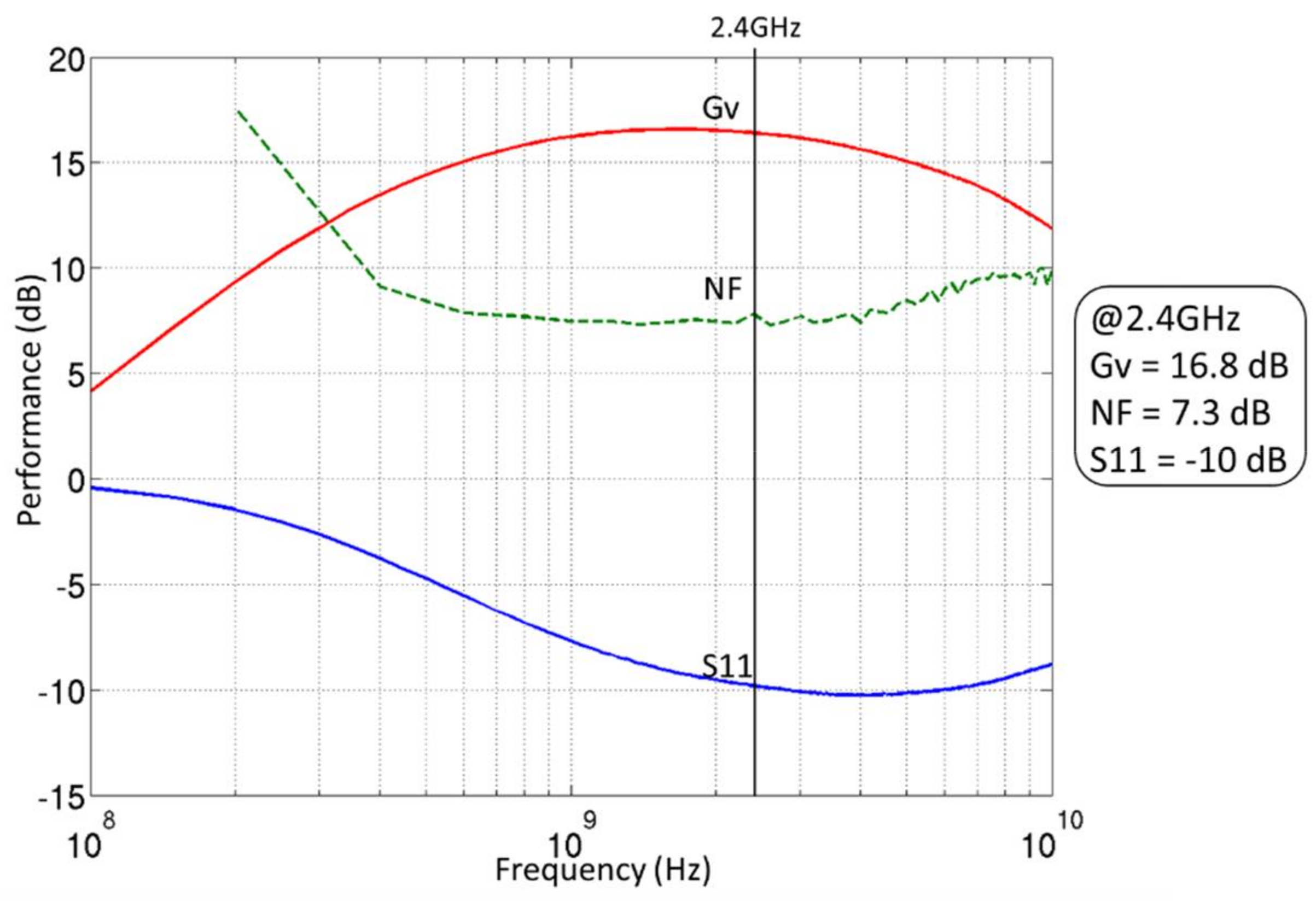

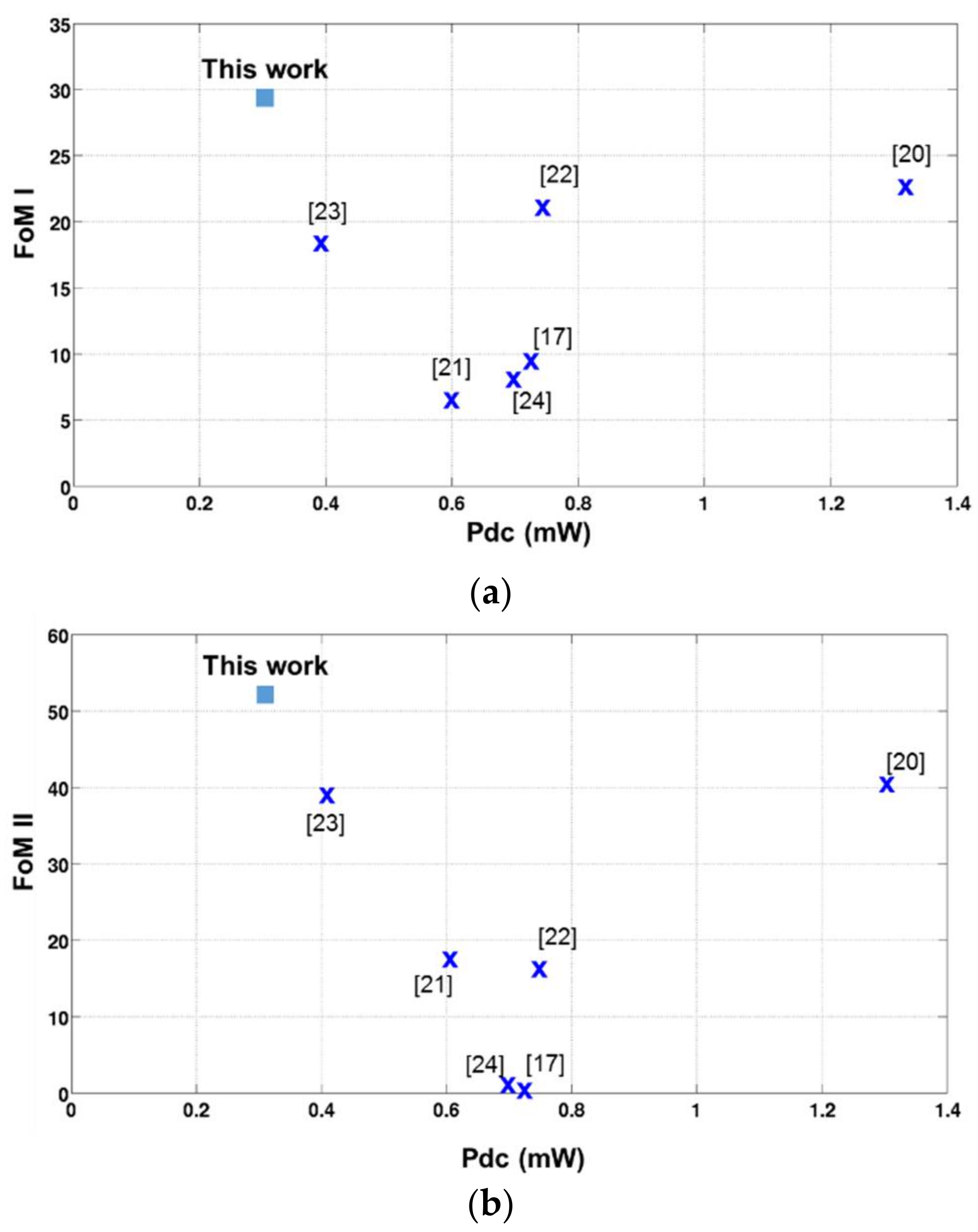

5.1. ULP LNA Mesurement Results

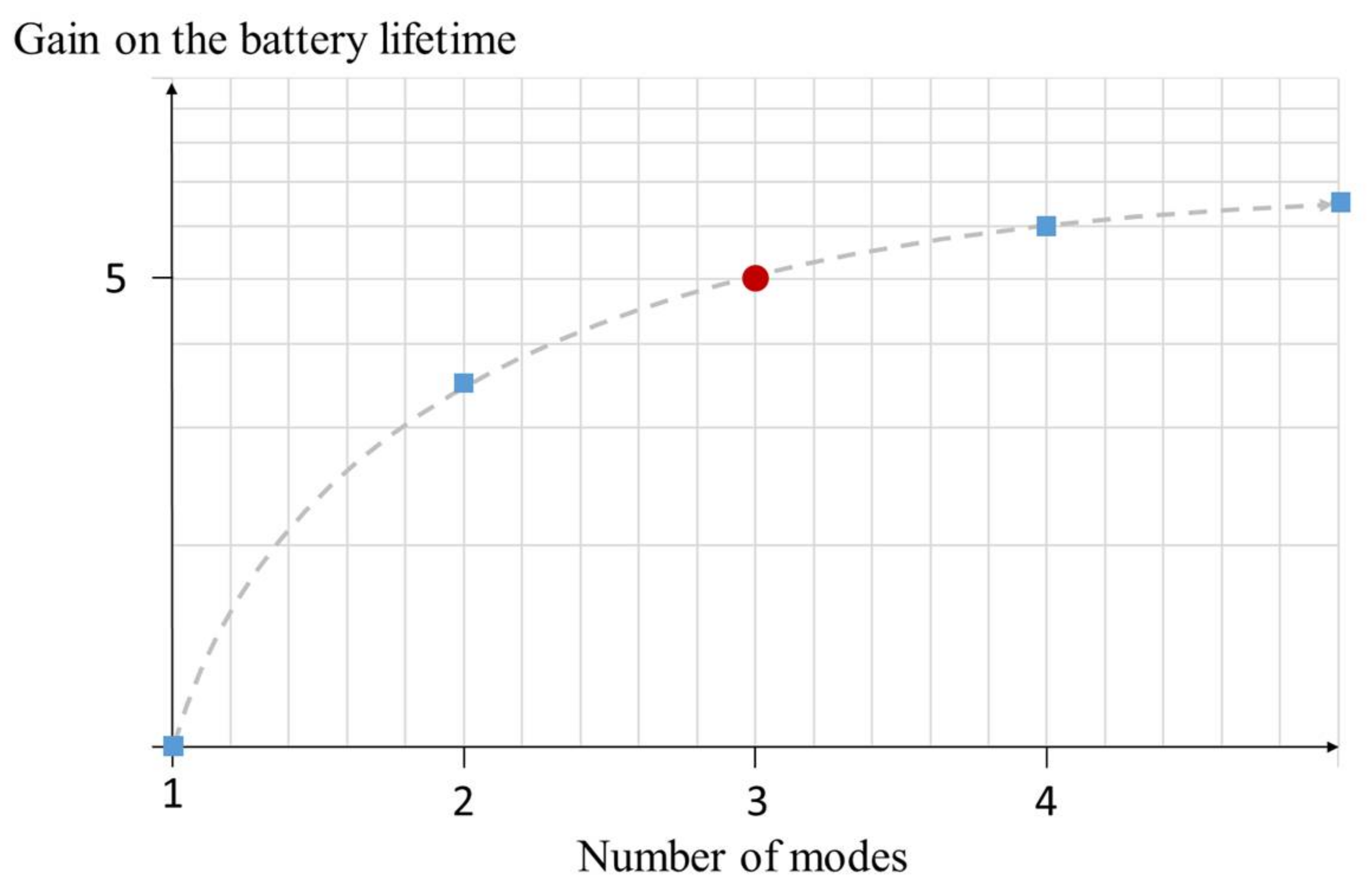

5.2. Gain on the Battery Lifetime with the Proposed LNA

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Take the World with You. Available online: https://www.ericsson.com/assets/local/investors/documents/financial-reports-and-filings/annual-reports/ericsson_ar_2010_en.pdf (accessed on 13 December 2017).

- Bachir, A.; Dohler, M.; Watteyne, T.; Leung, K.K. MAC Essentials for Wireless Sensor Networks. IEEE Commun. Surv. Tutor. 2010, 12, 222–248. [Google Scholar] [CrossRef]

- Raja, M.K.; Chen, X.; Lei, Y.D.; Bin, Z.; Yeung, B.C.; Xiaojun, Y. A 18 mW Tx, 22 mW Rx transceiver for 2.45 GHz IEEE 802.15.4 WPAN in 0.18-µm CMOS. In Proceedings of the 2010 IEEE Asian Solid State Circuits Conference (A-SSCC), Beijing, China, 8–10 November 2010; pp. 1–4. [Google Scholar]

- Pletcher, N.M.; Gambini, S.; Rabaey, J. A 52 µW Wake-Up Receiver with −72 dBm Sensitivity Using an Uncertain-IF Architecture. IEEE J. Solid State Circuits 2009, 44, 269–280. [Google Scholar] [CrossRef]

- Lanzisera, S.; Mehta, A.M.; Pister, K.S.J. Reducing Average Power in Wireless Sensor Networks through Data Rate Adaptation. In Proceedings of the 2009 IEEE International Conference on Communications, Dresden, Germany, 14–18 June 2009; pp. 1–6. [Google Scholar]

- Dwivedi, S.; Amrutur, B.; Bhat, N. Power Scalable Radio Receiver Design Based on Signal and Interference Condition. J. Low Power Electron. Appl. 2012, 2, 242–264. [Google Scholar] [CrossRef]

- Oguz, A.; Morche, D.; Dehollaini, C. Adaptive power reconfigurability for decreasing power dissipation of wireless personal area network receivers. In Proceedings of the 2011 IEEE International Symposium on Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 1900–1903. [Google Scholar]

- Lolis, L.; de Souza, M.; Zambon, L.B.; Mariano, A. Impact of a fully reconfigurable LNA on an RF front-end: A system level analysis. In Proceedings of the 2014 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS), Marseille, France, 7–10 December 2014; pp. 662–665. [Google Scholar]

- Banerjee, D.; Muldrey, B.; Wang, X.; Sen, S.; Chatterjee, A. Self-Learning RF Receiver Systems: Process Aware Real-Time Adaptation to Channel Conditions for Low Power Operation. IEEE Trans. Circuits Syst. Regul. Pap. 2017, 64, 195–207. [Google Scholar] [CrossRef]

- Zaini, J.; Hameau, F.; Taris, T.; Morche, D.; Tran, L.Q.V.; Audebert, P. Channel aware receiver front end for low power 2.4 GHz Wireless Sensor Network: A system level analysis. In Proceedings of the 2016 14th IEEE International New Circuits and Systems Conference (NEWCAS), Vancouver, BC, Canada, 26–29 June 2016; pp. 1–4. [Google Scholar]

- Retz, G.; Shanan, H.; Mulvaney, K.; O’Mahony, S.; Chanca, M.; Crowley, P.; Billon, C.; Khan, K.; Quinlan, P. A highly integrated low-power 2.4 GHz transceiver using a direct-conversion diversity receiver in 0.18 µm CMOS for IEEE802.15.4 WPAN. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, ISSCC 2009, San Francisco, CA, USA, 8–12 February 2009; pp. 414–415. [Google Scholar]

- Kwon, Y.-I.; Park, T.J.; Cho, K.-S.; Lee, H.-Y. A 9 mW Highly-Digitized 802.15.4 Receiver Using Bandpass ADC and IF Level Detection. IEEE Microw. Wirel. Compon. Lett. 2008, 18, 824–826. [Google Scholar] [CrossRef]

- Camus, M.; Butaye, B.; Garcia, L.; Sie, M.; Pellat, B.; Parra, T. A 5.4 mW 0.07 mm2 2.4 GHz Front-End Receiver in 90 nm CMOS for IEEE 802.15.4 WPAN. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, ISSCC 2008, San Francisco, CA, USA, 3–7 February 2008; pp. 368–620. [Google Scholar]

- Perumana, B.G.; Mukhopadhyay, R.; Chakraborty, S.; Lee, C.-H.; Laskar, J. A Low-Power Fully Monolithic Subthreshold CMOS Receiver with Integrated LO Generation for 2.4 GHz Wireless PAN Applications. IEEE J. Solid State Circuits 2008, 43, 2229–2238. [Google Scholar] [CrossRef]

- Lont, M.; Milosevic, D.; Dolmans, G.; van Roermund, A.H.M. Mixer-First FSK Receiver with Automatic Frequency Control for Body Area Networks. IEEE Trans. Circuits Syst. Regul. Pap. 2013, 60, 2051–2063. [Google Scholar] [CrossRef]

- Elwan, H.; Tekin, A.; Pedrotti, K. A Differential-Ramp Based 65 dB-Linear VGA Technique in 65 nm CMOS. IEEE J. Solid State Circuits 2009, 44, 2503–2514. [Google Scholar] [CrossRef]

- Wang, S.B.T.; Niknejad, A.M.; Brodersen, R.W. Design of a Sub-mW 960-MHz UWB CMOS LNA. IEEE J. Solid State Circuits 2006, 41, 2449–2456. [Google Scholar] [CrossRef]

- Belmas, F.; Hameau, F.; Fournier, J. A Low Power Inductorless LNA with Double Enhancement in 130 nm CMOS. IEEE J. Solid State Circuits 2012, 47, 1094–1103. [Google Scholar] [CrossRef]

- Kim, J.; Hoyos, S.; Silva-Martinez, J. Wideband Common-Gate CMOS LNA Employing Dual Negative Feedback with Simultaneous Noise, Gain, and Bandwidth Optimization. IEEE Trans. Microw. Theory Tech. 2010, 58, 2340–2351. [Google Scholar] [CrossRef]

- Belmas, F.; Hameau, F.; Fournier, J. A 1.3 mW 20 dB gain low power inductorless LNA with 4 dB Noise Figure for 2.45 GHz ISM band. In Proceedings of the 2011 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Baltimore, Maryland, 5–7 June 2011; pp. 1–4. [Google Scholar]

- Li, Z.; Wang, Z.; Zhang, M.; Chen, L.; Wu, C.; Wang, Z. A 2.4 GHz Ultra-Low-Power Current-Reuse CG-LNA with Active-Boosting Technique. IEEE Microw. Wirel. Compon. Lett. 2014, 24, 348–350. [Google Scholar] [CrossRef]

- Parvizi, M.; Allidina, K.; El-Gamal, M.N. A Sub-mW, Ultra-Low-Voltage, Wideband Low-Noise Amplifier Design Technique. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2015, 23, 1111–1122. [Google Scholar] [CrossRef]

- Parvizi, M.; Allidina, K.; El-Gamal, M.N. An Ultra-Low-Power Wideband Inductorless CMOS LNA with Tunable Active Shunt-Feedback. IEEE Trans. Microw. Theory Tech. 2016, 64, 1843–1853. [Google Scholar] [CrossRef]

- Fiorelli, R.; Silveira, F.; Peralı, E. MOST Moderate—Weak-Inversion Region as the Optimum Design Zone for CMOS 2.4-GHz CS-LNAs. IEEE Trans. Microw. Theory Tech. 2014, 62, 556–566. [Google Scholar] [CrossRef]

| Modulation | Frequency | Channel Bandwidth | Data Rate | Number of Nodes | Signal to Noise Ratio (SNRmin) | Bit Error Rate (BER) | Packet Error Rate (PER) |

|---|---|---|---|---|---|---|---|

| OQPSK | 2.4 GHz (ISM) | 5 MHz | 250 kbits/s | 264 | 10 dB | 10−6 | 1% |

| Mode | Low Performance Mode | Medium Performance Mode | High Performance Mode |

|---|---|---|---|

| Sensitivity (dBm) | −75 | −85 | −90 |

| Usage time (%) | 76 | 23 | 1 |

| Power consumption (mW) | 2.2 | 5.8 | 10 |

| Mode | Low Performance Mode |

|---|---|

| Sensitivity (dBm) | −75 |

| Usage time (%) | 76 |

| NFRX (dB) | 22 |

| NFLNA (dB) | 7 |

| GvLNA (dB) | 15 |

| PdcRX (mW) | 2.2 |

| PdcLNA (mW) | 0.5 |

| Performance | 3-σ min | 3-σ max |

|---|---|---|

| NFLNA (dB) | 7.2 | 6.5 |

| GLNA (dB) | 16 | 18.8 |

| Sensitivity (dBm) | −75.3 | −76.8 |

| Ref. | Gv (dB) | 3 dB-BW (GHz) | NF (dB) | IIP3 (dBm) | Pdc (mW) | Supply (V) | Tech. | Area (mm2) | FoM 1 | FoM 2 |

|---|---|---|---|---|---|---|---|---|---|---|

| T.W. | 16.8 | 0.45–6 | 7.3 | −16 | 0.3 | 0.6 | FDSOI 28 nm | 0.0015 | 29.3 | 53.7 |

| [20] | 20 | 0.1–2.7 | 4 | −12 | 1.32 | 1.2 | CMOS 0.13 µm | 0.007 | 22.3 | 41.4 |

| [21] | 14.7 | 2.1–2.5 | 4.8 | 2 | 0.6 | 1.8 | CMOS 0.18 µm | 0.39 | 7 | 19.2 |

| [22] | 12.6 | 0.1–7 | 6.5 | −8 | 0.75 | 0.5 | CMOS 90 nm | 0.23 | 21.1 | 17.8 |

| [17] | 10.6 1 | 0.1–1 | 4 | −10.2 | 0.72 | 1.2 | CMOS 0.13 µm | 0.26 | 8.9 | 0.3 |

| [23] | 9.9 1 | 0.1–2.2 | 5.5 | −11.5 | 0.4 | 1 | CMOS 0.1 µm | 0.0052 | 16.7 | 39.4 |

| [24] | 9.7 | 2–2.8 | 4.4 | −4 | 0.7 | 1.2 | CMOS 90 nm | 0.91 | 7.9 | 0.8 |

| FoM LNA | Aimed: 23 | Measured: 29.3 |

|---|---|---|

| Gain on the battery lifetime | 5.1 | 6.7 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zaini-Desevedavy, J.; Hameau, F.; Taris, T.; Morche, D.; Audebert, P. An Ultra-Low Power 28 nm FD-SOI Low Noise Amplifier Based on Channel Aware Receiver System Analysis. J. Low Power Electron. Appl. 2018, 8, 10. https://doi.org/10.3390/jlpea8020010

Zaini-Desevedavy J, Hameau F, Taris T, Morche D, Audebert P. An Ultra-Low Power 28 nm FD-SOI Low Noise Amplifier Based on Channel Aware Receiver System Analysis. Journal of Low Power Electronics and Applications. 2018; 8(2):10. https://doi.org/10.3390/jlpea8020010

Chicago/Turabian StyleZaini-Desevedavy, Jennifer, Frédéric Hameau, Thierry Taris, Dominique Morche, and Patrick Audebert. 2018. "An Ultra-Low Power 28 nm FD-SOI Low Noise Amplifier Based on Channel Aware Receiver System Analysis" Journal of Low Power Electronics and Applications 8, no. 2: 10. https://doi.org/10.3390/jlpea8020010

APA StyleZaini-Desevedavy, J., Hameau, F., Taris, T., Morche, D., & Audebert, P. (2018). An Ultra-Low Power 28 nm FD-SOI Low Noise Amplifier Based on Channel Aware Receiver System Analysis. Journal of Low Power Electronics and Applications, 8(2), 10. https://doi.org/10.3390/jlpea8020010