A Novel Low Power Bitcell Design Featuring Inherent SEU Prevention and Self Correction Capabilities †

Abstract

:1. Introduction

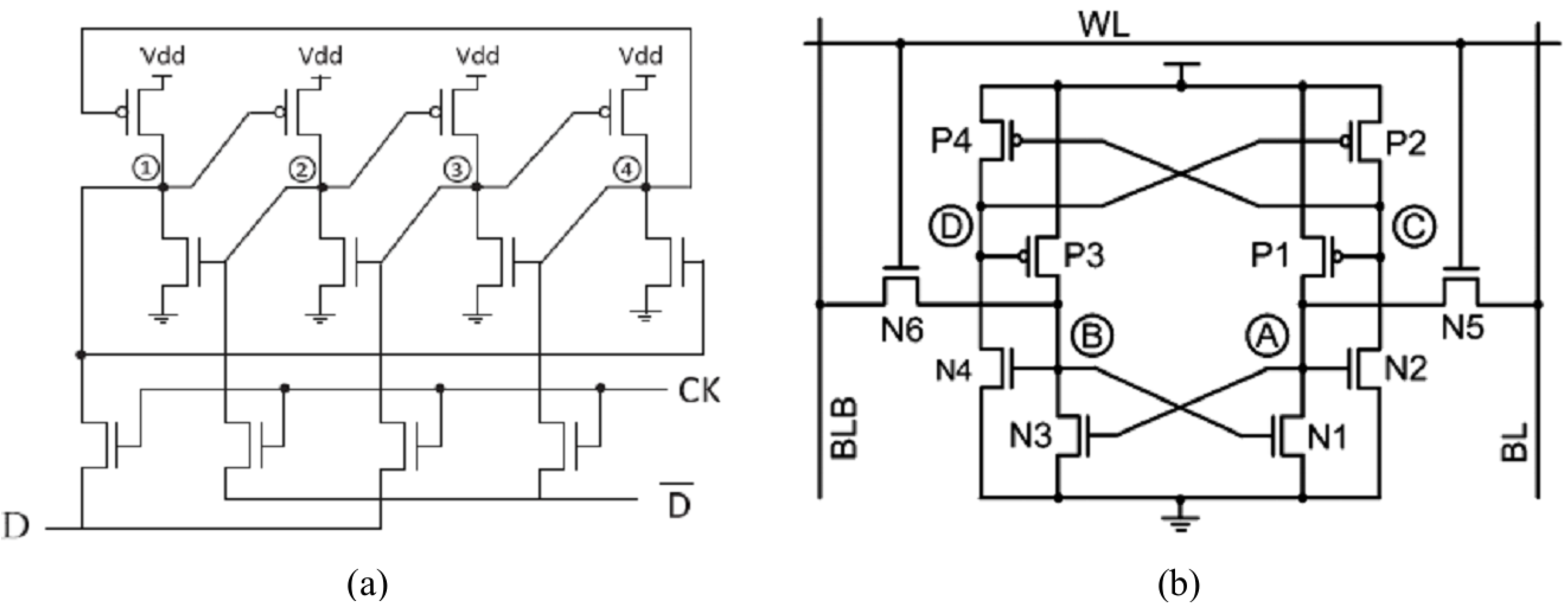

2. Previously Proposed Radiation Hardened by Design Bitcells

2.1. DICE

2.2. Quatro-10T

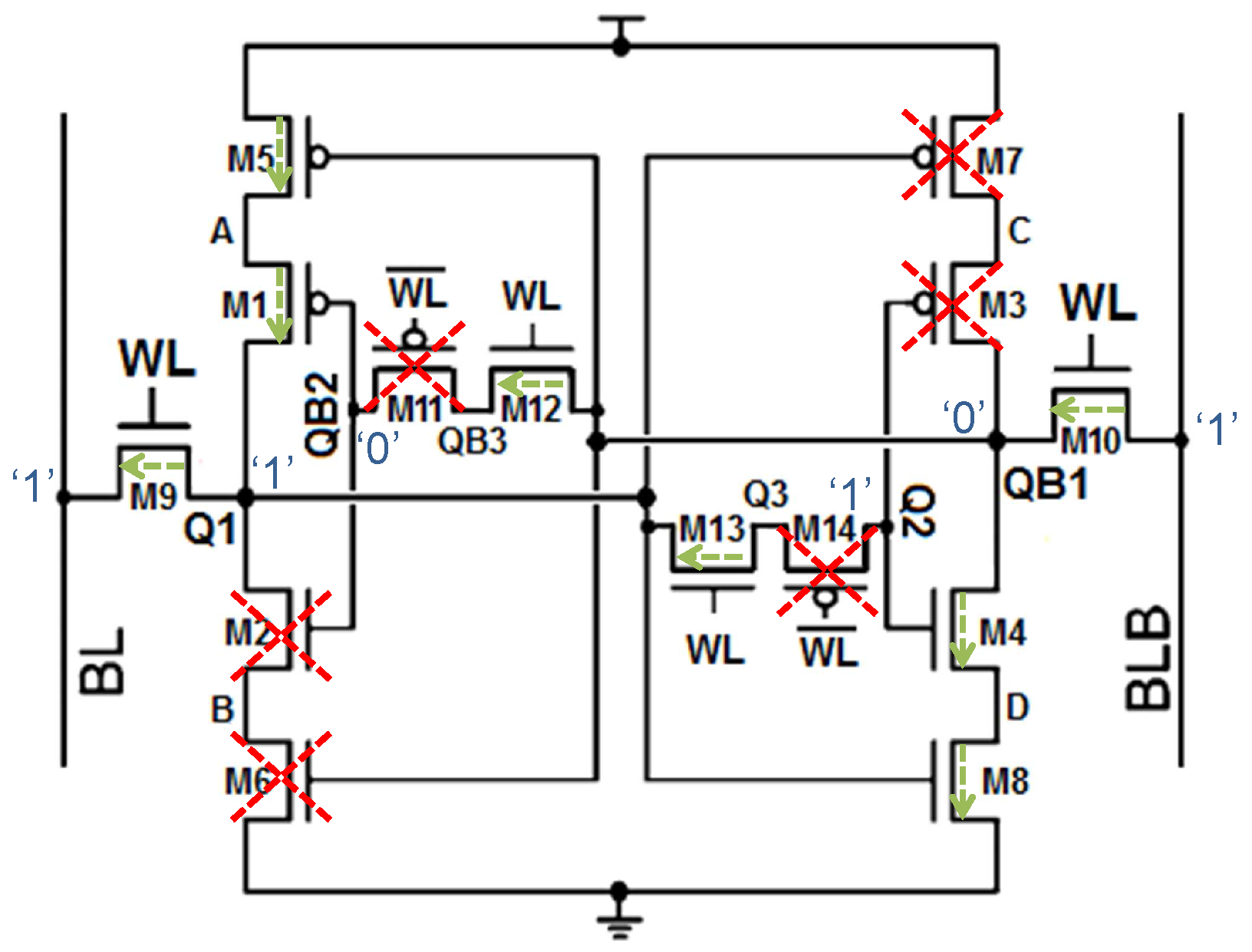

3. The Proposed SHIELD Bitcell

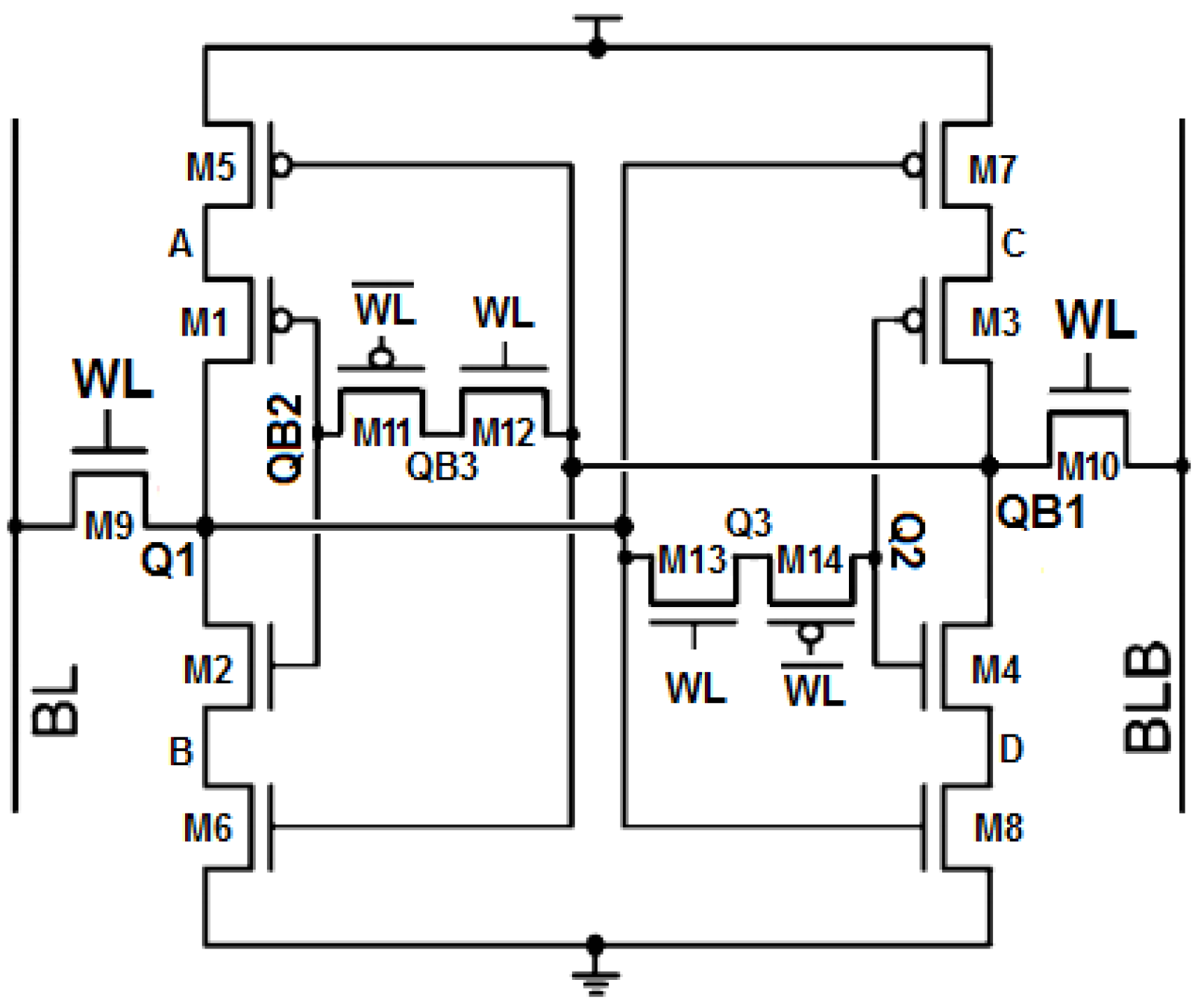

3.1. Proposed Bitcell Structure

3.2. Functionality

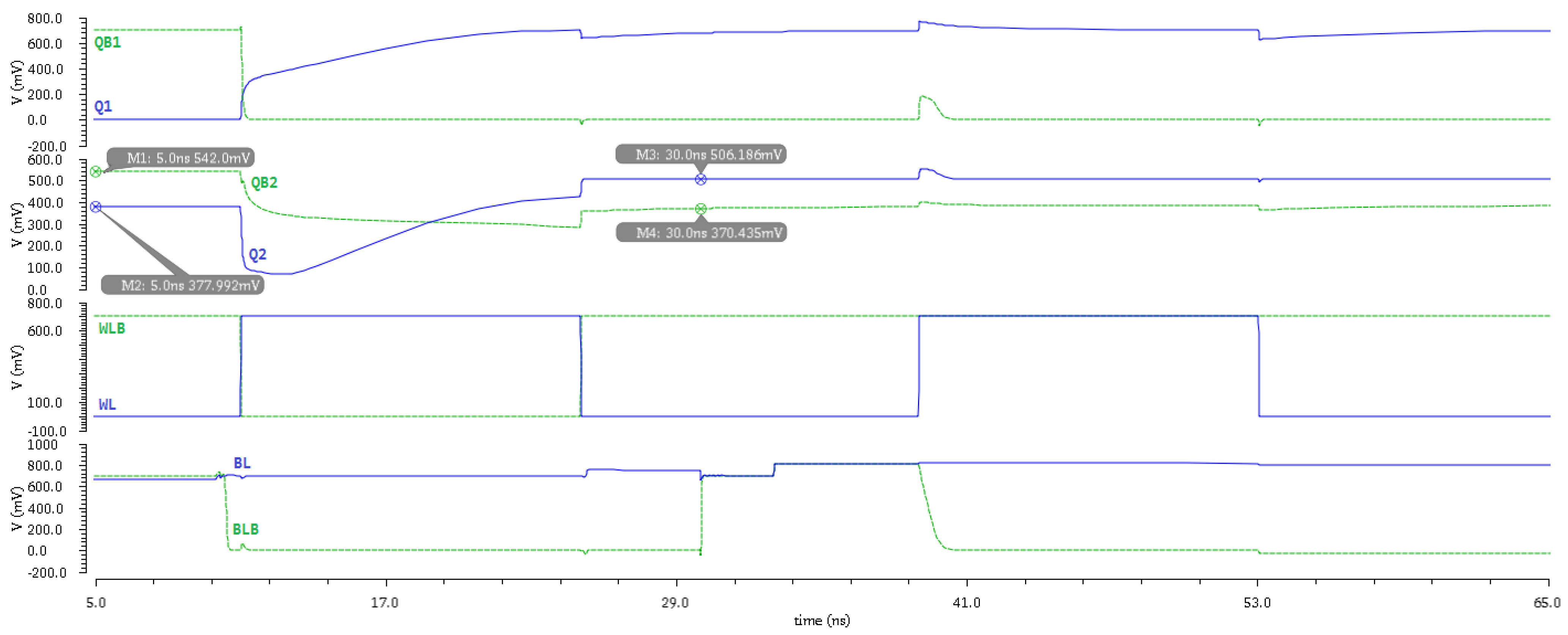

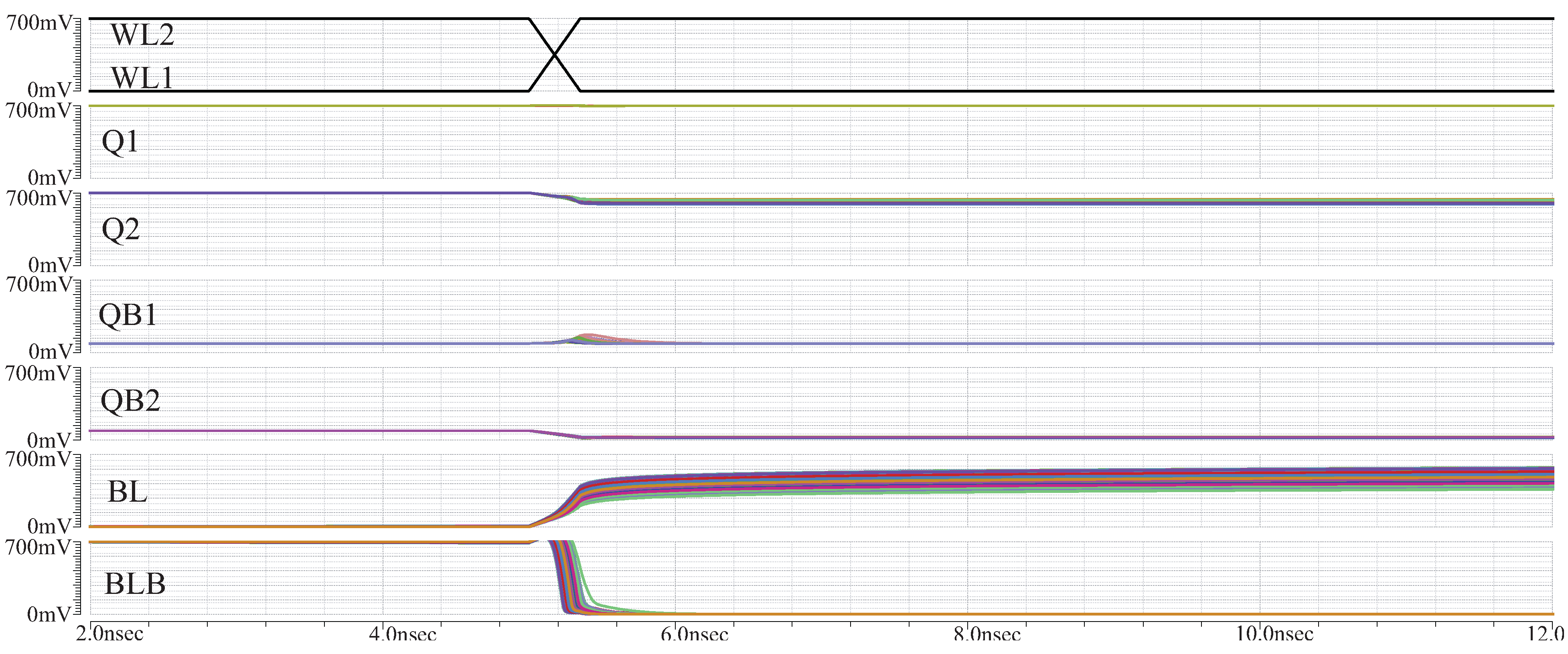

3.2.1. Write Operation

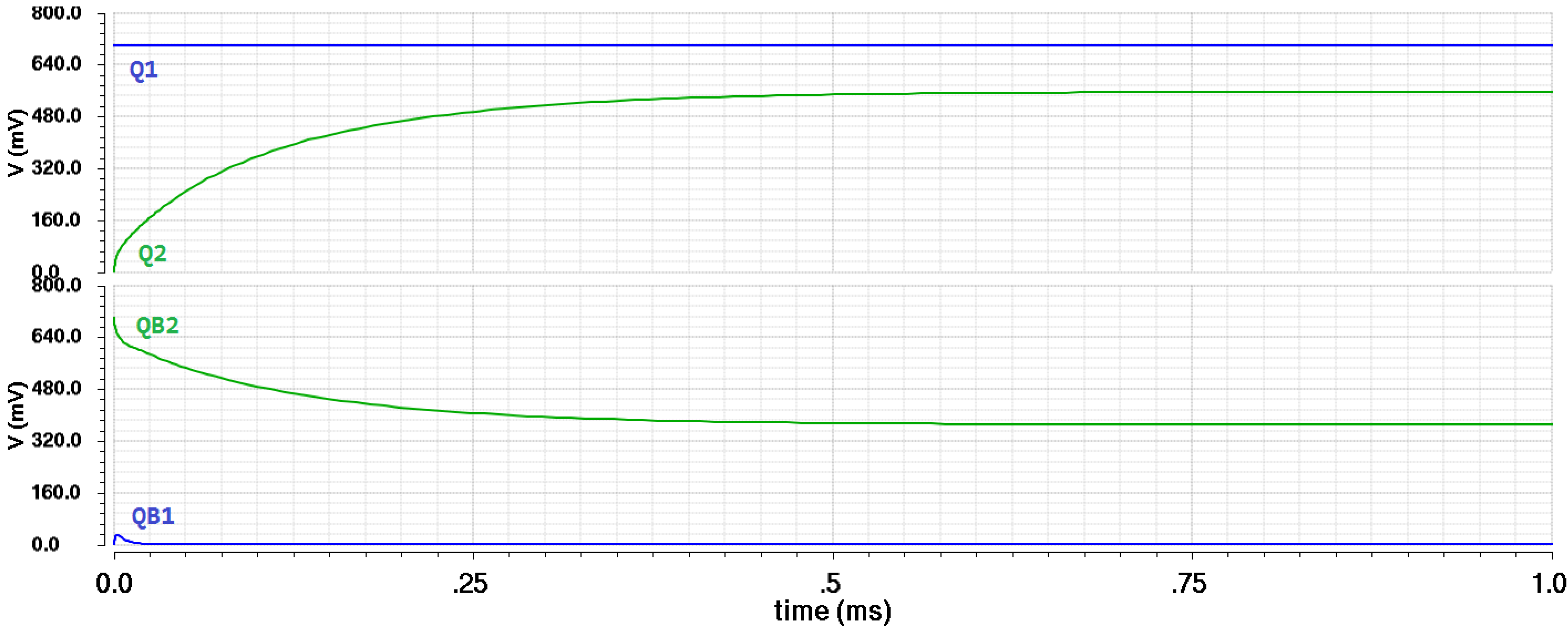

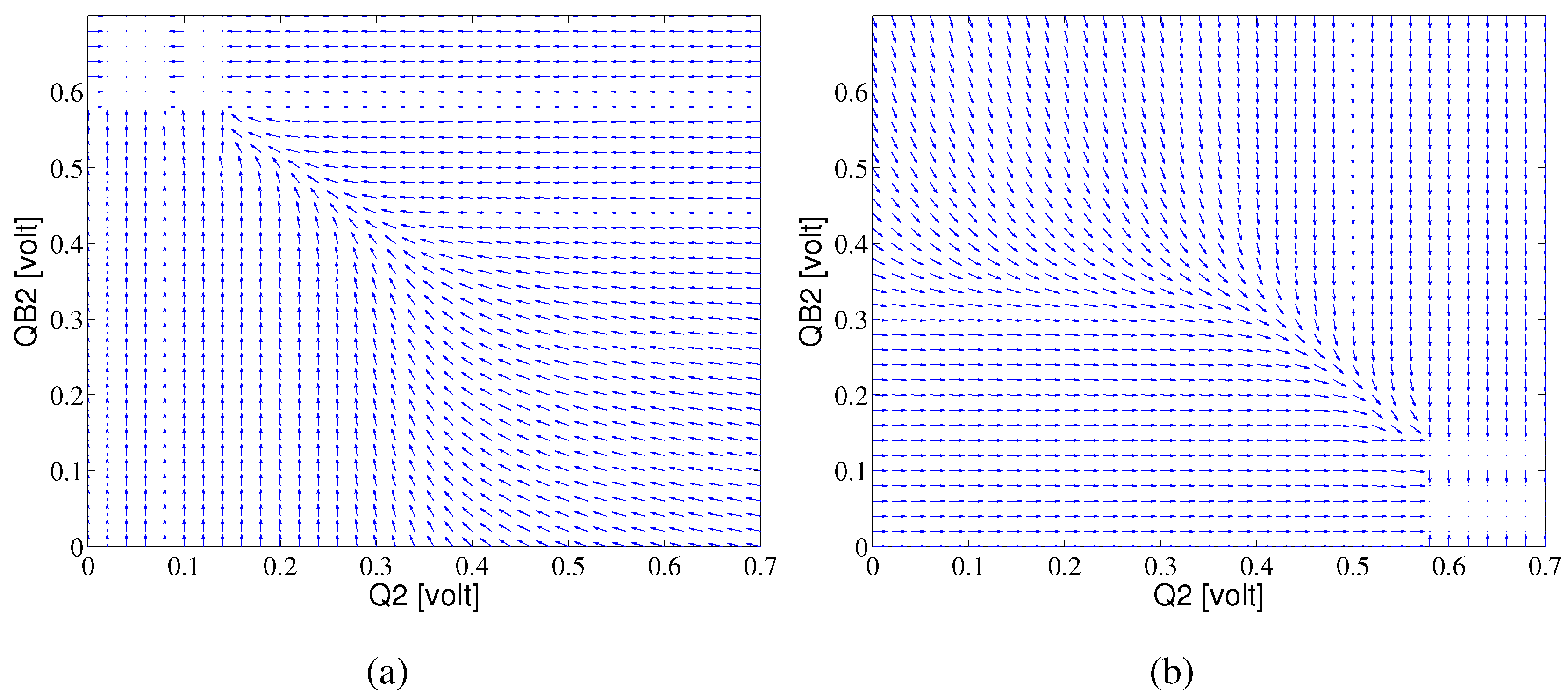

3.2.2. Hold State

3.2.3. Read

3.2.4. Behavior of the Secondary Data Storage Nodes

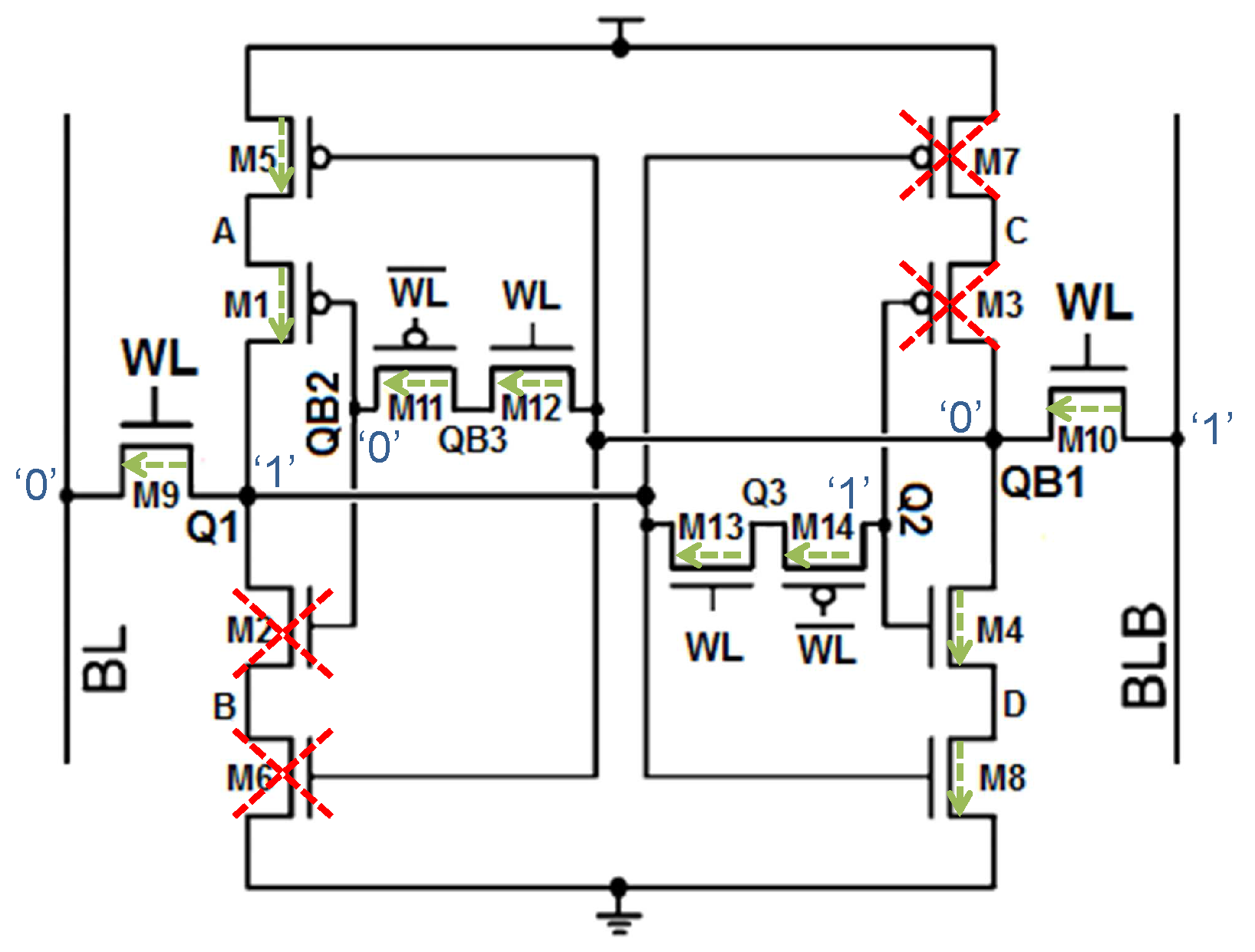

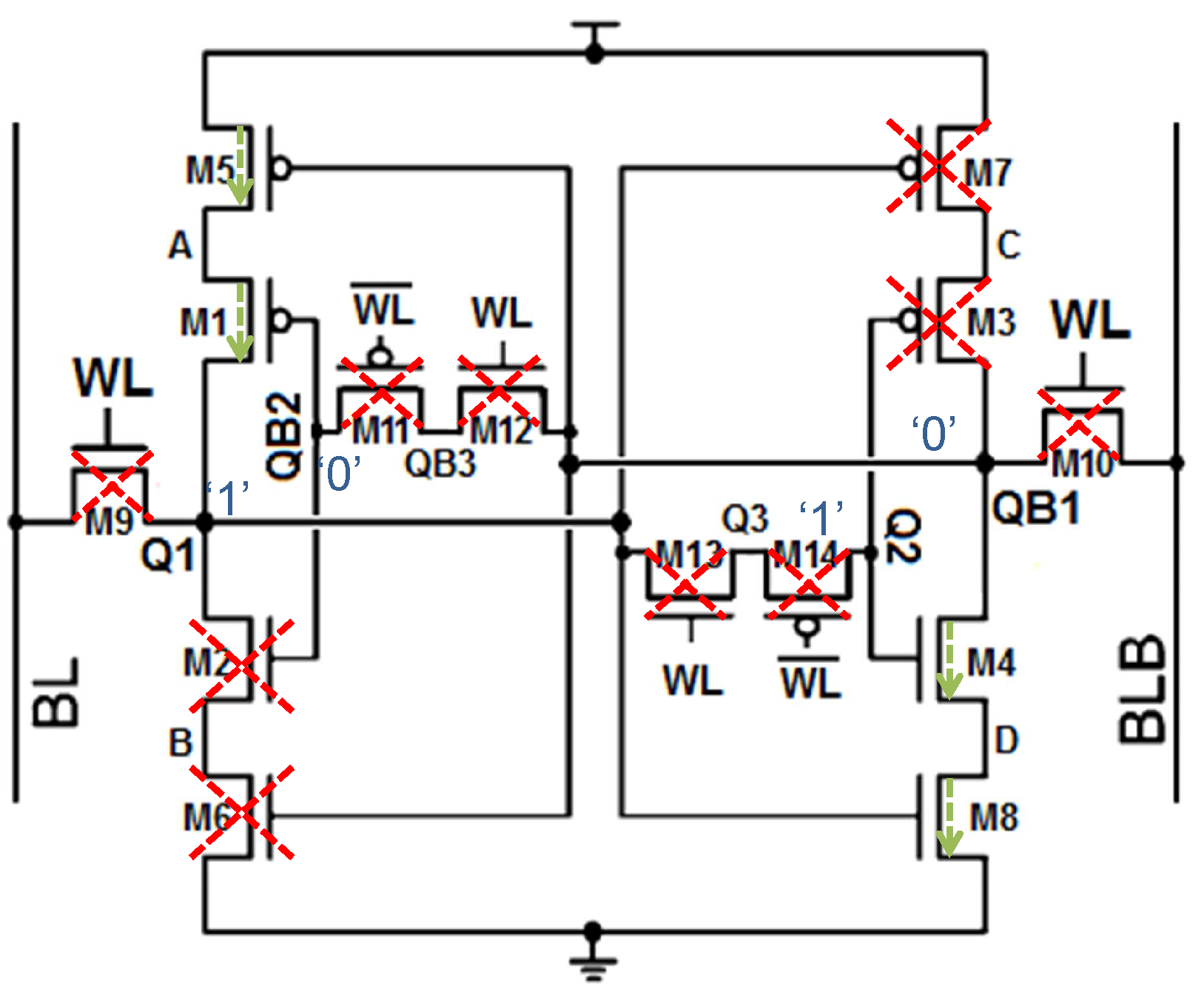

3.3. SEU Hardening

3.3.1. Particle Impact at Node from “0” to “1”

3.3.2. Particle Impact at Node from “1” to “0”

3.3.3. Particle Impact at Node from “0” to “1”

4. Simulations and Results

4.1. SEU Mitigation

4.1.1. SEU Modeling

4.1.2. SEU Simulation Results

| SEU Simulation | SHIELD | DICE | Quatro-10T | 6T |

|---|---|---|---|---|

| :“1” →“0” | >1 pC | >1 pC | >1 pC | 2.2 fC |

| :“0” →“1” | >1 pC | >1 pC | 3.7 fC | 5.6 fC |

| :“1” →“0” | NP | >1 pC | 2.5 fC | - |

| :“0” →“1” | >1 pC | >1 pC | >1 pC | - |

| >1 pC | >1 pC | 2.5 fC | 2.2 fC |

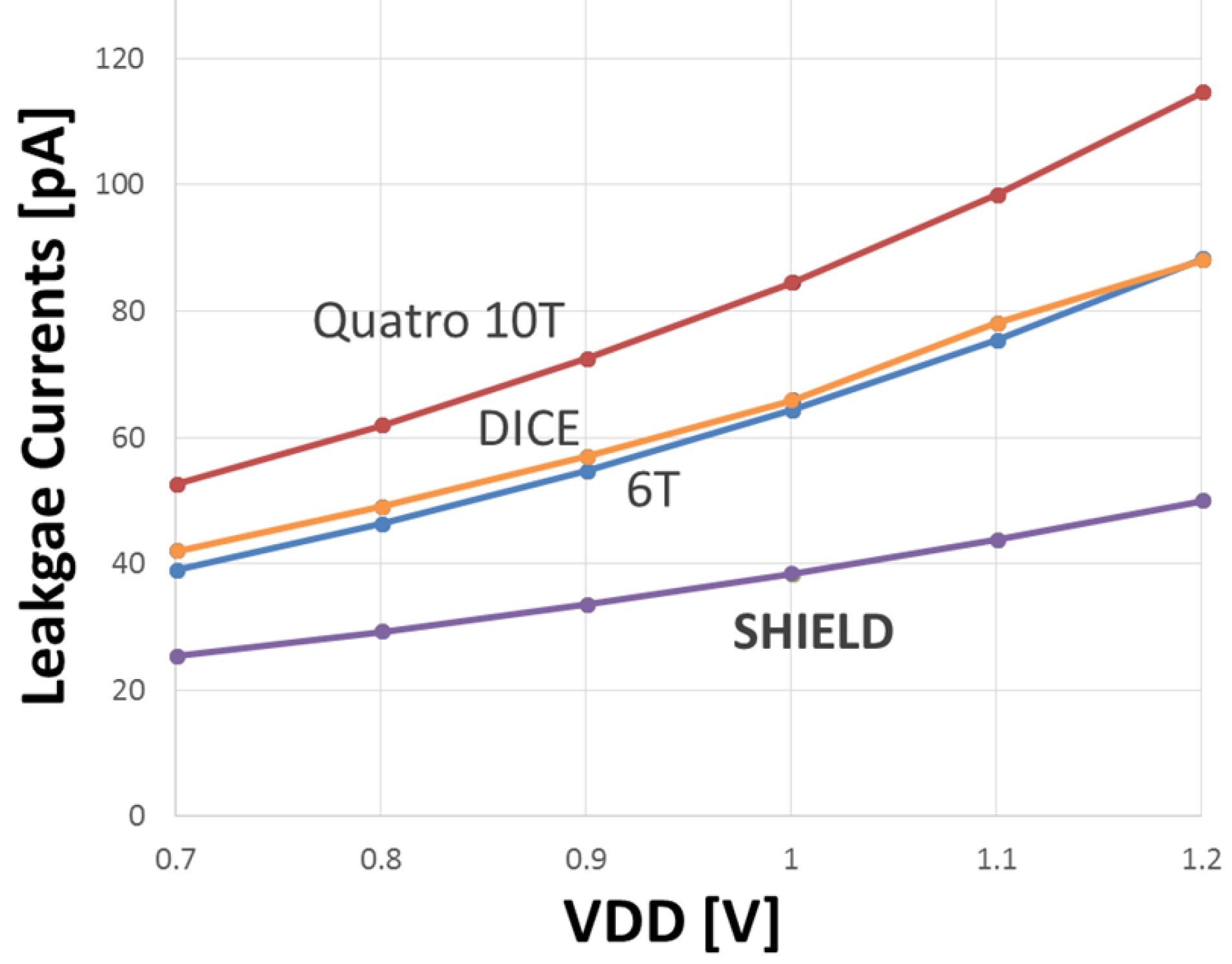

4.2. Power Consumption

| Bitcell | Leakage Current [pA] | Static Power [pW] |

|---|---|---|

| SHIELD | 25.37 | 17.76 |

| 6T | 38.97 | 27.28 |

| DICE | 41.93 | 29.35 |

| Quatro 10T | 52.5 | 36.7 |

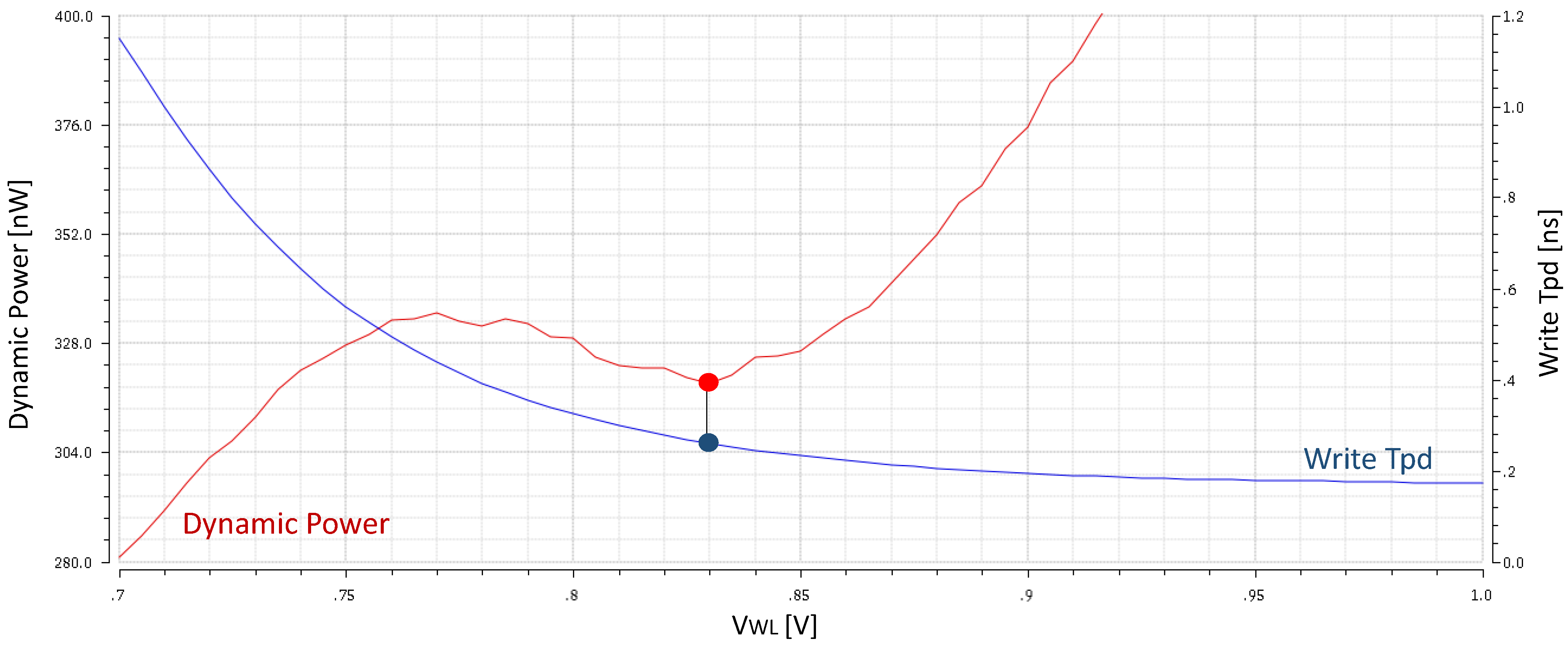

4.3. Improvement of Tpd

4.4. Half Select Functionality

4.5. Bitcell Stability

4.6. Functionality under Reduced Supply Voltage

- “Cut-off” network transistors (M11 to M14) implementation using lvt transistors.The rationale behind this modification is the increase of voltage margin at the and nodes, by propagating a larger voltage swing during the write operation. This guarantees that at the side holding a logic “0”, the inner inverter PMOS transistor (M1/M3) will be in cut-off state (closed) and its complementary NMOS transistor (M2/M4) will be in sub-threshold state (open).

- Replacement of the inner transistors of the gated inverter (M1 to M4) by lvt transistors.The rationale behind this modification is to make the inner inverter transistors more sensitive to the voltage levels of the secondary data storage nodes (/), at the gate of the inner inverter.

| Suggested | Supply | Leakage | Static | M1/M3 |

|---|---|---|---|---|

| Modifications | Voltage [V] | Current [pA] | Power [pW] | PMOS state |

| Before modifications | 0.5 | 15.58 | 7.79 | |

| 0.6 | 18.1 | 10.86 | ||

| 0.7 | 20.8 | 14.56 | ||

| Solution 1 | 0.5 | 15.64 | 7.82 | |

| 0.6 | 18.14 | 10.88 | ||

| 0.7 | 20.83 | 14.58 | ||

| Solution 2 | 0.5 | 16.69 | 8.34 | |

| 0.6 | 19.29 | 11.57 | ||

| 0.7 | 22.1 | 15.47 | ||

| Solutions 1 and 2 | 0.5 | 16.69 | 8.34 | |

| 0.6 | 19.29 | 11.57 | ||

| 0.7 | 22.1 | 15.47 |

4.7. Technology In-Dependency

| Node | Bitcell | Leakage Current [pA] | Static Power [pW] |

|---|---|---|---|

| 65 nm | SHIELD | 25.37 | 17.76 |

| 6T | 38.97 | 27.28 | |

| 90 nm | SHIELD | 7.7 | 5.4 |

| 6T | 9.57 | 6.7 | |

| 180 nm | SHIELD | 2.59 | 1.82 |

| 6T | 3.68 | 2.57 |

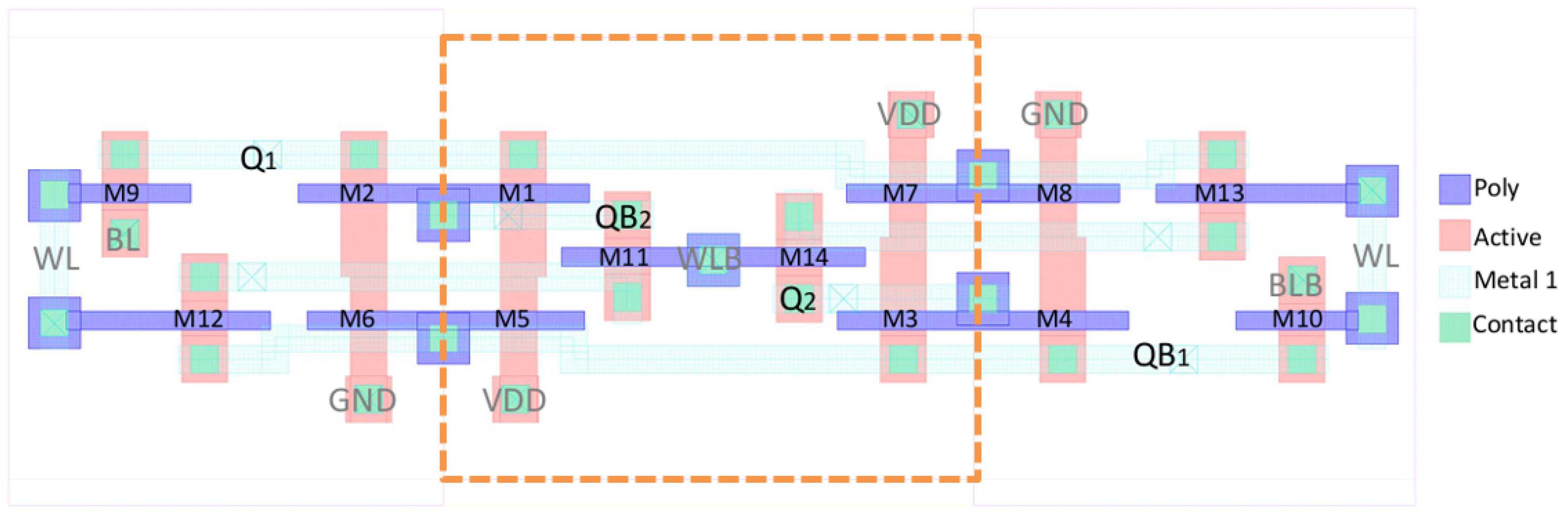

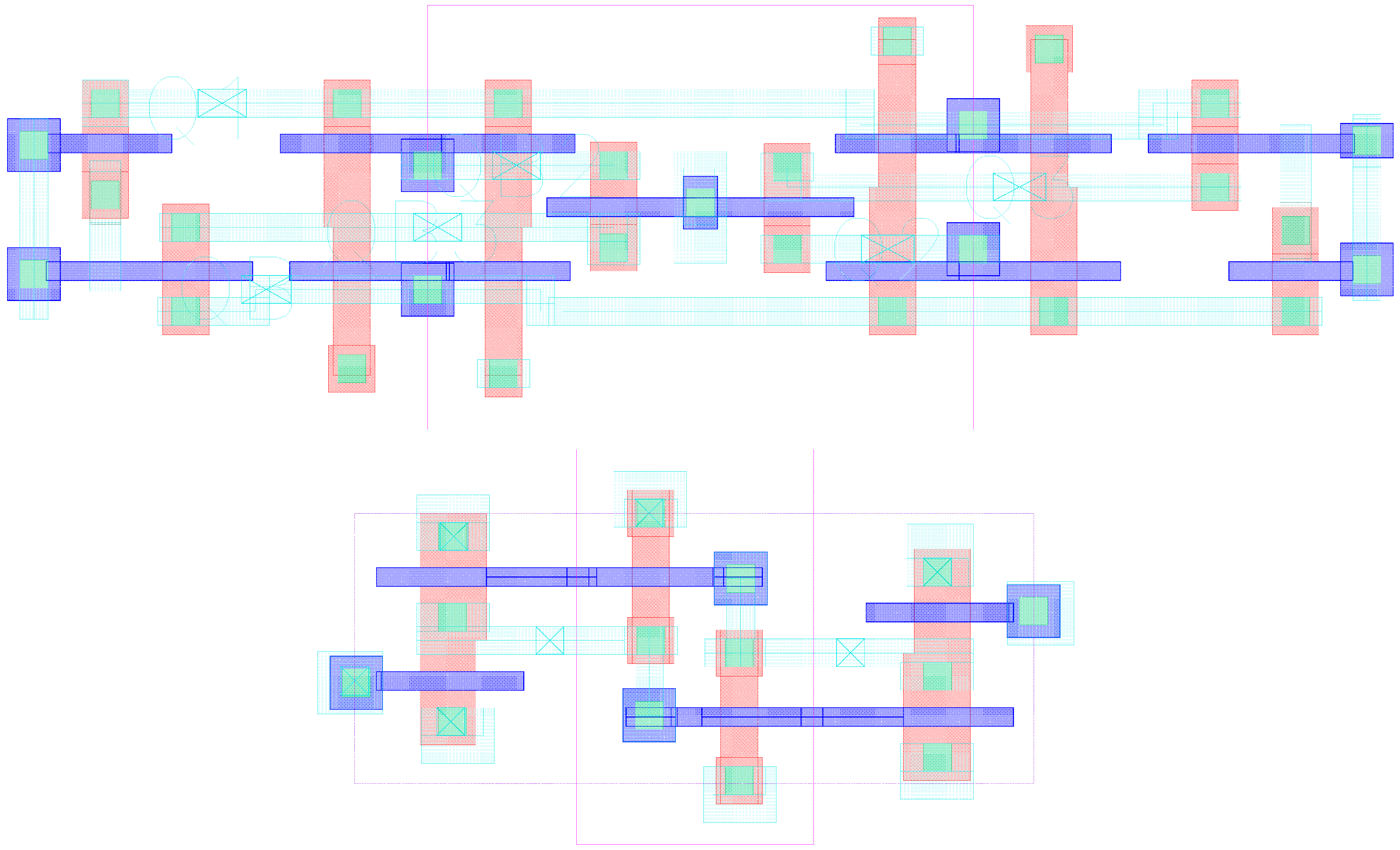

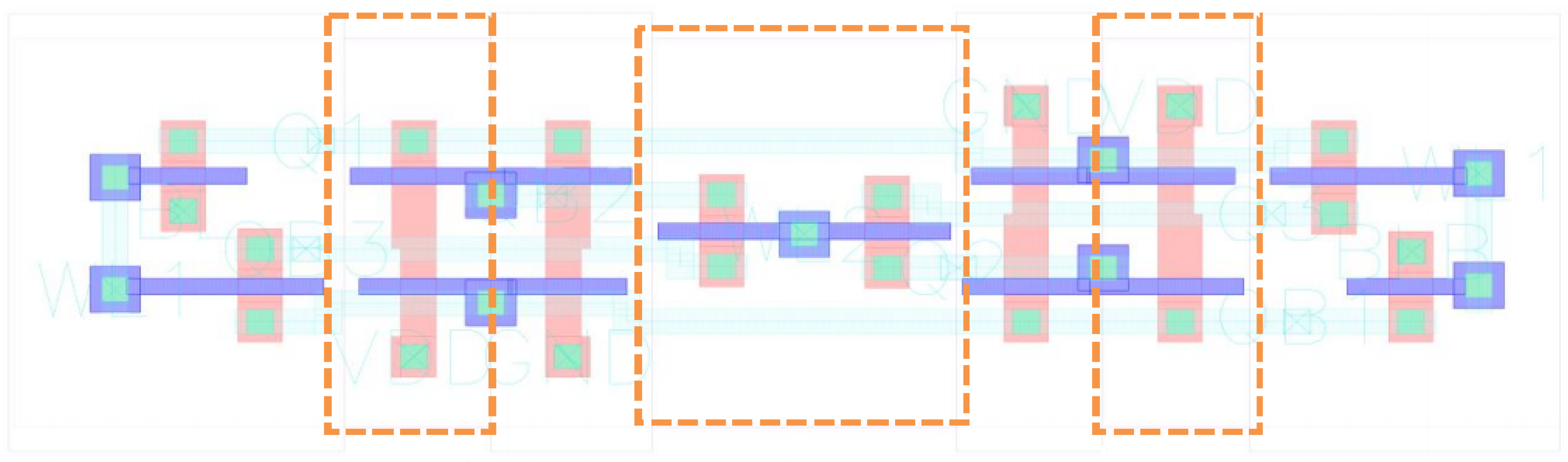

5. Layout Design

Layout Variation for MNU Tolerance

6. Conclusions

Author Contributions

Conflicts of Interest

References

- Calhoun, B.H.; Wang, A.; Chandrakasan, A. Modeling and sizing for minimum energy operation in subthreshold circuits. IEEE J. Solid-State Circuits 2005, 40, 1778–1786. [Google Scholar] [CrossRef]

- Roy, K.; Mukhopadhyay, S.; Mahmoodi-Meimand, H. Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. IEEE Proc. 2003, 91, 305–327. [Google Scholar] [CrossRef]

- Messenger, G.C. Collection of charge on junction nodes from ion tracks. IEEE Trans. Nucl. Sci. 1982, 29, 2024–2031. [Google Scholar] [CrossRef]

- Karnik, T.; Hazucha, P. Characterization of soft errors caused by single event upsets in CMOS processes. IEEE Trans. Dependable Secur. Comput. 2004, 1, 128–143. [Google Scholar] [CrossRef]

- Chandra, V.; Aitken, R. Impact of technology and voltage scaling on the soft error susceptibility in nanoscale cmos. In Proceedings of the IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems, Boston, MA, USA, 1–3 October 2008; pp. 114–122.

- Sterpone, L.; Violante, M. Analysis of the robustness of the TMR architecture in SRAM-based FPGAs. IEEE Trans. Nucl. Sci. 2005, 52, 1545–1549. [Google Scholar] [CrossRef]

- Chen, C.L.; Hsiao, M.Y. Error-correcting codes for semiconductor memory applications: A state-of-the-art review. IBM J. Res. Dev. 1984, 28, 124–134. [Google Scholar] [CrossRef]

- Schwank, J.R.; Ferlet-Cavrois, V.; Shaneyfelt, M.R.; Paillet, P.; Dodd, P.E. Radiation effects in SOI technologies. IEEE Trans. Nucl. Sci. 2003, 50, 522–538. [Google Scholar] [CrossRef]

- Calin, T.; Nicolaidis, M.; Velazco, R. Upset hardened memory design for submicron CMOS technology. IEEE Trans. Nucl. Sci. 1996, 43, 2874–2878. [Google Scholar] [CrossRef]

- Jahinuzzaman, S.M.; Rennie, D.J.; Sachdev, M. A Soft Error Tolerant 10T SRAM Bit-Cell with Differential Read Capability. IEEE Trans. Nucl. Sci. 2009, 56, 3768–3773. [Google Scholar] [CrossRef]

- Teman, A.; Pergament, L.; Cohen, O.; Fish, A. A Minimum Leakage Quasi-Static RAM Bitcell. J. Low Power Electron. 2011, 1, 204–218. [Google Scholar] [CrossRef]

- Teman, A.; Pergament, L.; Cohen, O.; Fish, A. A 250 mV 8 kb 40 nm Ultra-Low Power 9T Supply Feedback SRAM (SF-SRAM). IEEE J. Solid-State Circuits 2011, 46, 2713–2726. [Google Scholar] [CrossRef]

- Vaknin, A.; Yona, O.; Teman, A. A Double-Feedback 8T SRAM Bitcell for Low-Voltage Low-Leakage Operation. In Proceedings of the 2013 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Monterey, CA, USA, 7–10 October 2013; pp. 1–2.

- Kulkarni, J.P.; Roy, K. Ultralow-Voltage Process-Variation-Tolerant Schmitt-Trigger-Based SRAM Design. IEEE Trans. VLSI Syst. 2012, 20, 319–332. [Google Scholar] [CrossRef]

- Pescovsky, A.; Chertkow, O.; Atias, L.; Fish, A. SEU Hardening: Incorporating an Extreme Low Power Bitcell Design (SHIELD). In Proceedings of the SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; IEEE: Piscataway, NJ, USA; pp. 1–3.

- Amusan, O.A.; Witulski, A.F.; Massengill, L.W.; Bhuva, B.L. Charge Collection and Charge Sharing in a 130 nm CMOS Technology. IEEE Trans. Nucl. Sci. 2006, 53, 3253–3258. [Google Scholar] [CrossRef]

- Dodd, P.E.; Massengill, L.W. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Garg, R.; Jayakumar, N.; Khatri, S.P.; Choi, G.S. Circuit-level design approaches for radiation-hard digital electronics. IEEE Trans. VLSI Syst. 2009, 17, 781–792. [Google Scholar] [CrossRef]

- Hass, K.J.; Ambles, J.W. Single event transients in deep submicron CMOS. In Proceedings of the Midwest Symposium on Circuits and Systems, Las Cruces, NM, USA, 8–11 August 1999; Volume 42, pp. 122–125.

- Schwank, J.R.; Shaneyfelt, M.R.; Dodd, P.E. Radiation hardness assurance testing of microelectronic devices and integrated circuits: Radiation environments, physical mechanisms, and foundations for hardness assurance. IEEE Trans. Nucl. Sci. 2013, 60, 2074–2100. [Google Scholar] [CrossRef]

- Kim, N.S.; Austin, T.; Baauw, D.; Mudge, T.; Flautner, K.; Hu, J.S.; Irwin, M.J.; Kandemir, M.; Narayanan, V. Leakage current: Moore’s law meets static power. Computer 2003, 36, 68–75. [Google Scholar]

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chertkow, O.; Pescovsky, A.; Atias, L.; Fish, A. A Novel Low Power Bitcell Design Featuring Inherent SEU Prevention and Self Correction Capabilities. J. Low Power Electron. Appl. 2015, 5, 130-150. https://doi.org/10.3390/jlpea5020130

Chertkow O, Pescovsky A, Atias L, Fish A. A Novel Low Power Bitcell Design Featuring Inherent SEU Prevention and Self Correction Capabilities. Journal of Low Power Electronics and Applications. 2015; 5(2):130-150. https://doi.org/10.3390/jlpea5020130

Chicago/Turabian StyleChertkow, Oron, Ariel Pescovsky, Lior Atias, and Alexander Fish. 2015. "A Novel Low Power Bitcell Design Featuring Inherent SEU Prevention and Self Correction Capabilities" Journal of Low Power Electronics and Applications 5, no. 2: 130-150. https://doi.org/10.3390/jlpea5020130

APA StyleChertkow, O., Pescovsky, A., Atias, L., & Fish, A. (2015). A Novel Low Power Bitcell Design Featuring Inherent SEU Prevention and Self Correction Capabilities. Journal of Low Power Electronics and Applications, 5(2), 130-150. https://doi.org/10.3390/jlpea5020130