SOTB Implementation of a Field Programmable Gate Array with Fine-Grained Vt Programmability †

Abstract

:1. Introduction

2. Overviews of the SOTB Transistor and Flex Power FPGA Architecture

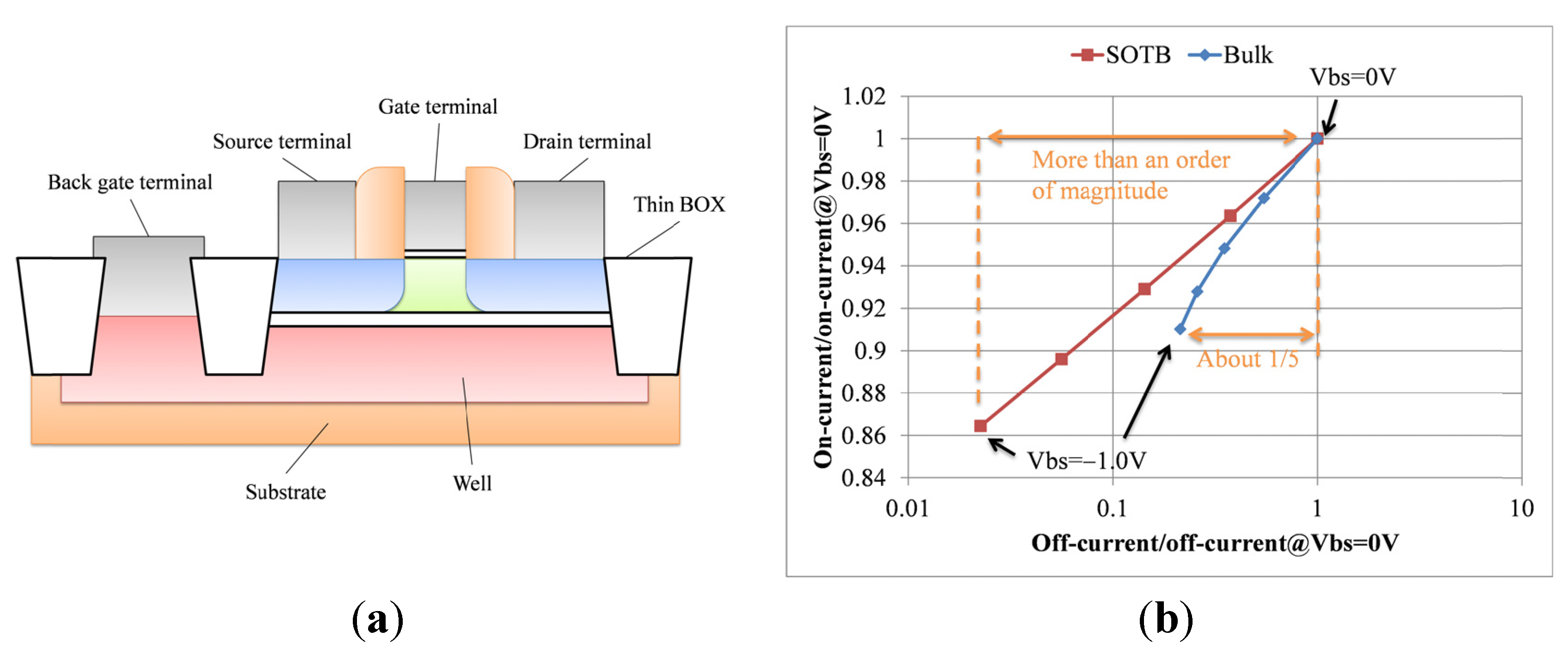

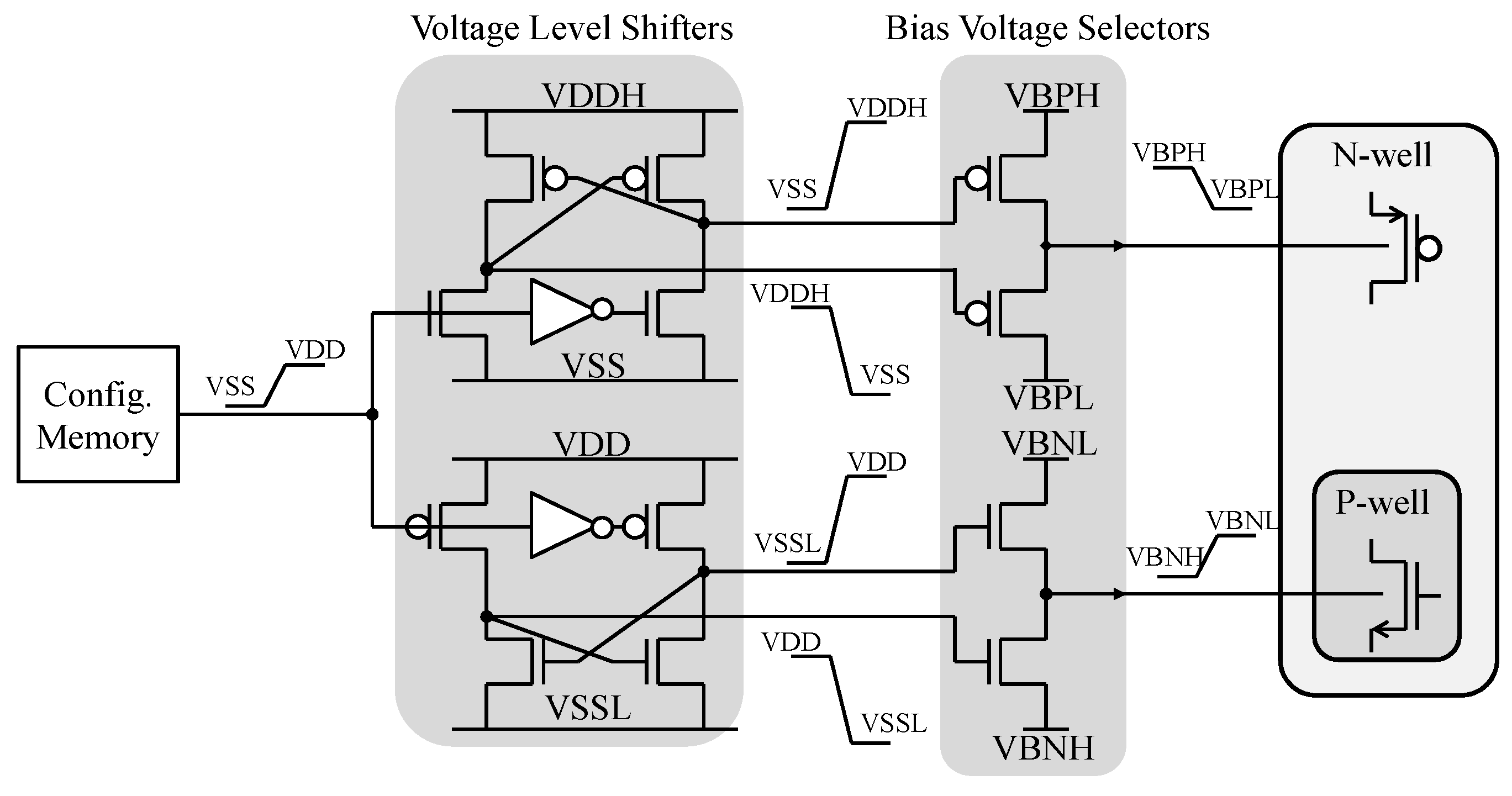

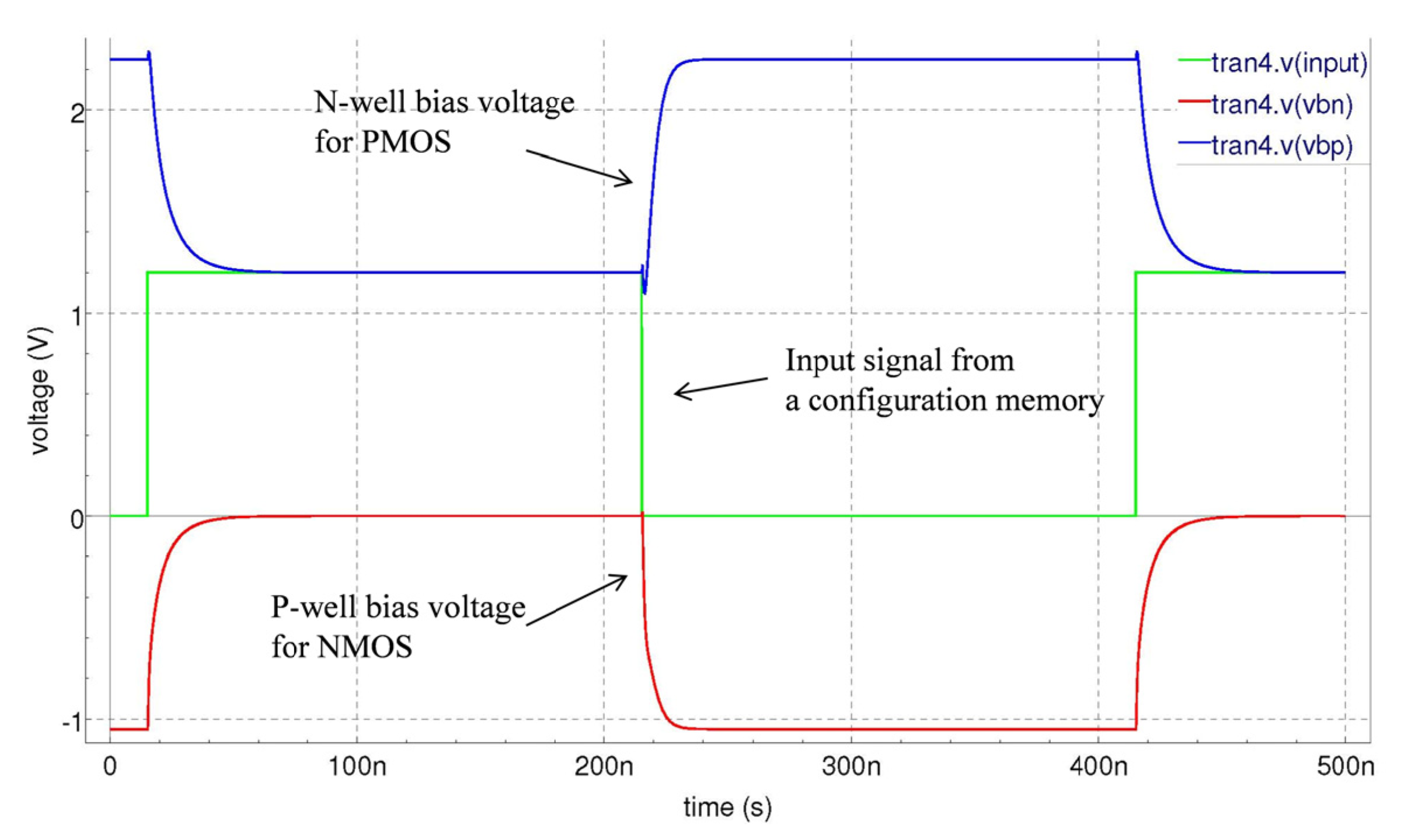

2.1. Silicon on Thin Buried Oxide (SOTB) Transistor

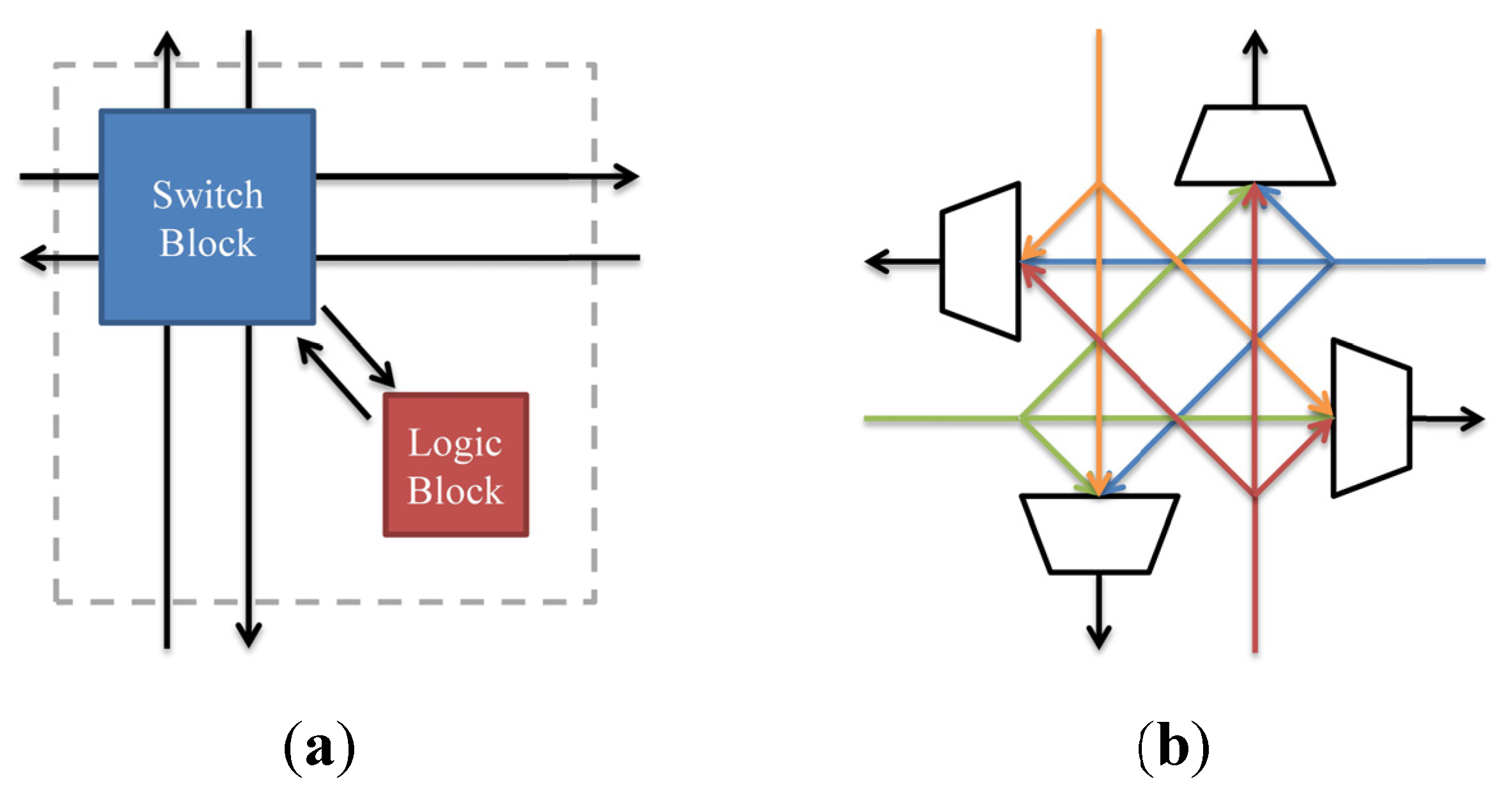

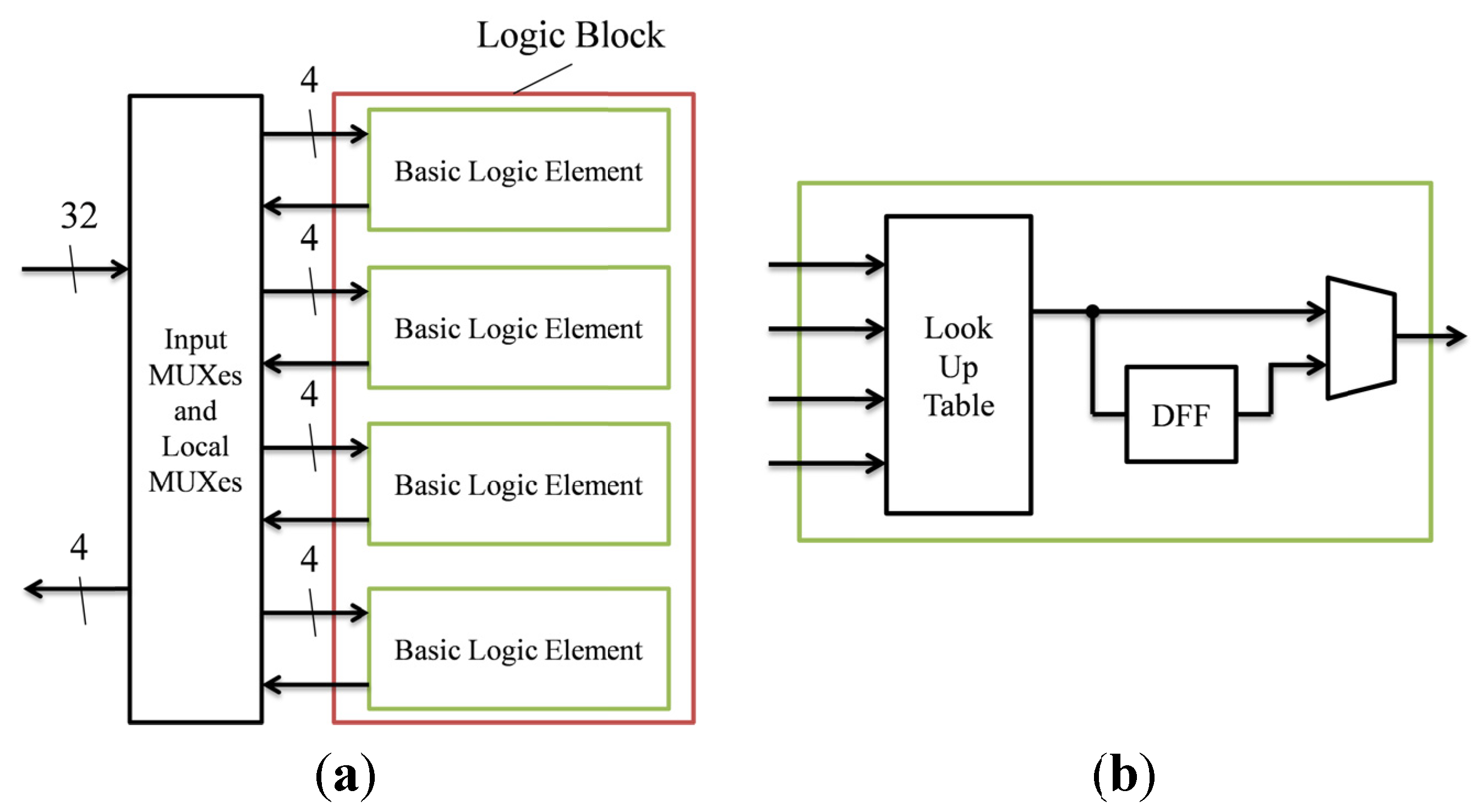

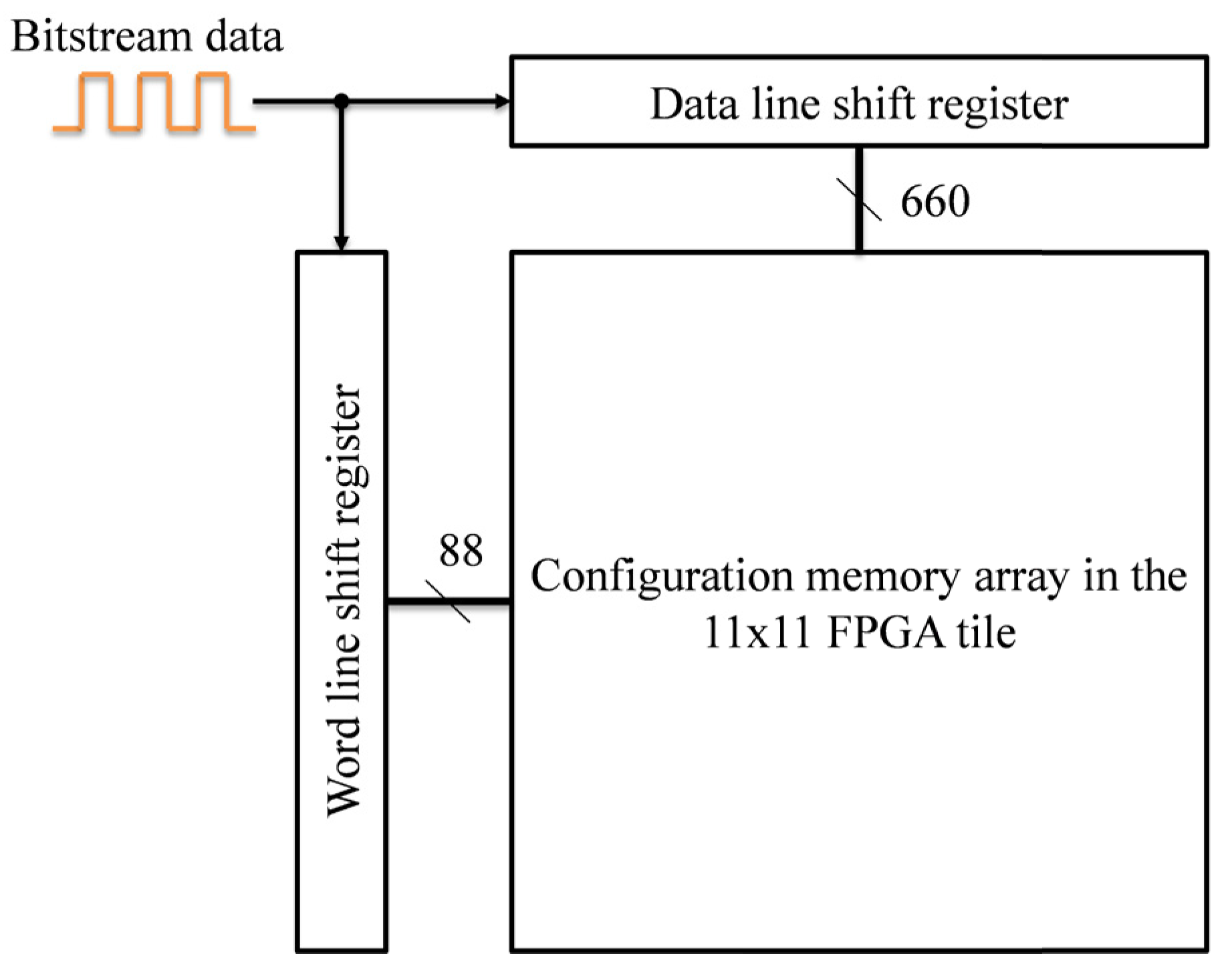

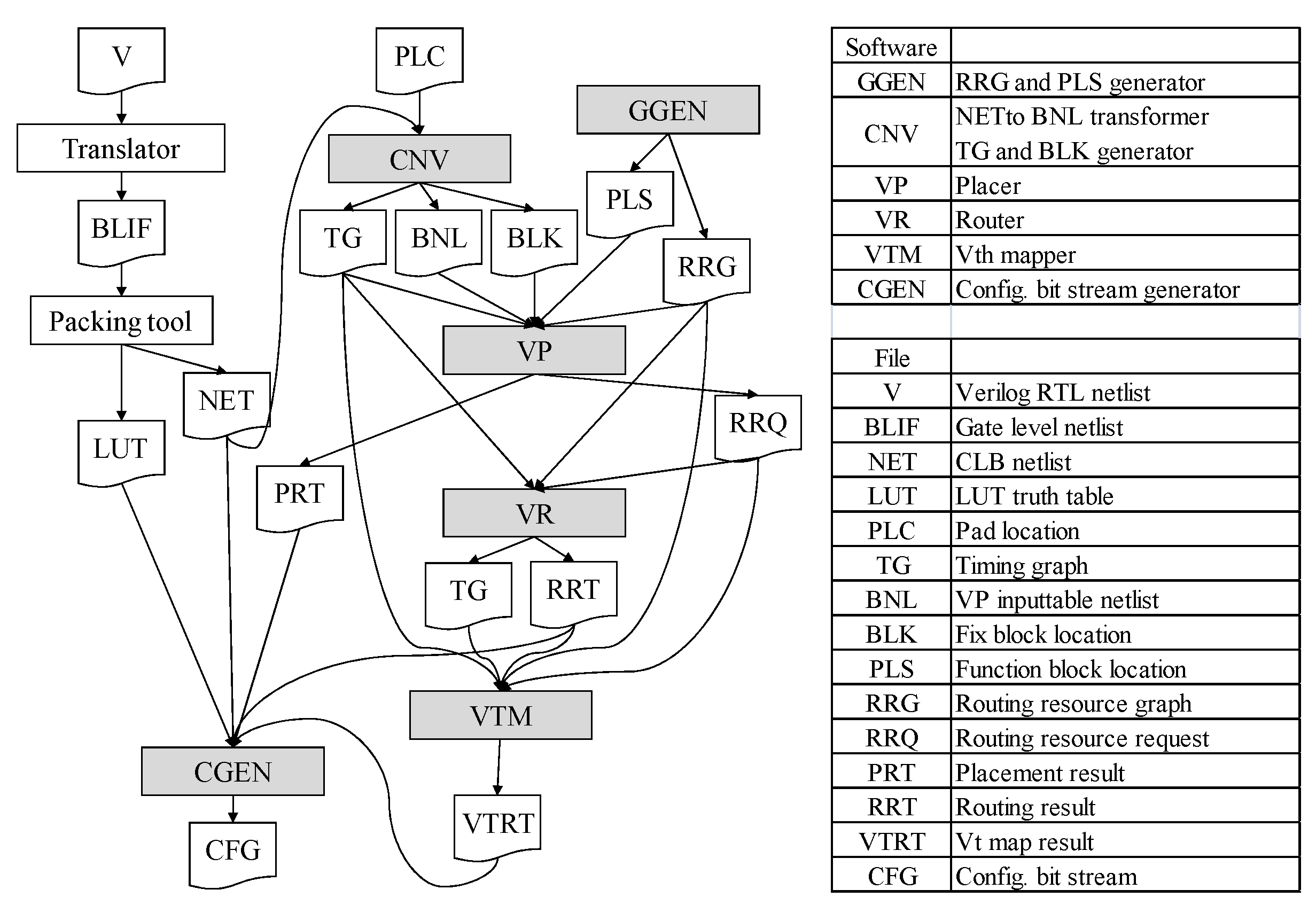

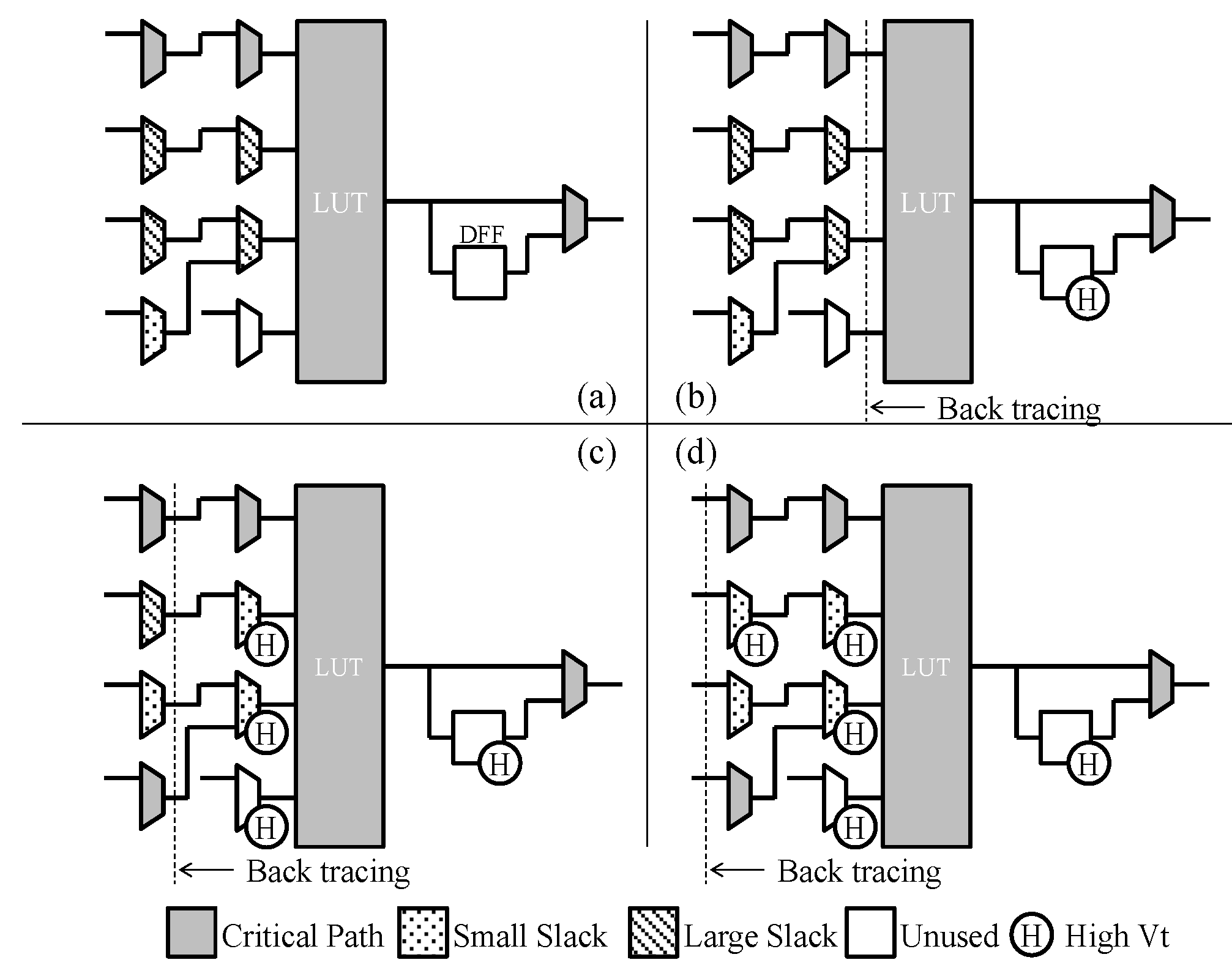

2.2. Flex Power FPGA Architecture

| Parameter | Value |

|---|---|

| # of tiles | 121 (11 × 11) |

| Wire length | 4 |

| Switch matrix topology | Disjoint |

| Routing architecture | Unidirectional and single driver programmable interconnect |

| Routing channel width | 16 |

| # of BLEs per a CLB (configurable logic block) | 4 |

| # of CLB inputs | 13 |

| # of CLB outputs | 4 |

| # of BLE inputs | 7 |

| # of Vt control domains per a tile | 57 |

3. Evaluation Results

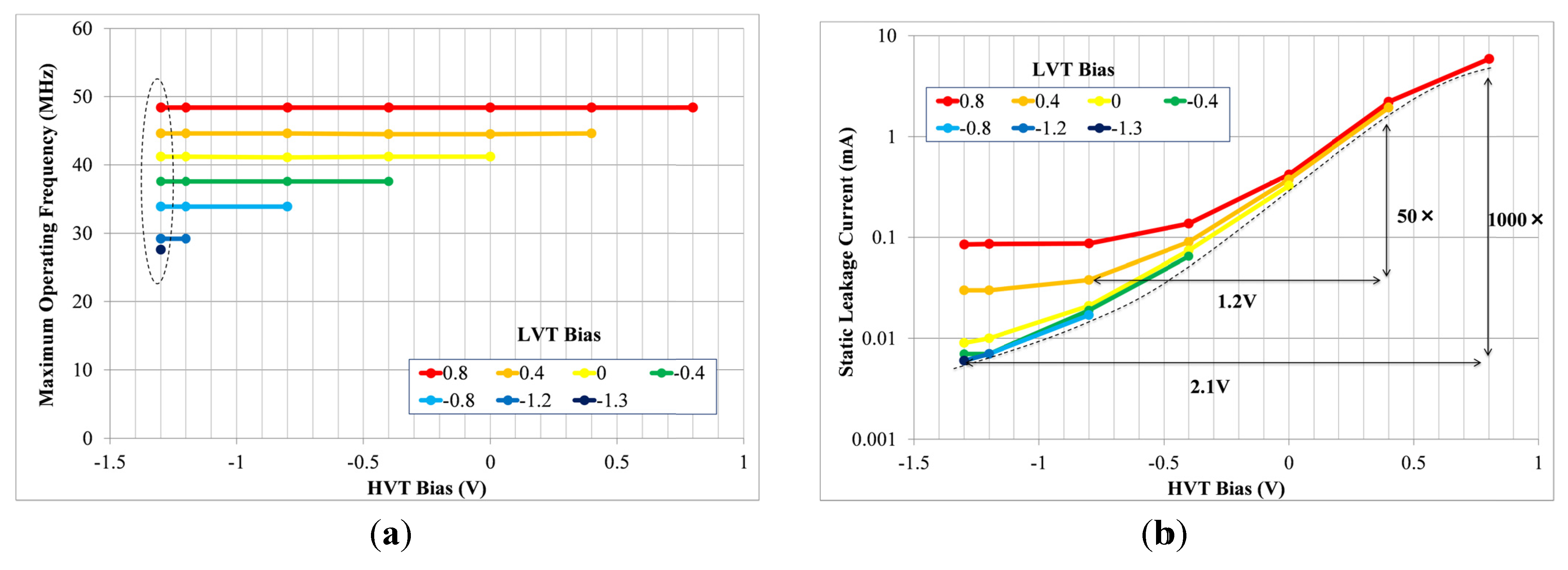

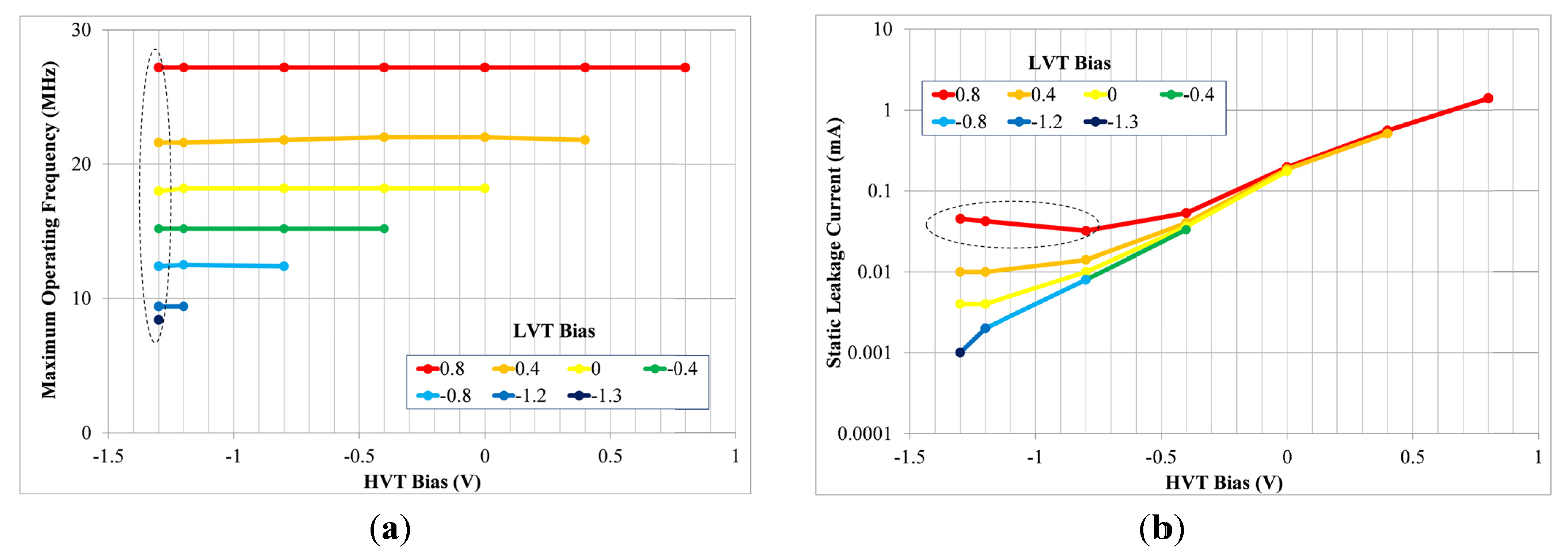

3.1. Operating Speed and Static Leakage Current

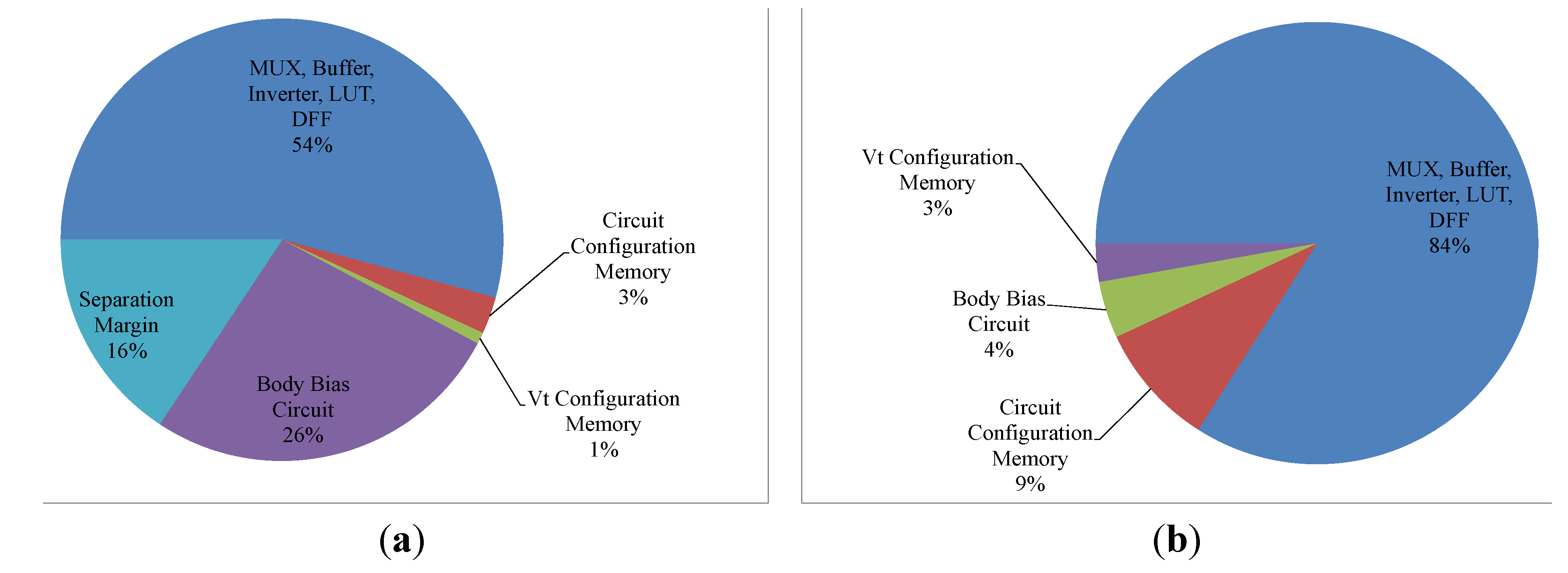

3.2. Overhead

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Kuon, I.; Rose, J. Measuring the Gap between FPGAs and ASICs. In Proceedings of the 2006 ACM/SIGDA 14th International Symposium on Field Programmable Gate Arrays, Monterey, CA, USA, 22–24 February 2006; pp. 21–30.

- Li, F.; Lin, Y.; He, L.; Cong, J. Low-Power FPGA Using Predefined Dual-Vdd/Dual-Vt Fabrics. In Proceedings of the 2004 ACM/SIGDA 12th International Symposium on Field Programmable Gate Arrays, Monterey, CA, USA, 22–24 February 2004; pp. 42–50.

- Rahman, A.; Polavarapuv, V. Evaluation of Low-Leakage Design Techniques for Field Programmable Gate Arrays. In Proceedings of the 2004 ACM/SIGDA 12th International Symposium on Field Programmable Gate Arrays, Monterey, CA, USA, 22–24 February 2004; pp. 23–30.

- Gayasen, A.; Tasi, Y.; Vijaykrishnan, N.; Kandemir, M.; Irwin, M.J.; Tuan, T. Reduced Leakage Energy in FPGAs Using Region-Constrained Placement. In Proceedings of the 2004 ACM/SIGDA 12th International Symposium on Field Programmable Gate Arrays, Monterey, CA, USA, 22–24 February 2004; pp. 51–58.

- Anderson, J.H.; Najim, F.N. Low-Power Programmable Routing Circuitry for FPGAs. In Proceedings of the 2004 IEEE/ACM International Conference on Computer-aided Design, Washington, DC, USA, 7–11 November 2004; pp. 602–609.

- Lin, Y.; Li, F.; He, L. Routing Track Duplication with Fine-Grained Power-Gating for FPGA Interconnect Power Reduction. In Proceedings of the 2005 Asia and South Pacific Design Automation Conference, Shanghai, China, 18–21 January 2005; pp. 645–650.

- Rahman, A.; Das, S.; Tuan, T.; Rahut, A. Heterogeneous Routing Architecture for Low-Power FPGA Fabric. In Proceedings of the IEEE Custom Integrated Circuits Conference 2005, San Jose, CA, USA, 21 September 2005; pp. 183–186.

- Tuan, T.; Kao, S.; Rahman, A.; Das, S.; Trimberger, S. A 90 nm Lowpower FPGA for Battery-Powered Applications. In Proceedings of the 2006 ACM/SIGDA 14th International Symposium on Field Programmable Gate Arrays, Monterey, CA, USA, 22–24 February 2006; pp. 3–11.

- Kawanami, T.; Hioki, M.; Nagase, H.; Tsutsumi, T.; Nakagawa, T.; Sekigawa, T.; Koike, H. Preliminary evaluation of flex power FPGA: A power reconfigurable architecture with fine granularity. IEICE Trans. Inf. Syst. 2004, 8, 2004–2010. [Google Scholar]

- Tsuchiya, R.; Horiuchi, M.; Kimura, S.; Yamaoka, M.; Kawahara, T.; Maegawa, S.; Ipposhi, T.; Ohji, Y.; Matsuoka, H. Silicon on Thin BOX: A New Paradigm of the CMOSFET for Low-Power High-Performance Application Featuring Wide-Range Back-Bias Control. In Proceedings of the IEEE International Electron Devices Meeting 2004, San Francisco, CA, USA, 13–15 December 2004; pp. 631–634.

- Hioki, M.; Sekigawa, T.; Nakagawa, T.; Kawanami, T.; Matsumoto, Y; Tsutsumi, T.; Koike, H. Fully-Functional FPGA prototype with Fine-Grain Programmable Body Biasing. In Proceedings of the ACM/SIGDA International Symposium on Field Programmable Gate Arrays, Monterey, CA, USA, 11–13 February 2013; pp. 73–80.

- Sugii, N.; Tsuchiya, R.; Ishigaki, T.; Morita, Y.; Yoshimoto, H.; Kimura, S. Local Vth Variability and Scalability in Silicon-on-Thin-Box (SOTB) CMOS with Small Random-Dopant Fluctuation. IEEE Trans. Electron Devices 2010, 57, 835–845. [Google Scholar] [CrossRef]

- Kawanami, T.; Hioki, M.; Matsumoto, Y.; Tsutsumi, T.; Nakagawa, T.; Sekigawa, T.; Koike, H. Optimal Set of Body Bias Voltages for an FPGA with Field-Programmable Vth Components. In Proceedings of the 2006 IEEE International Conference on Field Programmable Technology, Bangkok, Thailand, 13–15 December 2006; pp. 329–332.

© 2014 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Hioki, M.; Ma, C.; Kawanami, T.; Ogasahara, Y.; Nakagawa, T.; Sekigawa, T.; Tsutsumi, T.; Koike, H. SOTB Implementation of a Field Programmable Gate Array with Fine-Grained Vt Programmability. J. Low Power Electron. Appl. 2014, 4, 188-200. https://doi.org/10.3390/jlpea4030188

Hioki M, Ma C, Kawanami T, Ogasahara Y, Nakagawa T, Sekigawa T, Tsutsumi T, Koike H. SOTB Implementation of a Field Programmable Gate Array with Fine-Grained Vt Programmability. Journal of Low Power Electronics and Applications. 2014; 4(3):188-200. https://doi.org/10.3390/jlpea4030188

Chicago/Turabian StyleHioki, Masakazu, Chao Ma, Takashi Kawanami, Yasuhiro Ogasahara, Tadashi Nakagawa, Toshihiro Sekigawa, Toshiyuki Tsutsumi, and Hanpei Koike. 2014. "SOTB Implementation of a Field Programmable Gate Array with Fine-Grained Vt Programmability" Journal of Low Power Electronics and Applications 4, no. 3: 188-200. https://doi.org/10.3390/jlpea4030188

APA StyleHioki, M., Ma, C., Kawanami, T., Ogasahara, Y., Nakagawa, T., Sekigawa, T., Tsutsumi, T., & Koike, H. (2014). SOTB Implementation of a Field Programmable Gate Array with Fine-Grained Vt Programmability. Journal of Low Power Electronics and Applications, 4(3), 188-200. https://doi.org/10.3390/jlpea4030188