An Ultra-Low Energy Subthreshold SRAM Bitcell for Energy Constrained Biomedical Applications †

Abstract

:1. Introduction

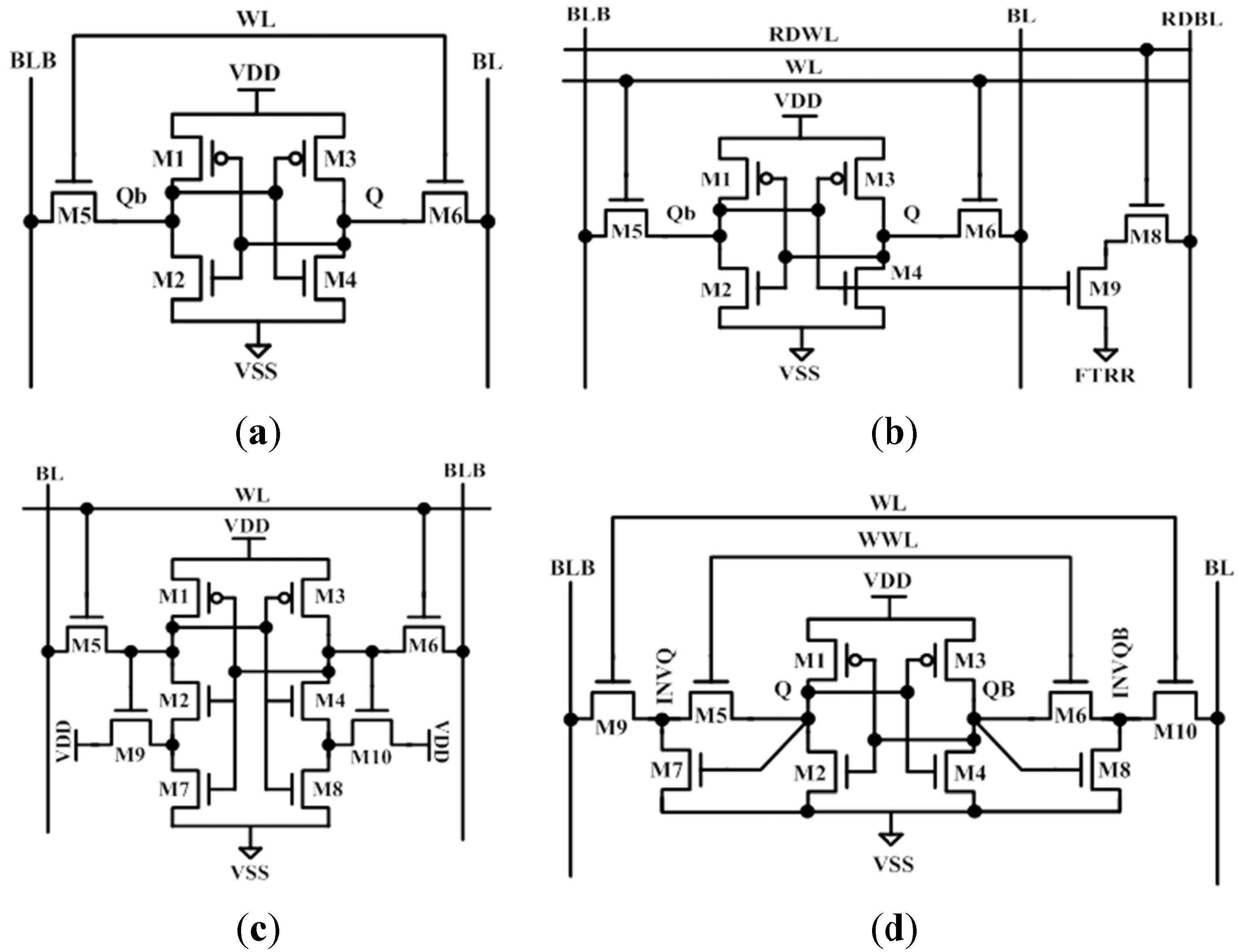

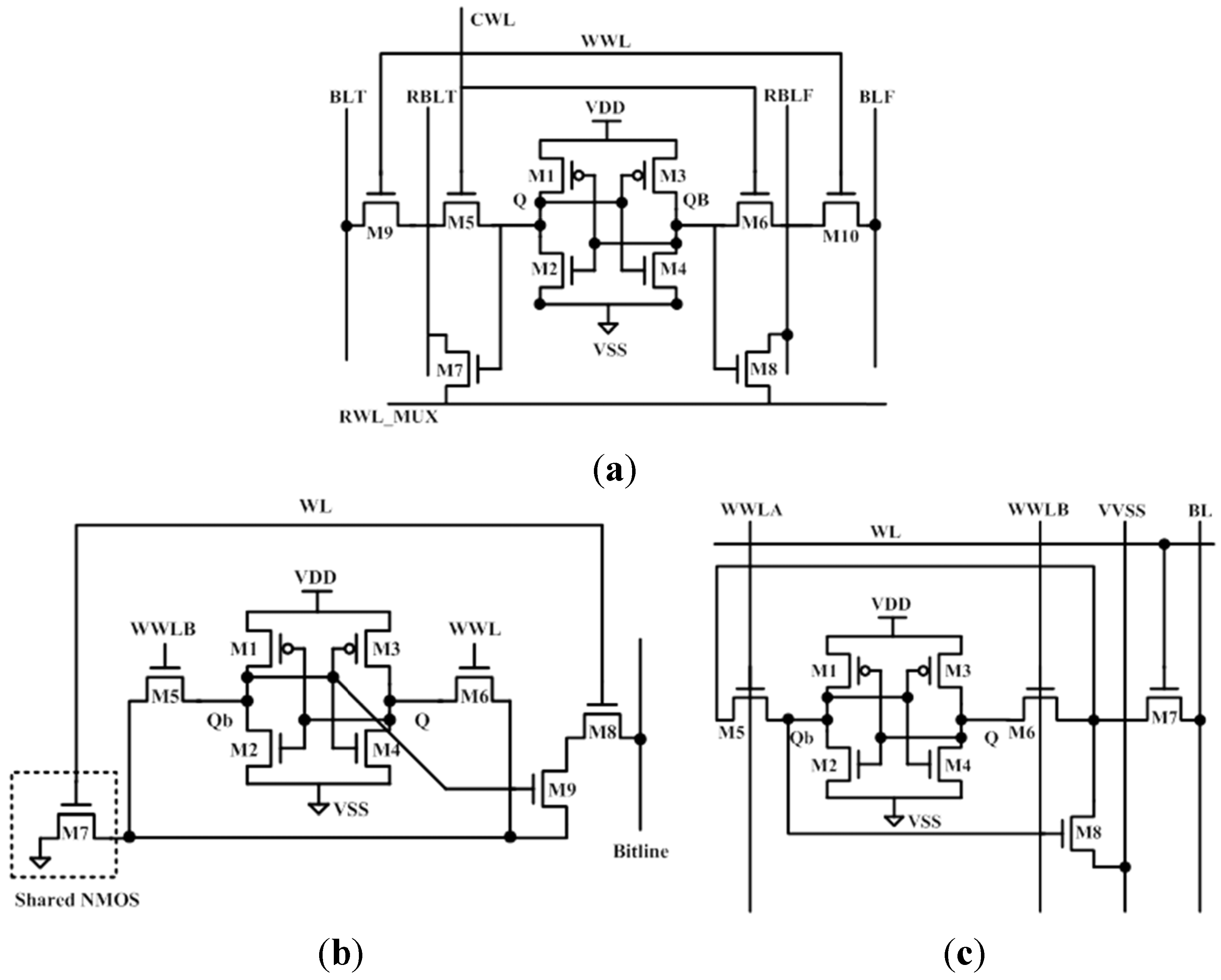

2. Subthreshold Bitcells Topologies

3. Limitations of Available Bitcells

3.1. SRAM Half-Select-Issue in Write Operation

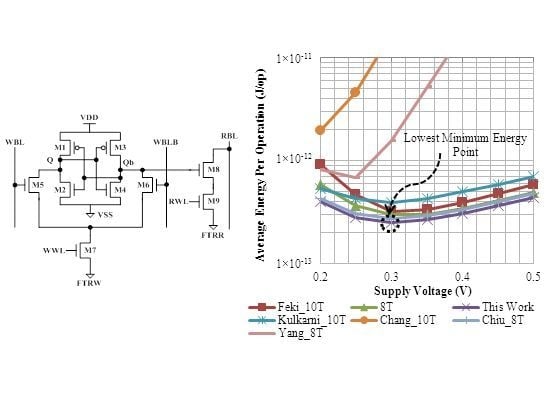

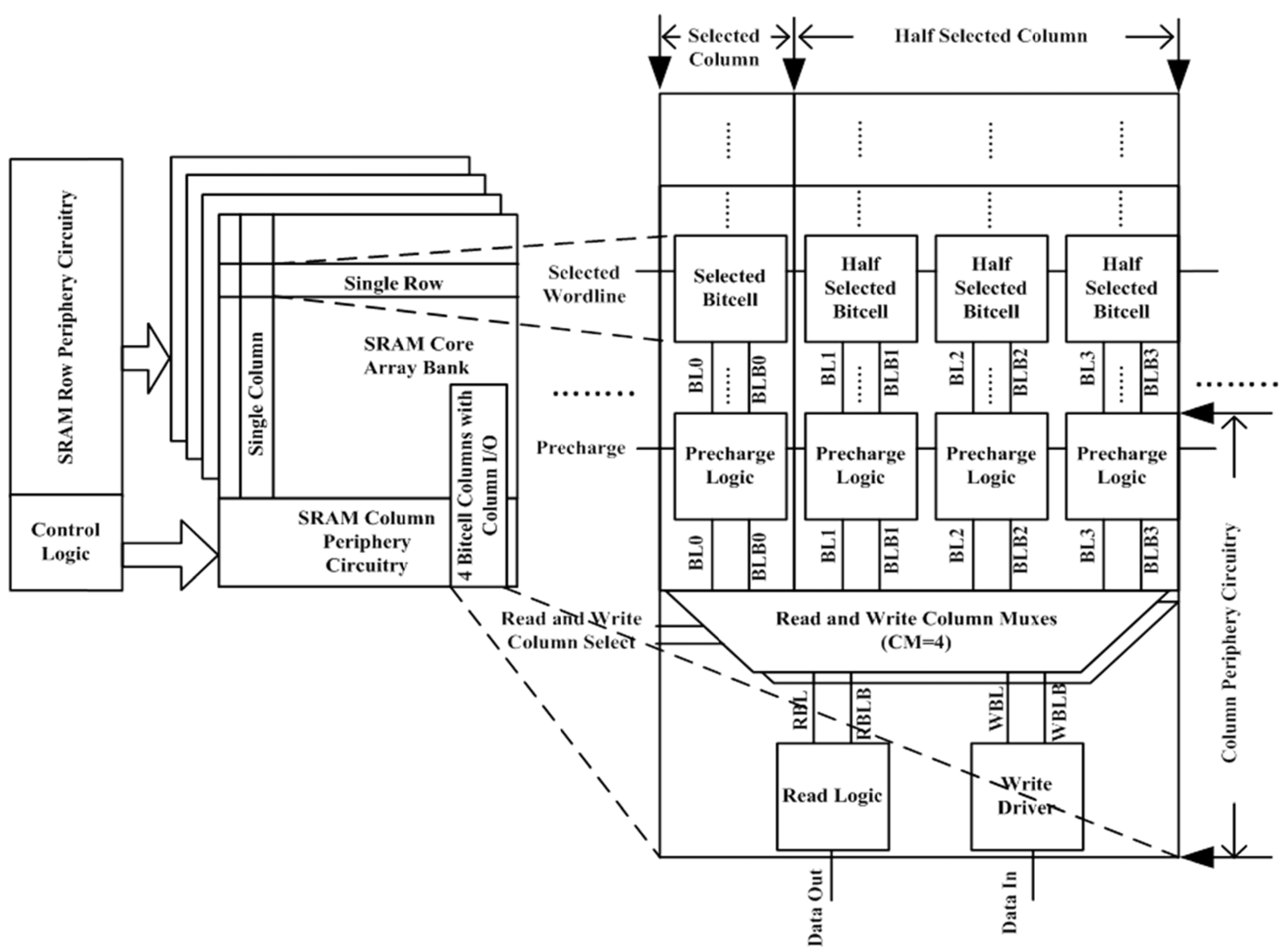

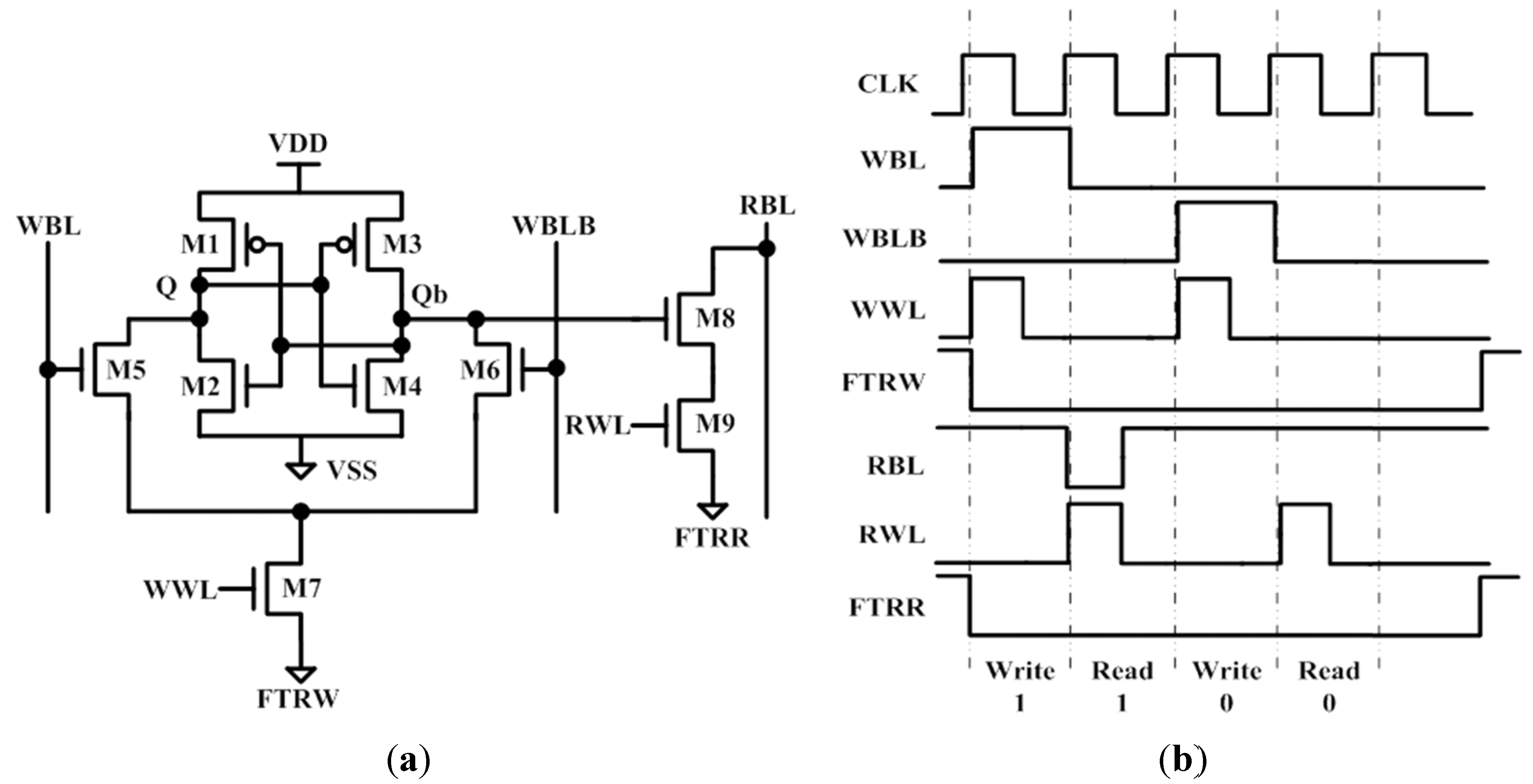

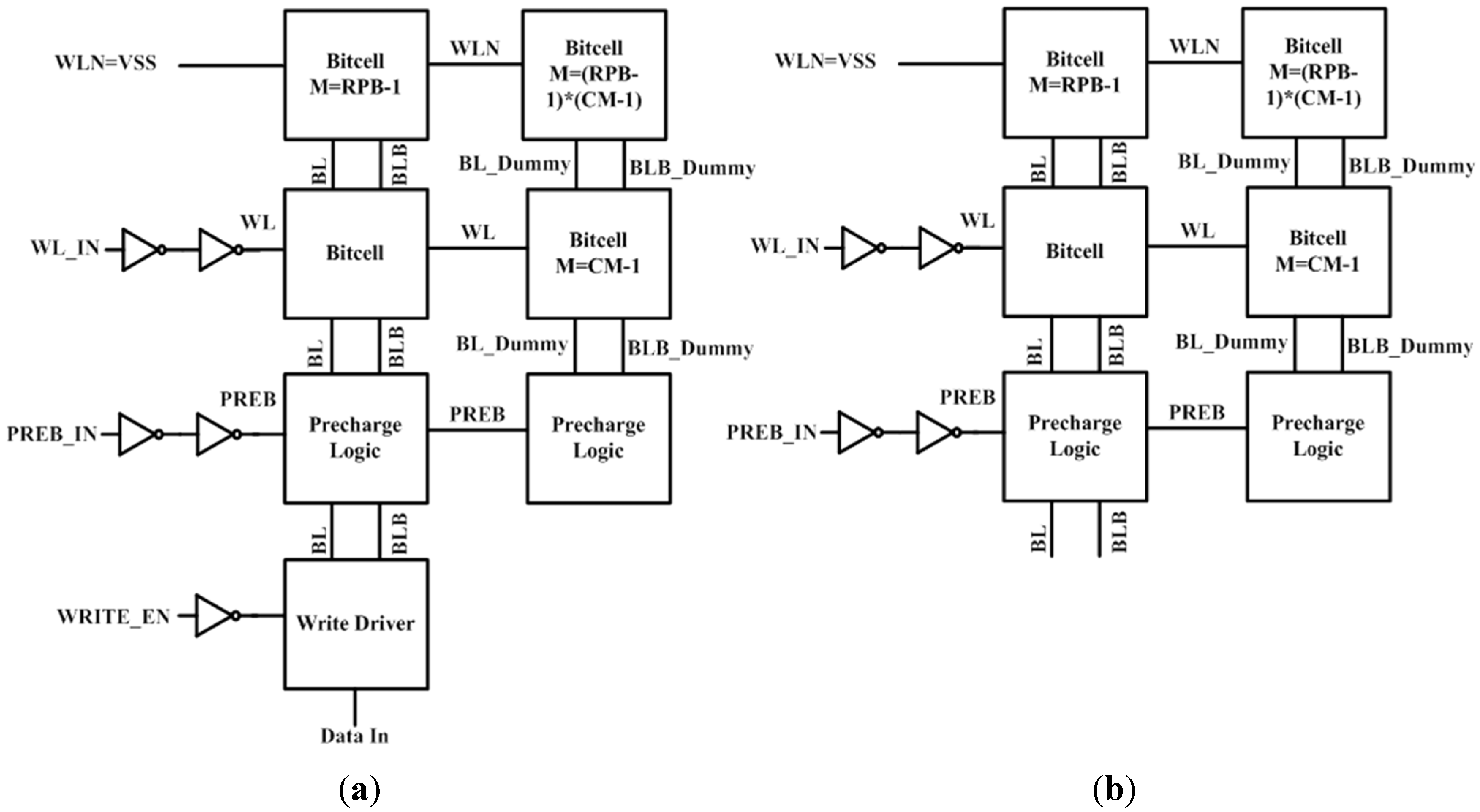

4. Proposed 9T Bitcell

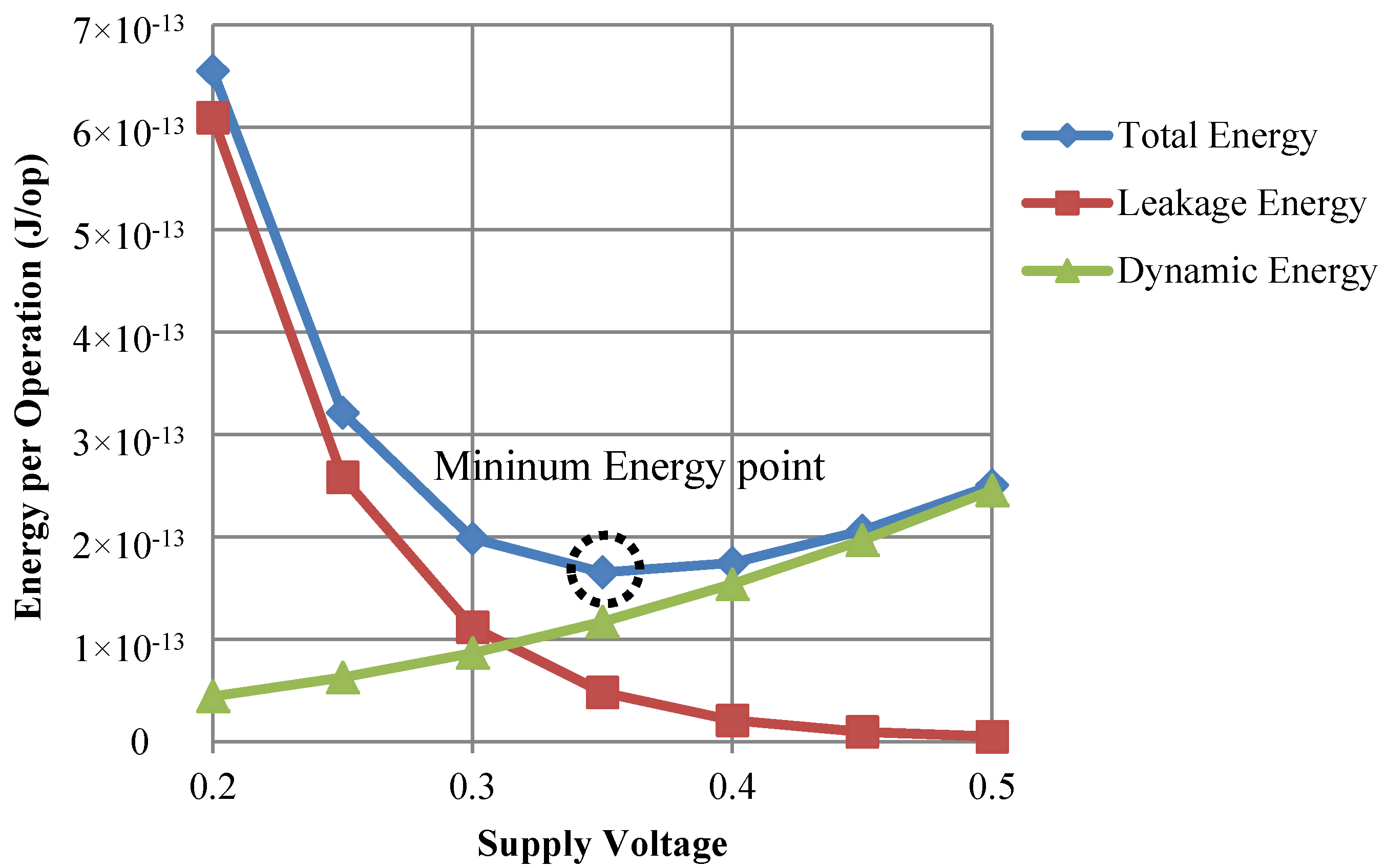

5. Minimum Energy per Operation of Subthreshold SRAMs

5.1. Read-Write Weighted Energy per Operation and Fraction of Read and Write

6. Experimental Setup

6.1. Experimental Assumptions

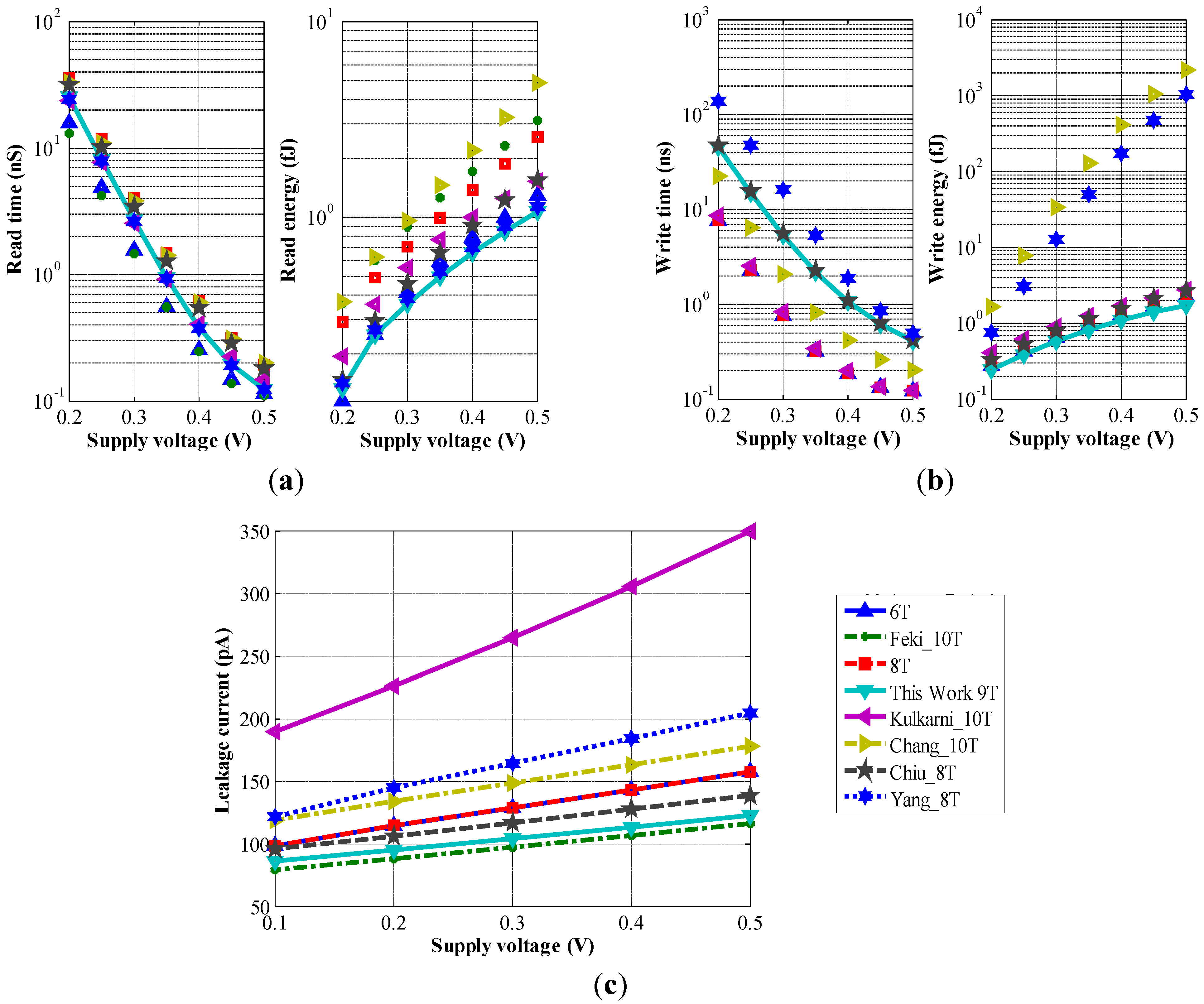

7. Results and Comparisons

| Metrics | 6T | 8T [10] | 10T [8] | 10T [6] | This work | 10T [7] | 8T [9] | 8T [14] |

|---|---|---|---|---|---|---|---|---|

| Read time (μ) | 0.30 | 0.73 | 0.28 | 0.48 | 0.45 | 0.69 | 0.65 | 0.45 |

| Read energy (μ) | 0.82 | 1.46 | 1.79 | 1.19 | 0.71 | 2.26 | 0.96 | 0.75 |

| Write time (μ) | 0.19 | 0.20 | 0.47 | 0.26 | 1.33 | 0.46 | 1.39 | 3.24 |

| Write energy (μ) | 1.35 | 1.36 | 1.24 | 1.98 | 1.21 | 421.71 | 1.69 | 180.67 |

| Leakage current (μ) | 187.8 | 188.2 | 136.1 | 468.4 | 146.1 | 211.8 | 161.9 | 245.3 |

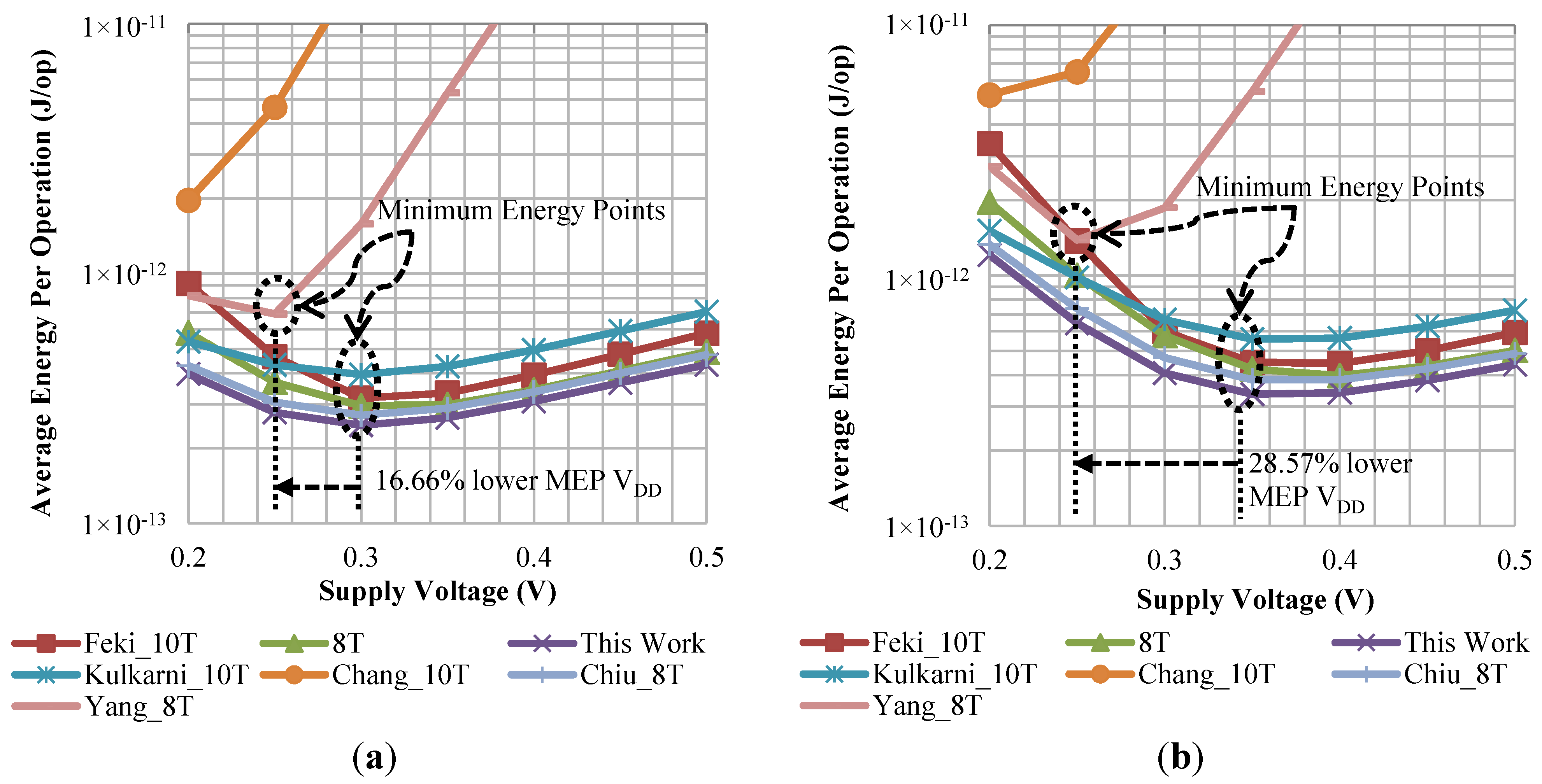

7.1. Comparison of Total Energy per Operation

7.2. MEP vs. Fraction of Read and Write and Comparison Results

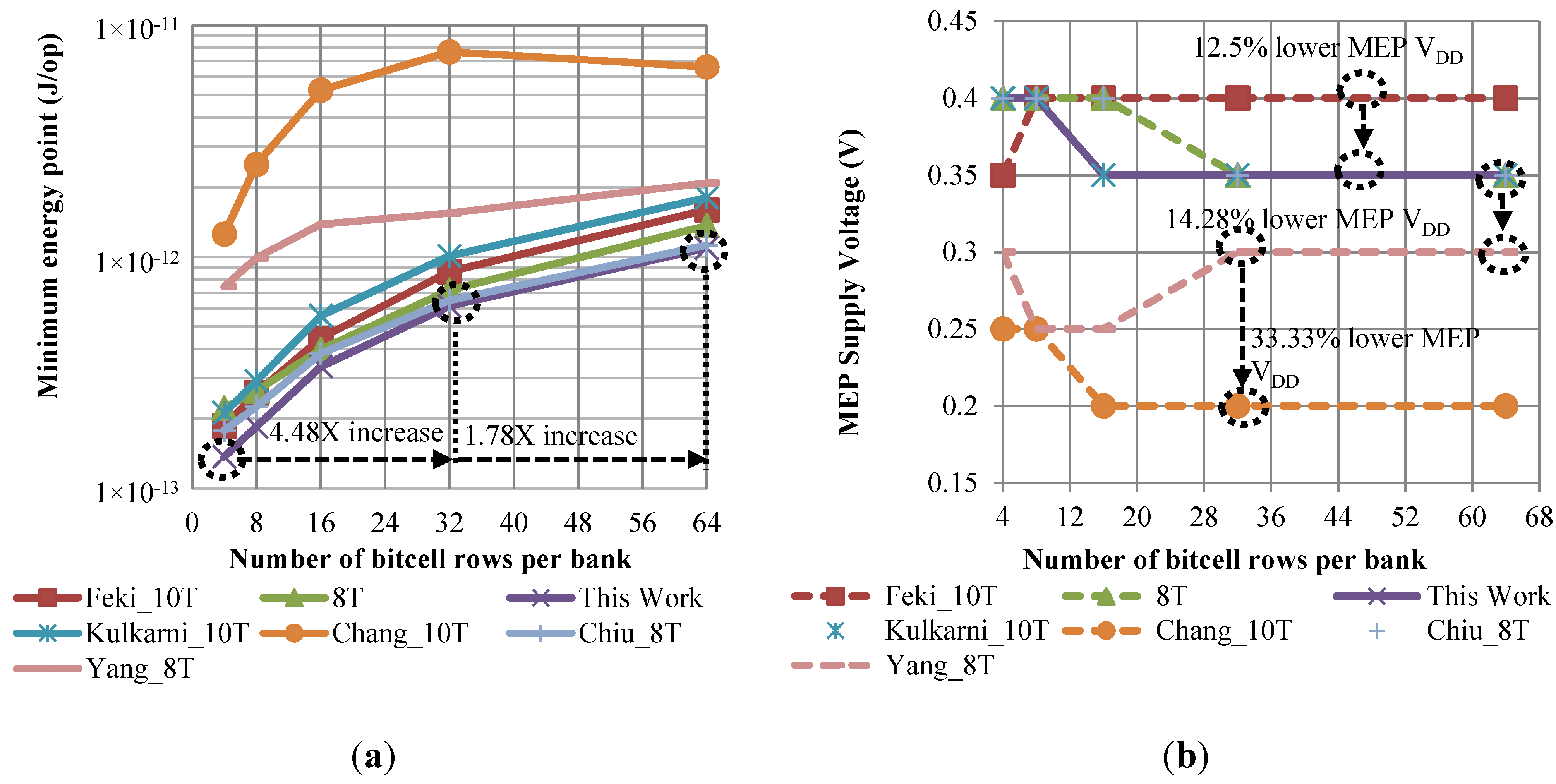

7.3. MEP vs. Number of Bitcell Rows per Bank Comparison Results

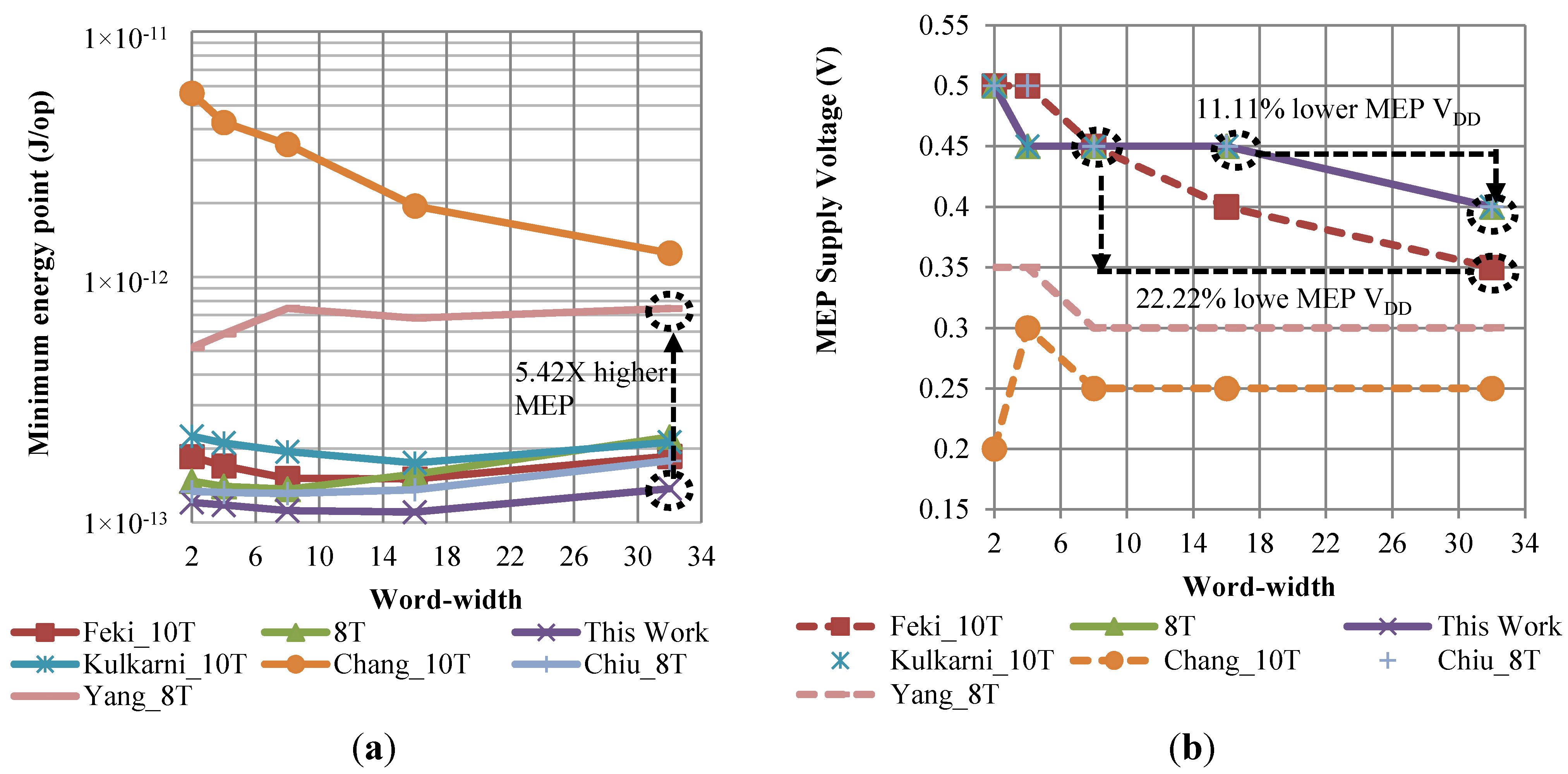

7.4. MEP vs. Word-Width Comparison Results

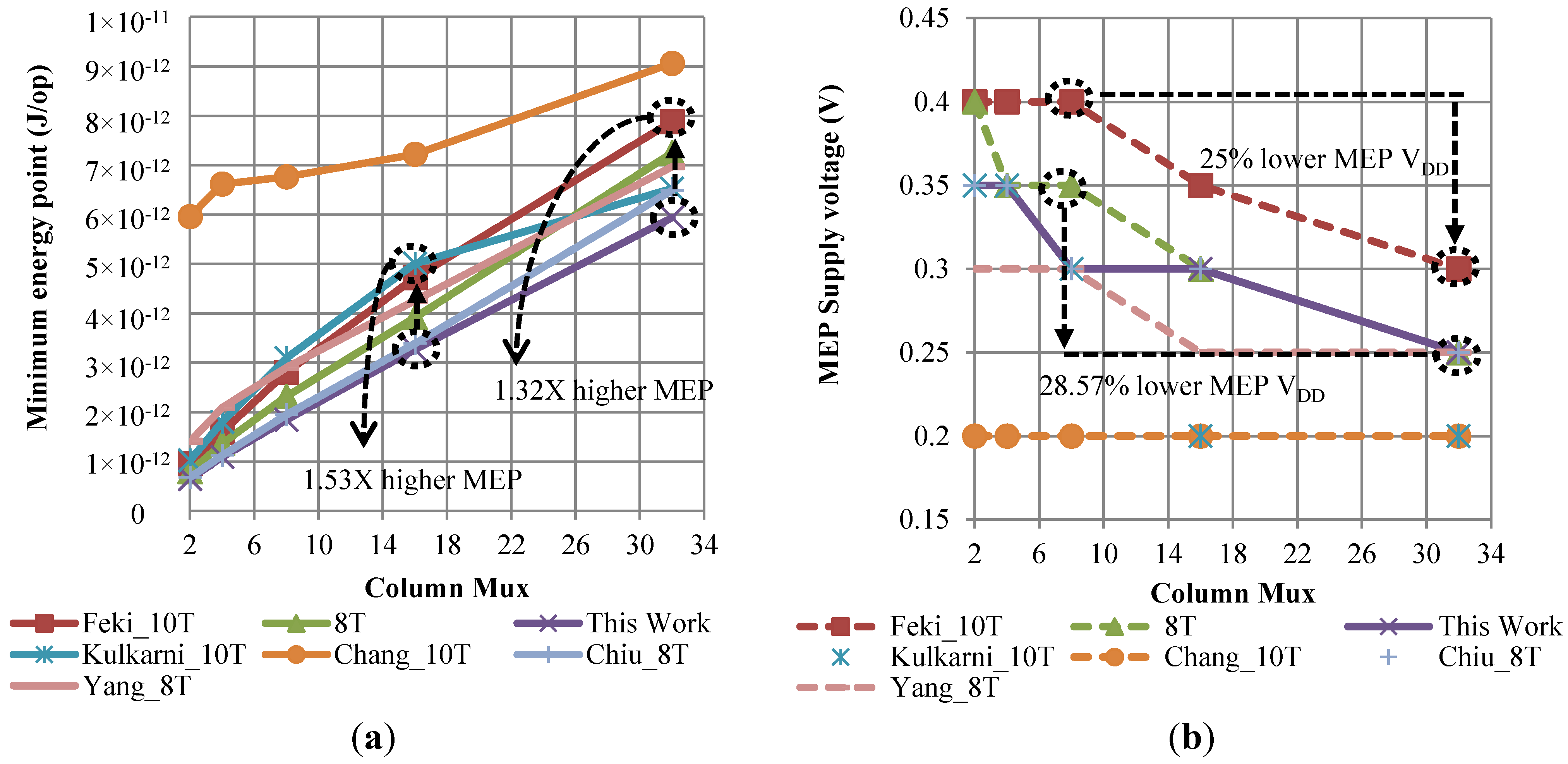

7.5. MEP vs. Column Mux Comparison Results

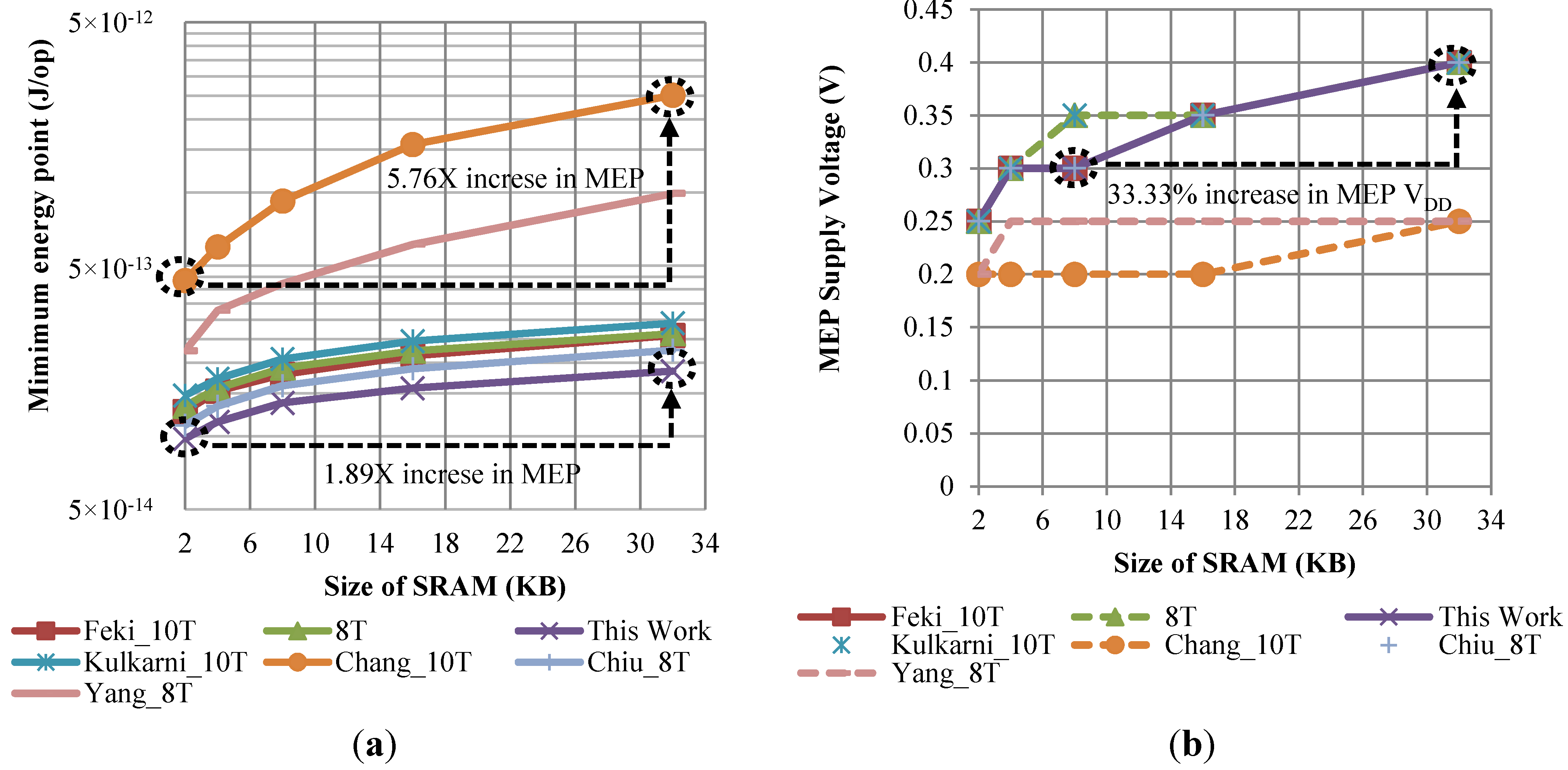

7.6. MEP vs. SRAM Size Comparison Results

8. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Zhang, Y.Q.; Zhang, F.; Shakhsheer, Y.; Silver, J.D.; Klinefelter, A.; Nagaraju, M.; Boley, J.; Pandey, J.; Shrivastava, A.; Carlson, E.J.; et al. A batteryless 19 µW MICS/ISM-band energy harvesting body sensor node SoC for ExG applications. IEEE J. Solid State Circuits 2013, 48, 199–213. [Google Scholar] [CrossRef]

- Chen, G.; Fojtik, M.; Kim, D.; Fick, D.; Park, J.; Seok, M.; Chen, M.-T.; Foo, Z.Y.; Sylvester, D.; Blaauw, D. Millimeter-scale nearly perpetual sensor system with stacked battery and solar cells. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 288–289.

- Wang, A.; Chandrakasan, A.P.; Kosonocky, S.V. Optimal supply and threshold scaling for subthreshold CMOS circuits. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, Pittsburgh, PA, USA, 25–26 April 2002; pp. 5–9.

- Wang, A.; Chandrakasan, A. A 180-mV subthreshold FFT processor using a minimum energy design methodology. IEEE J. Solid State Circuits 2005, 40, 310–319. [Google Scholar] [CrossRef]

- Seevinck, E.; List, F.J.; Lohstroh, J. Static-noise margin analysis of MOS SRAM cells. IEEE J. Solid State Circuits 1987, 22, 748–754. [Google Scholar] [CrossRef]

- Kulkarni, J.P.; Kim, K.; Roy, K. A 160 mV robust schmitt trigger based subthreshold SRAM. IEEE J. Solid State Circuits 2007, 42, 2303–2313. [Google Scholar] [CrossRef]

- Chang, I.-J.; Kim, J.J.; Park, S.P.; Roy, K. A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. IEEE J. Solid State Circuits 2009, 44, 650–658. [Google Scholar]

- Feki, A.; Allard, B.; Turgis, D.; Lafont, J.; Ciampolini, L. Proposal of a new ultra low leakage 10T sub threshold SRAM bitcell. In Proceedings of the 2012 International SoC Design Conference (ISOCC), Jeju Island, Korea, 4–7 November 2012; pp. 470–474.

- Chiu, Y.-W.; Lin, J.-Y.; Tu, M.-H.; Jou, S.-J.; Chuang, C.-Y. 8T Single-ended sub-threshold SRAM with cross-point data-aware write operation. In Proceedings of the 2011 International Symposium on Low Power Electronics and Design (ISLPED), Fukuoka, Japan, 1–3 August 2011; pp. 169–174.

- Verma, N.; Chandrakasan, A.P. A 256 kb 65 nm 8T subthreshold SRAM employing sense-amplifier redundancy. IEEE J. Solid State Circuits 2008, 43, 141–149. [Google Scholar] [CrossRef]

- Chandra, V.; Pietrzyk, C.; Aitken, R. On the efficacy of write-assist techniques in low voltage nanoscale SRAMs. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 8–12 March 2010; pp. 345–350.

- Mann, R.W.; Nalam, S.; Wang, J.J.; Calhoun, B.H. Limits of bias based assist methods in nano-scale 6T SRAM. In Proceedings of the 2010 11th International Symposium on Quality Electronic Design (ISQED), San Jose, CA, USA, 22–24 March 2010; pp. 1–8.

- Kim, T.; Liu, J.; Keane, J.; Kim, C.H. A high-density subthreshold SRAM with data-independent bitline leakage and virtual ground replica scheme. IEEE J. Solid State Circuits 2008, 43, 518–529. [Google Scholar] [CrossRef]

- Yang, H.-I.; Yang, S.-C.; Hsia, M.-C.; Lin, Y.-W.; Chen, C.-C.; Chang, C.-S.; Lin, G.-C.; Chen, Y.-N.; Chuang, C.-T.; Hwang, W.; et al. A high-performance low VMIN 55 nm 512 Kb disturb-free 8T SRAM with adaptive VVSS control. In Proceedings of the 2011 IEEE International SOC Conference (SOCC), Taipei, Taiwan, 26–28 September 2011; pp. 197–200.

- Slayman, C. Soft errors—Past history and recent discoveries. In Proceedings of the 2010 IEEE International Integrated Reliability Workshop Final Report (IRW), Stanford Sierra, CA, USA, 17–21 October 2010; pp. 25–30.

- Banerjee, A.; Calhoun, B.H. An ultra low energy 9T half-select-free subthreshold SRAM bitcell. In Proceedings of the 2013 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Monterey, CA, USA, 7–10 October 2013; pp. 1–2.

- Kim, H.; Kim, S.; van Helleputte, N.; Artes, A.; Konijnenburg, M.; Huisken, J.; van Hoof, C.; Yazicioglu, R.F. A configurable and low-power mixed signal SoC for portable ECG monitoring applications. IEEE Trans. Biomed. Circuits Syst. 2013, 8, 257–267. [Google Scholar] [CrossRef]

- Yan, L.; Bae, J.; Lee, S.; Roh, T.; Song, K.; Yoo, H.-J. A 3.9 mW 25-electrode reconfigured sensor for wearable cardiac monitoring system. IEEE J. Solid State Circuits 2011, 46, 353–364. [Google Scholar] [CrossRef]

© 2014 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Banerjee, A.; Calhoun, B.H. An Ultra-Low Energy Subthreshold SRAM Bitcell for Energy Constrained Biomedical Applications. J. Low Power Electron. Appl. 2014, 4, 119-137. https://doi.org/10.3390/jlpea4020119

Banerjee A, Calhoun BH. An Ultra-Low Energy Subthreshold SRAM Bitcell for Energy Constrained Biomedical Applications. Journal of Low Power Electronics and Applications. 2014; 4(2):119-137. https://doi.org/10.3390/jlpea4020119

Chicago/Turabian StyleBanerjee, Arijit, and Benton H. Calhoun. 2014. "An Ultra-Low Energy Subthreshold SRAM Bitcell for Energy Constrained Biomedical Applications" Journal of Low Power Electronics and Applications 4, no. 2: 119-137. https://doi.org/10.3390/jlpea4020119

APA StyleBanerjee, A., & Calhoun, B. H. (2014). An Ultra-Low Energy Subthreshold SRAM Bitcell for Energy Constrained Biomedical Applications. Journal of Low Power Electronics and Applications, 4(2), 119-137. https://doi.org/10.3390/jlpea4020119