MOS Current Mode Logic Near Threshold Circuits †

Abstract

:1. Introduction

2. Background

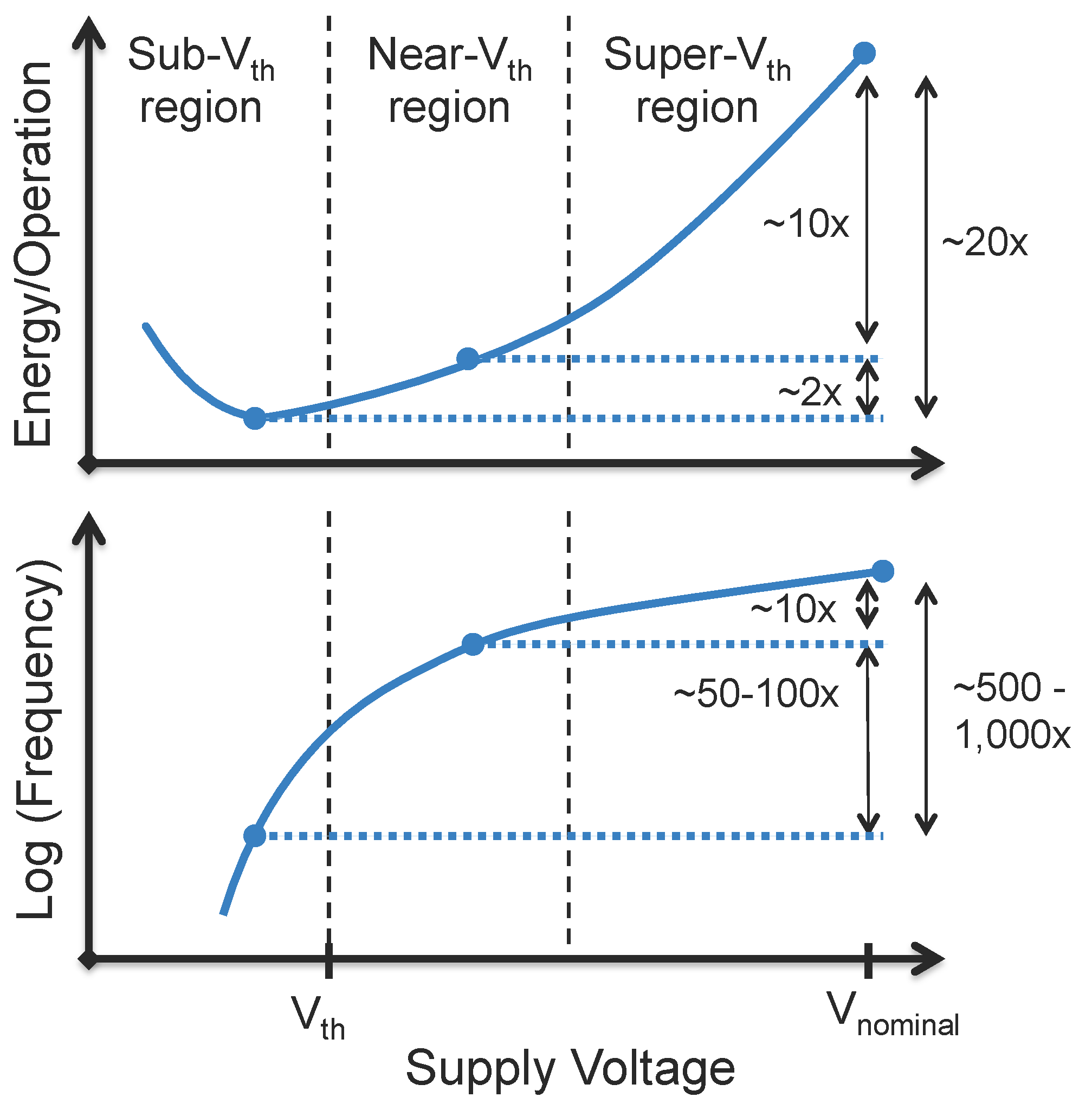

2.1. Near Threshold Circuits

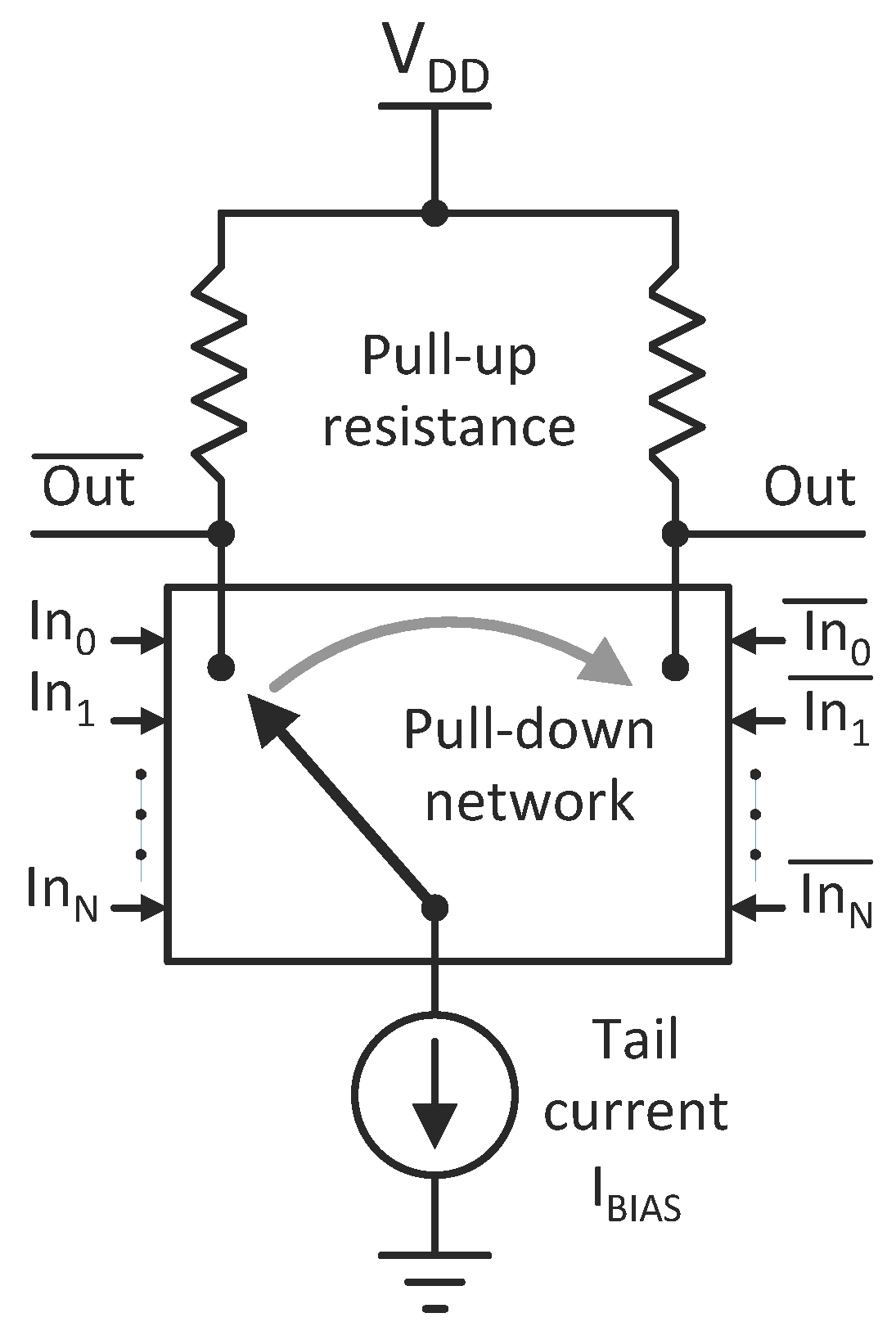

2.2. MCML Circuits

2.2.1. Power Efficiency of MCML

2.2.2. High Speed of MCML

2.2.3. Low Noise Environment of MCML

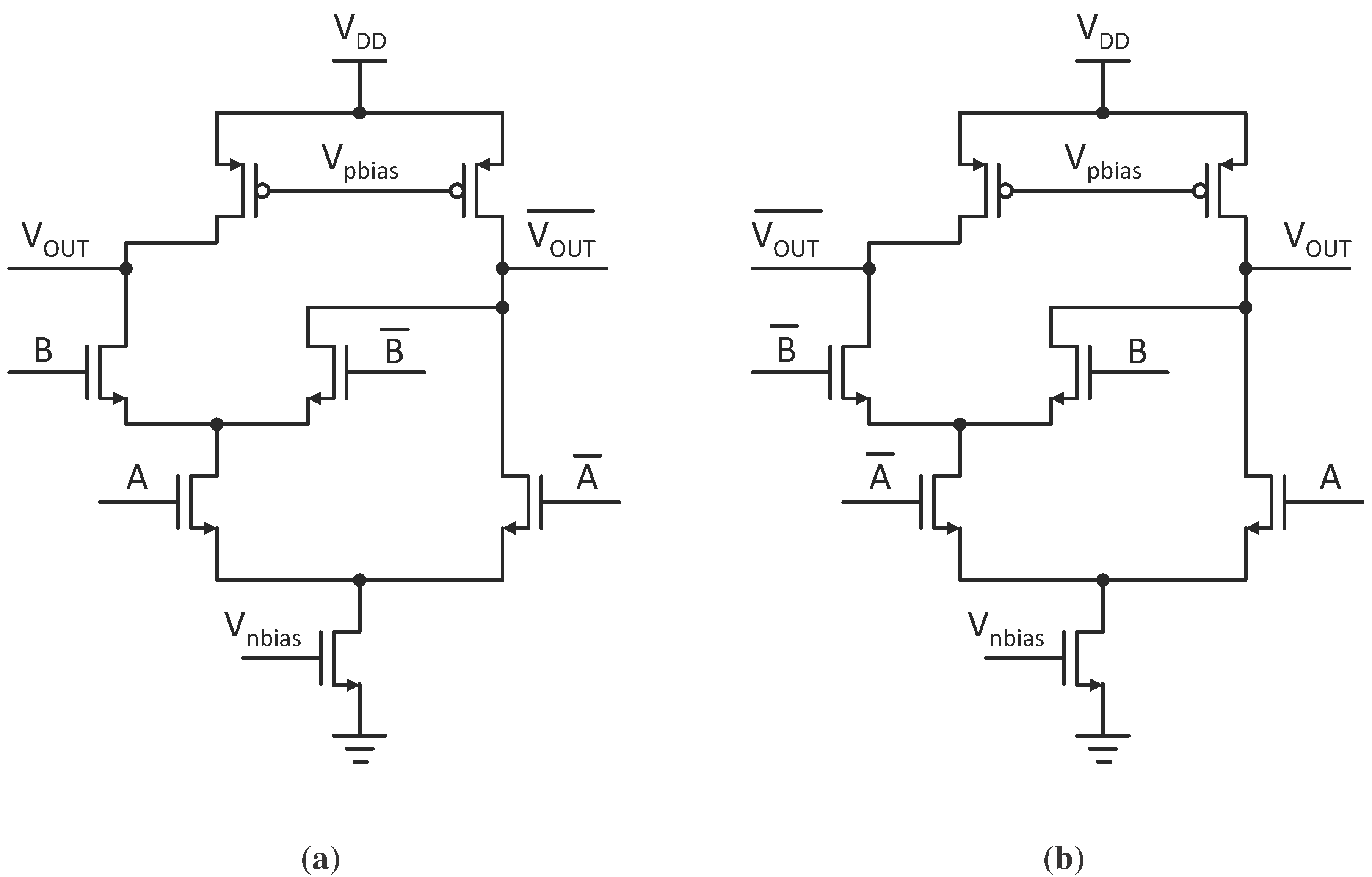

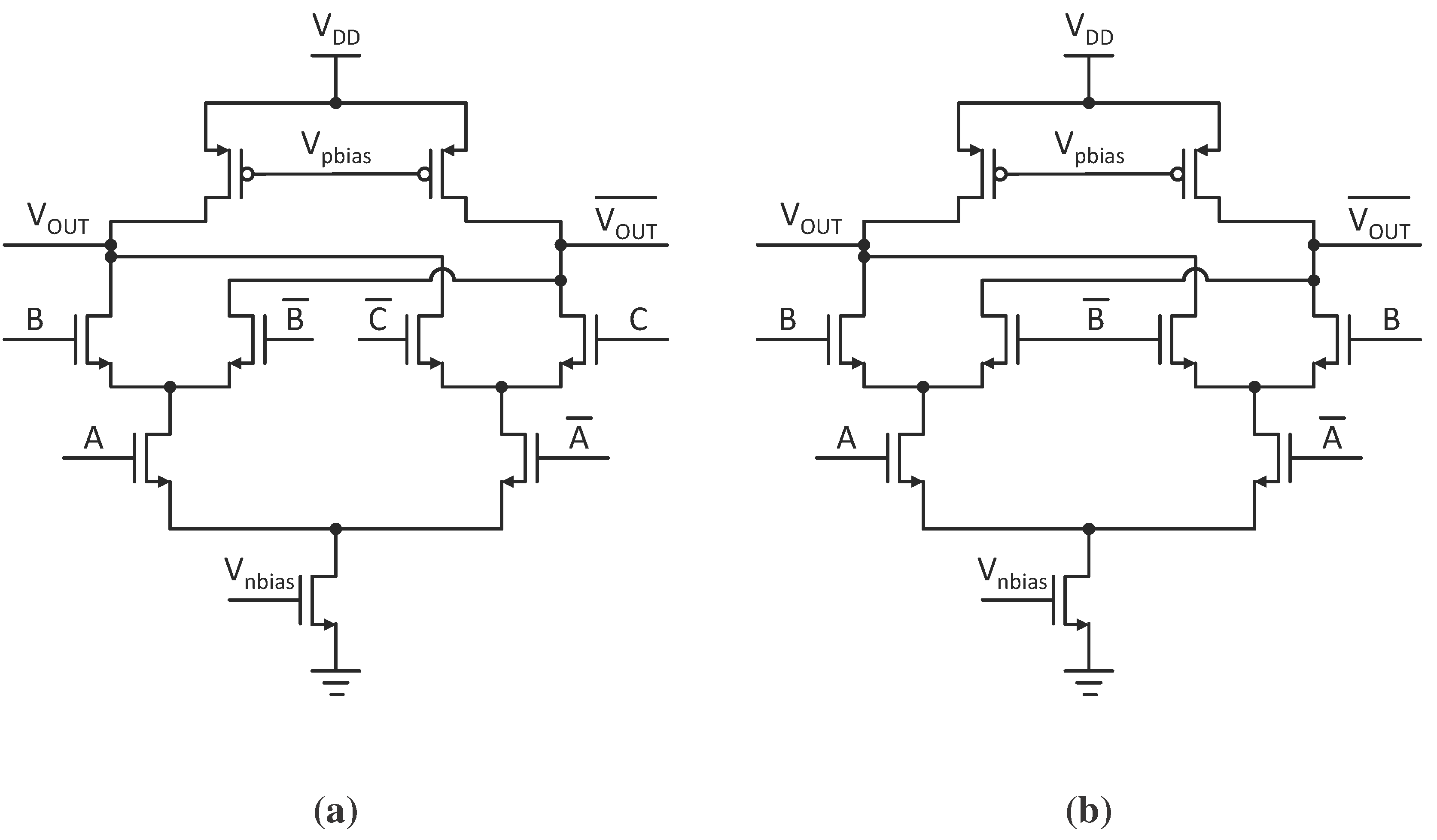

2.2.4. Logic Gates

3. Combination of MCML and NTC

3.1. MCML with NTC

| Standard CMOS | CMOS with NTC | Standard MCML | MCML with NTC | |

|---|---|---|---|---|

| Speed | S | Up to | Up to S | |

| Energy consumption | E | ≈E (also when idle) | ≈ (also when idle) | |

| Power network inductive noise | ≈ | ≈N | ≈N | ≈ |

| Variations | Standard sensitivity | variations can cause timing failures | Sensitivity to mismatch | mismatch can cause logical failures |

3.2. Sensitivity to Process Variation of MCML with NTC

3.3. Characterization of Basic MCML with NTC Gates

| Gate type | Technology | Delay (ps) | Dynamic power (nW) | Static power (nW) | Supply voltage (mV) |

|---|---|---|---|---|---|

| NAND gate | CMOS with NTC | 120 | 2,270 | 0.150 | 400 |

| MCML with NTC | 99 | 800 | 800 | 400 | |

| NOR gate | CMOS with NTC | 112 | 1,600 | 0.090 | 400 |

| MCML with NTC | 89 | 1,200 | 1,200 | 400 | |

| XOR gate | CMOS with NTC | 267 | 2,600 | 1.225 | 400 |

| MCML with NTC | 147 | 800 | 800 | 400 |

4. Simulation Setup

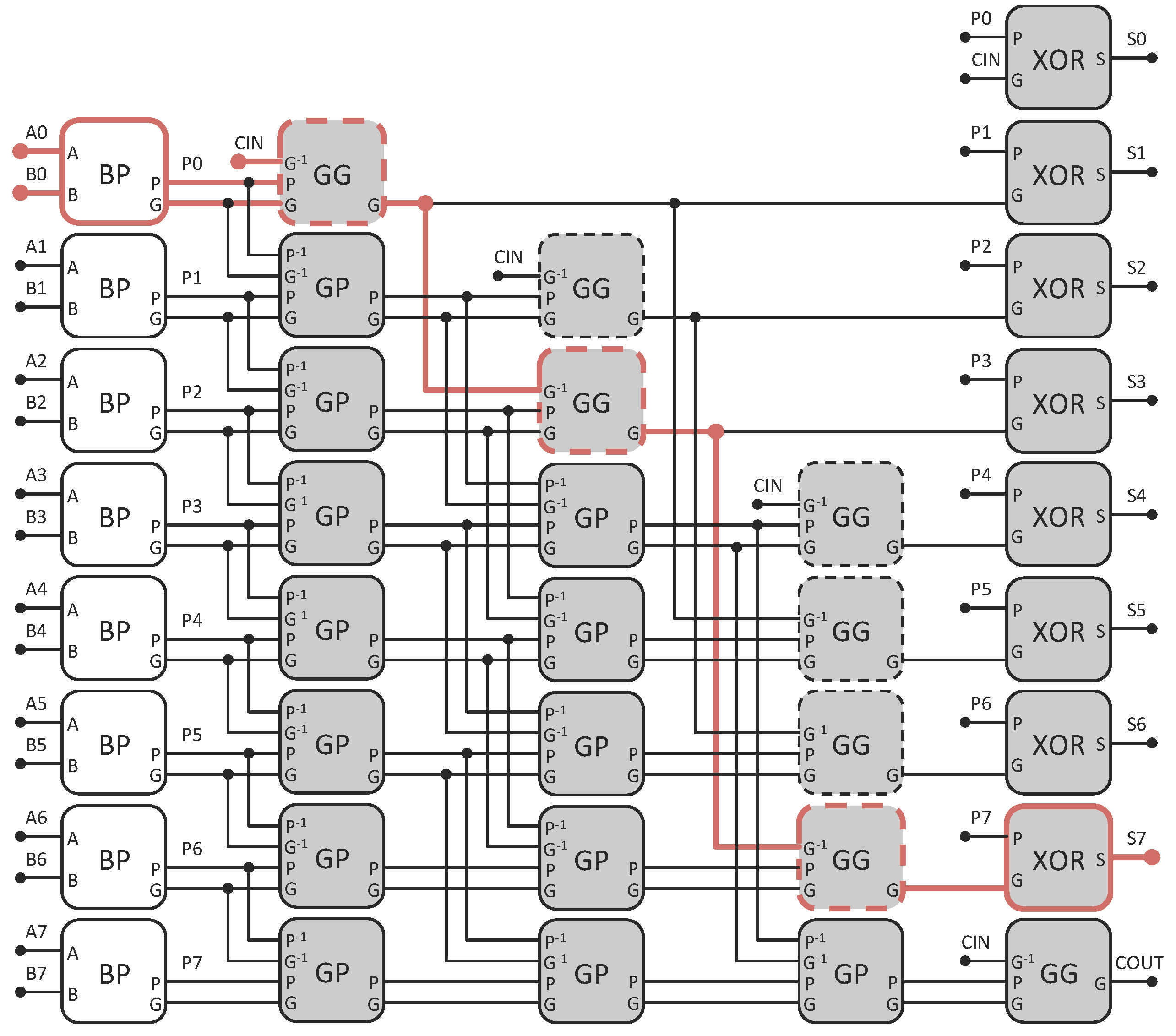

4.1. Description of Test Circuit

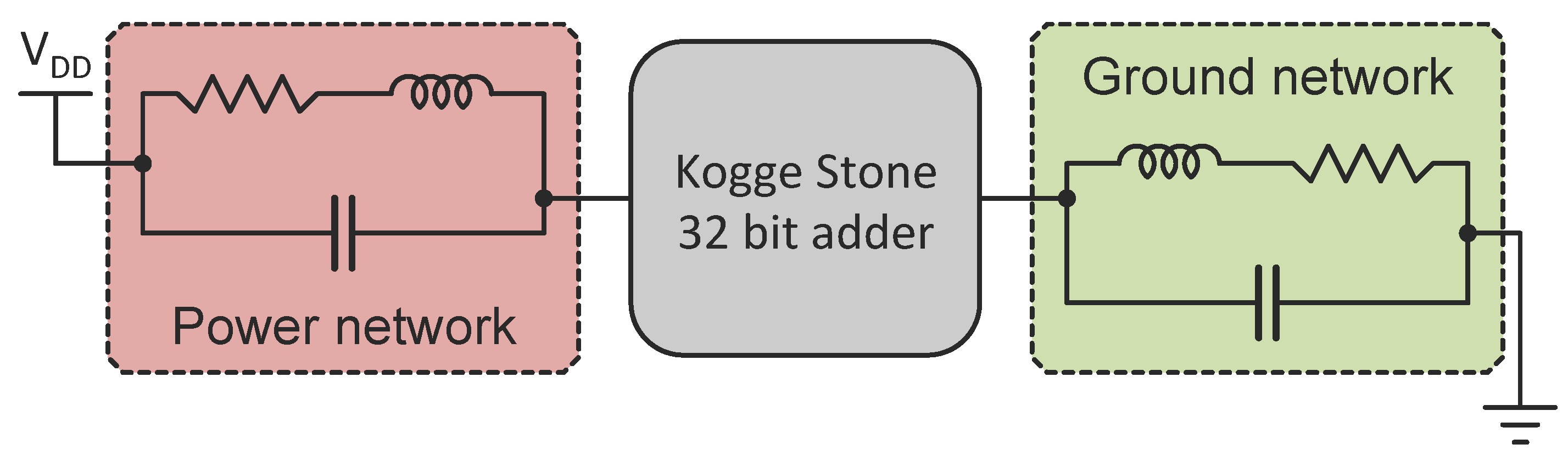

4.2. Power Simulation Setup

4.3. Noise Simulation Setup

5. Simulation Results

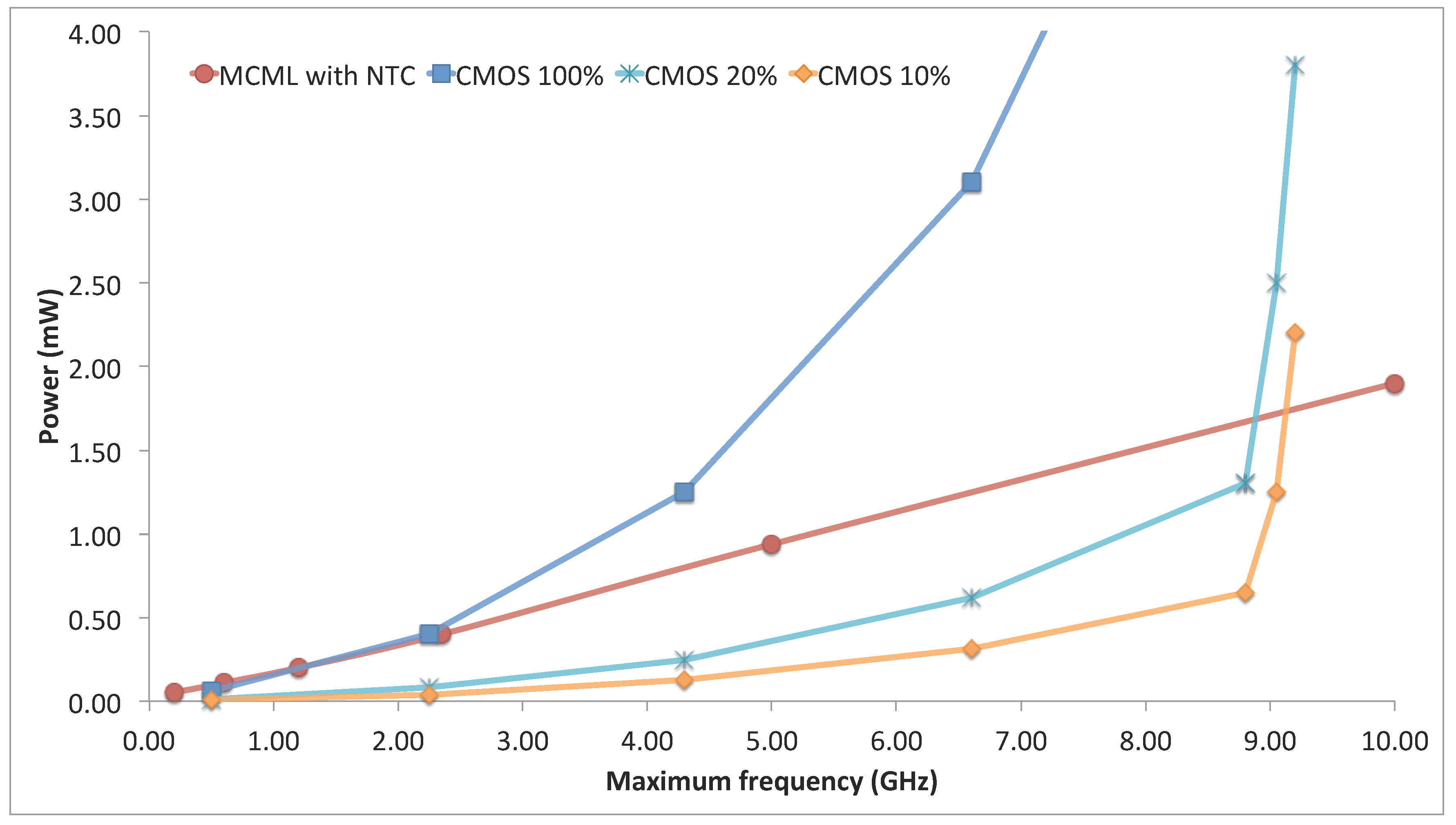

5.1. Power/Speed

5.2. Noise

| Power network parasitic impedances | Noise induced on power network (mV) | ||||

|---|---|---|---|---|---|

| Resistance (ohm) | Capaitance (fF) | Inductance (nH) | MCML | CMOS | Ratio |

| absolute value | absolute value | ||||

| 2 | 50 | 1 | 0.56 | 6.27 | 11 |

| 2 | 50 | 2 | 0.94 | 9.92 | 11 |

| 2 | 50 | 4 | 0.70 | 14.64 | 21 |

| 2 | 100 | 1 | 1.28 | 6.19 | 5 |

| 2 | 100 | 2 | 0.95 | 9.14 | 10 |

| 2 | 100 | 4 | 1.81 | 13.51 | 7 |

| 2 | 200 | 1 | 0.55 | 6.21 | 11 |

| 2 | 200 | 2 | 0.93 | 9.96 | 11 |

| 2 | 200 | 4 | 0.66 | 12.56 | 19 |

| 5 | 50 | 1 | 1.32 | 6.50 | 5 |

| 5 | 50 | 2 | 0.84 | 9.75 | 12 |

| 5 | 50 | 4 | 1.71 | 14.63 | 9 |

| 5 | 100 | 1 | 0.51 | 6.52 | 13 |

| 5 | 100 | 2 | 0.93 | 9.29 | 10 |

| 5 | 100 | 4 | 0.72 | 13.24 | 18 |

| 5 | 200 | 1 | 1.25 | 6.60 | 5 |

| 5 | 200 | 2 | 0.83 | 10.02 | 12 |

| 5 | 200 | 4 | 1.61 | 12.16 | 8 |

6. Conclusions

Acknowledgements

Conflicts of Interest

References

- Salman, E.; Friedman, E.G. High Performance Integrated Circuit Design; McGraw-Hill Publisher: New York, NY, USA, 2012. [Google Scholar]

- Kaul, H.; Anders, M.; Hsu, S.; Agarwal, A.; Krishnamurthy, R.; Borkar, S. Near-Threshold Voltage (NTV) Design: Opportunities and Challenges. In Proceedings of the ACM/IEEE Design Automation Conference, San Francisco, CA, USA, 3–7 June 2012; pp. 1149–1154.

- Alioto, M.; Palumbo, G. Feature-Power-Aware Design Techniques for Nanometer MOS Current-Mode Logic Gates: A Design Framework. IEEE Circuits Syst. Mag. 2006, 6, 42–61. [Google Scholar] [CrossRef]

- Jain, S.; Khare, S.; Yada, S.; Ambili, V.; Salihundam, P.; Ramani, S.; Muthukumar, S.; Srinivasan, M.; Kumar, A.; Gb, S.K.; et al. A 280 mV-to-1.2 V Wide-Operating-Range IA-32 Processor in 32 nm CMOS. In Proceedings of the IEEE Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 66–68.

- Dreslinski, R.; Wieckowski, M.; Blaauw, D.; Sylvester, D.; Mudge, T. Near-Threshold Computing: Reclaiming Moore’s Law through Energy Efficient Integrated Circuits. IEEE Proc. 2010, 98, 253–266. [Google Scholar] [CrossRef]

- Islam, A.; Akram, M.; Imran, A.; Hasan, M. Energy Efficient and Process Tolerant Full Adder Design in Near Threshold Region Using FinFET. In Proceedings of the International Symposium on Electronic System Design, Bhubaneswar, India, 20–22 December 2010; pp. 56–60.

- Hassan, H.; Anis, M.; Elmasry, M. MOS Current Mode Logic: Design, Optimization, and Variability. In Proceedings of the IEEE International SOC Conference, Santa Clara, CA, USA, 12–15 September 2004; pp. 247–250.

- Hassan, H.; Anis, M.; Elmasry, M. MOS Current Mode Circuits: Analysis, Design, and Variability. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2005, 13, 885–898. [Google Scholar] [CrossRef]

- Tang, T.; Friedman, E. Simultaneous Switching Noise in on-Chip CMOS Power Distribution Networks. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2002, 10, 487–493. [Google Scholar] [CrossRef]

- Abdulkarim, O.M.; Shams, M. A Symmetric MOS Current-Mode Logic Universal Gate for High Speed Applications. In Proceedings of the ACM Great Lakes Symposium on VLSI, Lago Maggiore, Italy, 11–13 March 2007; pp. 212–215.

- Mandapati, V.S.R.; Nishanth, P.V.; Paily, R. Study of Transistor Mismatch in Differential Amplifier at 32 nm CMOS Technology. Int. J. Comput. Sci. Issues 2011, 1, 109–115. [Google Scholar]

- Kuhn, K. Reducing Variation in Advanced Logic Technologies: Approaches to Process and Design for Manufacturability of Nanoscale CMOS. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 471–474.

- Tawfik, S.; Kursun, V. FinFET Technology Development Guidelines for Higher Performance, Lower Power, and Stronger Resilience to Parameter Variations. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Cancun, Mexico, 2–5 August 2009; pp. 431–434.

- Cao, Y.K. Predictive Technology Models. Available online: http://ptm.asu.edu/ (accessed on 29 April 2014).

- Kogge, P.M.; Stone, H.S. A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Equations. IEEE Trans. Comput. 1973, C-22, 786–793. [Google Scholar] [CrossRef]

- The International Technology Roadmap for Semiconductors. Available online: http://www.itrs.net/ (accessed on 29 April 2014).

- Pavlidis, V.F.; Friedman, E.G. Three-Dimensional Integrated Circuit Design; Morgan Kaufmann: Burlington, MA, USA, 2009. [Google Scholar]

© 2014 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Shapiro, A.; Friedman, E.G. MOS Current Mode Logic Near Threshold Circuits. J. Low Power Electron. Appl. 2014, 4, 138-152. https://doi.org/10.3390/jlpea4020138

Shapiro A, Friedman EG. MOS Current Mode Logic Near Threshold Circuits. Journal of Low Power Electronics and Applications. 2014; 4(2):138-152. https://doi.org/10.3390/jlpea4020138

Chicago/Turabian StyleShapiro, Alexander, and Eby G. Friedman. 2014. "MOS Current Mode Logic Near Threshold Circuits" Journal of Low Power Electronics and Applications 4, no. 2: 138-152. https://doi.org/10.3390/jlpea4020138

APA StyleShapiro, A., & Friedman, E. G. (2014). MOS Current Mode Logic Near Threshold Circuits. Journal of Low Power Electronics and Applications, 4(2), 138-152. https://doi.org/10.3390/jlpea4020138