A Physical Unclonable Function Based on a Differential Subthreshold PMOS Array with 9.73 × 10−4 Stabilized BER and 1.3 pJ/bit in 65 nm

Abstract

1. Introduction

2. The Physical Unclonable Function (PUF) Primitive

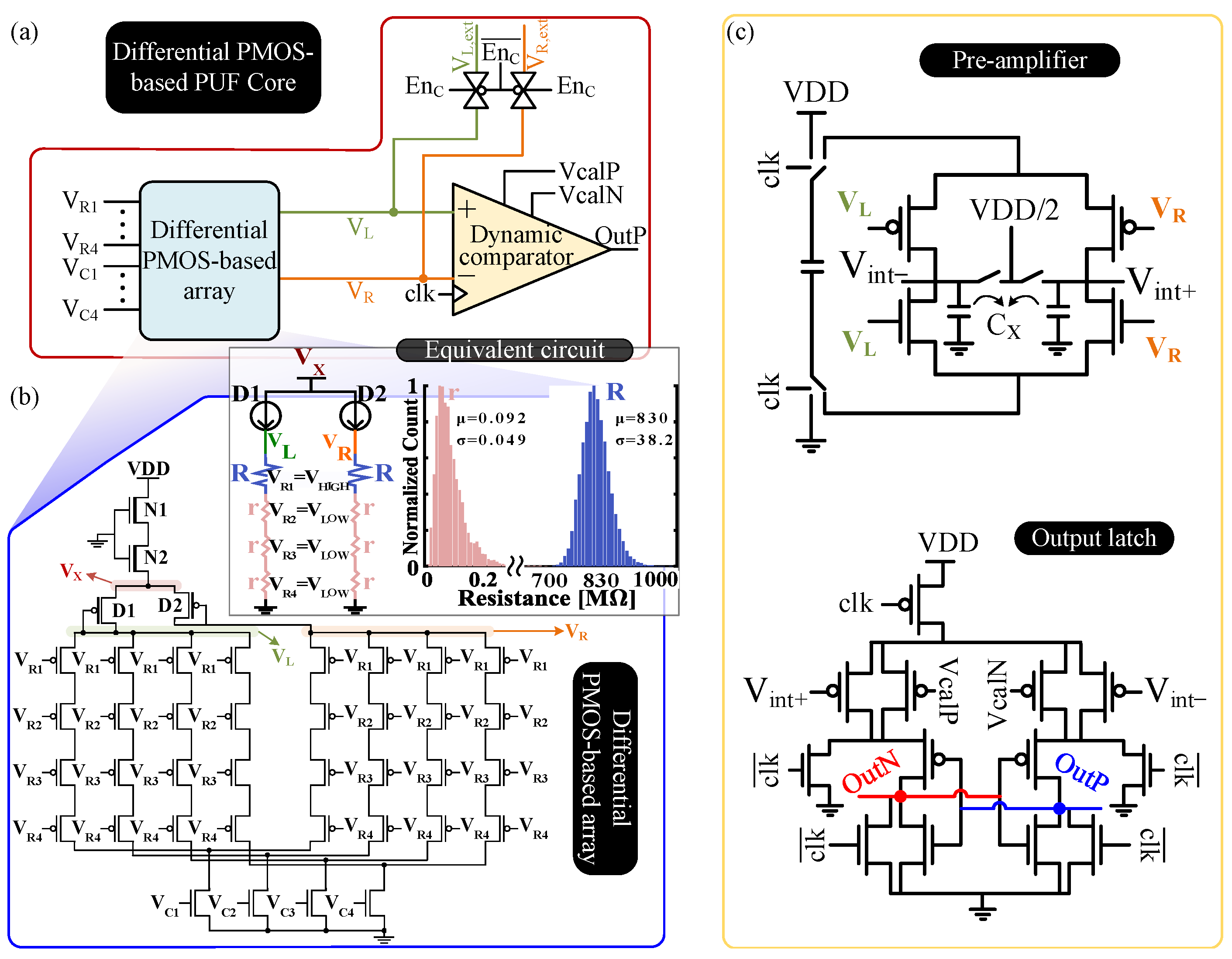

2.1. PUF Core

2.2. Comparator

3. Results

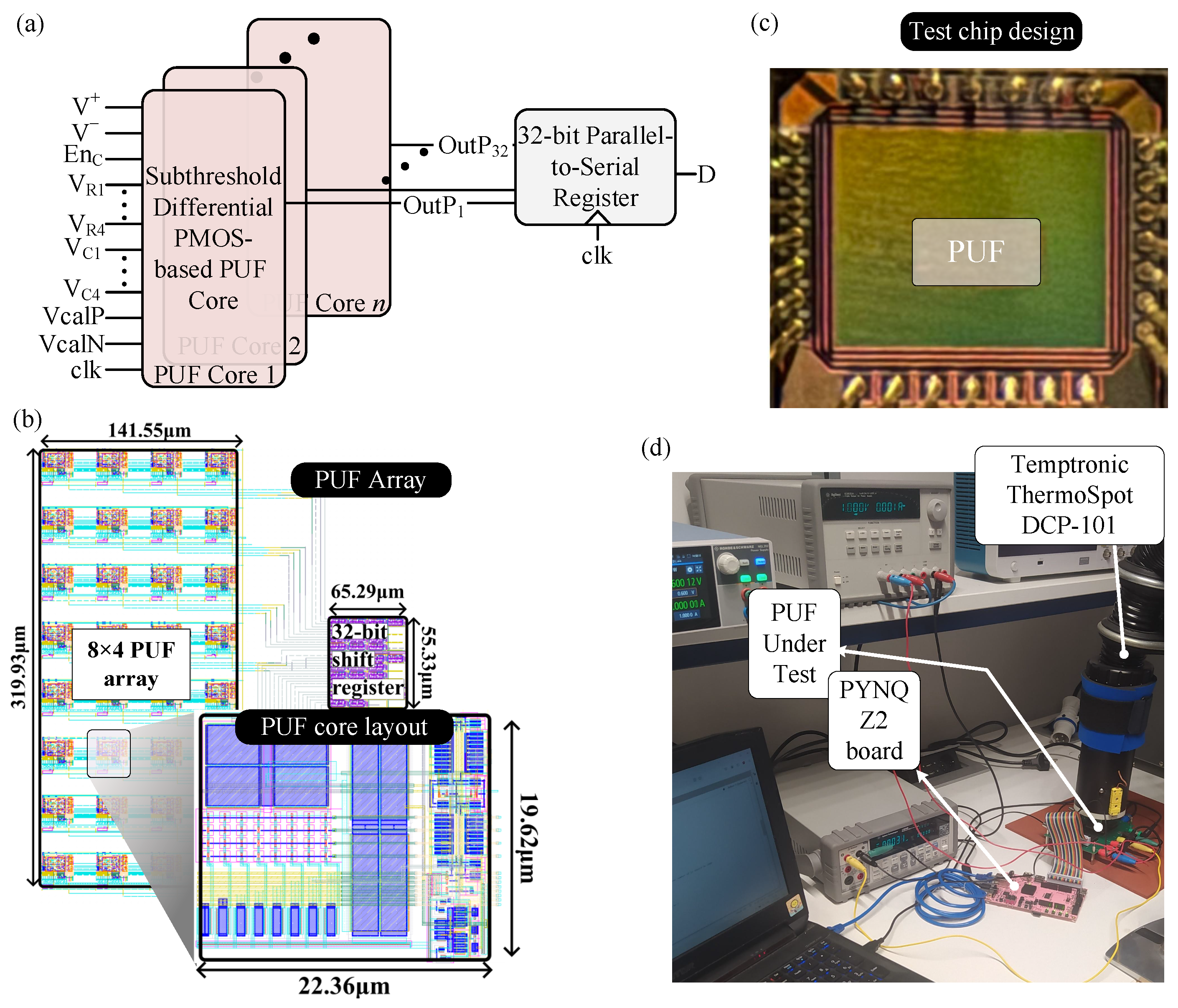

3.1. Test Chip and Measurement Setup

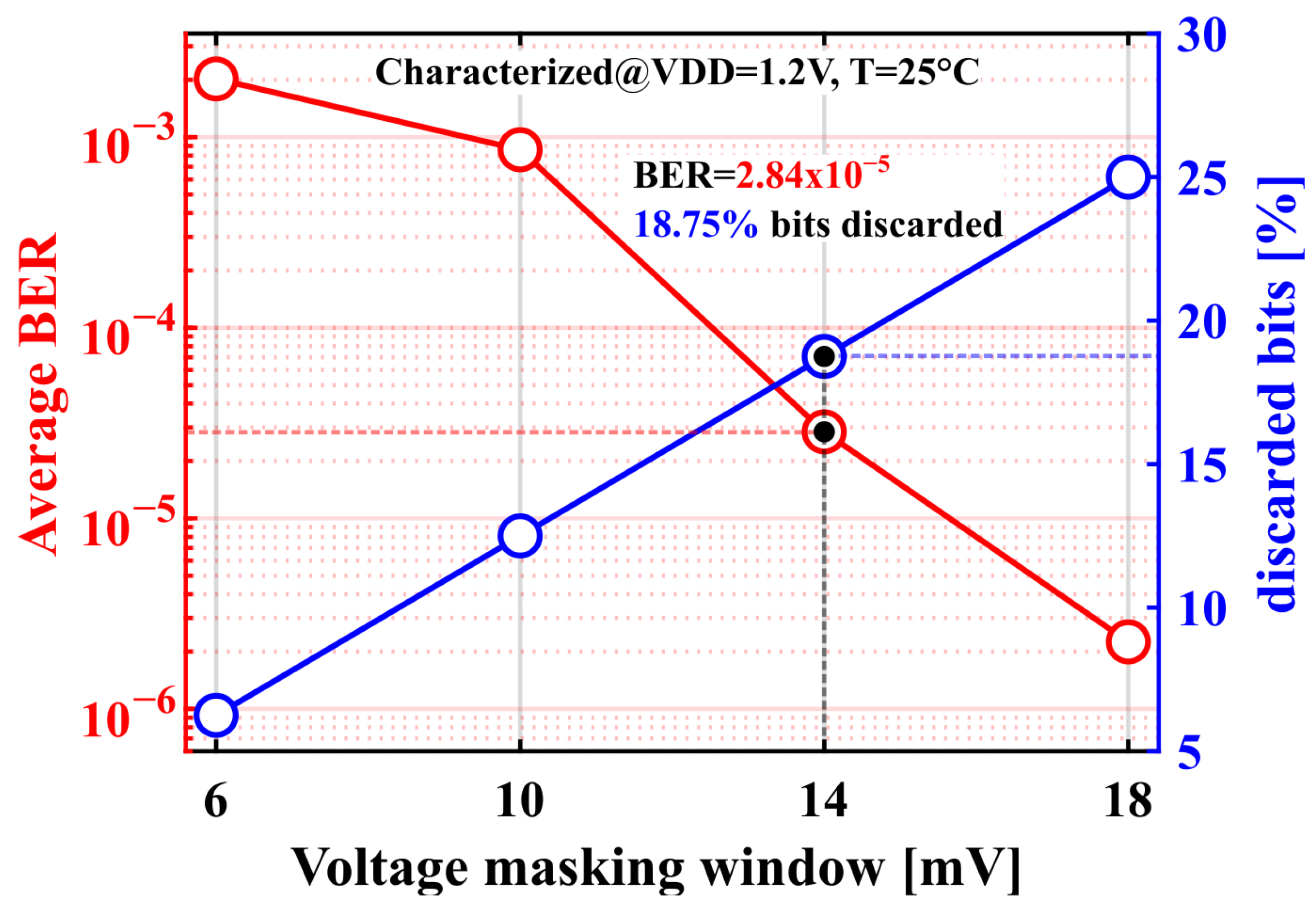

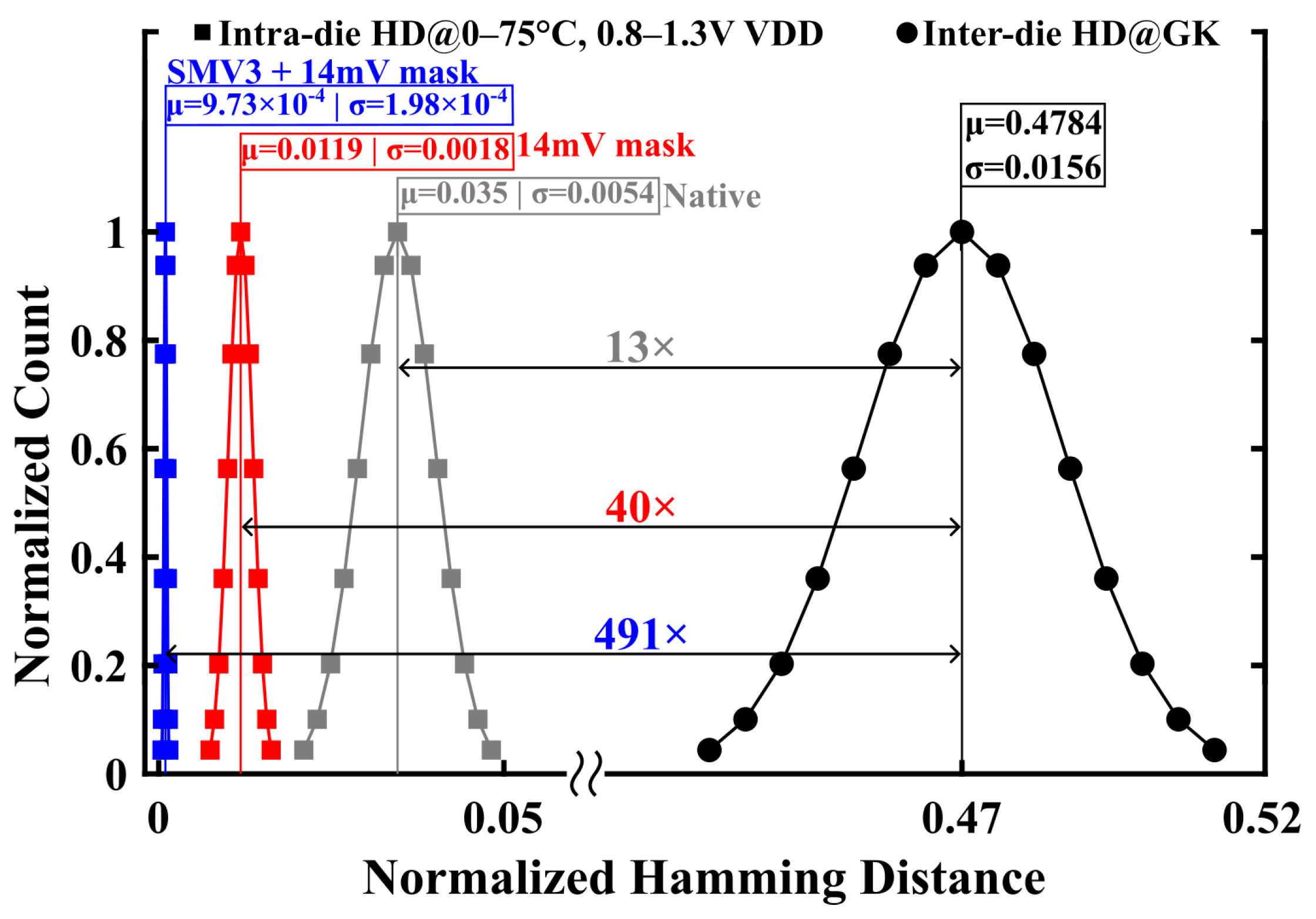

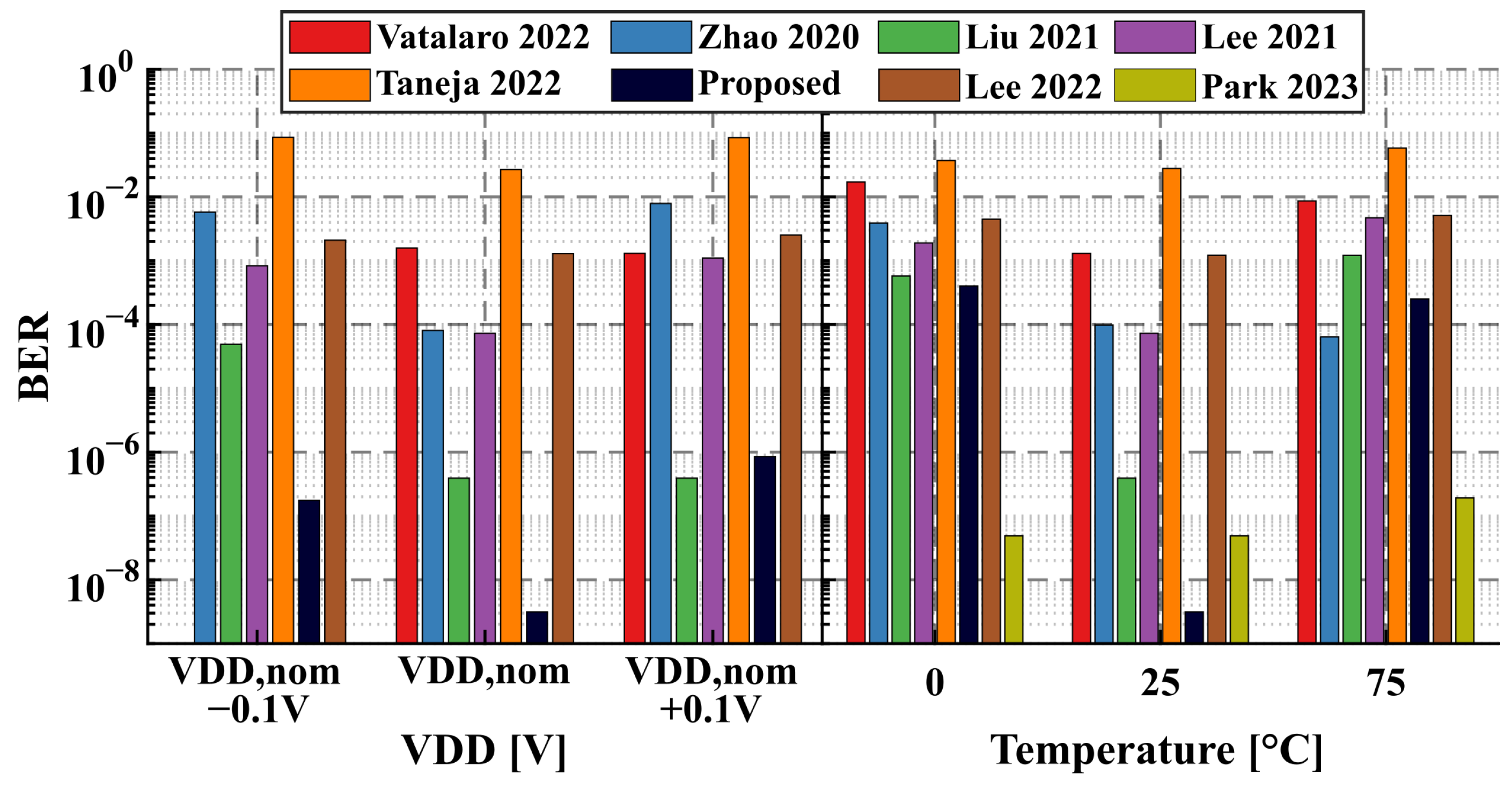

3.2. Bit Error Rate Characterization

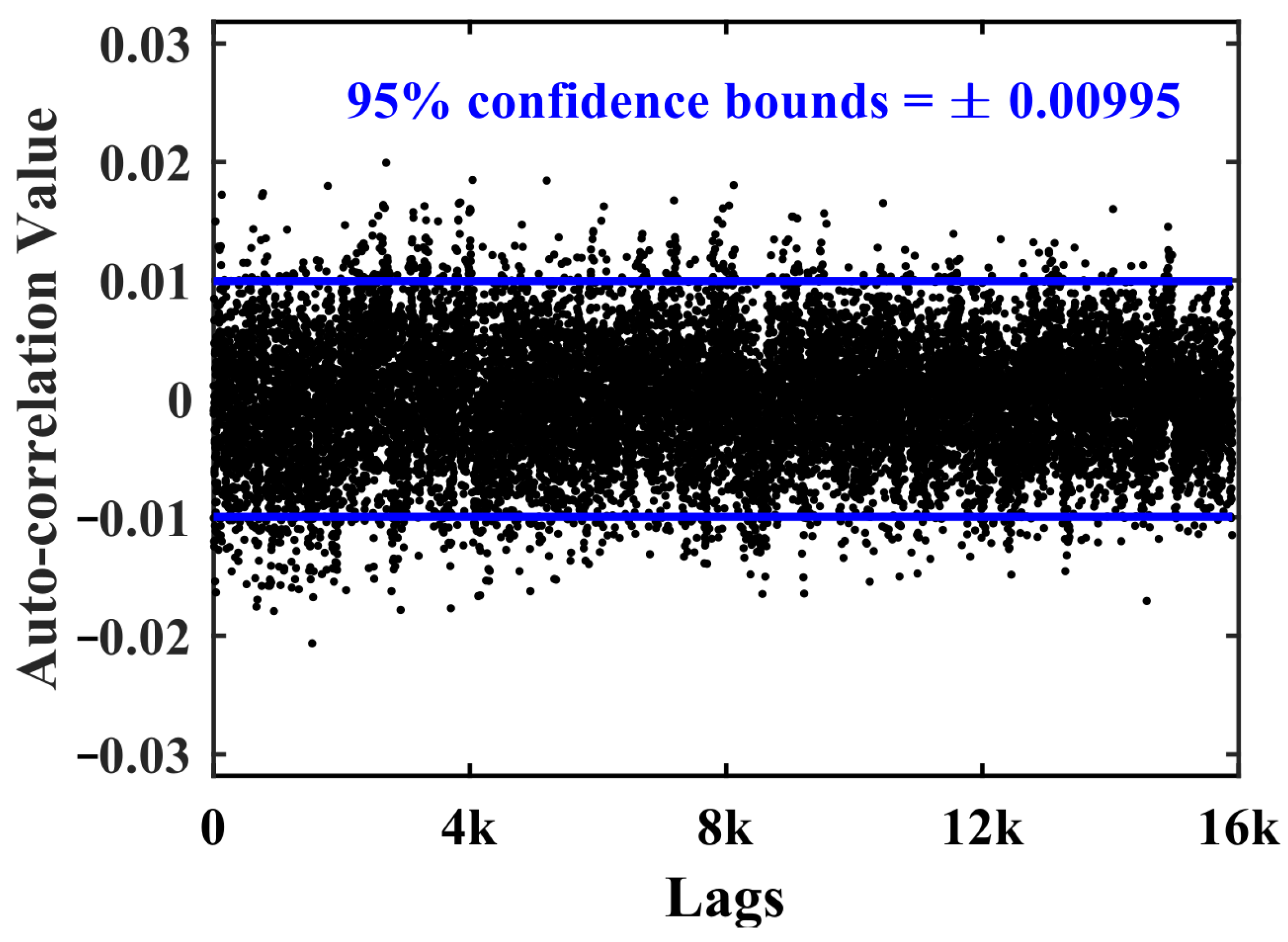

3.3. Uniqueness, Uniformity, and Randomness

3.4. Comparison

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Herder, C.; Yu, M.D.; Koushanfar, F.; Devadas, S. Physical unclonable functions and applications: A tutorial. Proc. IEEE 2014, 102, 1126–1141. [Google Scholar] [CrossRef]

- Alvarez, A.B.; Zhao, W.; Alioto, M. Static physically unclonable functions for secure chip identification with 1.9–5.8% native bit instability at 0.6–1 V and 15 fJ/bit in 65 nm. IEEE J. Solid-State Circuits 2016, 51, 763–775. [Google Scholar]

- Mexis, N.; Anagnostopoulos, N.A.; Katzenbeisser, S.; Kavun, E.B.; Tehranipoor, S.; Arul, T. Achieving Error-Free Lightweight Authentication With DRAM-Based Physical Unclonable Functions. IEEE Trans. Circuits Syst. I Regul. Pap. 2025, 72, 637–646. [Google Scholar] [CrossRef]

- Stanzione, S.; Puntin, D.; Iannaccone, G. CMOS silicon physical unclonable functions based on intrinsic process variability. IEEE J. Solid-State Circuits 2011, 46, 1456–1463. [Google Scholar] [CrossRef]

- Vatalaro, M.; Rose, R.D.; Maccaronio, V.; Lanuzza, M.; Crupi, F. Highly Stable PUFs Based on Stacked Voltage Divider for Near-Zero BER Native Sensitivity to Voltage Variations. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 72, 521–534. [Google Scholar] [CrossRef]

- Lee, J.; Kim, M.; Jeong, M.; Shin, G.; Lee, Y. A 20F2/Bit Current-Integration-Based Differential nand-Structured PUF for Stable and V/T Variation-Tolerant Low-Cost IoT Security. IEEE J. Solid-State Circuits 2022, 57, 2957–2968. [Google Scholar] [CrossRef]

- Alioto, M. Trends in Hardware Security: From Basics to ASICs. IEEE Solid-State Circuits Mag. 2019, 11, 56–74. [Google Scholar] [CrossRef]

- Amirany, A.; Mohebbi, L. SQTRNG: Spintronic Quaternary True Random Number Generator. SPIN 2025, 15. [Google Scholar] [CrossRef]

- Lim, S.; Song, B.; Jung, S.O. Highly independent MTJ-based PUF system using diode-connected transistor and two-step postprocessing for improved response stability. IEEE Trans. Inf. Forensics Secur. 2020, 15, 2798–2807. [Google Scholar] [CrossRef]

- Lee, S.; Kang, J.; Kim, J.M.; Kim, N.; Han, D.; Lee, T.; Ko, S.; Yang, J.; Lee, S.; Lee, S.; et al. Spintronic physical unclonable functions based on field-free spin–orbit-torque switching. Adv. Mater. 2022, 34, 2203558. [Google Scholar] [CrossRef] [PubMed]

- Maes, R. Physically Unclonable Functions: Constructions, Properties and Applications; Springer: Berlin/Heidelberg, Germany, 2013. [Google Scholar]

- Tran, S.; Ngo, C.T.; Pham, V.K.; Hong, J.P. A Lightweight ECC-Compatible End-to-End Security Protocol Using CRP-PUF and TRNG for IoT Devices. IEEE Internet Things J. 2025; early access. [Google Scholar]

- Qureshi, M.A.; Munir, A. PUF-RAKE: A PUF-based robust and lightweight authentication and key establishment protocol. IEEE Trans. Dependable Secur. Comput. 2021, 19, 2457–2475. [Google Scholar] [CrossRef]

- Liu, J.; Zhao, Y.; Zhu, Y.; Chan, C.H.; Martins, R.P. A Weak PUF-Assisted Strong PUF With Inherent Immunity to Modeling Attacks and Ultra-Low BER. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 4898–4907. [Google Scholar] [CrossRef]

- Mathew, S.K.; Satpathy, S.K.; Anders, M.A.; Kaul, H.; Hsu, S.K.; Agarwal, A.; Chen, G.K.; Parker, R.J.; Krishnamurthy, R.K.; De, V. 16.2 A 0.19pJ/b PVT-variation-tolerant hybrid physically unclonable function circuit for 100% stable secure key generation in 22nm CMOS. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 278–279. [Google Scholar] [CrossRef]

- Shifman, Y.; Shor, J. Preselection Methods to Achieve Very Low BER in SRAM-Based PUFs—A Tutorial. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 2551–2556. [Google Scholar] [CrossRef]

- He, Z.; Chen, W.; Zhang, L.; Chi, G.; Gao, Q.; Harn, L. A Highly Reliable Arbiter PUF With Improved Uniqueness in FPGA Implementation Using Bit-Self-Test. IEEE Access 2020, 8, 181751–181762. [Google Scholar] [CrossRef]

- He, Y.; Li, D.; Yu, Z.; Yang, K. An automatic self-checking and healing physically unclonable function (PUF) with <3 × 10−8 bit error rate. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), Online, 13–22 February 2021; IEEE: San Francisco, CA, USA, 2021; Volume 64, pp. 506–508. [Google Scholar]

- Al-Tamimi, A.; Ali, S.; Cao, Y.; Bermak, A. Threshold voltage based dual memristor crossbar PUF. AEU-Int. J. Electron. Commun. 2024, 175, 155012. [Google Scholar] [CrossRef]

- Ni, L.; Zhang, J. S2RAM PUF: An ultra-low power subthreshold SRAM PUF with zero bit error rate. In Proceedings of the 61st ACM/IEEE Design Automation Conference, San Francisco, CA, USA, 23–27 June 2024; pp. 1–6. [Google Scholar]

- Zambrano, B.; Garzón, E.; Strangio, S.; Iannaccone, G.; Lanuzza, M. A 0.6 V–1.8 V Compact Temperature Sensor With 0.24 °C Resolution, ±1.4 °C Inaccuracy and 1.06 nJ per Conversion. IEEE Sens. J. 2022, 22, 11480–11488. [Google Scholar] [CrossRef]

- Tang, X.; Shen, L.; Kasap, B.; Yang, X.; Shi, W.; Mukherjee, A.; Pan, D.Z.; Sun, N. An Energy-Efficient Comparator With Dynamic Floating Inverter Amplifier. IEEE J. Solid-State Circuits 2020, 55, 1011–1022. [Google Scholar] [CrossRef]

- Böhm, C.; Hofer, M. Physical Unclonable Functions in Theory and Practice; Springer Science & Business Media: New York, NY, USA, 2012. [Google Scholar]

- Zhao, Q.; Wu, Y.; Zhao, X.; Cao, Y.; Chang, C.H. A 1036-F2/Bit High Reliability Temperature Compensated Cross-Coupled Comparator-Based PUF. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 1449–1460. [Google Scholar] [CrossRef]

- Liu, K.; Chen, X.; Pu, H.; Shinohara, H. A 0.5-V Hybrid SRAM Physically Unclonable Function Using Hot Carrier Injection Burn-In for Stability Reinforcement. IEEE J. Solid-State Circuits 2021, 56, 2193–2204. [Google Scholar] [CrossRef]

- Taneja, S.; Rajanna, V.K.; Alioto, M. In-Memory Unified TRNG and Multi-Bit PUF for Ubiquitous Hardware Security. IEEE J. Solid-State Circuits 2022, 57, 153–166. [Google Scholar] [CrossRef]

- Vatalaro, M.; De Rose, R.; Lanuzza, M.; Crupi, F. Static CMOS physically unclonable function based on 4T voltage divider with 0.6%–1.5% bit instability at 0.4–1.8 V operation in 180 nm. IEEE J. Solid-State Circuits 2022, 57, 2509–2520. [Google Scholar] [CrossRef]

- Liang, Z.Y.; Wei, H.H.; Liu, T.T. A Wide-Range Variation-Resilient Physically Unclonable Function in 28 nm. IEEE J. Solid-State Circuits 2020, 55, 817–825. [Google Scholar] [CrossRef]

- Lee, J.; Lee, D.; Lee, Y.; Lee, Y. A 354F2 Leakage-Based Physically Unclonable Function With Lossless Stabilization Through Remapping for Low-Cost IoT Security. IEEE J. Solid-State Circuits 2021, 56, 648–657. [Google Scholar] [CrossRef]

- Park, J.; Sim, J.Y. A Reconfigurable LDO-Assisted Physically Unclonable Function Achieving a Zero-BER With 14% Masking. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 3244–3253. [Google Scholar] [CrossRef]

| Test Name | Stream Length | Number of Runs | Average p-Value | Pass (%) |

|---|---|---|---|---|

| ine Frequency | 4800 | 10 | 0.327 | 90 |

| Block Frequency | 4800 | 10 | 0.089 | 90 |

| Cumulative Sums (Forward) | 4800 | 10 | 0.076 | 80 |

| Cumulative Sums (Reverse) | 4800 | 10 | 0.052 | 80 |

| Runs | 4800 | 10 | 0.098 | 80 |

| Longest Run of Ones | 4800 | 10 | 0.17 | 90 |

| FFT | 4800 | 10 | 0.215 | 100 |

| Approximate Entropy | 4800 | 10 | 0.103 | 80 |

| Serial | 4800 | 10 | 0.177 | 80 |

| This Work | JSSC’22 [27] | JSSC’21 [25] | TVLSI’20 [24] | JSSC’20 [28] | JSSC’21 [29] | JSSC’22 [26] | TCAS-I’23 [30] | JSSC’22 [6] | ||

|---|---|---|---|---|---|---|---|---|---|---|

| Tech. [nm] | 65 | 180 | 130 | 65 | 28 | 180 | 28 | 40 | 180 | |

| Area [] | 45,286 | 300,115 | 39,935 | 2750 | - | 15,400 | - | - | ||

| Area/bit [] | 18.93 | 102 | 8.4 | 4.38 | 26 | 11.48 | 0.88 | 19.77 | 0.66 | |

| Area/bit [F2] | 4480 | 3148 | 497 | 1036 | 33,163 | 354 | 1125 | 12,356 | 20 | |

| Array size | 512b | 8 × 32 | 16 × 64 | 16 × 16 | 128b | 64 × 16 | - | 128b | 256 × 32 | |

| Uniqueness | 0.4784 | 0.493 | 0.4873 | 0.4953 | 0.4994 | 0.4946 | 0.503 | 0.5027 | - | - |

| Uniformity | 0.504 | - | - | 0.498 | 0.506 | - | 0.503 | - | - | - |

| Stabilization method | Offset mask + SMV3 | - | HCI Burn-in | TMV + DBD + SMV | Delay calibration + TMV7 | TMV11 + Remapping | - | DBD | Trimming + TMV11 | Remapping + TMV11 |

| Native BER@GK | 1.69% | 0.16% | 0.29% | 0.44% | 1.40% | 0.43% | 1.80% | 1.33% | 0.937% | |

| Native BER across V/T variations | 3.5% | 0.65% (b) 0.5% (c) | 1.37% (0.7 V) 5.76% (120 C) | 3.13% | 8.4% (0.4 V) 4.5% (125 C) | 3.51% (1.8 V) 4.2% (80 C) | 6.70% | 0.297% | 2.26% (1.9 V) 4.54% (−20 C) | |

| Stabilized BER across V/T variations | - | 0% | 0.69% | 0.55% (b) 0.078% (c) | 0.43% (1.8 V) 0.47% (80 C) | - | 0.331% (1.9 V) 0.633% (−20 C) | 0.726% (1.9 V) 1.362% (−20 C) | ||

| Masking ratio | 19% | - | - | 4% | - | - | - | 14% | 20% | 0% |

| ACF@95% | 0.00995 | 0.0472 | 0.0334 | 0.0197 | 0.041 | 0.0139 | 0.007 | 0.0424 | 0.007 | |

| VDD Range [V] | 0.8–1.3 | 0.4–1.8 | 0.5–0.7 | 1–1.4 | 0.4–1.3 | 1–1.8 | 0.75–1.05 | 0.9–1.4 | 1.5–1.9 | |

| Temperature range [C] | 0–75 | 10–80 | −40–120 | −50–150 | −40–125 | 0–80 | −25–100 | −40–125 | −20–80 | |

| Energy/bit [J] | 1.37p | - | 2.07f@0.5V | 2.98p | 2.15p | 465p | 72f | 0.186p | 138p | |

| Throughput [b/s] | 8 K | - | 23 M | 8 M | - | 0.65 K | 12.6 M | 69.9 M | 1.6 K | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zambrano, B.; Strangio, S.; Garzón, E.; Catania, A.; Iannaccone, G.; Lanuzza, M. A Physical Unclonable Function Based on a Differential Subthreshold PMOS Array with 9.73 × 10−4 Stabilized BER and 1.3 pJ/bit in 65 nm. J. Low Power Electron. Appl. 2025, 15, 53. https://doi.org/10.3390/jlpea15030053

Zambrano B, Strangio S, Garzón E, Catania A, Iannaccone G, Lanuzza M. A Physical Unclonable Function Based on a Differential Subthreshold PMOS Array with 9.73 × 10−4 Stabilized BER and 1.3 pJ/bit in 65 nm. Journal of Low Power Electronics and Applications. 2025; 15(3):53. https://doi.org/10.3390/jlpea15030053

Chicago/Turabian StyleZambrano, Benjamin, Sebastiano Strangio, Esteban Garzón, Alessandro Catania, Giuseppe Iannaccone, and Marco Lanuzza. 2025. "A Physical Unclonable Function Based on a Differential Subthreshold PMOS Array with 9.73 × 10−4 Stabilized BER and 1.3 pJ/bit in 65 nm" Journal of Low Power Electronics and Applications 15, no. 3: 53. https://doi.org/10.3390/jlpea15030053

APA StyleZambrano, B., Strangio, S., Garzón, E., Catania, A., Iannaccone, G., & Lanuzza, M. (2025). A Physical Unclonable Function Based on a Differential Subthreshold PMOS Array with 9.73 × 10−4 Stabilized BER and 1.3 pJ/bit in 65 nm. Journal of Low Power Electronics and Applications, 15(3), 53. https://doi.org/10.3390/jlpea15030053