Current-Mode Quadrature Oscillator Simple Designs

Abstract

1. Introduction

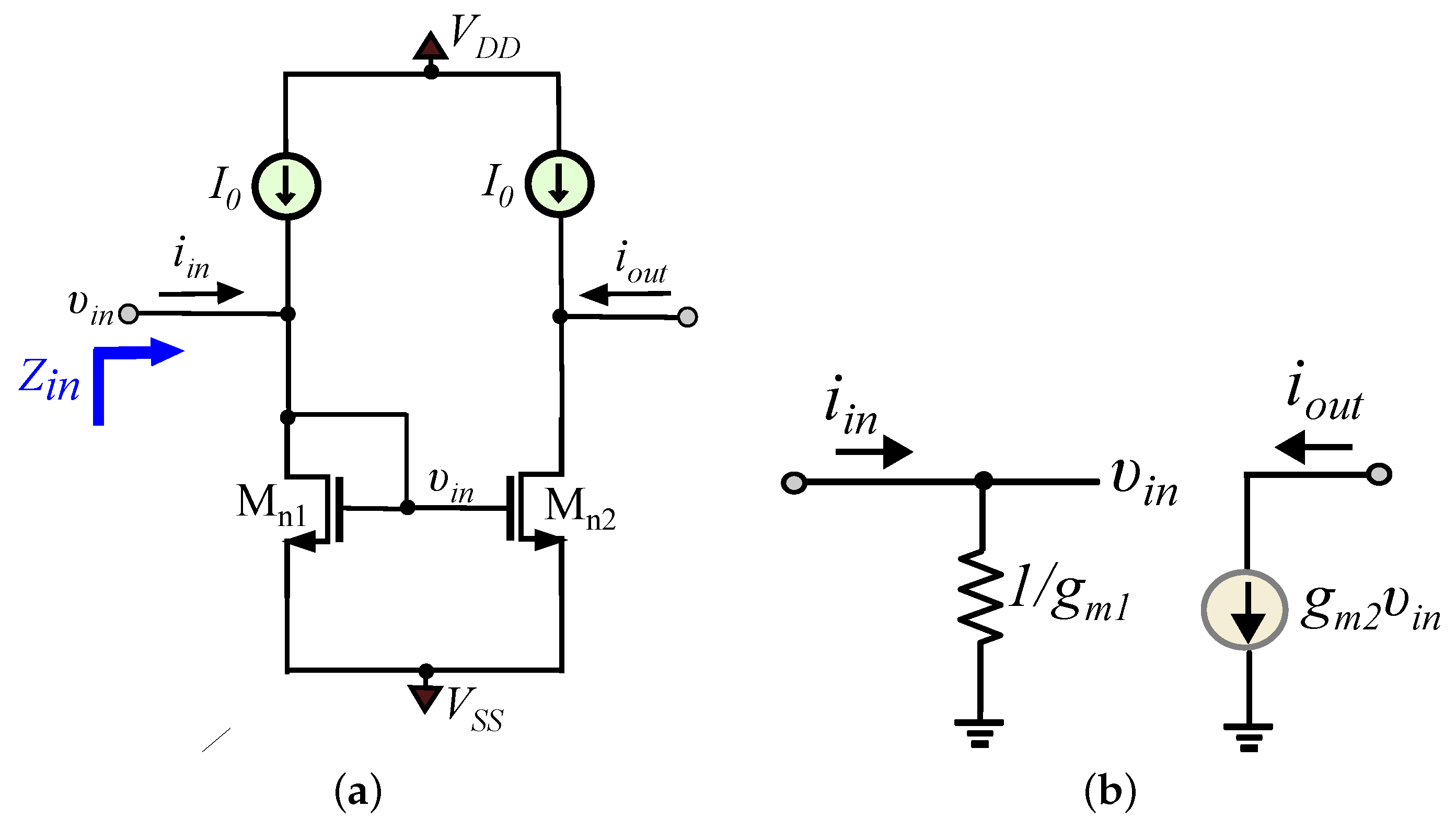

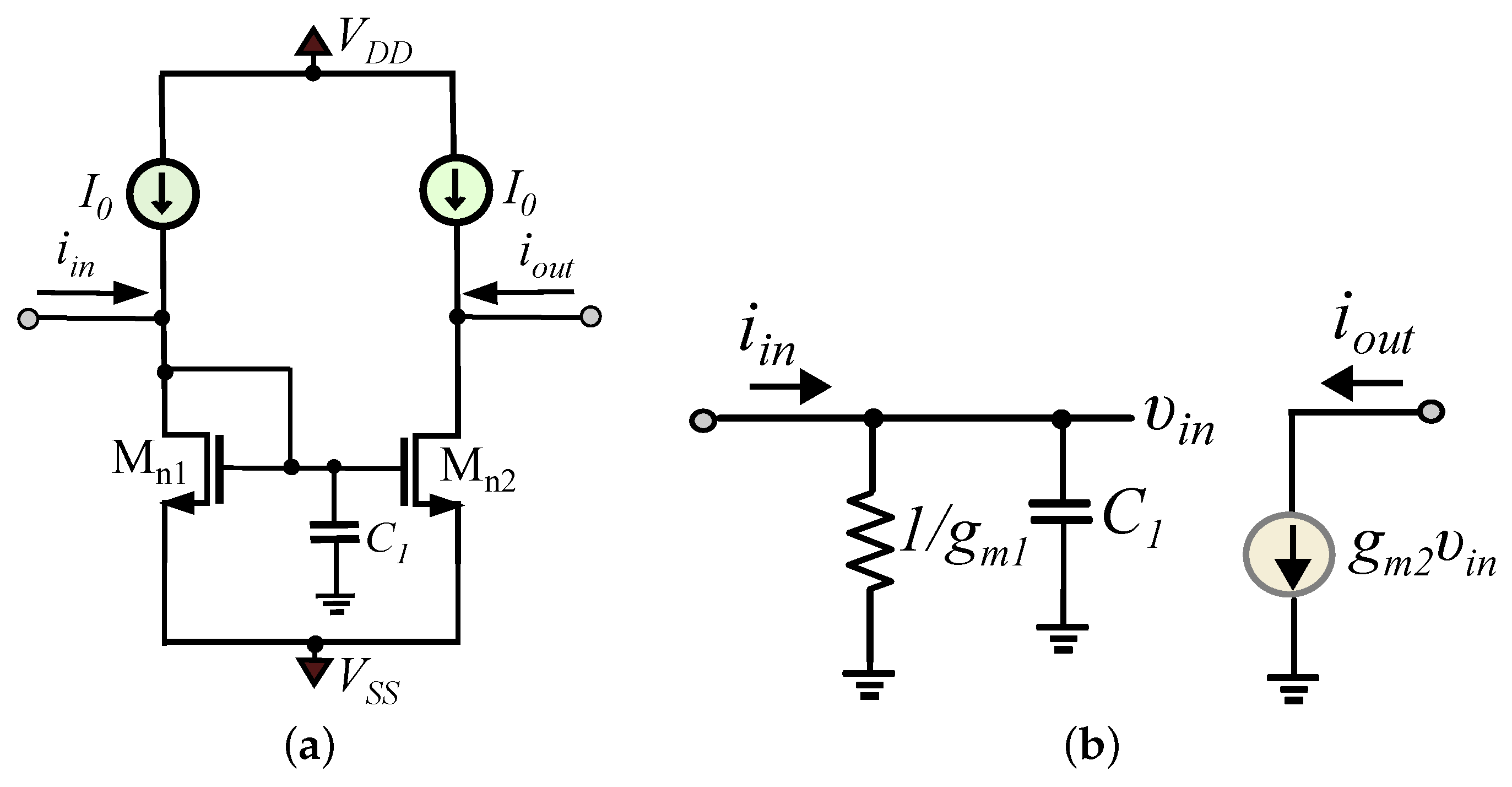

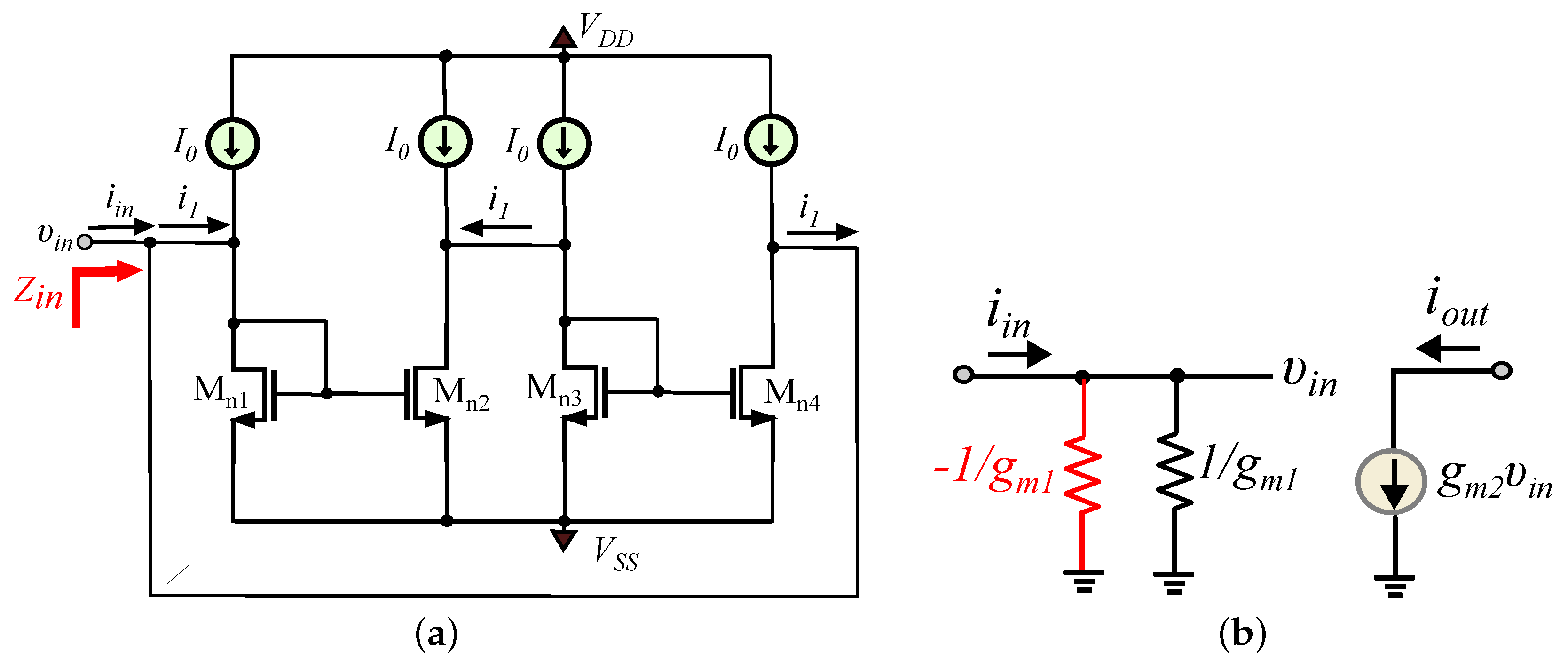

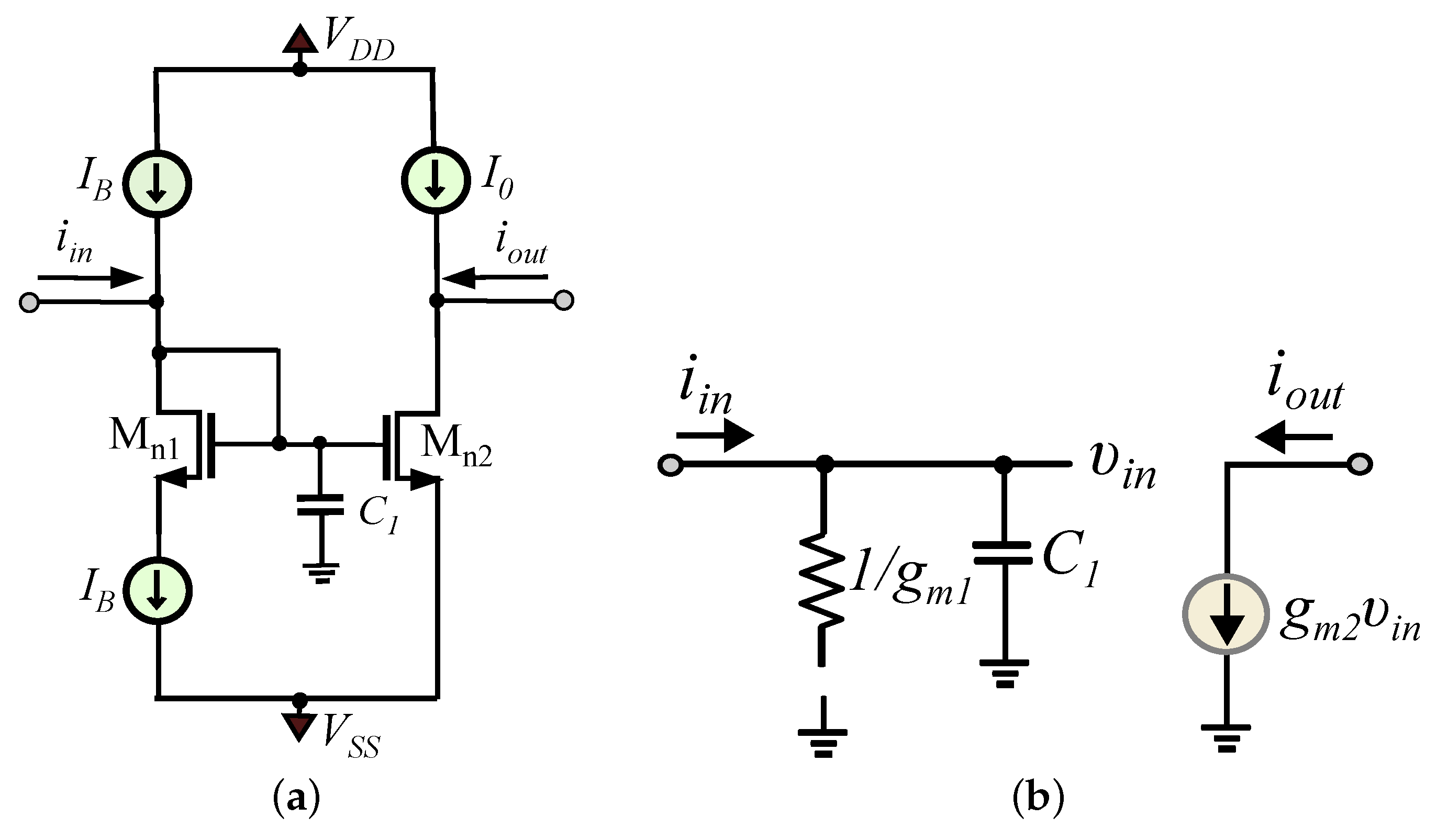

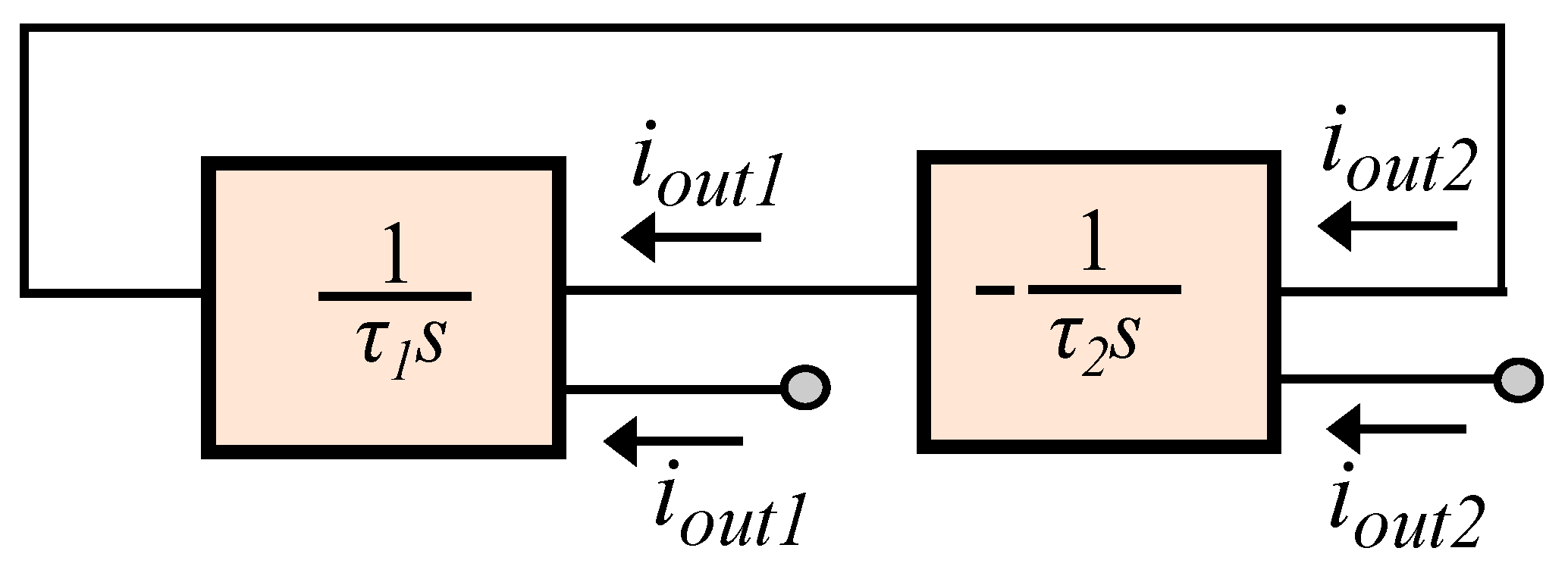

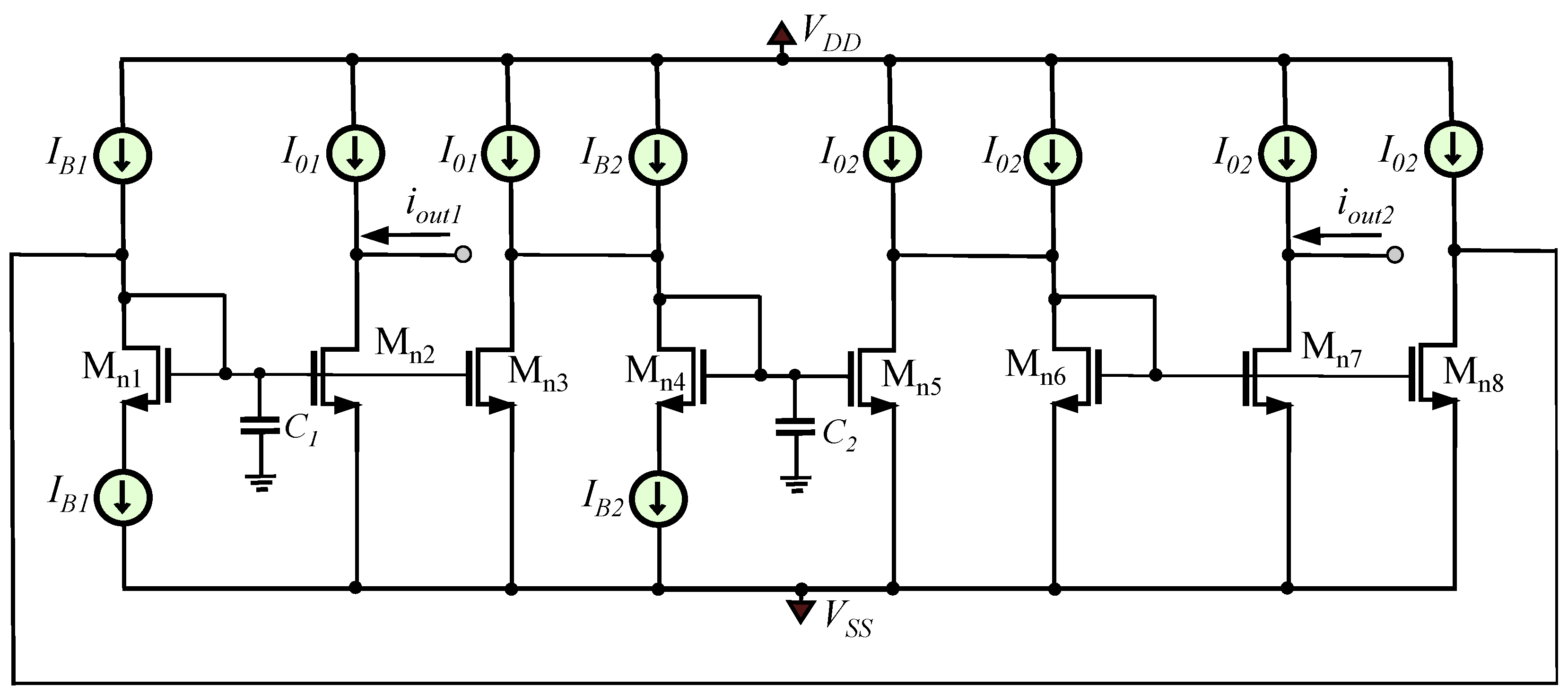

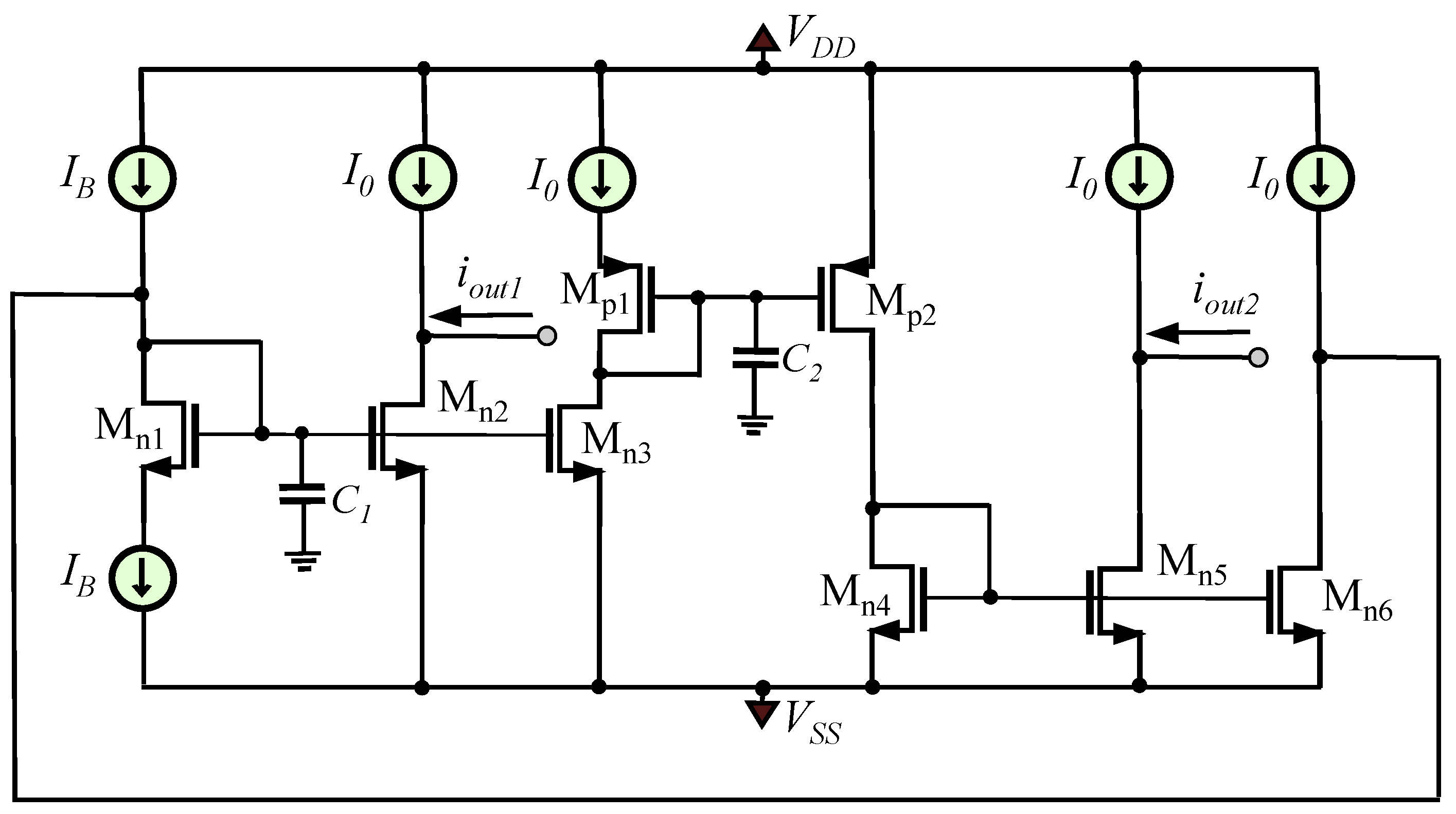

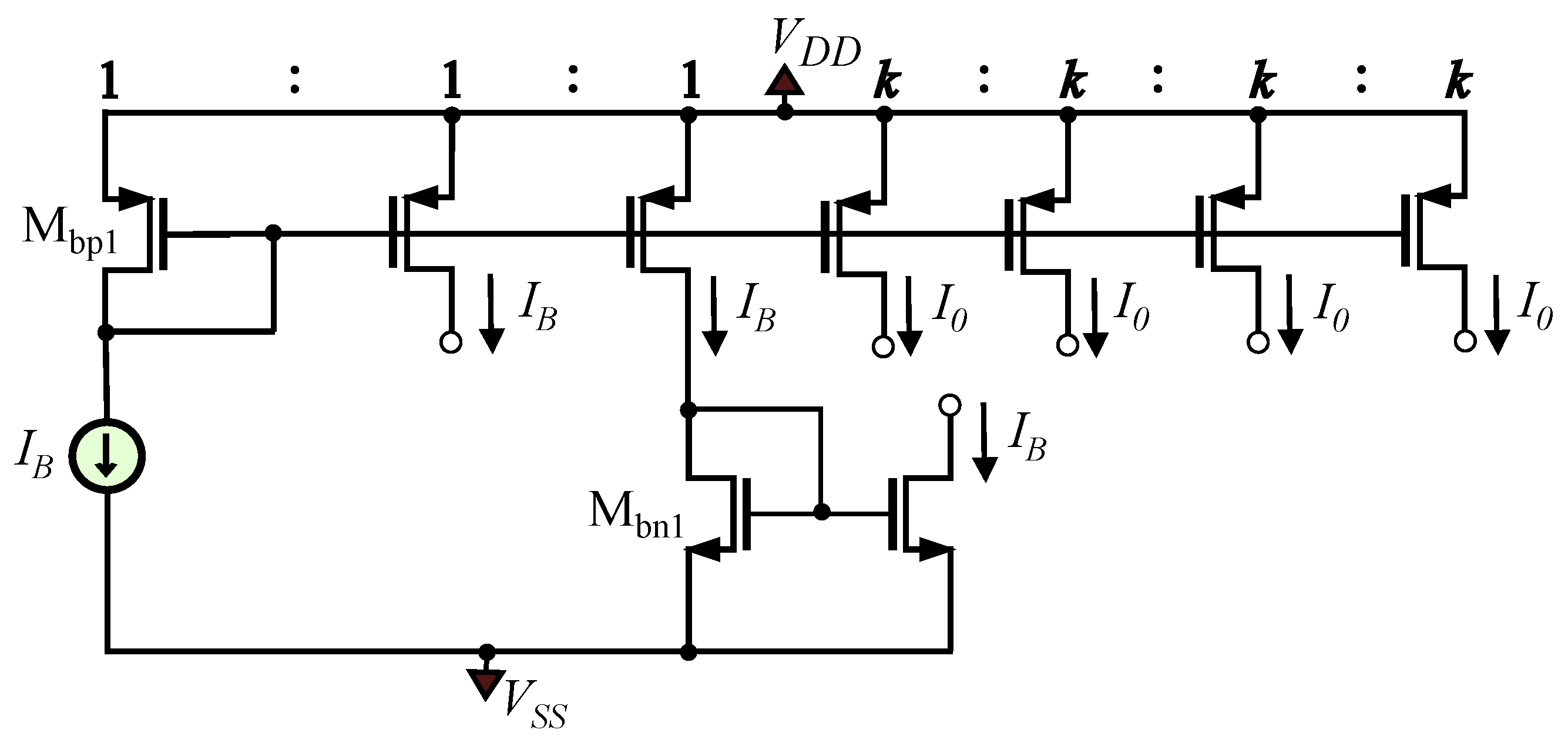

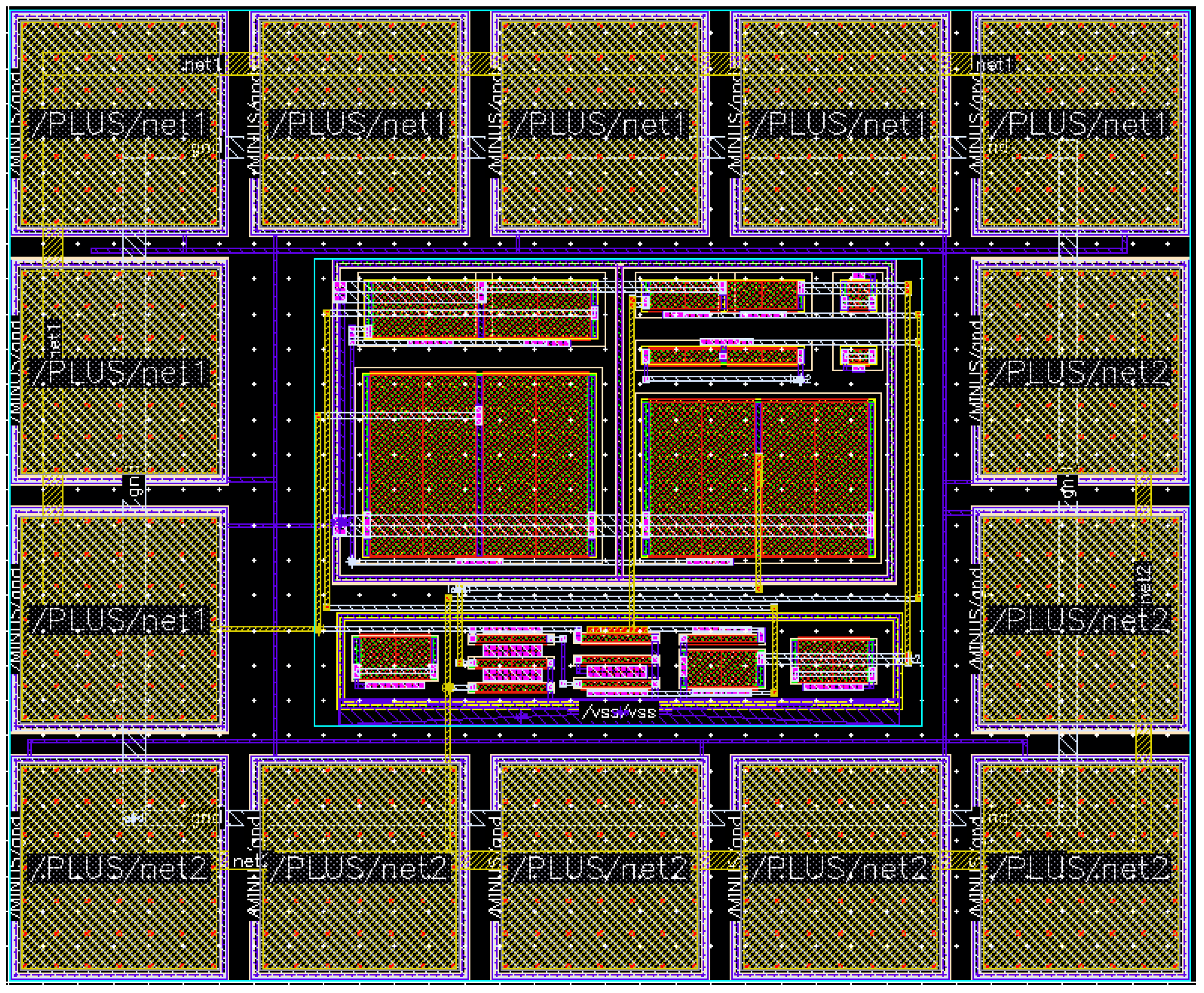

2. Current-Mode Integration Stages Based on Current-Mirrors

- (a)

- (b)

- (c)

- (d)

- There is not any matching requirement between the transistors Mn1 − Mn2, in contrast to the topology in Figure 5. The reason is that, under the assumption that the capacitor is initially discharged, the value of the voltage at the common-gate connection of Mn1 − Mn2 is equal to zero. Therefore, the gate-source voltage of Mn2 becomes equal to , making its transconductance to be: offering linear dependence from the current .

3. Proposed Sinusoidal Quadrature Oscillator

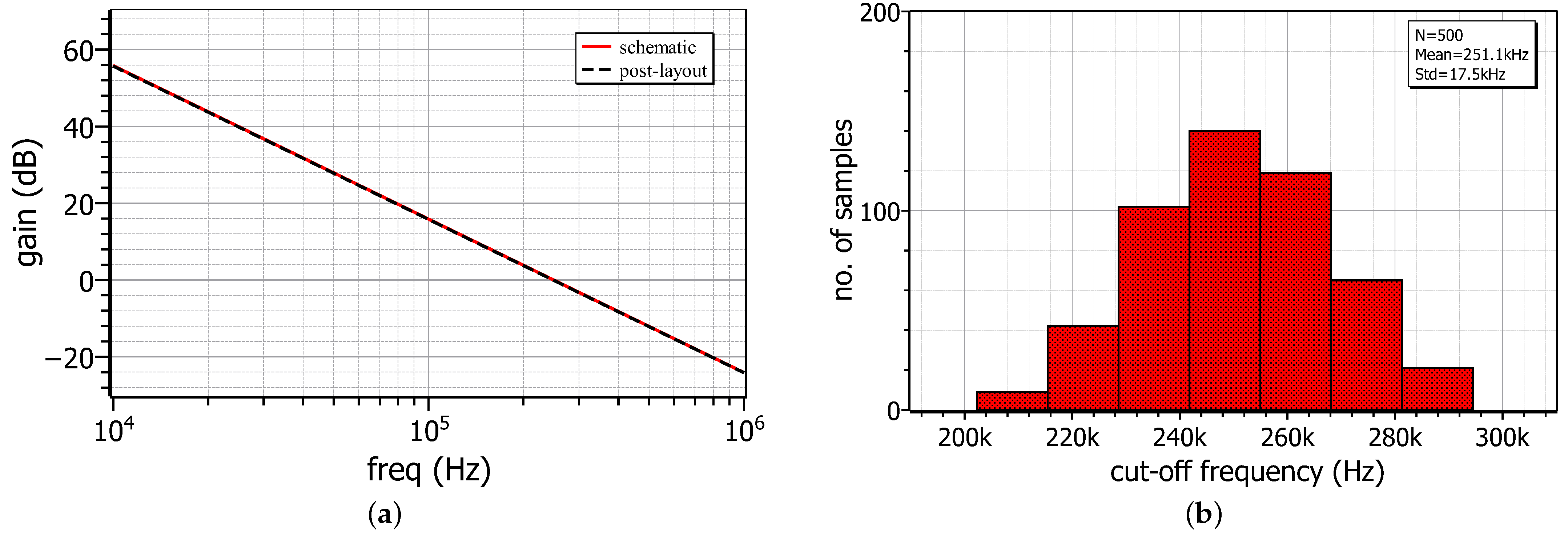

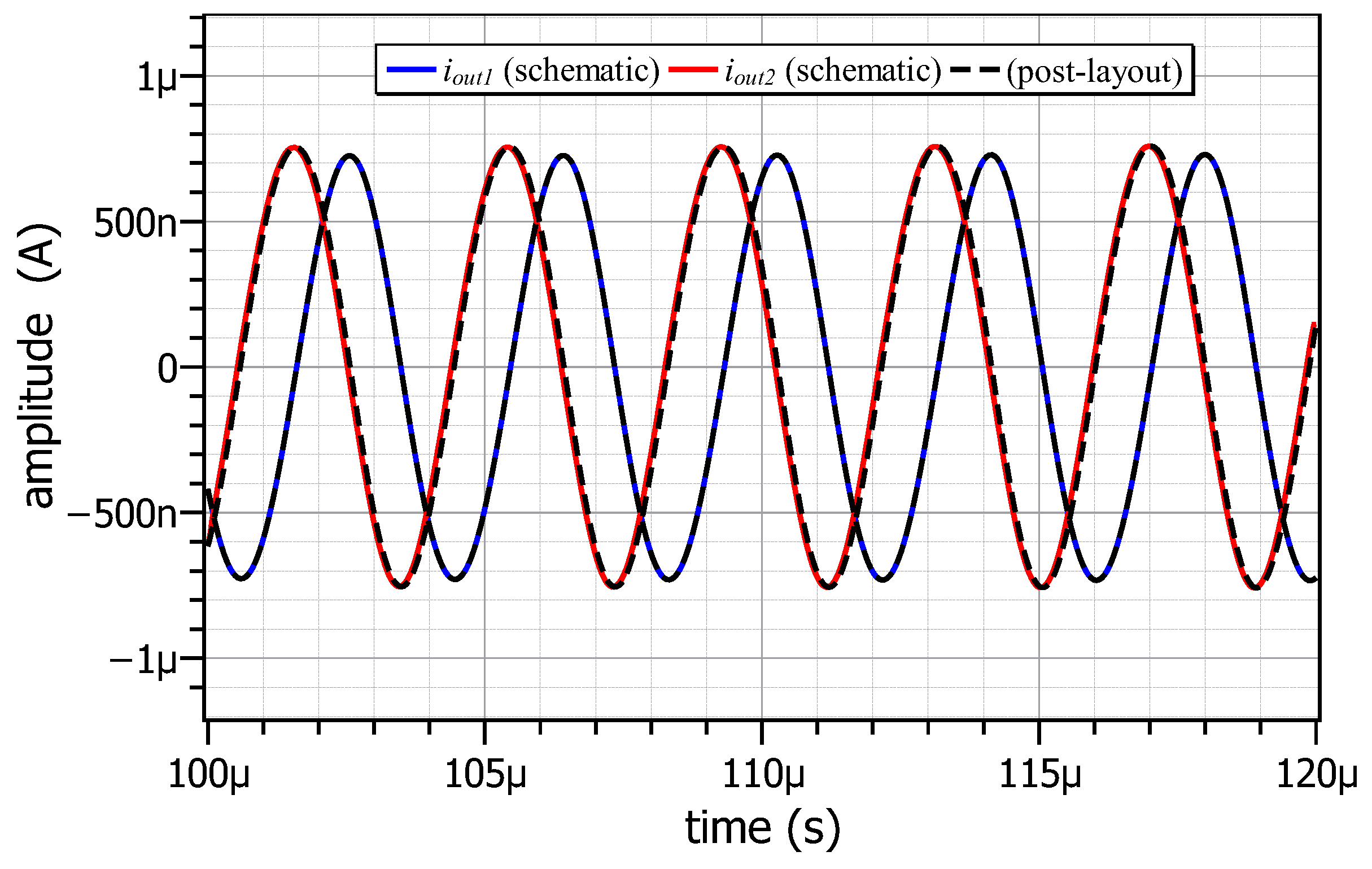

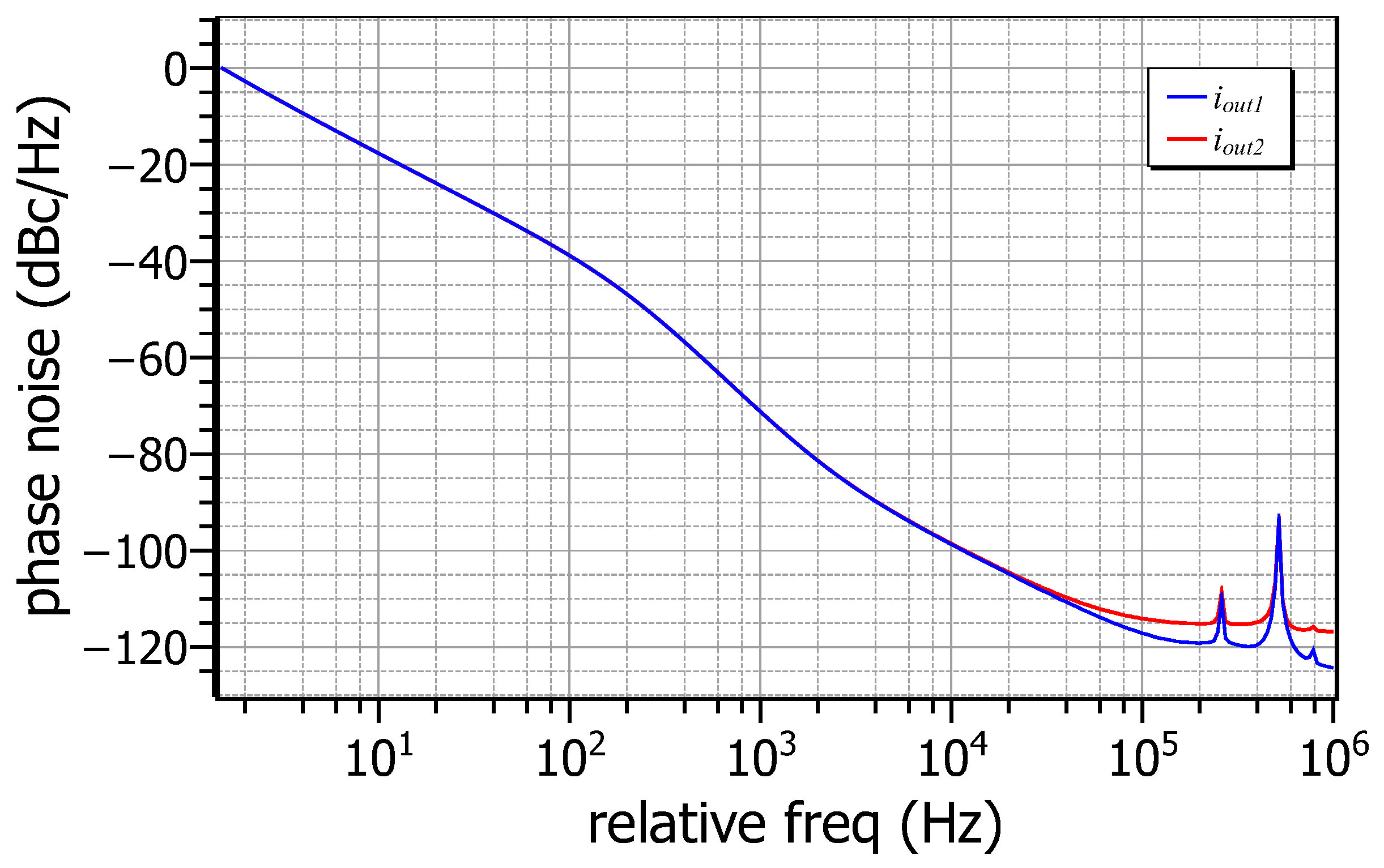

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Siripruchyanun, M.; Jaikla, W. Cascadable current-mode biquad filter and quadrature oscillator using DO-CCCIIs and OTA. Circuits Syst. Signal Process. 2009, 28, 99–110. [Google Scholar] [CrossRef]

- Thosdeekoraphat, T.; Summart, S.; Saetiaw, C.; Santalunai, S.; Thongsopa, C. CCTAs based current-mode quadrature oscillator with high output impedances. Int. J. Electron. Electr. Eng. 2013, 1, 52–56. [Google Scholar] [CrossRef]

- Sakul, C.; Jaikla, W.; Dejhan, K. New resistorless current-mode quadrature oscillators using 2 CCCDTAs and grounded capacitors. Radioengineering 2011, 20, 890–896. [Google Scholar]

- Keawon, R.; Jaikla, W. A resistor-less current-mode quadrature sinusoidal oscillator employing single CCCDTA and grounded capacitors. Prz. Elektrotechniczny 2011, 87, 138–141. [Google Scholar]

- Summart, S.; Thongsopa, C.; Jaikla, W. OTA based current-mode sinusoidal quadrature oscillator with non-interactive control. Prz. Elektrotechniczny 2012, 88, 14–17. [Google Scholar]

- Maiti, S.; Pal, R.R. Dual-mode quadrature oscillator employing single Current Controlled Current Conveyor transconductance amplifier. Int. J. Innov. Res. Sci. Eng. Technol. 2013, 2, 3105–3112. [Google Scholar]

- Thosdeekoraphat, T.; Summart, S.; Thongsopa, C. Current-mode Sinusoidal Oscillator using Single Dual-output Current Controlled Current Conveyor Transconductance Amplifier (DO-CCCCTA). Aust. J. Basic Appl. Sci 2013, 7, 230–236. [Google Scholar]

- Siriphot, D.; Pookrongtong, N.; Lumchanao, W. Single CDCTA Based Electronically Adjustable Current-mode Quadrature Sinusoidal Oscillator. Appl. Sci. Eng. Prog. 2018, 11, 209–216. [Google Scholar] [CrossRef][Green Version]

- Kumngern, M.; Jongchanachavawat, W.; Phatsornsiri, P.; Wongprommoon, N.; Khateb, F.; Kulej, T. Current-mode first-order versatile filter using translinear current conveyors with controlled current gain. Electronics 2023, 12, 2828. [Google Scholar] [CrossRef]

- Kumngern, M.; Khateb, F.; Kulej, T. A Novel Multiple-Input Single-Output Current-Mode Shadow Filter and Shadow Oscillator Using Current-Controlled Current Conveyors. Circuits Syst. Signal Process. 2024, 43, 5438–5462. [Google Scholar] [CrossRef]

- Souliotis, G.; Psychalinos, C. Harmonic oscillators realized using current amplifiers and grounded capacitors. Int. J. Circuit Theory Appl. 2007, 35, 165–173. [Google Scholar] [CrossRef]

- Jantakun, A.; Jaikla, W. Current-mode quadrature oscillator based on CCCDTAs with noninteractive dual-current control for both condition of oscillation and frequency of oscillation. Turk. J. Electr. Eng. Comput. Sci. 2013, 21, 81–89. [Google Scholar] [CrossRef]

- Summart, S.; Thongsopa, C.; Jaikla, W. New current-controlled current-mode sinusoidal quadrature oscillators using CDTAs. AEU-Int. J. Electron. Commun. 2015, 69, 62–68. [Google Scholar] [CrossRef]

- Das, R.; Bhowmick, B.; Paul, P.; Karmakar, S.; Banerjee, K. Current Differencing Transconductance Amplifier (CDTA) based current mode quadrature oscillator. In Advances in Computer, Communication and Control: Proceedings of ETES 2018; Springer: Singapore, 2019; pp. 35–47. [Google Scholar] [CrossRef]

- Yeşil, A.; Kaçar, F. Current and voltage mode quadrature oscillator based on Voltage Differencing Buffered Amplifier. Electrica 2018, 18, 6–12. [Google Scholar] [CrossRef]

- Singh, A.K.; Kumar, P.; Senani, R. Current-mode quadrature oscillator using CFCC. Am. J. Electr. Electron. Eng. 2018, 6, 85–89. [Google Scholar]

- Kumngern, M.; Khateb, F. Current-mode universal filter and quadrature oscillator using Current Controlled Current Follower Transconductance Amplifiers. Analog Integr. Circuits Signal Process. 2019, 100, 235–248. [Google Scholar] [CrossRef]

- Gupta, M.; Dogra, P.; Arora, T.S. Novel current mode universal filter and dual-mode quadrature oscillator using VDCC and all grounded passive elements. Aust. J. Electr. Electron. Eng. 2019, 16, 220–236. [Google Scholar] [CrossRef]

- Arora, T.S.; Gupta, M.; Gupta, S.N. An Explicit Output Current-mode Quadrature Sinusoidal Oscillator and a Universal Filter Employing Only Grounded Passive Components-a Minimal Realisation. Adv. Electr. Electron. Eng. 2021, 19, 258–271. [Google Scholar] [CrossRef]

- Roongmuanpha, N.; Tangsrirat, W.; Pukkalanun, T. Single VDGA-based mixed-mode universal filter and dual-mode quadrature oscillator. Sensors 2022, 22, 5303. [Google Scholar] [CrossRef]

- Summart, S.; Sirithai, S.; Vaisopha, B.; Jantakun, A. Electronically controlled biquadratic filter and quadrature oscillator using CDTAs. Int. J. Eng. Technol. Innov. 2022, 12, 322–335. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Róbinson, M.; Sanchez-Sinecio, E. Current-mode continuous-time filters: Two design approaches. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 1992, 39, 337–341. [Google Scholar] [CrossRef]

- Lee, S.S.; Zele, R.H.; Allstot, D.J.; Liang, G. CMOS continuous-time current-mode filters for high-frequency applications. IEEE J. Solid-State Circuits 1993, 28, 323–329. [Google Scholar] [CrossRef]

- Koliopoulos, C.; Psychalinos, C. A comparative study of the performance of the flipped voltage follower based low-voltage current mirrors. In Proceedings of the 2007 International Symposium on Signals, Circuits and Systems, Iasi, Romania, 13–14 July 2007; pp. 192–195. [Google Scholar] [CrossRef]

- Souliotis, G.; Haritantis, I. Current-mode filters based on current mirror arrays. Int. J. Circuit Theory Appl. 2008, 36, 173–183. [Google Scholar] [CrossRef]

- Laoudias, C.; Psychalinos, C. Universal biquad filter topology using low-voltage current mirrors. Int. J. Circuit Theory Appl. 2012, 40, 65–75. [Google Scholar] [CrossRef]

- Laoudias, C.; Psychalinos, C. 1.5-V complex filters using current mirrors. IEEE Trans. Circuits Syst. II Express Briefs 2011, 58, 575–579. [Google Scholar] [CrossRef]

- Gupta, M.; Aggarwal, P.; Singh, P.; Jindal, N.K. Low voltage current mirrors with enhanced bandwidth. Analog Integr. Circuits Signal Process. 2009, 59, 97–103. [Google Scholar] [CrossRef]

- Aggarwal, B.; Gupta, M.; Gupta, A.K. A comparative study of various current mirror configurations: Topologies and characteristics. Microelectron. J. 2016, 53, 134–155. [Google Scholar] [CrossRef]

- Shrivastava, A.; Pandey, R.; Jindal, C. Low-voltage flipped voltage follower cell based current mirrors for high frequency applications. Wirel. Pers. Commun. 2020, 111, 143–161. [Google Scholar] [CrossRef]

- Aggarwal, B. Novel current mirrors based on folded flipped voltage follower configuration. Wirel. Pers. Commun. 2022, 123, 645–653. [Google Scholar] [CrossRef]

- Kumar, A.; Tripathi, S.L.; Verma, C.; Raboaca, M.S.; Enescu, F.M.; Mihaltan, T.C. Design and Analysis of Low Power Bio-amplifier with Current Mirror Topology at CMOS 45nm Technology Node. In Proceedings of the 2022 14th International Conference on Electronics, Computers and Artificial Intelligence (ECAI), Ploiesti, Romania, 30 June–1 July 2022; pp. 1–5. [Google Scholar] [CrossRef]

- Huang, J.; Wang, C.; Zhou, T.; Lu, W.; Zhao, Y.; Liu, Y.; Li, Y. A shifting current mirror driver circuit for electrical impedance tomography applications. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 3832–3836. [Google Scholar] [CrossRef]

- Nam, K.; Choi, G.; Yoo, M.; Kang, S.; Jin, B.; Son, H.; Kim, K.; Ko, H. A low-noise and mismatch-tolerant current-mirror-based potentiostat circuit for glucose monitoring. Microelectron. J. 2023, 132, 105694. [Google Scholar] [CrossRef]

- Nako, J.; Psychalinos, C.; Minaei, S.; Yuce, E. Current-Mirror Based Filters with Reduced Circuit Complexity. Int. J. Circuit Theory Appl. 2025. early view. [Google Scholar] [CrossRef]

- Doreyatim, M.; Akbari, M.; Nazari, M.; Mahani, S. A low-voltage gain boosting-based current mirror with high input/output dynamic range. Microelectron. J. 2019, 90, 88–95. [Google Scholar] [CrossRef]

- Monfaredi, K.; Faraji Baghtash, H. An extremely low-voltage and high-compliance current mirror. Circuits Syst. Signal Process. 2020, 39, 30–53. [Google Scholar] [CrossRef]

- Jindal, C.; Pandey, R. A high output resistance, wide bandwidth, and low input resistance current mirror using flipped voltage follower cell. Int. J. Circuit Theory Appl. 2021, 49, 3286–3301. [Google Scholar] [CrossRef]

| Topology | No. of Active Elements | No. of Transistors | Resistors | Independent Control of O.C. 7 and O.F. 8 | Electronic Tunability |

|---|---|---|---|---|---|

| [13] | 3 CDTA 1 | 69 | — | yes | yes |

| [14] | 1 CDTA 1 | 47 | 1 | yes | yes |

| [18] | 2 VDCC 2 | 60 | 2 | yes | yes |

| [16] | 2 CFCC 3 | 104 | 5 | yes | no |

| [19] | 2 VDCC 2 | 60 | 3 | yes | yes |

| [12] | 2 CCCDTA 4 | 70 | — | yes | yes |

| [20] | 1 VDGA 5 | 27 | 1 | yes | yes |

| [21] | 4 CDTA 1 | 116 | — | yes | yes |

| [15] | 2 VDBA 6 | 44 | 1 | yes | yes |

| [17] | 2 CCFTA 1 | 70 | — | yes | yes |

| [11] | — | 22 | — | no | yes |

| Figure 7 | — | 18 | — | yes | yes |

| Figure 8 | — | 14 | — | yes | yes |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nako, J.; Psychalinos, C.; Minaei, S. Current-Mode Quadrature Oscillator Simple Designs. J. Low Power Electron. Appl. 2025, 15, 13. https://doi.org/10.3390/jlpea15010013

Nako J, Psychalinos C, Minaei S. Current-Mode Quadrature Oscillator Simple Designs. Journal of Low Power Electronics and Applications. 2025; 15(1):13. https://doi.org/10.3390/jlpea15010013

Chicago/Turabian StyleNako, Julia, Costas Psychalinos, and Shahram Minaei. 2025. "Current-Mode Quadrature Oscillator Simple Designs" Journal of Low Power Electronics and Applications 15, no. 1: 13. https://doi.org/10.3390/jlpea15010013

APA StyleNako, J., Psychalinos, C., & Minaei, S. (2025). Current-Mode Quadrature Oscillator Simple Designs. Journal of Low Power Electronics and Applications, 15(1), 13. https://doi.org/10.3390/jlpea15010013