A 1.87 µW Capacitively Coupled Chopper Instrumentation Amplifier with a 0.36 mV Output Ripple and a 1.8 GΩ Input Impedance for Biomedical Recording †

Abstract

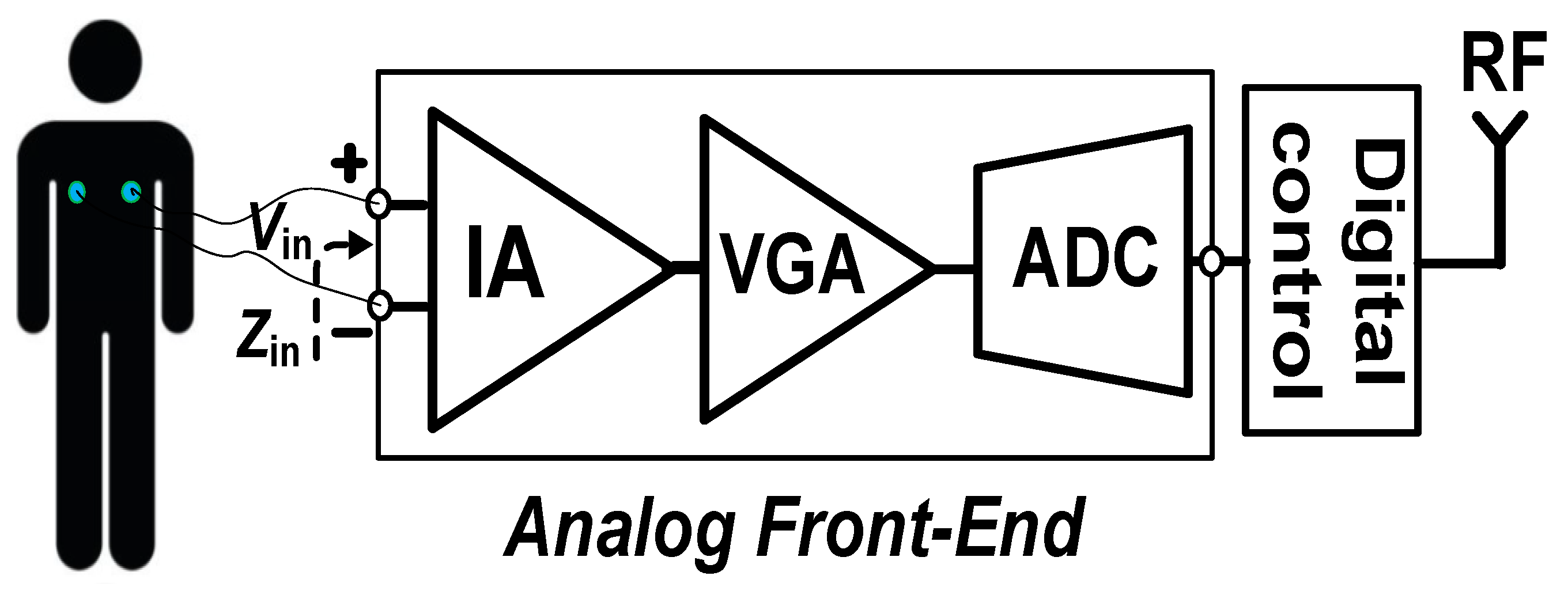

1. Introduction

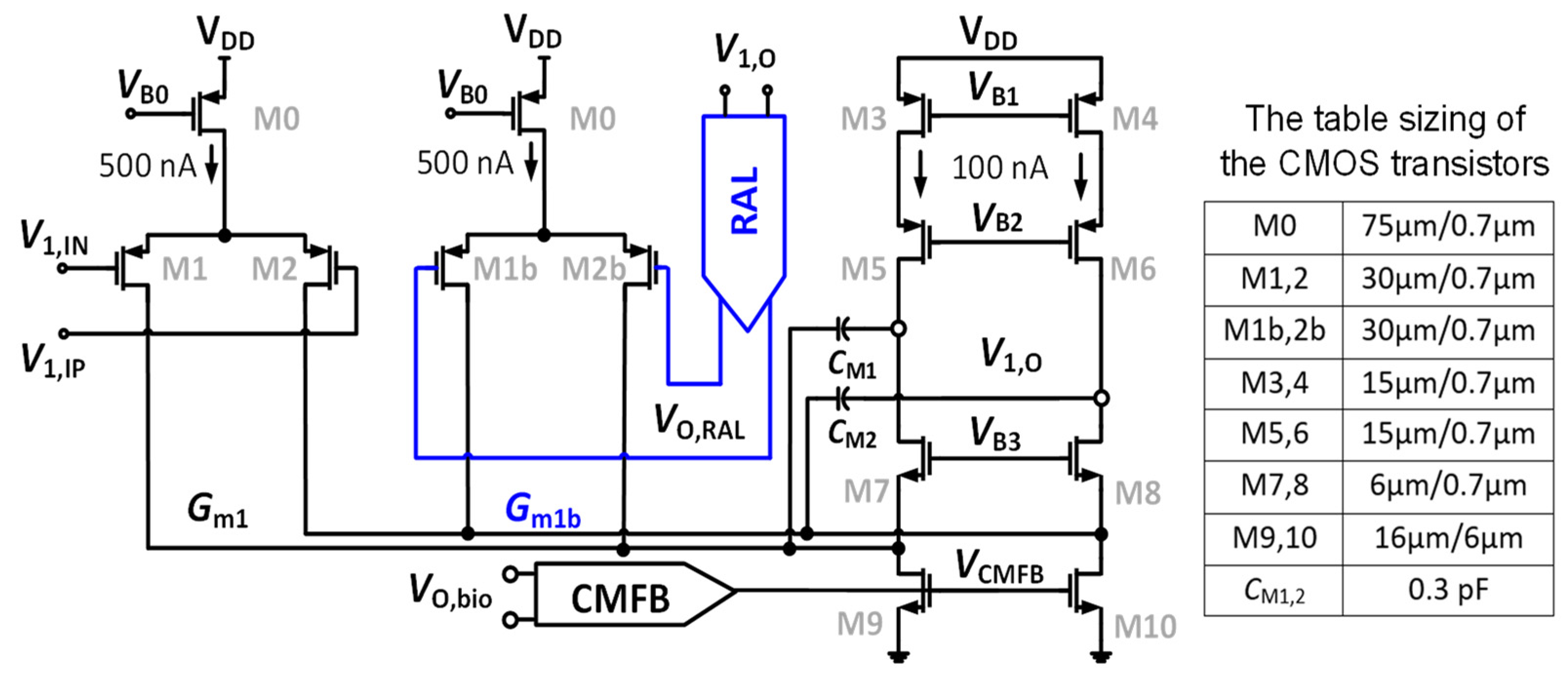

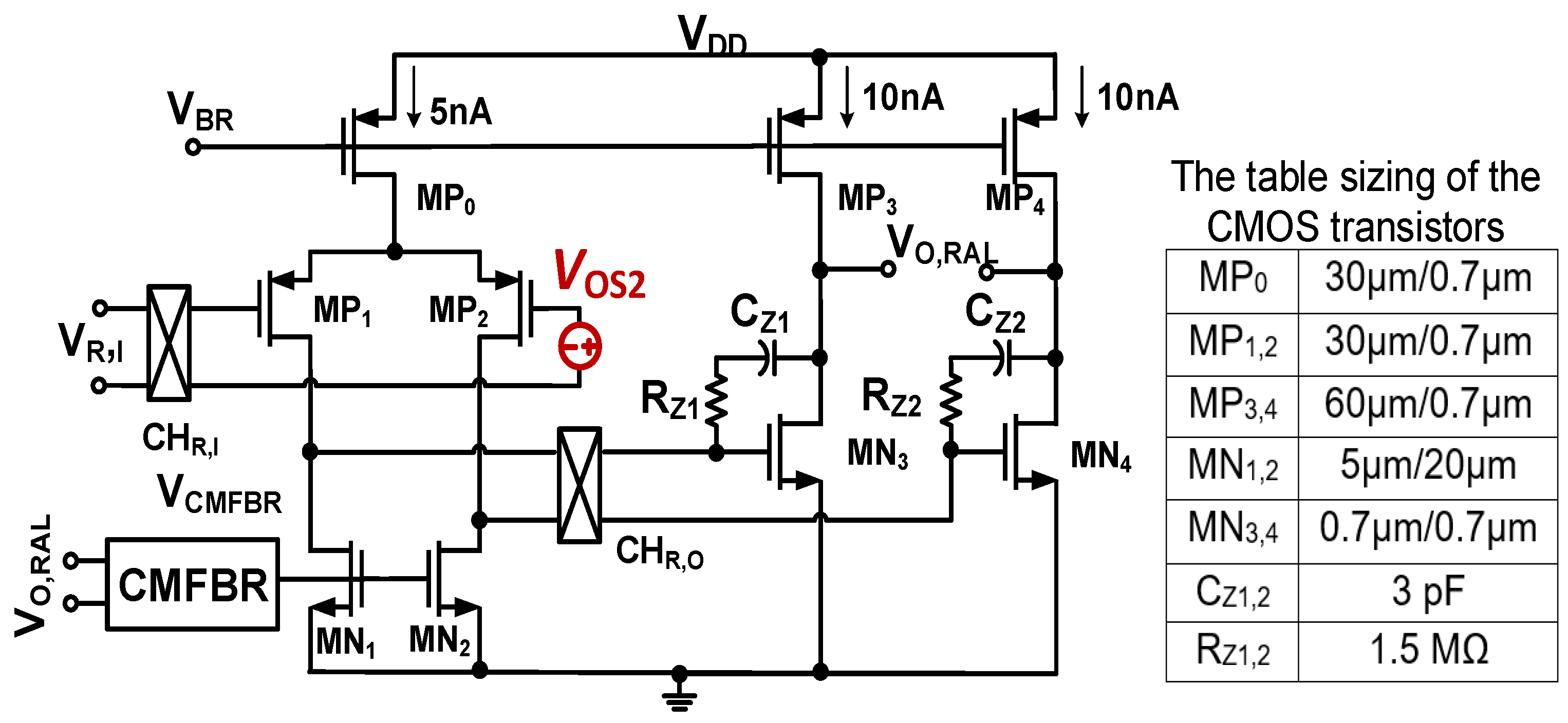

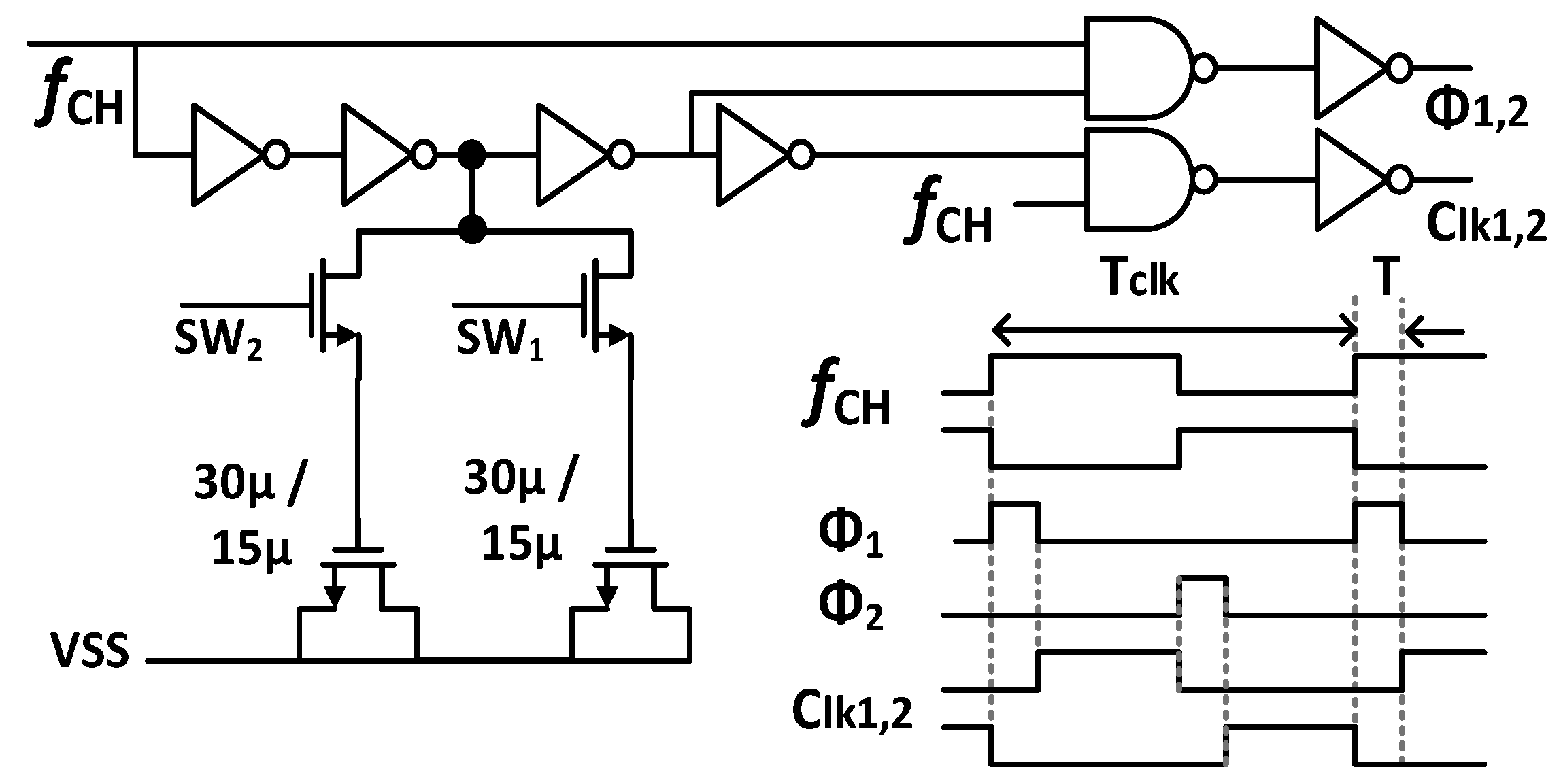

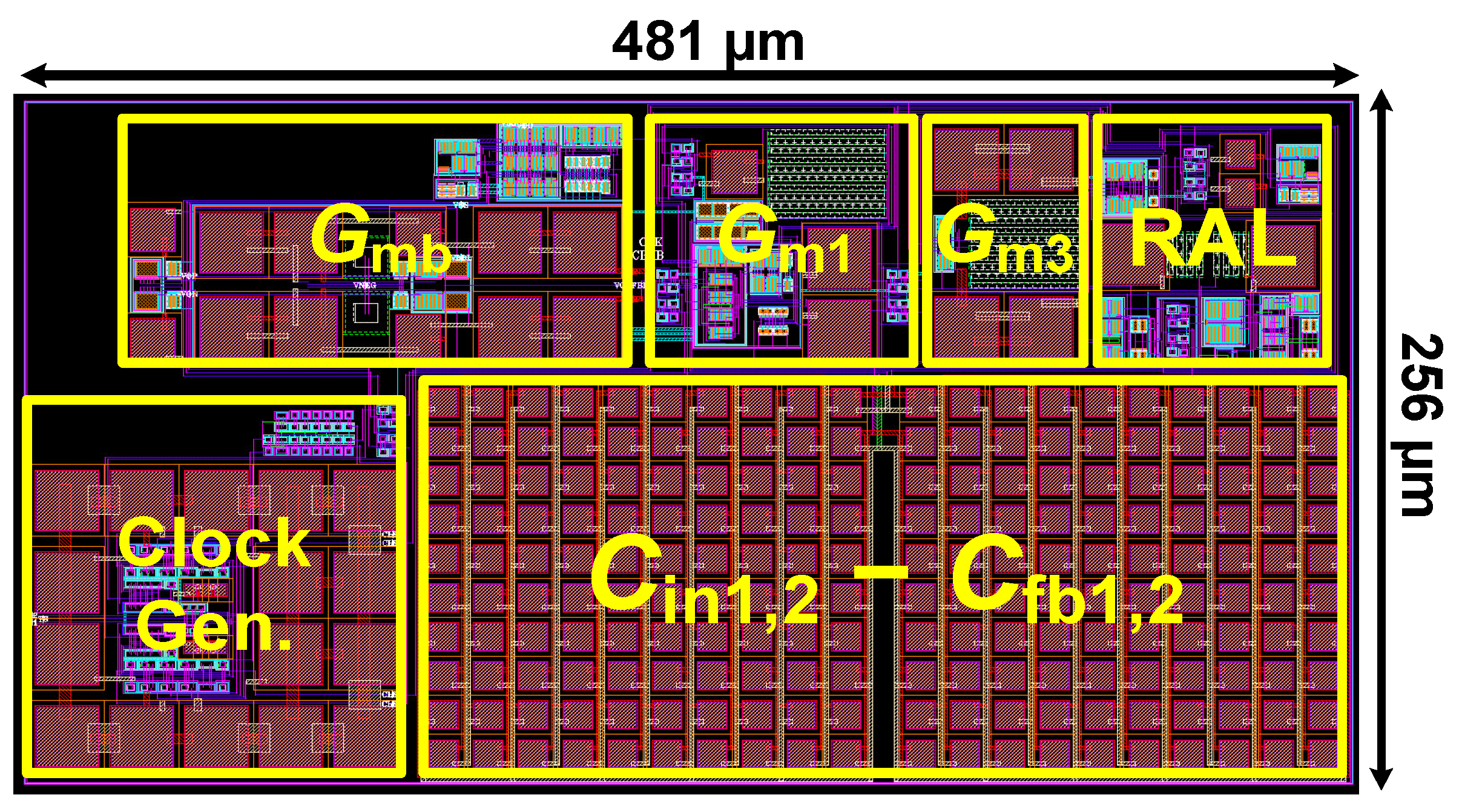

2. Design

3. Circuit Implementation

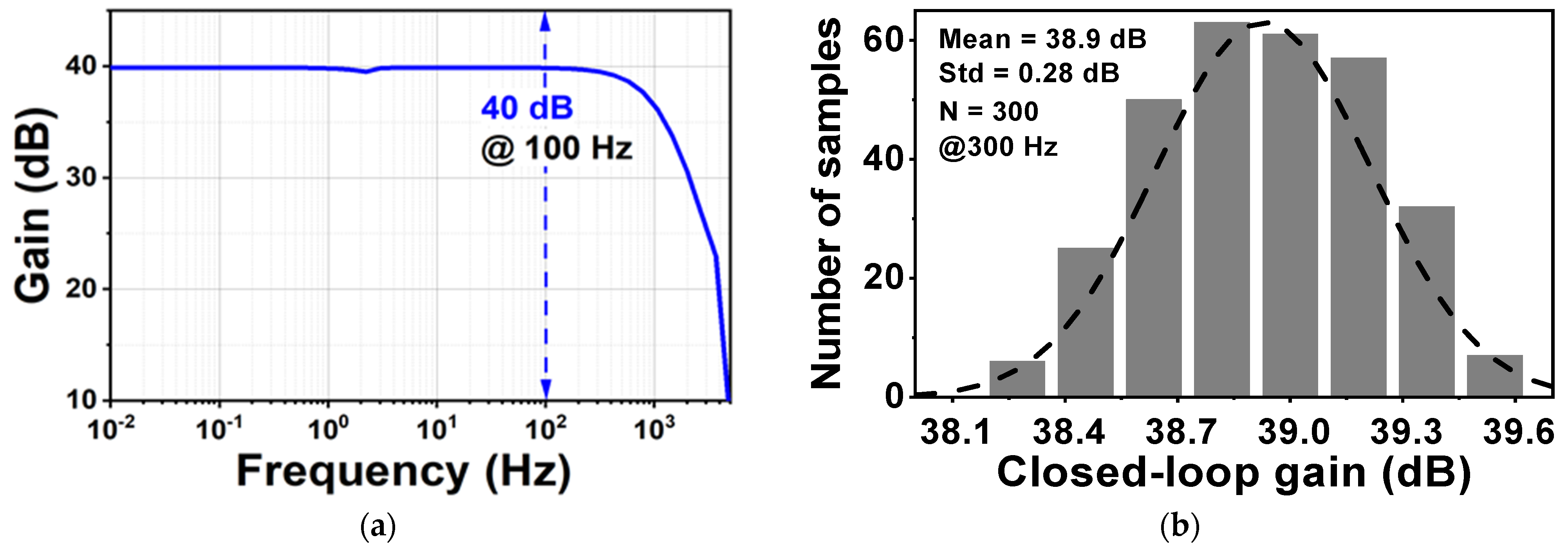

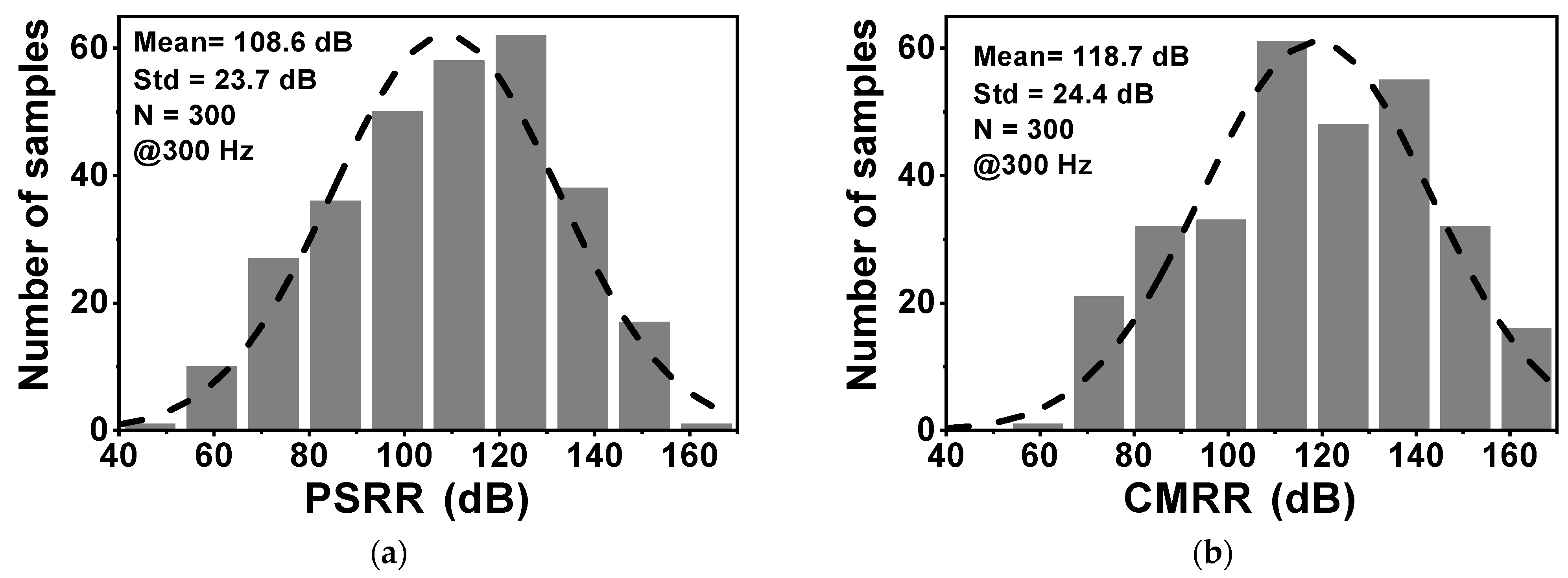

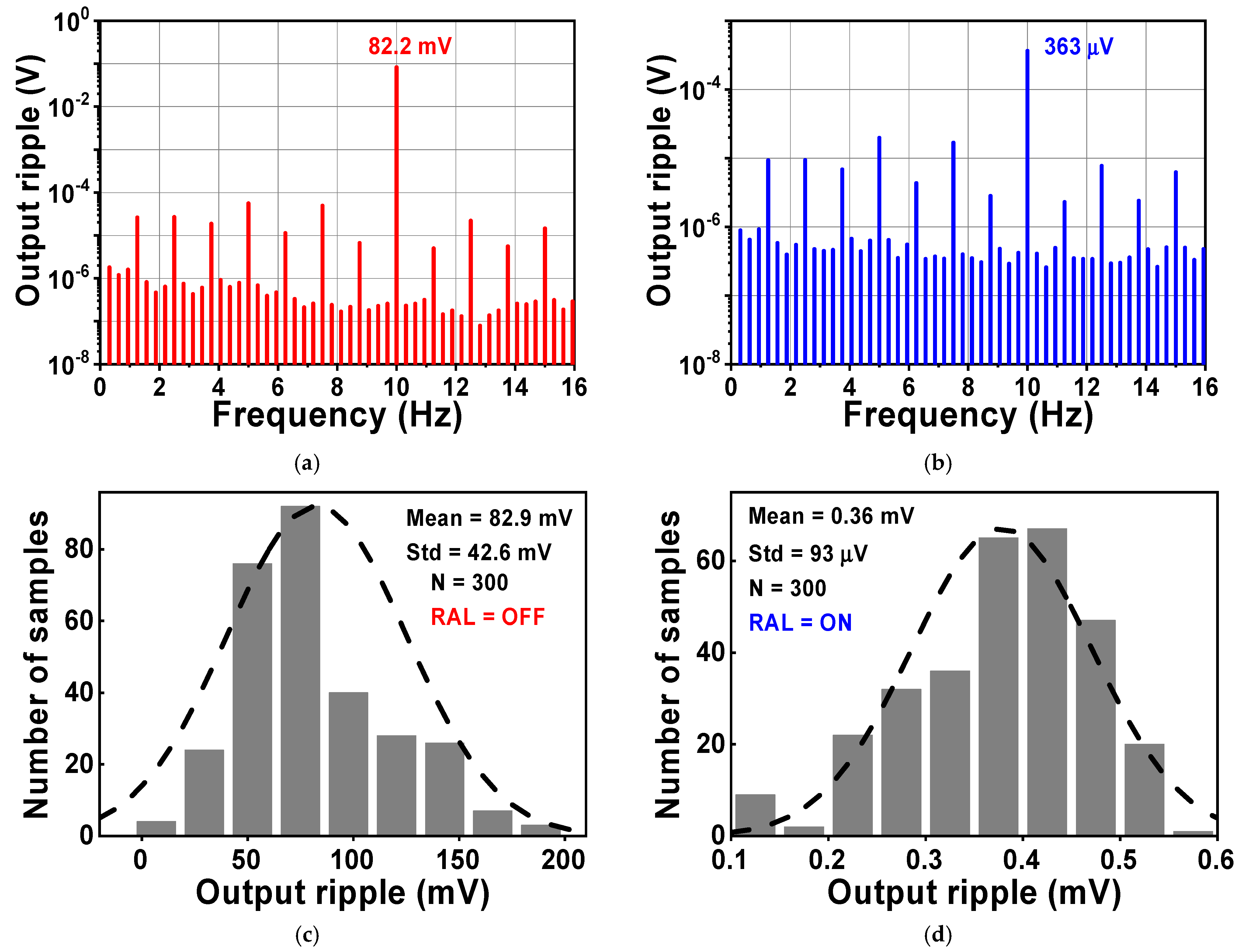

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Tran, X.P.; Pham, X.T.; Kieu, X.T.; Nguyen, L.C.; Pham, D.P.; Hoang, M.K. A 1.8-GΩ Input Impedance 45-dB Ripple Reduction Factor Chopper Amplifier for Biomedical Recording. In Proceedings of the 2023 International Conference on Advanced Technologies for Communications (ATC), Da Nang, Vietnam, 19–21 October 2023. [Google Scholar]

- Wang, S.; Koickal, T.J.; Hamilton, A.; Mastropaolo, E.; Cheung, R.; Abel, A.; Smith, L.S.; Wang, L. A Power-Efficient Capacitive Read-Out Circuit With Parasitic-Cancellation for MEMS Cochlea Sensors. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 25–37. [Google Scholar] [CrossRef] [PubMed]

- Jiang, X.; Bian, G.-B.; Tian, Z. Removal of artifacts from EEG signals: A review. Sensors 2019, 19, 987. [Google Scholar] [CrossRef] [PubMed]

- Lin, C.T.; Ko, L.W.; Chang, M.H.; Duann, J.R.; Chen, J.Y.; Su, T.P.; Jung, T.P. Review of wireless and wearable electroencephalogram systems and brain-computer interfaces-a mini-review. Gerontology 2010, 56, 112–119. [Google Scholar] [CrossRef] [PubMed]

- Fiedler, P.; Mühle, R.; Griebel, S.; Pedrosa, P.; Fonseca, C.; Vaz, F.; Zanow, F.; Haueisen, J. Contact Pressure and Flexibility of Multipin Dry EEG Electrodes. IEEE Trans. Neural Syst. Rehabil. Eng. 2018, 26, 750–757. [Google Scholar] [CrossRef] [PubMed]

- Nguyen, V.-N.; Pham, X.T.; Lee, J.-W. Three-Step Cyclic Vernier TDC Using a Pulse-Shrinking Inverter-Assisted Residue Quantizer for Low-Complexity Resolution Enhancement. IEEE Trans. Instrum. Meas. 2021, 70, 1–12. [Google Scholar] [CrossRef]

- Chandrakumar, H.; Marković, D. A high dynamic-range neural recording chopper amplifier for simultaneous neural recording and stimulation. IEEE J. Solid-State Circuits 2017, 52, 645–656. [Google Scholar] [CrossRef]

- Pham, X.T.; Kieu, X.T.; Hoang, M.K. Ultra-Low Power Programmable Bandwidth Capacitively-Coupled Chopper Instrumentation Amplifier Using 0.2 V Supply for Biomedical Applications. J. Low Power Electron. Appl. 2023, 13, 37. [Google Scholar] [CrossRef]

- Xu, J.; Lin, Q.; Ding, M.; Li, Y.; Van Hoof, C.; Serdijn, W.; Van Helleputte, N. A 0.6V 3.8μW ECG/bio-impedance monitoring IC for disposable health patch in 40nm CMOS. In Proceedings of the 2018 IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 8–11 April 2018. [Google Scholar]

- Yaul, F.M.; Chandrakasan, A.P. A noise-efficient 36 nV/√Hz chopper amplifier using an inverter-based 0.2-V supply input stage. IEEE J. Solid-State Circuits 2017, 52, 3032–3042. [Google Scholar] [CrossRef]

- Huang, G.; Yin, T.; Wu, Q.; Zhu, Y.; Yang, H. A 1.3μW 0.7μVRMS chopper current-reuse instrumentation amplifier for EEG applications. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015. [Google Scholar]

- Wu, R.; Makinwa, K.A.A.; Huijsing, J.H. A Chopper Current-Feedback Instrumentation Amplifier With a 1 mHz 1/f Noise Corner and an AC-Coupled Ripple Reduction Loop. IEEE J. Solid-State Circuits 2009, 44, 3232–3243. [Google Scholar] [CrossRef]

- Park, J.H.; Tang, T.; Zhang, L.; Ng, K.A.; Gammad, G.G.L.; Yen, S.C.; Yoo, J. A 15-Channel Orthogonal Code Chopping Instrumentation Amplifier for Area-Efficient, Low-Mismatch Bio-Signal Acquisition. IEEE J. Solid-State Circuits 2020, 55, 2771–2780. [Google Scholar] [CrossRef]

- Nasseriana, M.; Peiravia, A.; Moradi, F. A fully-integrated 16-channel EEG readout front-end for neural recording applications. AEU—Int. J. Electron. Commun. 2018, 94, 109–121. [Google Scholar] [CrossRef]

- Li, J.; Zhu, L.; Su, R.; Wang, W.; Zhou, Y.; Xie, S.; Mao, G.; Zhou, Z. A Capacitively Coupled Chopper Instrumentation Amplifier With Deadtime Offset Reduction Technique for Neural Signal Sensing. IEEE Sens. Lett. 2024, 8, 1–4. [Google Scholar] [CrossRef]

- Zheng, J.; Ki, W.-H.; Hu, L.; Tsui, C.-Y. Chopper capacitively coupled instrumentation amplifier capable of handling large electrode offset for biopotential recordings. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 1392–1396. [Google Scholar] [CrossRef]

- Wu, J.; Law, M.K.; Mak, P.I.; Martins, R.P. A 2-µW 45-nV/√Hz readout front end with multiple-chopping active-high-pass ripple reduction loop and pseudo feedback DC servo loop. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 351–355. [Google Scholar]

- Chandrakumar, H.; Marković, D. An 80-mVpp Linear-Input Range, 1.6- GΩ Input Impedance, Low-Power Chopper Amplifier for Closed-Loop Neural Recording That Is Tolerant to 650-mVpp Common-Mode Interference. IEEE J. Solid-State Circuits 2017, 52, 2811–2828. [Google Scholar] [CrossRef]

- Zheng, J.; Ki, W.H.; Tsui, C.Y. Analysis and design of ripple reduction chopper bandpass amplifier. IEEE Trans. Circuits Syst. I Reg. Pap. 2018, 65, 1185–1195. [Google Scholar] [CrossRef]

- Chandrakumar, H.; Marković, D. A simple area-efficient ripple rejection technique for chopped biosignal amplifiers. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 189–193. [Google Scholar] [CrossRef]

- Fang, L.; Gui, P. A Low-Noise Low-Power Chopper Instrumentation Amplifier With Robust Technique for Mitigating Chopping Ripples. IEEE J. Solid-State Circuits 2022, 57, 1800–1811. [Google Scholar] [CrossRef]

- Luo, D.; Zhang, M.; Wang, Z. A Low-Noise Chopper Amplifier Designed for Multi-Channel Neural Signal Acquisition. IEEE J. Solid-State Circuits 2019, 54, 2255–2265. [Google Scholar] [CrossRef]

- Wenfei, C.; Yi, L.; Shubin, L.; Ling, W.; Rui, M.; Zhangming, Z. A 2.6 GΩ, 1.4 μVrms current-reuse instrumentation amplifier for wearable electrocardiogram monitoring. Microelectron. J. 2021, 107, 1049. [Google Scholar]

- Chen, X.; Mo, T.; Wu, P.; Wu, B. A Capacitive-Feedback Amplifier with 0.1% THD and 1.18 μVrms Noise for ECG Recording. Electronics 2024, 13, 378. [Google Scholar] [CrossRef]

- Baker, R.J. CMOS Circuit Design, Layout, and Simulation; Wiley: Hoboken, NJ, USA, 2010. [Google Scholar]

- Xu, J.; Fan, Q.; Huijing, J.H.; Hoof, C.V.; Yazicioglu, R.F.; Makinwa, K.A.A. Measurement and Analysis of Current Noise in Chopper Amplifiers. IEEE J. Solid-State Circuits 2013, 48, 1575–1584. [Google Scholar]

- Ha, H.; Hoof, C.V.; Helleputte, N.V. Measurement and Analysis of Input-Signal Dependent Flicker Noise Modulation in Chopper Stabilized Instrumentation Amplifier. IEEE Solid-State Circuits Lett. 2018, 4, 90–93. [Google Scholar] [CrossRef]

- Pham, X.T.; Vu, T.K.; Nguyen, T.D.; Pham-Nguyen, L. A 1.2-µW 41-dB Ripple Attenuation Chopper Amplifier Using Auto-Zero Offset Cancelation Loop for Area-Efficient Biopotential Sensing. Electronics 2022, 11, 1149. [Google Scholar] [CrossRef]

- Xu, W.; Wang, T.; Wei, X.; Yue, H.; Wei, B.; Duan, J.; Li, H. Low Noise, High Input Impedance Digital-Analog Hybrid Offset Suppression Amplifier for Wearable Dry Electrode ECG Monitoring. Electronics 2020, 9, 165. [Google Scholar] [CrossRef]

- Sawigun, C.; Thanapitak, S. A Compact Sub-µW CMOS ECG Amplifier With 57.5-MΩ Zin, 2.02 NEF, 8.16 PEF and 83.24-dB CMRR. IEEE Trans. Biomed. Circuits Syst. 2021, 15, 549–558. [Google Scholar] [CrossRef]

- Chen, M.; Chun, H.S.; Castro, I.D.; Torfs, T.; Lin, Q.; Van Hoof, C.; Wang, G.; Lian, Y.; Van Helleputte, N. A 400 GΩ Input-Impedance Active Electrode for Non-Contact Capacitively Coupled ECG Acquisition With Large Linear-Input-Range and High CM-Interference-Tolerance. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 2. [Google Scholar] [CrossRef]

| Block | Circuit | Components | Power Dissipation (nW) |

|---|---|---|---|

| Dual_FC (Gm1) | OPA-Dual FC | Differential Pair | 500 |

| Differential Pair | 500 | ||

| Cascode Branches | 200 | ||

| CMFB | 200 | ||

| CS (Gm3) | OPA-CS | Common source | 400 |

| RAL (Gm2) | Stage-1 | Differential Pair | 5 |

| Stage-2 | Common source | 20 | |

| CMFB2 | 5 | ||

| IBL (Gmb) | Buffer | 42 | |

| Total | 1872 | ||

| Ref. | [18] | [23] | [24] | [28] | [29] | [30] | [31] | This Work |

|---|---|---|---|---|---|---|---|---|

| Year | 2017 | 2021 | 2024 | 2022 | 2020 | 2021 | 2019 | 2024 |

| Power (µW) | 2 | 5.94 | 1.5 | 1.21 | 19.8 | 0.672 | 1.2 | 1.87 |

| Supply (V) | 1.2 | 1.8 | 2.47 | 1 | 1.8 | 2 | 5 | 1 |

| Output ripple (mV) | 0.012 | NA | NA | 0.061 | NA | NA | NA | 0.36 |

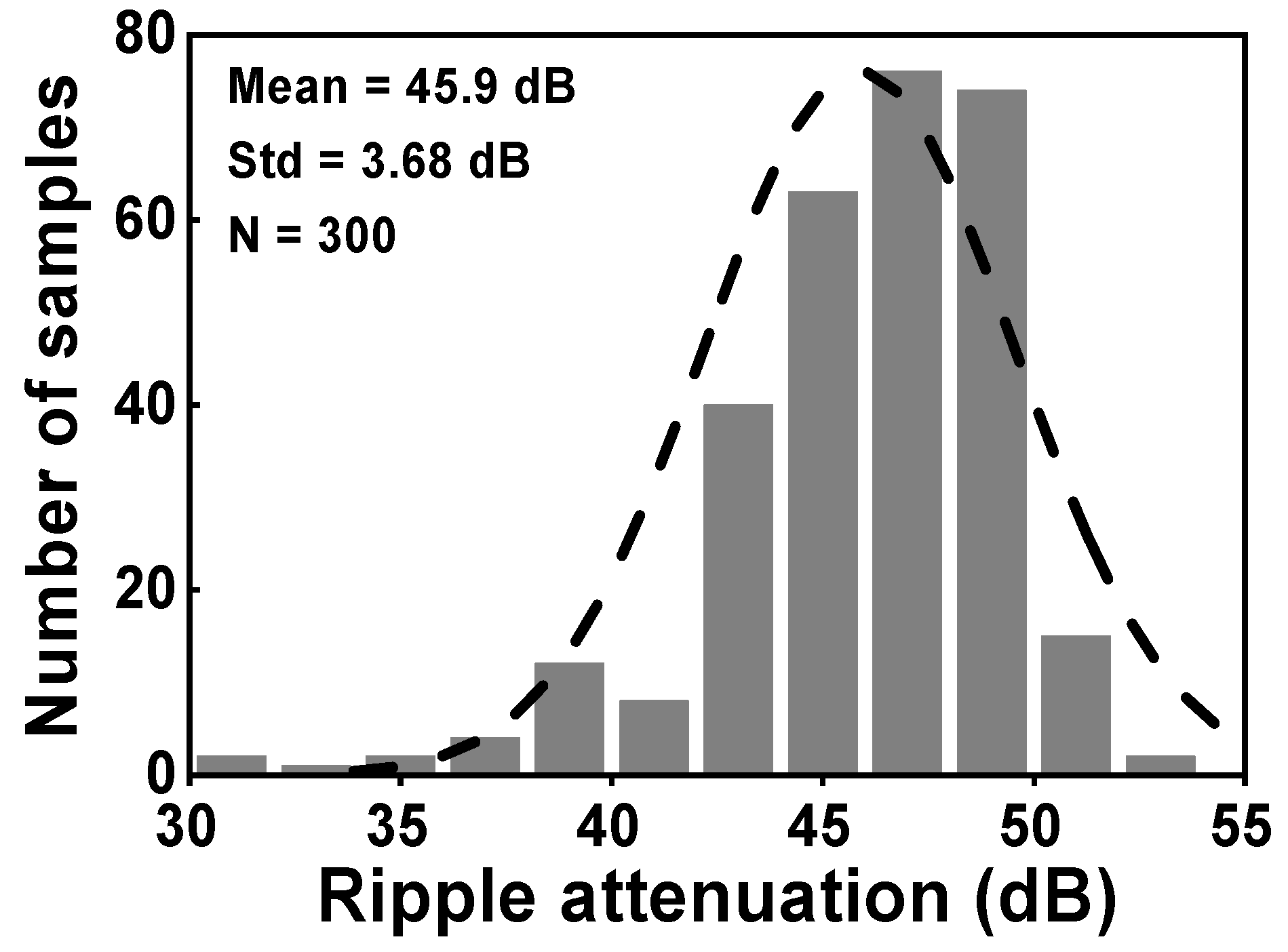

| Ripple Attennuation (dB) | NA | NA | NA | >41 | NA | NA | NA | 45.9 |

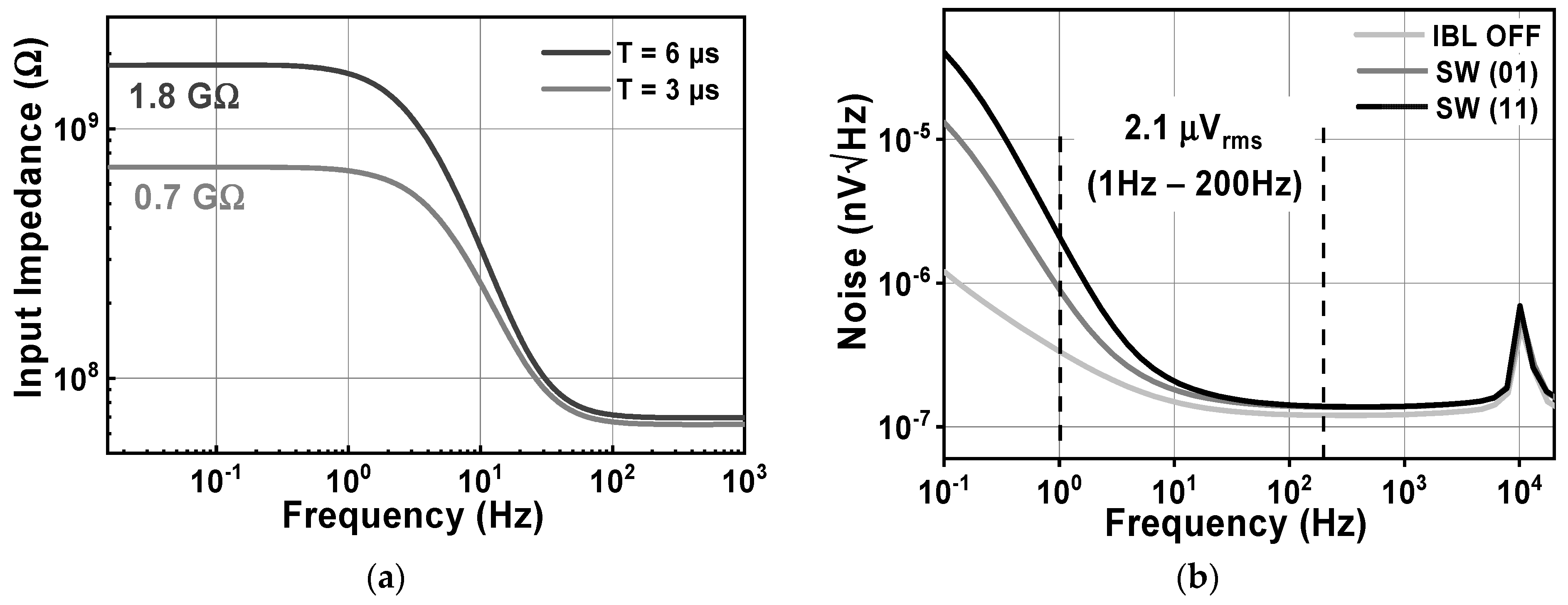

| Zin (GΩ) | 0.3 | 2.6 | NA | NA | 2.1 | 0.0575 | 400 | 1.8 |

| Gain (dB) | 25.7 | 40 | 59.7 | 40 | 46 | 40.6 | 20 | 40 |

| PSRR (dB) | NA | 85 | >70 | 87 | NA | 84.2 | N/A | 108.6 |

| CMRR (dB) | NA | 93 | >87 | 108 | 96 | 83.24 | >70 | 118.7 |

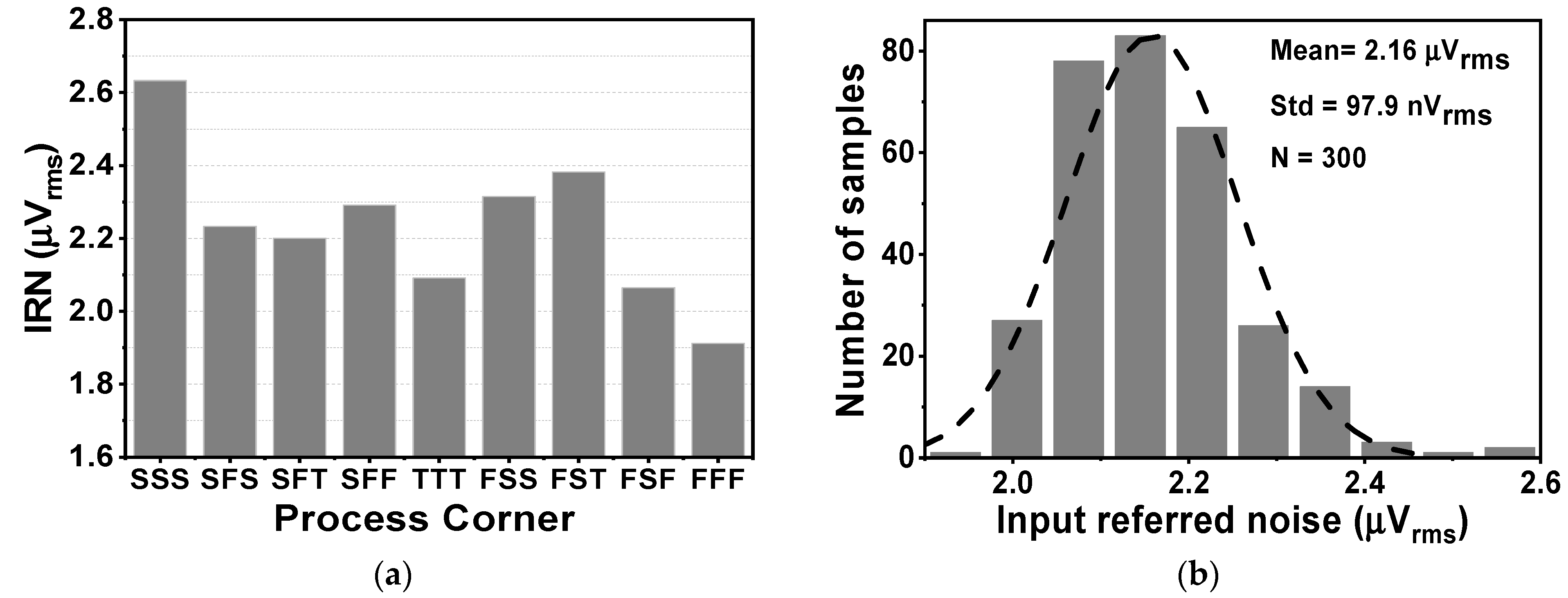

| IRN (µVrms) | 9 | 1.4 | 1.18 | 1.8 | 1.9 | 2.01 | 3.7 | 2.16 |

| NEF | 7 | NA | 2.13 | 5.4 | NA | 2.63 | NA | 7.5 |

| Tech. (nm) | 40 | 180 | 130 | 180 | 180 | 350 | 180 | 180 |

| Meas./Sim. | Meas. | Meas. | Sim. | Sim. | Sim. | Meas. | Meas. | Sim. |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tran, X.P.; Kieu, X.T.; Pham, X.T.; Pham, D.P.; Hoang, M.K. A 1.87 µW Capacitively Coupled Chopper Instrumentation Amplifier with a 0.36 mV Output Ripple and a 1.8 GΩ Input Impedance for Biomedical Recording. J. Low Power Electron. Appl. 2024, 14, 37. https://doi.org/10.3390/jlpea14030037

Tran XP, Kieu XT, Pham XT, Pham DP, Hoang MK. A 1.87 µW Capacitively Coupled Chopper Instrumentation Amplifier with a 0.36 mV Output Ripple and a 1.8 GΩ Input Impedance for Biomedical Recording. Journal of Low Power Electronics and Applications. 2024; 14(3):37. https://doi.org/10.3390/jlpea14030037

Chicago/Turabian StyleTran, Xuan Phuong, Xuan Thuc Kieu, Xuan Thanh Pham, Duy Phong Pham, and Manh Kha Hoang. 2024. "A 1.87 µW Capacitively Coupled Chopper Instrumentation Amplifier with a 0.36 mV Output Ripple and a 1.8 GΩ Input Impedance for Biomedical Recording" Journal of Low Power Electronics and Applications 14, no. 3: 37. https://doi.org/10.3390/jlpea14030037

APA StyleTran, X. P., Kieu, X. T., Pham, X. T., Pham, D. P., & Hoang, M. K. (2024). A 1.87 µW Capacitively Coupled Chopper Instrumentation Amplifier with a 0.36 mV Output Ripple and a 1.8 GΩ Input Impedance for Biomedical Recording. Journal of Low Power Electronics and Applications, 14(3), 37. https://doi.org/10.3390/jlpea14030037