Wideband Cascaded and Stacked Receiver Front-Ends Employing an Improved Clock-Strategy Technique

Abstract

:1. Introduction

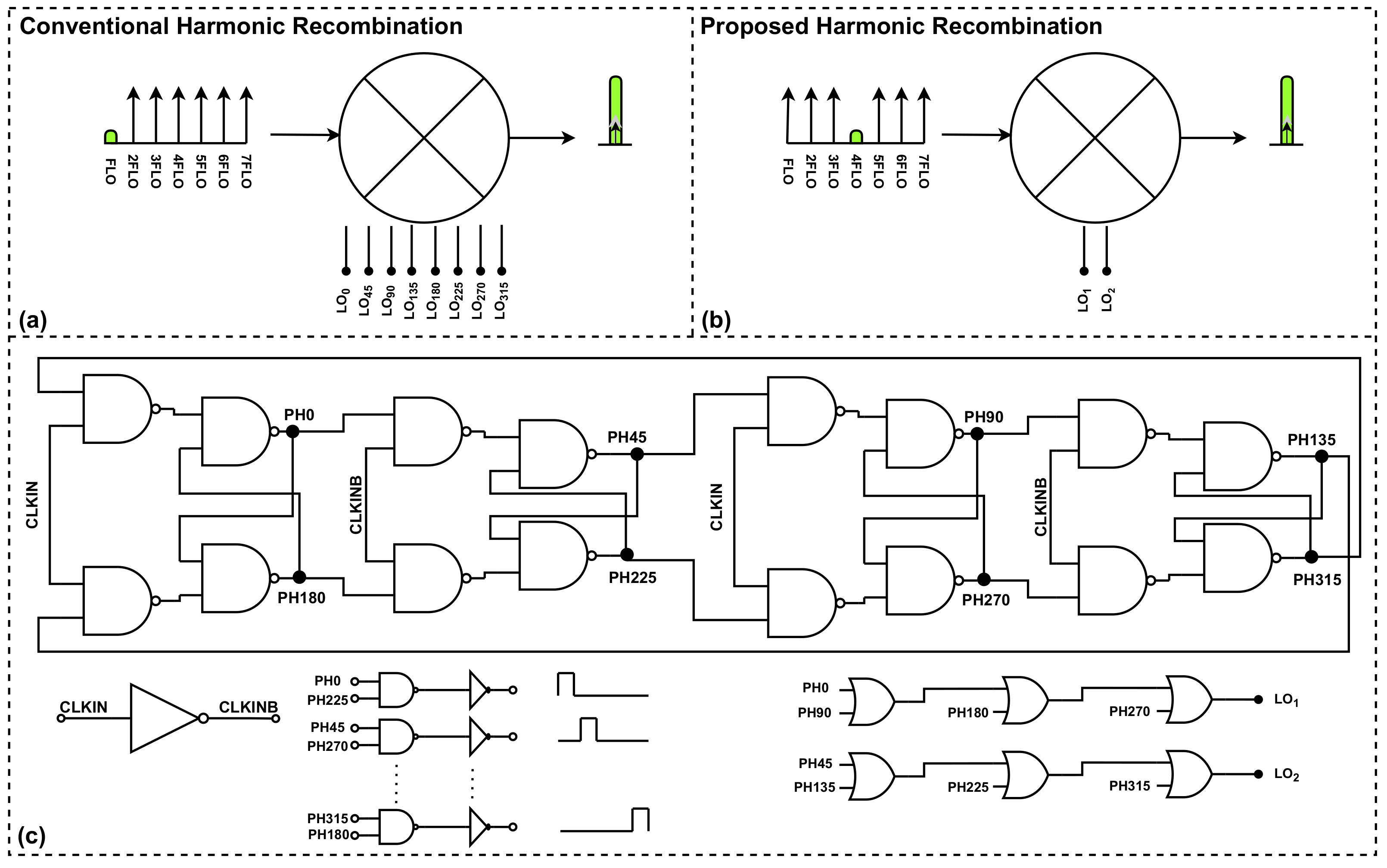

2. Clock Strategy Technique

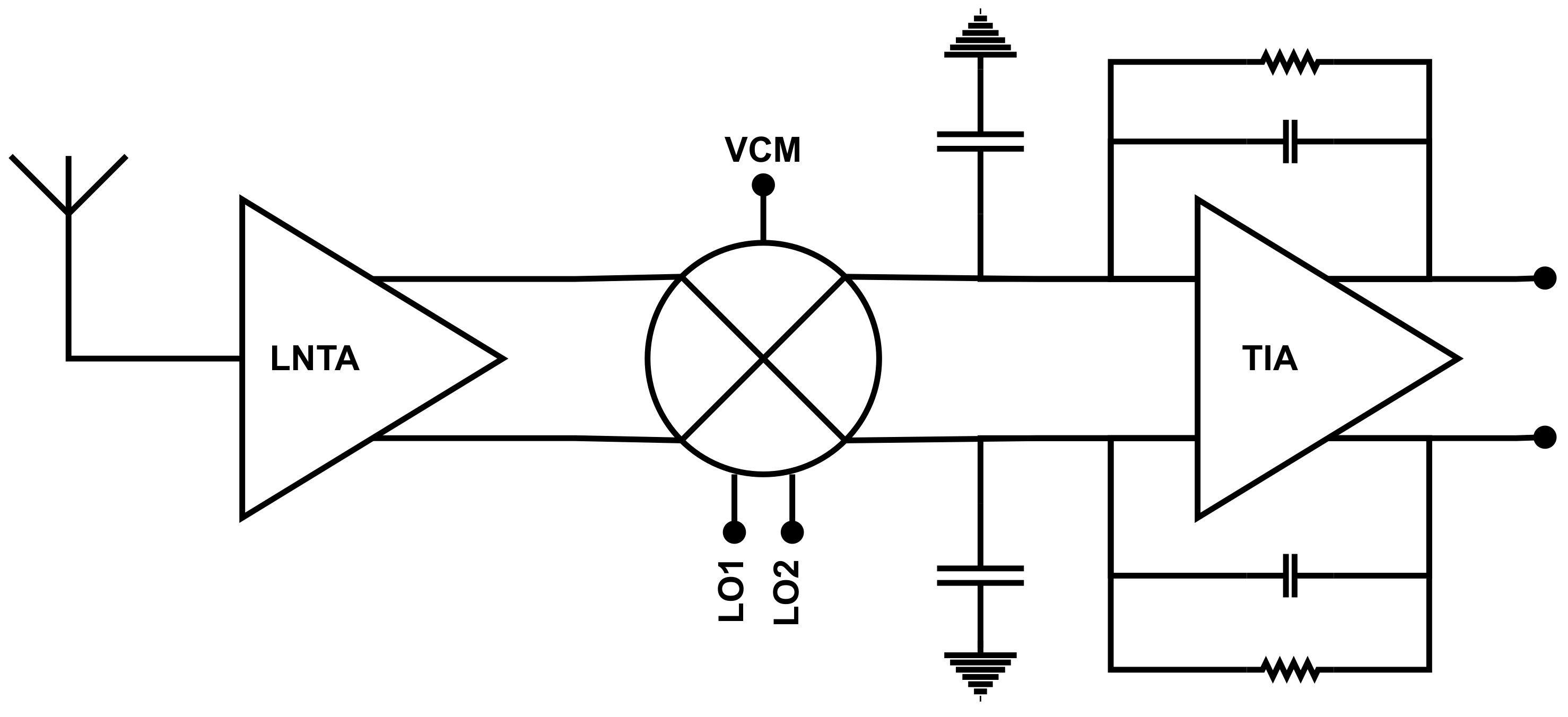

3. Cascaded Receiver Front-End Using the Proposed Clock Strategy

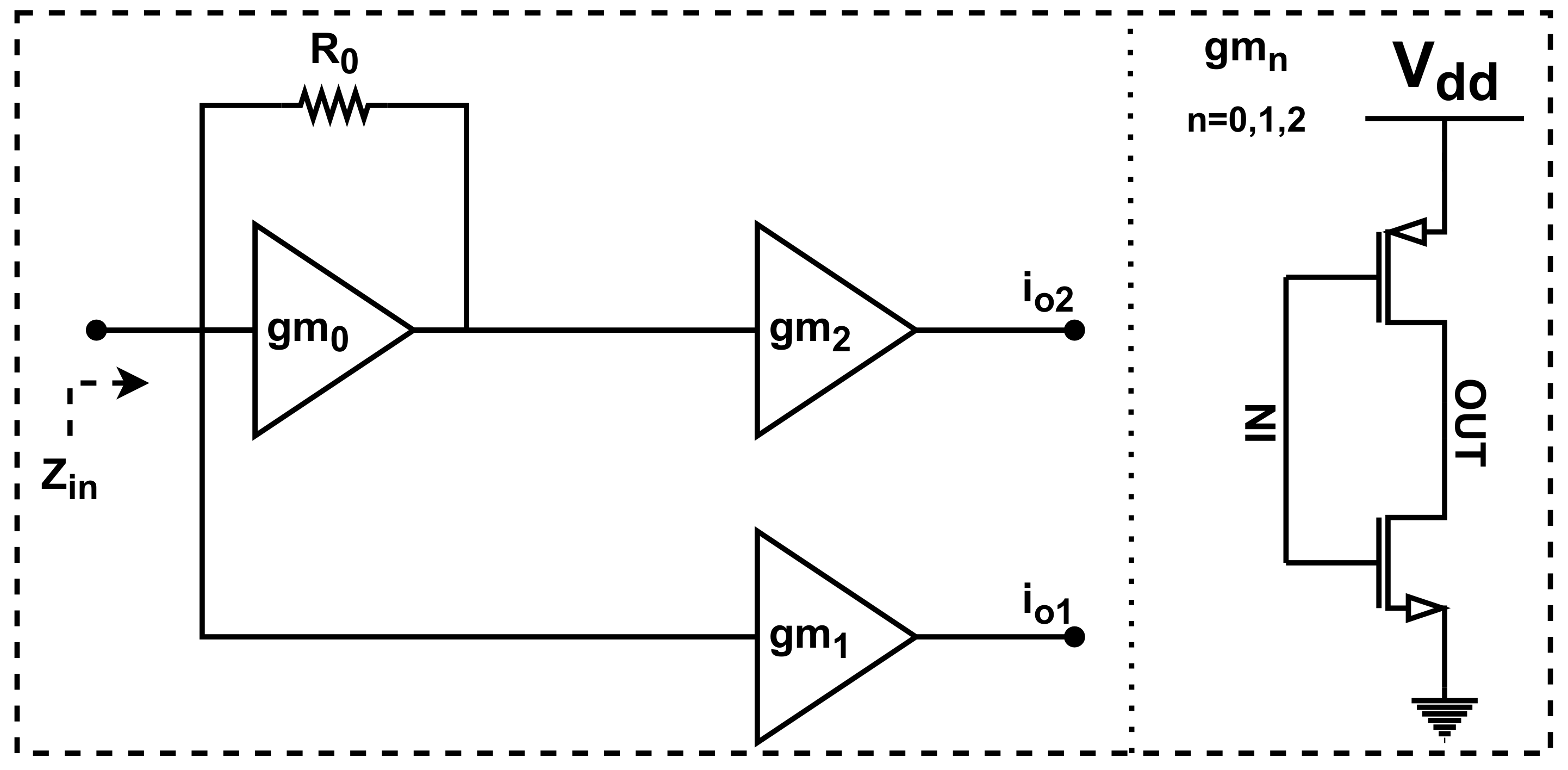

3.1. LNTA Design

3.2. Mixer Design

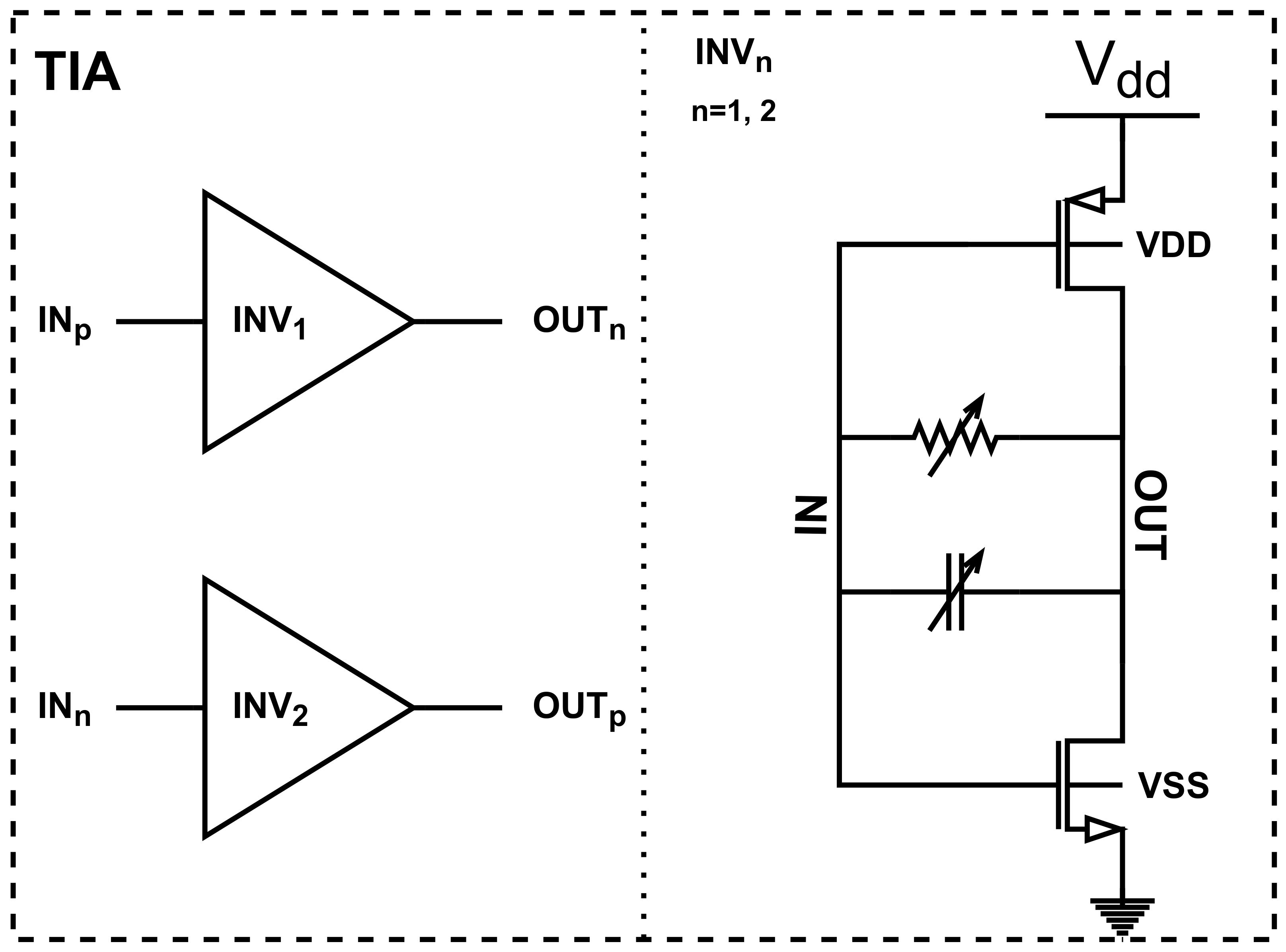

3.3. TIA Design

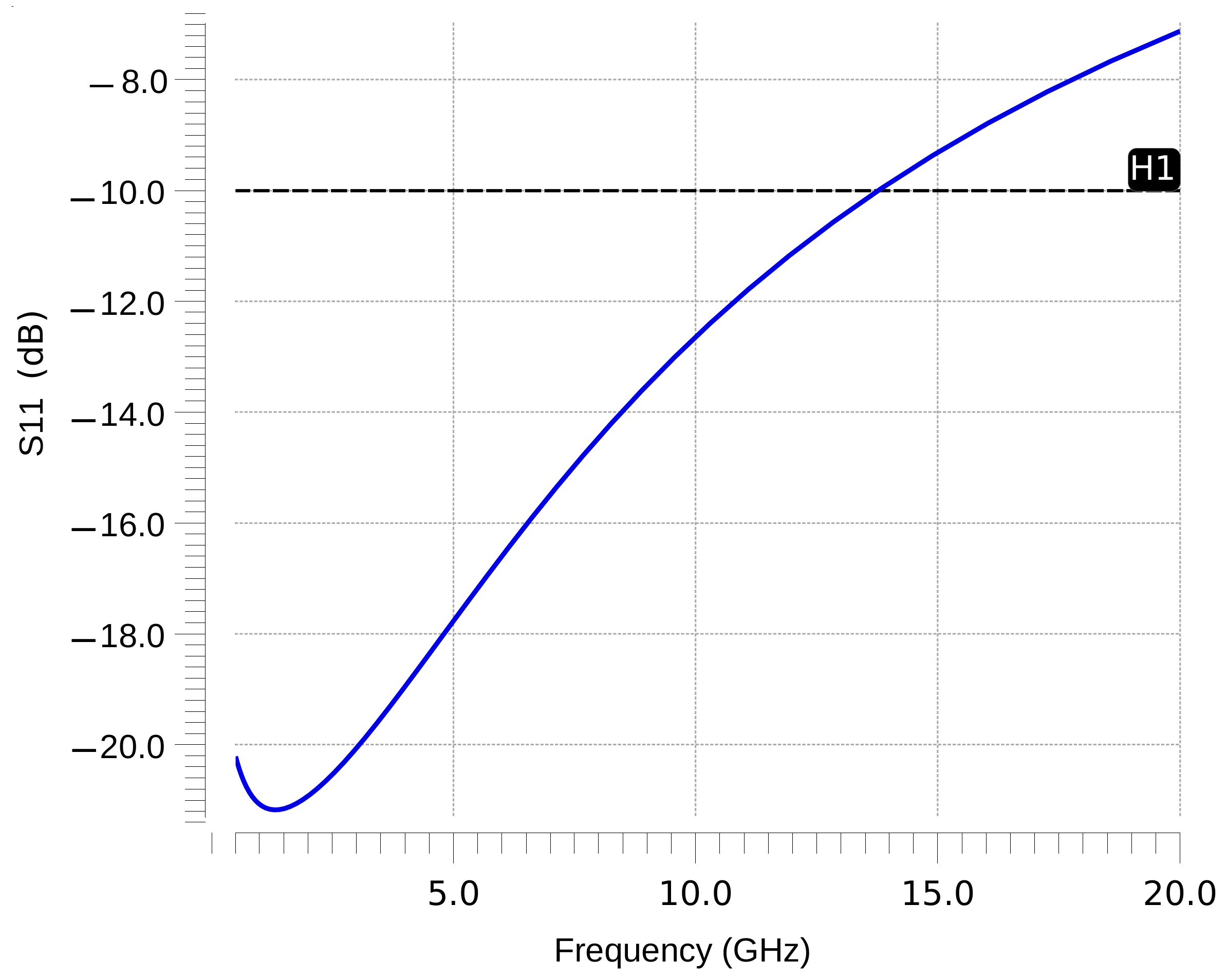

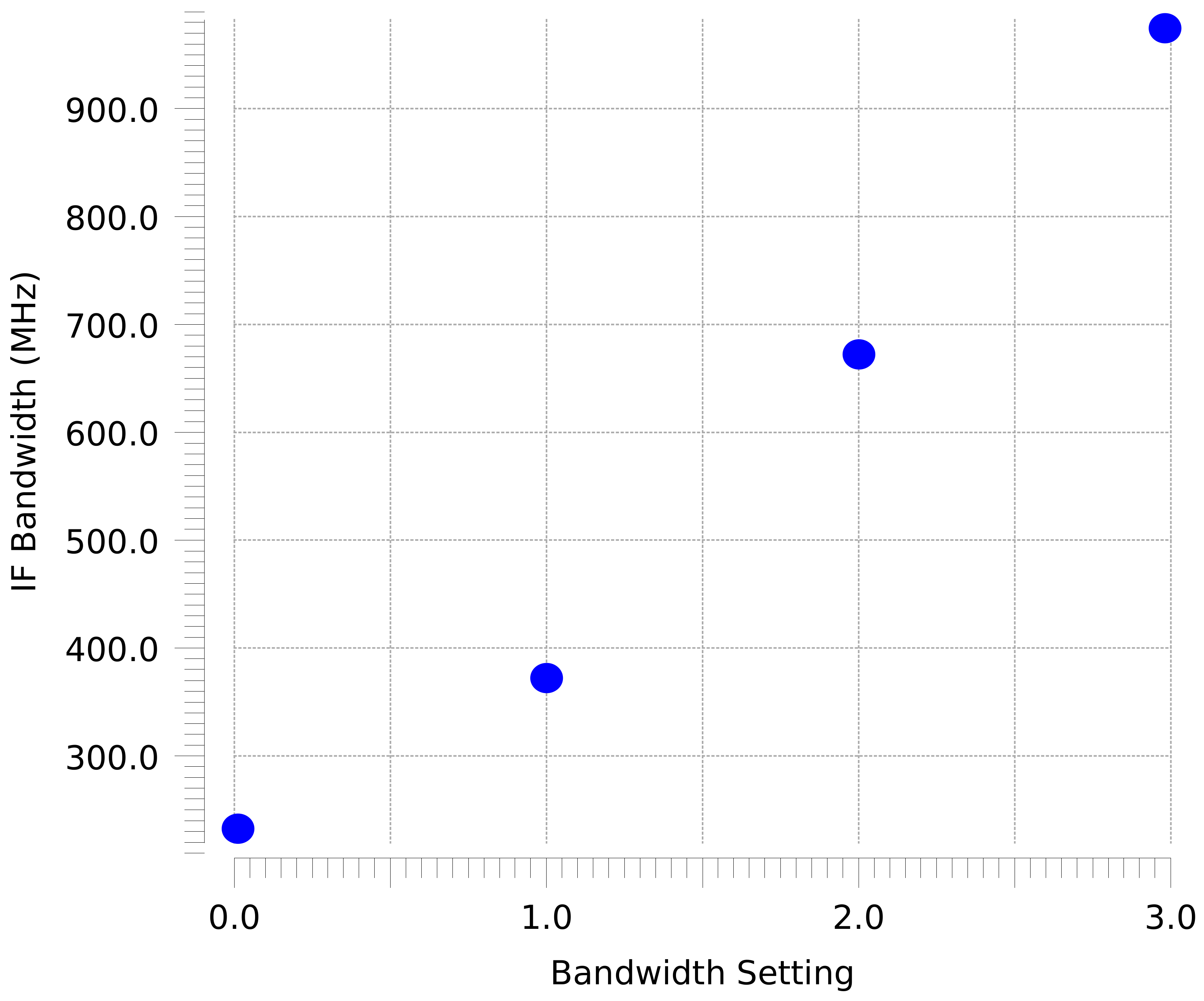

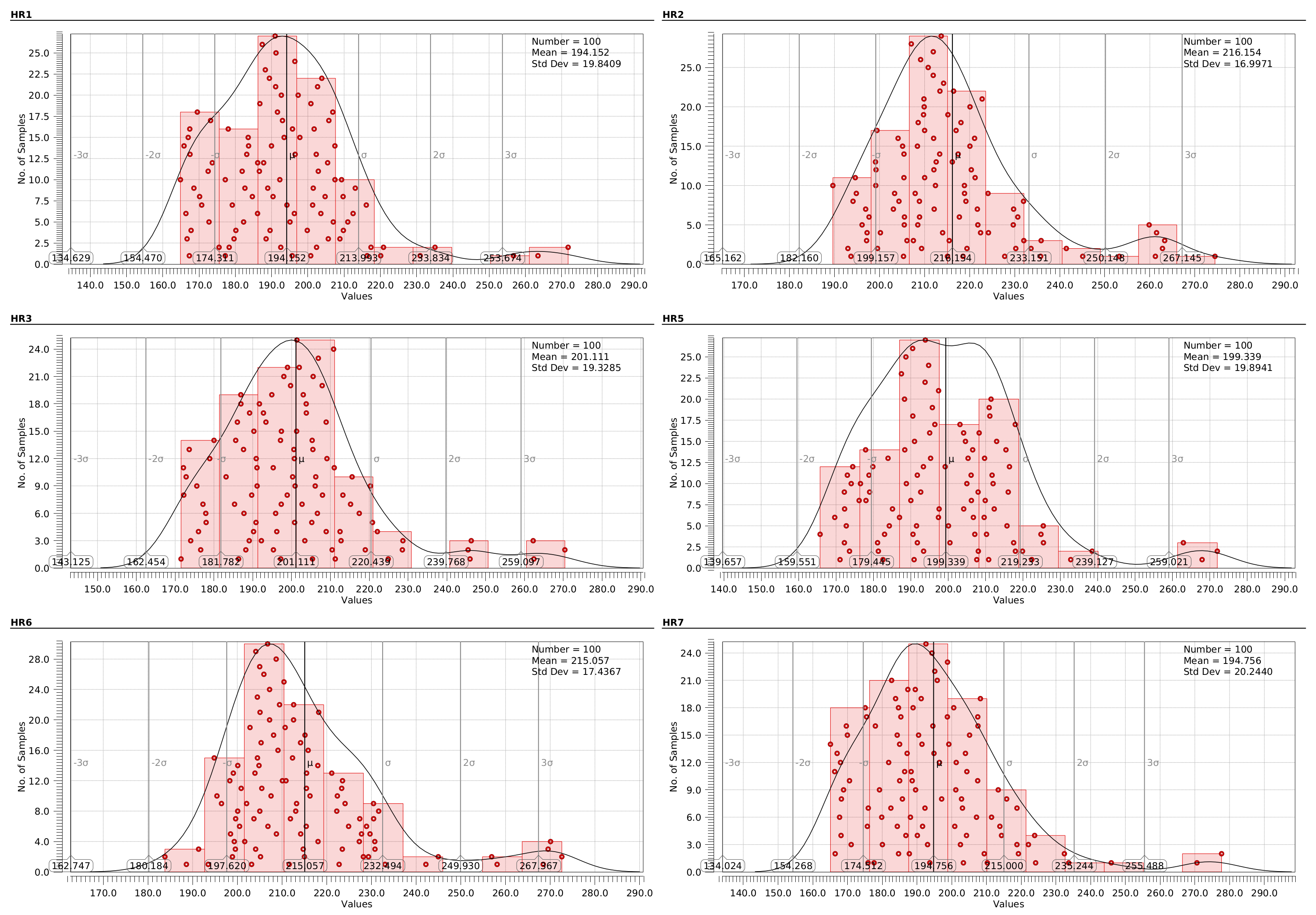

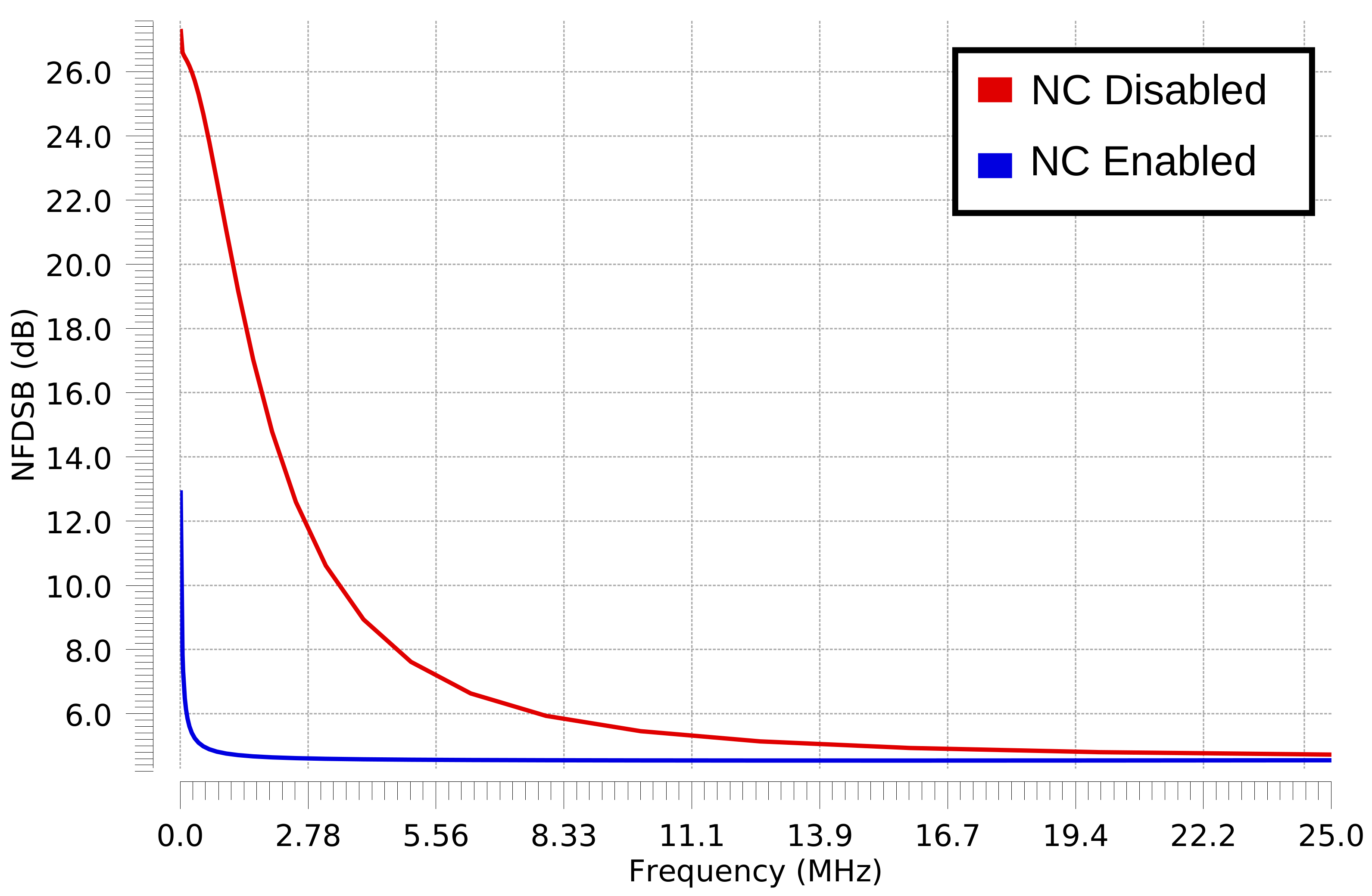

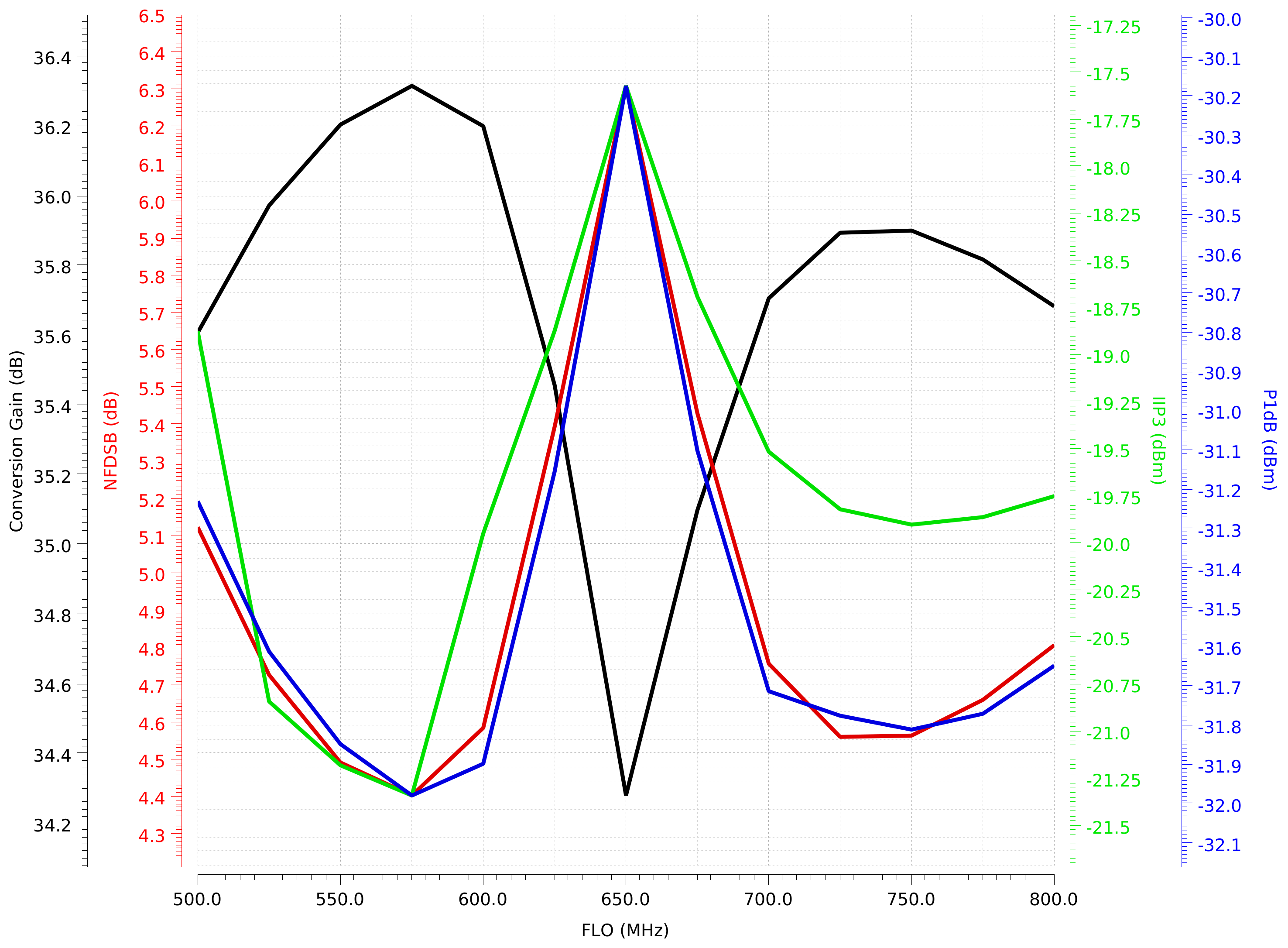

3.4. Simulation Results of the Cascaded Receiver Front-End

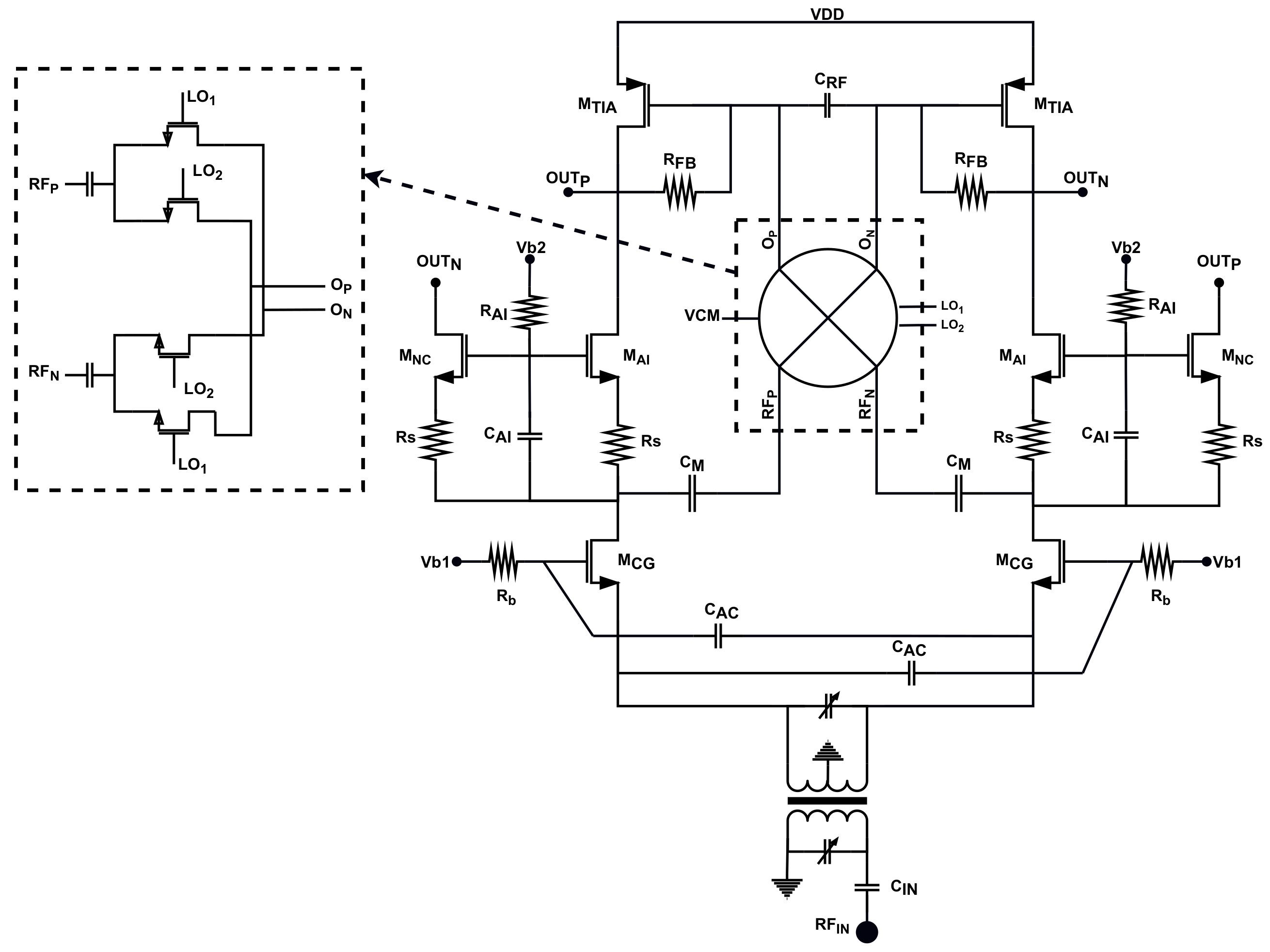

4. Stacked Receiver Front-End Using the Proposed Clock Strategy

4.1. LNTA Design

4.2. Active-Inductor and Noise-Cancellation Design

4.3. TIA Design

4.4. Simulation Results of the Stacked Receiver Front-End

5. Discussion

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| ADC | Analog-to-digital converter |

| AI | Active inductor |

| AIC | Adaptive interference cancelling |

| CG | Common-gate |

| CCC | Capacitor cross-coupled |

| CMOS | Complementary metal–oxide semiconductor |

| CS | Common-source |

| ÉTS | École de technologie supérieure |

| FDSOI | Fully depleted silicon on insulator |

| HR | Harmonic rejection |

| IF | Intermediate frequency |

| IIP3 | Third-order intercept point |

| IoT | Internet of things |

| LNA | Low-noise amplifier |

| LNTA | Low-noise transconductance amplifier |

| LO | Local-oscillator |

| NF | Noise figure |

| NC | Noise cancellation |

| NFDSB | Double side-band noise figure |

| RF | Radio frequency |

| SDR | Software-defined radio |

| TIA | Transimpedance amplifier |

| VCO | Voltage-controlled oscillator |

| Voltage-threshold | |

| Tranconductance |

References

- Mitola, J. The software radio architecture. IEEE Commun. Mag. 1995, 33, 26–38. [Google Scholar] [CrossRef]

- Ke, Y.; Gao, P.; Craninckx, J.; Van der Plas, G.; Gielen, G. A 2.8-to-8.5 mW GSM/bluetooth/UMTS/DVB-H/WLAN fully reconfigurable CT ΔΣ with 200kHz to 20MHz BW for 4G radios in 90nm digital CMOS. In Proceedings of the 2010 Symposium on VLSI Circuits, Honolulu, HI, USA, 16–18 June 2020; IEEE: Piscataway Township, NJ, USA, 2010; pp. 153–154. [Google Scholar]

- Murphy, D.; Darabi, H.; Xu, H. A noise-cancelling receiver resilient to large harmonic blockers. IEEE J. -Solid-State Circuits 2015, 50, 1336–1350. [Google Scholar] [CrossRef]

- Lin, F.; Mak, P.I.; Martins, R.P. An RF-to-BB-current-reuse wideband receiver with parallel N-path active/passive mixers and a single-MOS pole-zero LPF. IEEE J. -Solid-State Circuits 2014, 49, 2547–2559. [Google Scholar] [CrossRef]

- Elmi, M.; Tavassoli, M.; Jalali, A. A wideband receiver front-end using 1st and 3rd harmonics of the N-path filter response. Analog. Integr. Circuits Signal Process. 2018, 94, 451–467. [Google Scholar] [CrossRef]

- Zinjanab, A.P.; Jalali, A.; Farshi, H.T. A standard and harmonic blocker tolerant receiver front-end using a harmonic rejection differential N-path notch filter and blocks withstand to possible variations. AEU-Int. J. Electron. Commun. 2020, 125, 153356. [Google Scholar] [CrossRef]

- Andrews, C.; Molnar, A.C. A passive mixer-first receiver with digitally controlled and widely tunable RF interface. IEEE J. -Solid-State Circuits 2010, 45, 2696–2708. [Google Scholar] [CrossRef]

- Lien, Y.C.; Klumperink, E.A.; Tenbroek, B.; Strange, J.; Nauta, B. Enhanced-selectivity high-linearity low-noise mixer-first receiver with complex pole pair due to capacitive positive feedback. IEEE J. -Solid-State Circuits 2018, 53, 1348–1360. [Google Scholar] [CrossRef]

- Zolkov, E.; Cohen, E. A Mixer-First Receiver With Enhanced Matching Bandwidth by Using Baseband Reactance-Canceling LNA. IEEE Solid-State Circuits Lett. 2021, 4, 109–112. [Google Scholar] [CrossRef]

- Mohammadpour, A.; Manstretta, D.; Castello, R. A 140-μW Front-End With 5.7-dB NF and+ 10-dBm OOB-IIP3 Using Voltage-Mode Boosting Mixer. IEEE Microw. Wirel. Components Lett. 2021, 31, 729–732. [Google Scholar] [CrossRef]

- Bazrafshan, A.; Taherzadeh-Sani, M.; Nabki, F. A 0.8–4-GHz software-defined radio receiver with improved harmonic rejection through non-overlapped clocking. IEEE Trans. Circuits Syst. Regul. Pap. 2018, 65, 3186–3195. [Google Scholar] [CrossRef]

- Shams, N.; Nabki, F. Analysis and Comparison of Low-Power 6-GHz N-Path-Filter-Based Harmonic Selection RF Receiver Front-End Architectures. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2022, 30, 253–266. [Google Scholar] [CrossRef]

- Abbasi, A.; Moshrefi, A.H.; Nabki, F. A Wideband Low-Power Current-Reuse RF-to-BB Receiver Using a Clock Strategy Technique. In Proceedings of the 2022 20th IEEE Interregional NEWCAS Conference (NEWCAS), Quebec, QC, Canada, 19–22 June 2022; IEEE: Piscataway Township, NJ, USA, 2022; pp. 275–279. [Google Scholar]

- Weldon, J.A.; Narayanaswami, R.S.; Rudell, J.C.; Lin, L.; Otsuka, M.; Dedieu, S.; Tee, L.; Tsai, K.C.; Lee, C.W.; Gray, P.R. A 1.75-GHz highly integrated narrow-band CMOS transmitter with harmonic-rejection mixers. IEEE J. -Solid-State Circuits 2001, 36, 2003–2015. [Google Scholar] [CrossRef]

- Ru, Z.; Moseley, N.A.; Klumperink, E.A.; Nauta, B. Digitally enhanced software-defined radio receiver robust to out-of-band interference. IEEE J. -Solid-State Circuits 2009, 44, 3359–3375. [Google Scholar] [CrossRef]

- Wu, H.; Murphy, D.; Darabi, H. A harmonic-selective multi-band wireless receiver with digital harmonic rejection calibration. IEEE J. -Solid-State Circuits 2019, 54, 796–807. [Google Scholar] [CrossRef]

- Xu, Y.; Zhu, J.; Kinget, P.R. A Blocker-Tolerant RF Front End With Harmonic-Rejecting N-Path Filter. IEEE J. -Solid-State Circuits 2017, 53, 327–339. [Google Scholar] [CrossRef]

- Bagheri, R.; Mirzaei, A.; Chehrazi, S.; Heidari, M.E.; Lee, M.; Mikhemar, M.; Tang, W.; Abidi, A.A. An 800-MHz–6-GHz software-defined wireless receiver in 90-nm CMOS. IEEE J. -Solid-State Circuits 2006, 41, 2860–2876. [Google Scholar] [CrossRef]

- Manetakis, K.; McKay, T.G. Wideband Low Noise Amplifier Having DC Loops with Back Gate Biased Transistors. US Patent 10,700,653, 30 June 2023. [Google Scholar]

- Tedeschi, M.; Liscidini, A.; Castello, R. Low-power quadrature receivers for ZigBee (IEEE 802.15. 4) applications. IEEE J. -Solid-State Circuits 2010, 45, 1710–1719. [Google Scholar] [CrossRef]

- Lin, Z.; Mak, P.I.; Martins, R.P. A 2.4 GHz ZigBee Receiver Exploiting an RF-to-BB-Current-Reuse Blixer+ Hybrid Filter Topology in 65 nm CMOS. IEEE J. -Solid-State Circuits 2014, 49, 1333–1344. [Google Scholar] [CrossRef]

- Kim, S.; Kwon, K. A Low-Power RF-to-BB-Current-Reuse Receiver Employing Simultaneous Noise and Input Matching and 1/f Noise Reduction for IoT Applications. IEEE Microw. Wirel. Components Lett. 2019, 29, 614–616. [Google Scholar] [CrossRef]

- Abbasi, A.; Nabki, F. A Design Methodology for Wideband Current-Reuse Receiver Front-Ends Aimed at Low-Power Applications. Electronics 2022, 11, 1493. [Google Scholar] [CrossRef]

- Abbasi, A.; Moshrefi, A.H.; Nabki, F. A Wideband Low-Power RF-to-BB Current-Reuse Receiver Using an Active Inductor and 1/f Noise-Cancellation for L-Band Applications. IEEE Access 2022, 10, 95839–95848. [Google Scholar] [CrossRef]

| Value (dB) | −Inf | −Inf | −Inf | 2.2 | −Inf | −Inf | −Inf |

| Freq. (GHz) | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| Parameters | This Work Cascaded | This WorkStacked | [12] | [4] | [16] | [10] | [9] | [3] |

|---|---|---|---|---|---|---|---|---|

| Process node | 22 nm CMOS | 22 nm CMOS | 65 nm CMOS | 65 nm CMOS | 28 nm CMOS | 28 nm CMOS | 65 nm CMOS | 28 nm CMOS |

| Freq. (GHz) | 0.4–13 | 2–6 | 5.7–7.2 | 0.15–0.85 | 0.5–3 | 1–2 | 0.5–2 | 0.1–3.3 |

| S11 (dB) | <−10 | <−10 | <−10 | <−10 | <−10 | <−10 | <−10 | N/A |

| Gain (dB) | 26–36 | 34.5–36 | 36.4 | 51 | 42 | 29.4 | 36 | N/A |

| NF (dB) | 1.4–3.9 | 4.6–6.2 | 4.4 | 5.4 | 2.4–5 | 5.7 | 2.2–4.2 | 1.7 |

| IIP3 (dBm) | −10.5–7.5 | −21–17.5 * | −18.9 * | −12 * | 4 | −10 * | −11 * | 11.5 |

| 11 | 2.9 | 13 | 7.5 | 21 | 0.141 | 41–65 | 36.8–62.4 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Abbasi, A.; Nabki, F. Wideband Cascaded and Stacked Receiver Front-Ends Employing an Improved Clock-Strategy Technique. J. Low Power Electron. Appl. 2023, 13, 14. https://doi.org/10.3390/jlpea13010014

Abbasi A, Nabki F. Wideband Cascaded and Stacked Receiver Front-Ends Employing an Improved Clock-Strategy Technique. Journal of Low Power Electronics and Applications. 2023; 13(1):14. https://doi.org/10.3390/jlpea13010014

Chicago/Turabian StyleAbbasi, Arash, and Frederic Nabki. 2023. "Wideband Cascaded and Stacked Receiver Front-Ends Employing an Improved Clock-Strategy Technique" Journal of Low Power Electronics and Applications 13, no. 1: 14. https://doi.org/10.3390/jlpea13010014

APA StyleAbbasi, A., & Nabki, F. (2023). Wideband Cascaded and Stacked Receiver Front-Ends Employing an Improved Clock-Strategy Technique. Journal of Low Power Electronics and Applications, 13(1), 14. https://doi.org/10.3390/jlpea13010014