A 1.1 V 25 ppm/°C Relaxation Oscillator with 0.045%/V Line Sensitivity for Low Power Applications

Abstract

:1. Introduction

2. Review of Reported Relaxation Oscillator

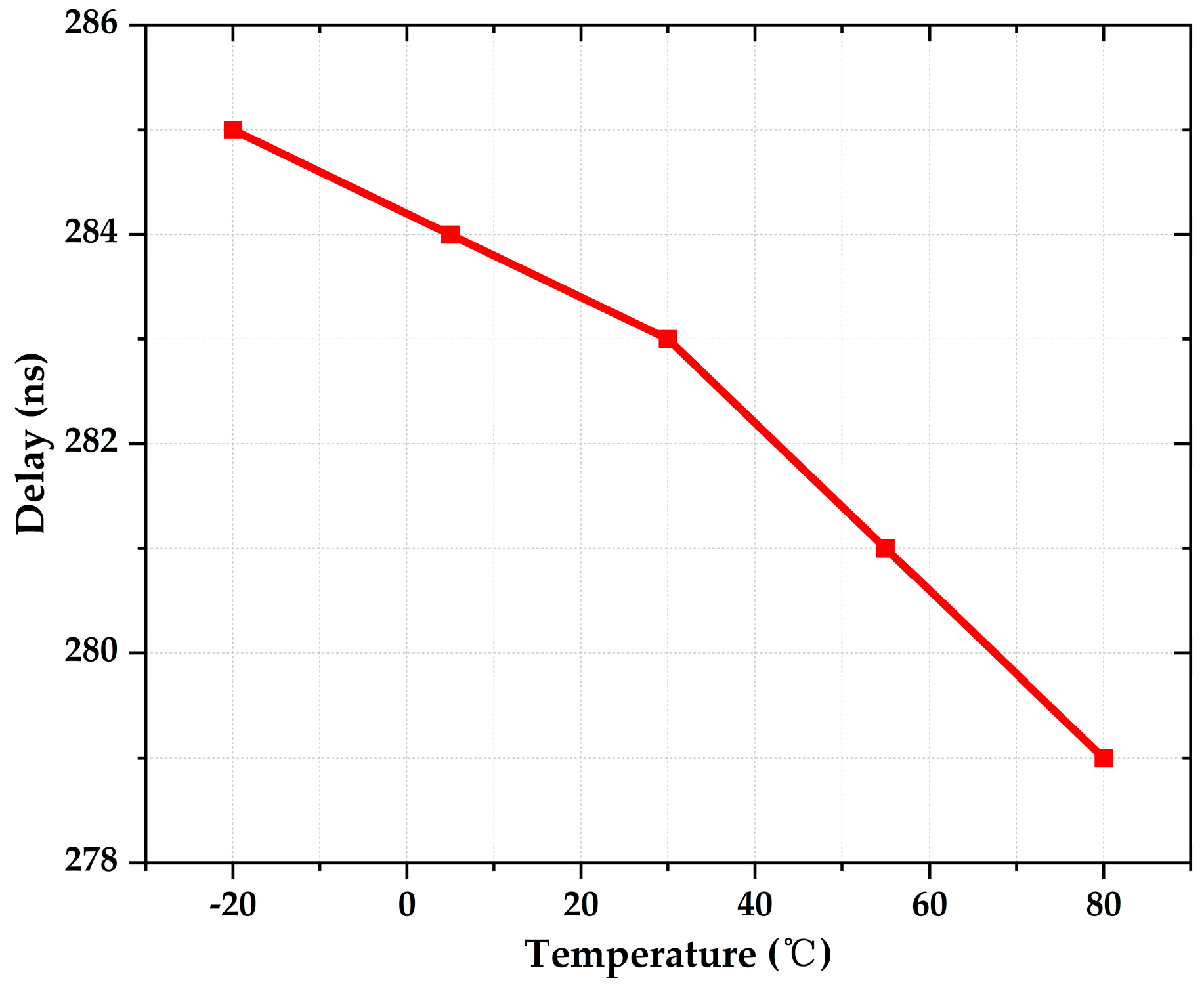

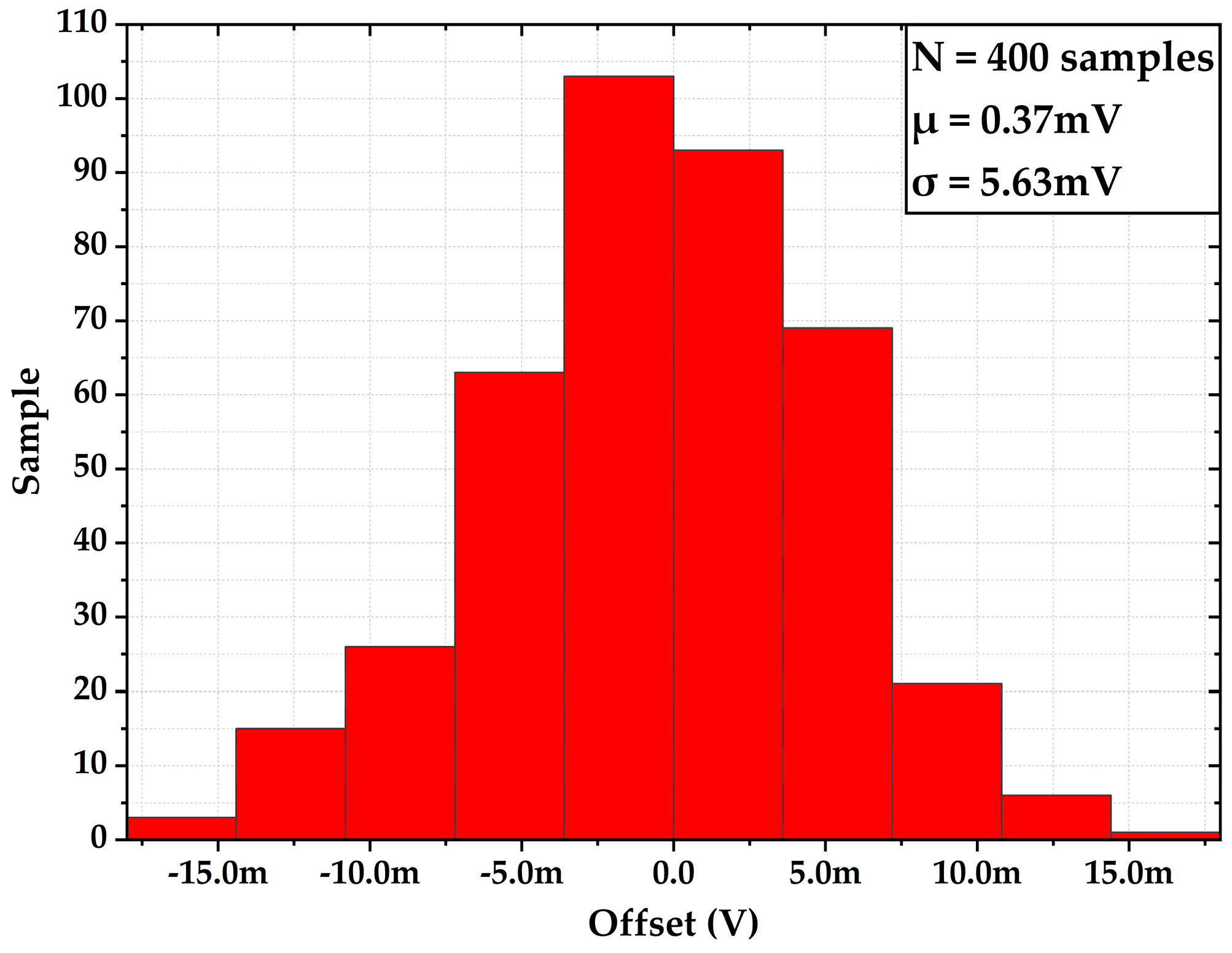

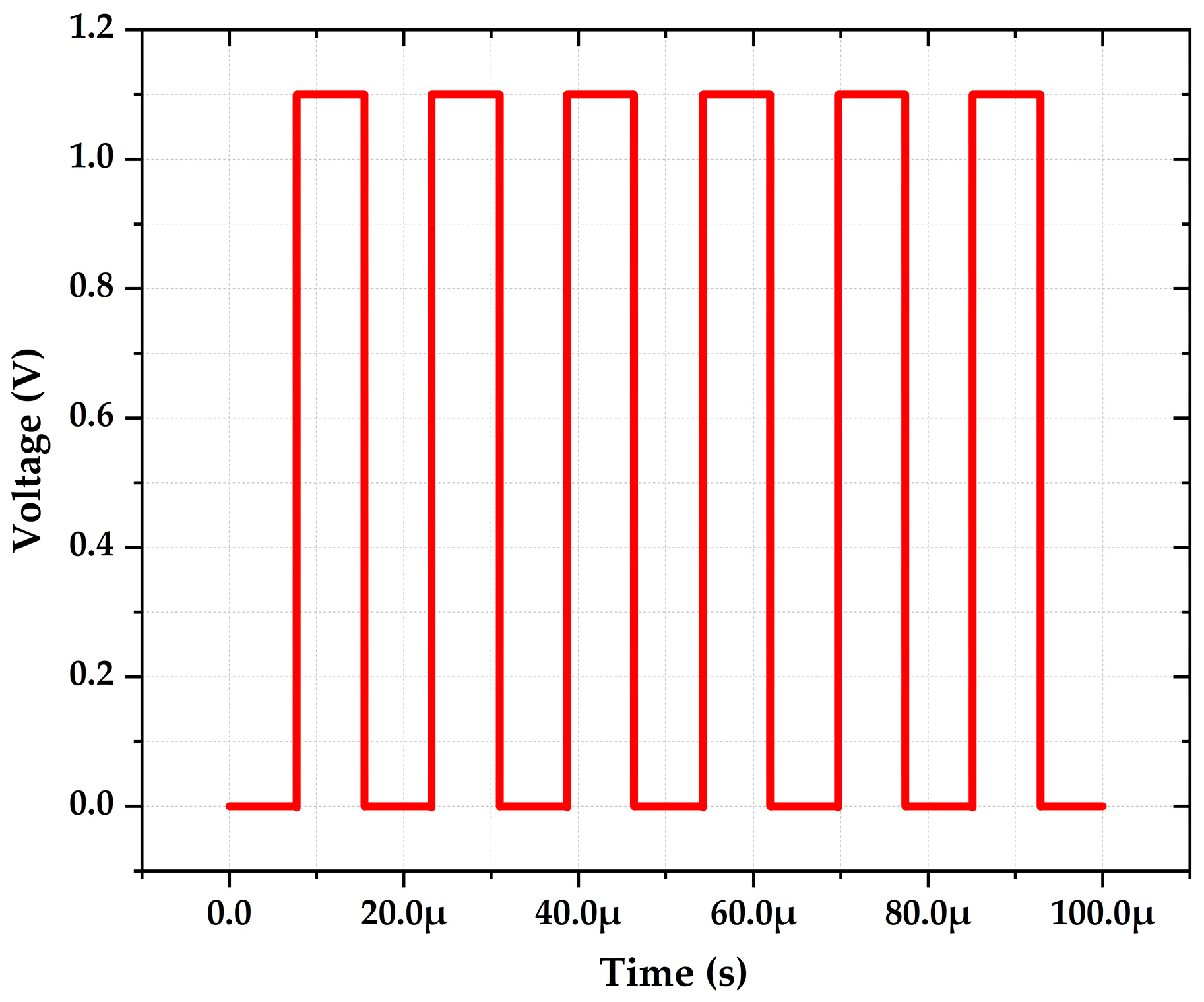

3. Proposed Relaxation Oscillator

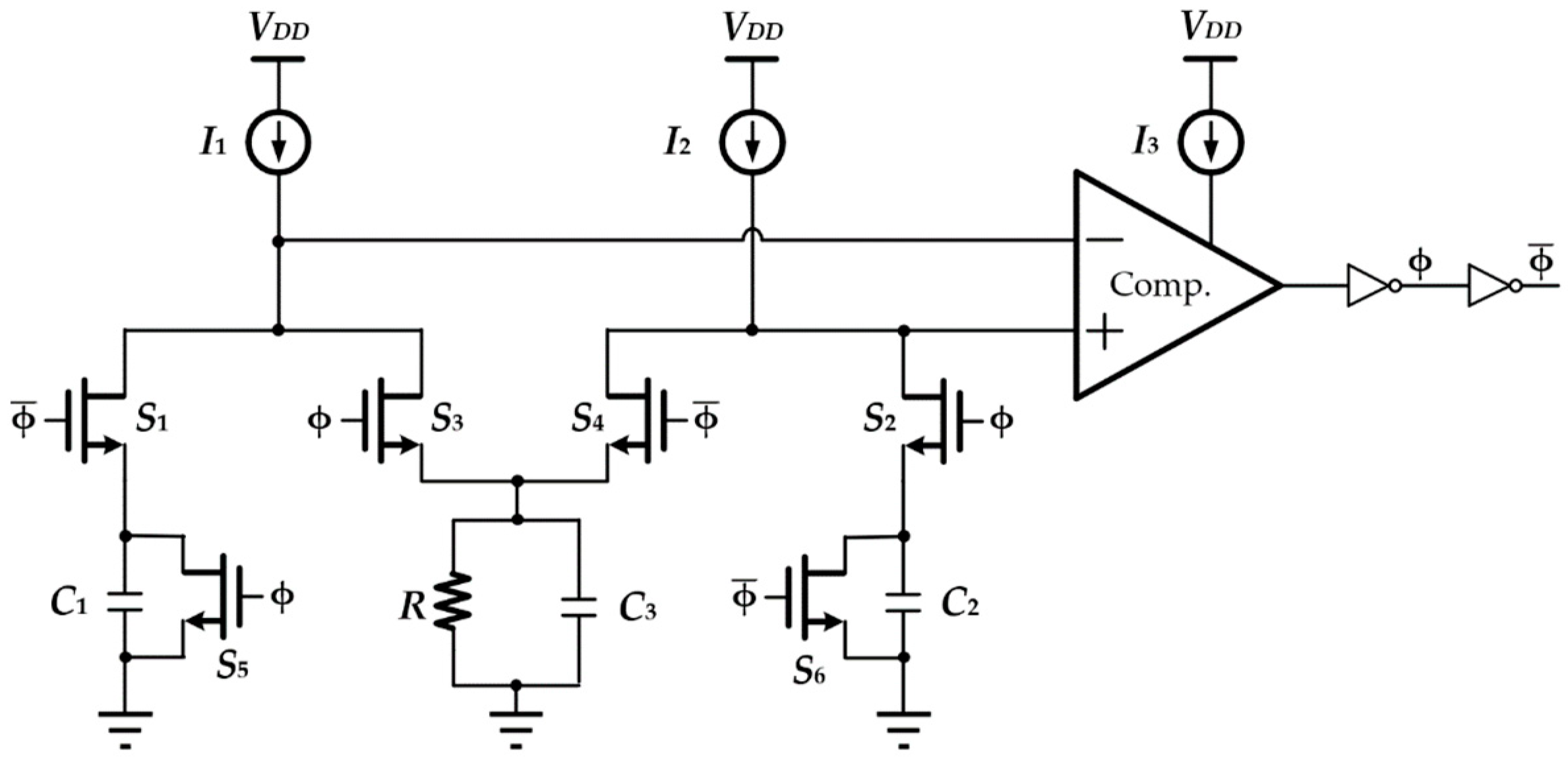

3.1. Topology of the Relaxation Oscillator

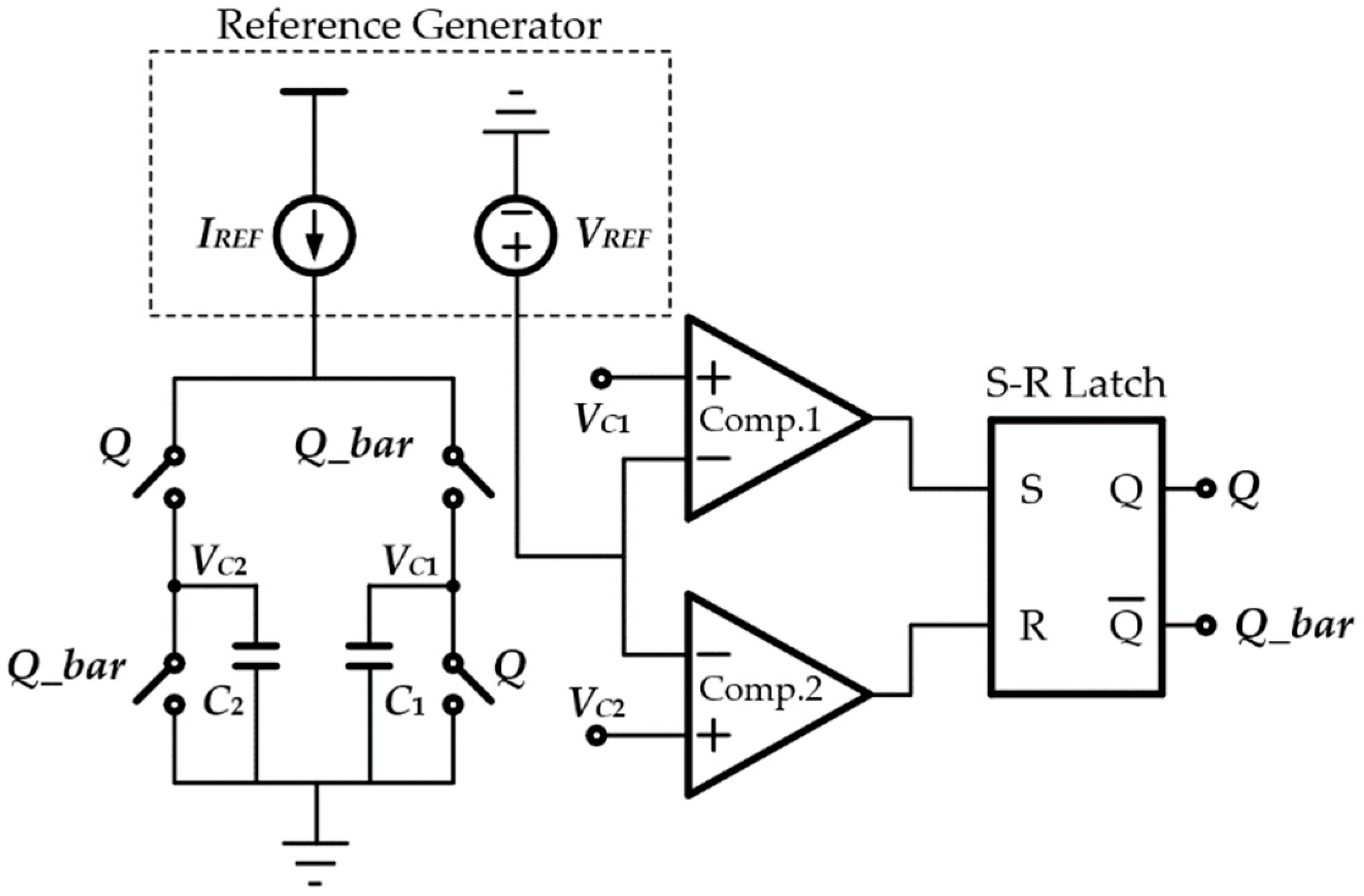

3.2. Reference Generator

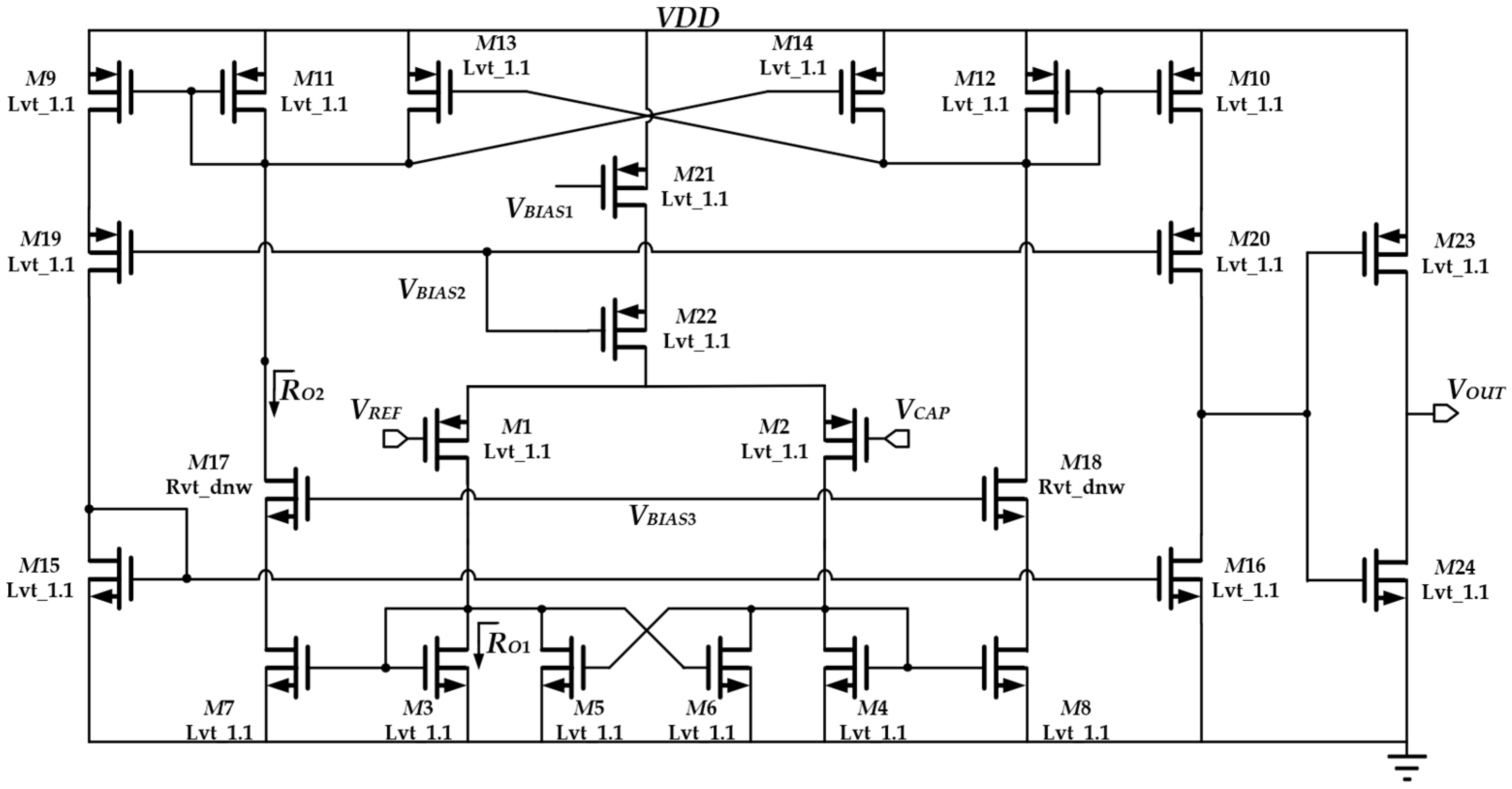

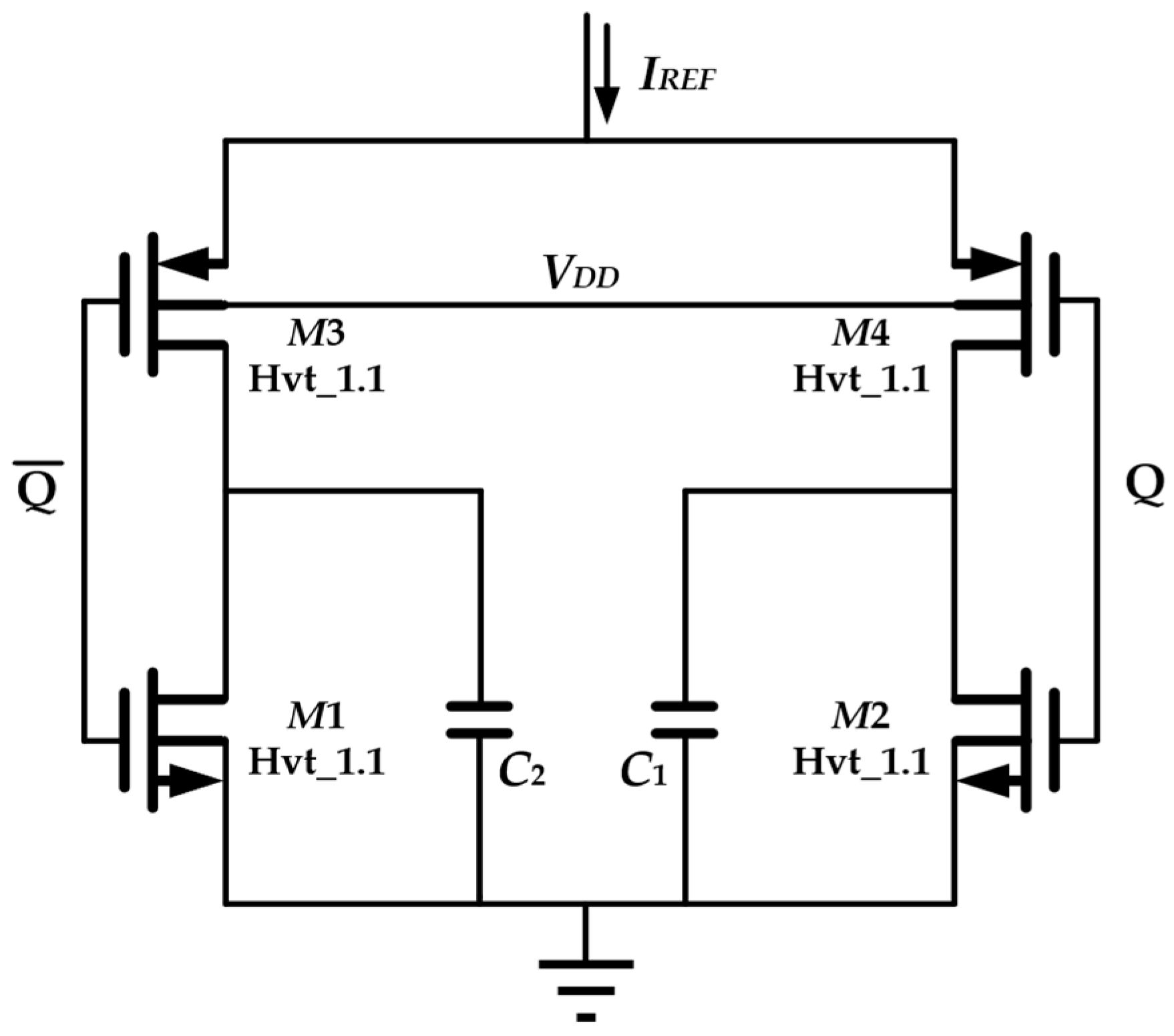

3.3. Comparator

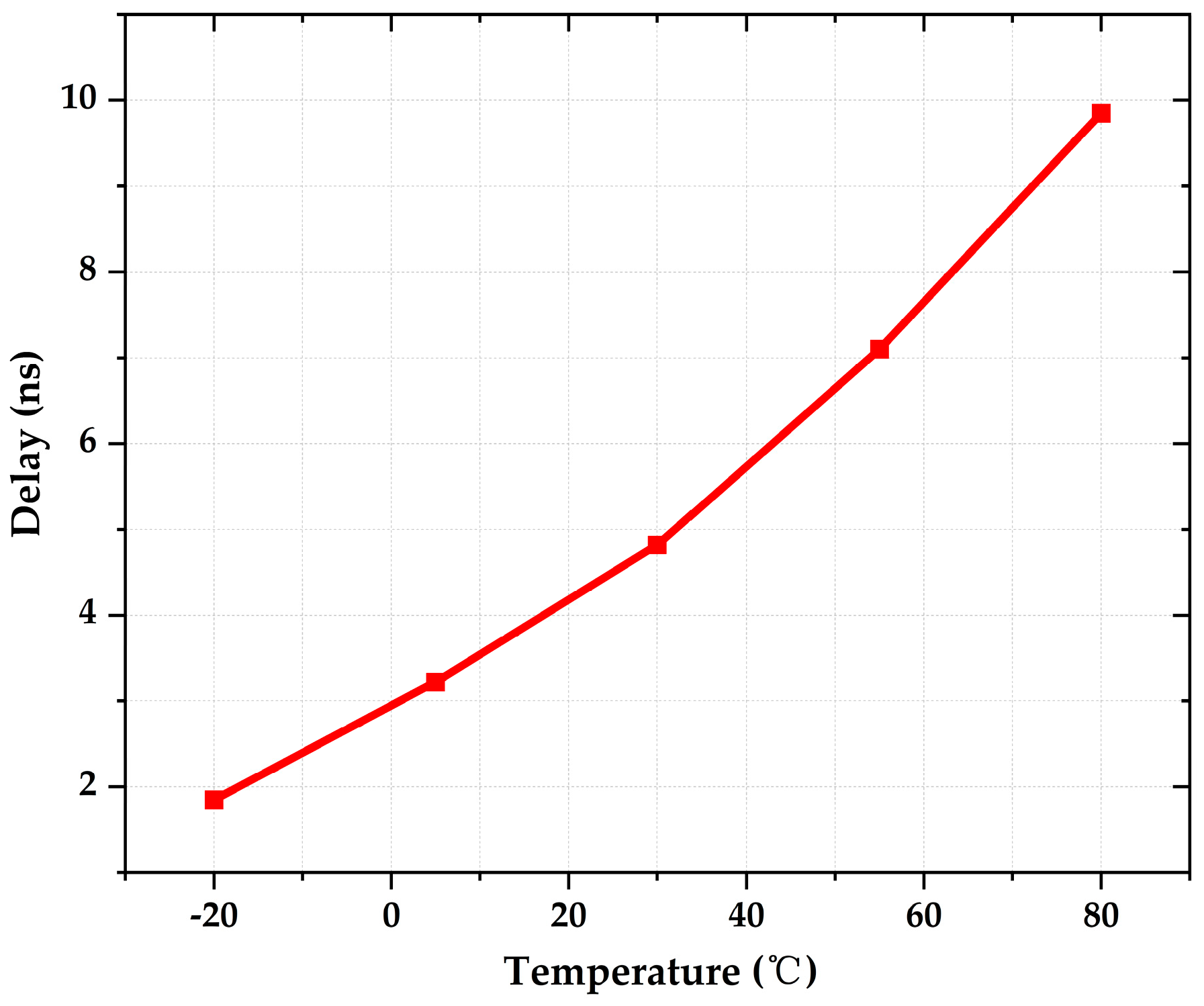

3.4. Leakage Current in Switches and Delay Compensation

4. Results and Discussions

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Tsubaki, K.; Hirose, T.; Kuroki, N.; Numa, M. A 32.55-kHz, 472-nW, 120ppm/°C, fully on-chip, variation tolerant CMOS relaxation oscillator for a real-time clock application. In Proceedings of the 2013 Proceedings of the ESSCIRC, Bucharest, Romania, 16–20 September 2013; pp. 315–318. [Google Scholar]

- Wang, J.; Goh, W.L. A 13.5-MHz relaxation oscillator with ±0.5% temperature stability for RFID application. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems, Montreal, QC, Canada, 22–25 May 2016; pp. 2431–2434. [Google Scholar]

- Cannillo, F.; Toumazou, C.; Lande, T.S. Nanopower subthreshold MCML in submicrometer CMOS technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 1598–1611. [Google Scholar] [CrossRef]

- Zhang, S.; Li, A.; Han, Y.; Jie, L.; Han, X.; Cheung, R.C. Temperature compensation technique for ring oscillators with tail current. Electron. Lett. 2016, 52, 1108–1110. [Google Scholar] [CrossRef]

- Zhang, X.; Apsel, A.B. A low-power, process-and-temperature-compensated ring oscillator with addition-based current source. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 58, 868–878. [Google Scholar] [CrossRef]

- Ballo, A.; Pennisi, S.; Scotti, G.; Venezia, C. A 0.5 V Sub-Threshold CMOS Current-Controlled Ring Oscillator for IoT and Implantable Devices. J. Low Power Electron. 2022, 12, 16. [Google Scholar] [CrossRef]

- Cimbili, B.; Wang, D.; Zhang, R.C.; Tan, X.L.; Chan, P.K. A PVT-tolerant relaxation oscillator in 65nm CMOS. In Proceedings of the 2016 IEEE Region 10 Conference, Singapore, 22–25 November 2016; pp. 2315–2318. [Google Scholar]

- Ma, L.; Koay, K.C.; Chan, P.K. A merged window comparator based relaxation oscillator with low temperature coefficient. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems, Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar]

- Medeiros, W.T.; Klimach, H.; Bampi, S. A 40 nW 32.7 kHz CMOS Relaxation Oscillator with Comparator Offset Cancellation for Ultra-Low Power applications. In Proceedings of the 2020 IEEE 11th Latin American Symposium on Circuits & Systems, San Jose, Costa Rica, 25–28 February 2020; pp. 1–4. [Google Scholar]

- Hsiao, K.J. A 32.4 ppm/°C 3.2-1.6 V self-chopped relaxation oscillator with adaptive supply generation. In Proceedings of the 2012 Symposium on VLSI Circuits, Honolulu, HI, USA, 13–15 June 2012; pp. 14–15. [Google Scholar]

- Xu, L.; Onabajo, M. A low-power temperature-compensated relaxation oscillator for built-in test signal generation. In Proceedings of the 2015 IEEE 58th International Midwest Symposium on Circuits and Systems, Fort Collins, CO, USA, 2–5 August 2015; pp. 1–4. [Google Scholar]

- Chan, P.K.; Zhang, H.L. A switched-capacitor interface circuit for integrated sensor applications. In Proceedings of the 2001 IEEE International Symposium on Circuits and Systems, Sydney, NSW, Australia, 6–9 May 2001; pp. 372–375. [Google Scholar]

- Ye, S.Q.; Chan, P.K. A low-power switched-capacitor humidity sensor interface. In Proceedings of the 2010 IEEE Asia Pacific Conference on Circuits and Systems, Kuala Lumpur, Malaysia, 6–9 December 2010; pp. 1039–1042. [Google Scholar]

- Ong, G.T.; Chan, P.K. A Power-Aware Chopper-Stabilized Instrumentation Amplifier for Resistive Wheatstone Bridge Sensors. IEEE Trans. Instrum. Meas. 2014, 63, 2253–2263. [Google Scholar] [CrossRef]

- Chan, P.K.; Ng, K.A.; Zhang, X.L. A CMOS chopper-stabilized differential difference amplifier for biomedical integrated circuits. In Proceedings of the 2004 47th Midwest Symposium on Circuits and Systems, Hiroshima, Japan, 25–28 July 2004; pp. 3–33. [Google Scholar]

- Savanth, A.; Weddell, A.S.; Myers, J.; Flynn, D.; Al-Hashimi, B.M. A Sub-nW/kHz Relaxation Oscillator with Ratioed Reference and Sub-Clock Power Gated Comparator. IEEE J. Solid-State Circuits 2019, 54, 3097–3106. [Google Scholar] [CrossRef]

- Tsai, Y.-K.; Lu, L.-H. A 51.3-MHz 21.8-ppm/°C CMOS Relaxation Oscillator with Temperature Compensation. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 490–494. [Google Scholar] [CrossRef]

- Ji, Y.; Liao, J.; Arjmandpour, S.; Novello, A.; Sim, J.-Y.; Jang, T. A Second-Order Temperature-Compensated On-Chip R-RC Oscillator Achieving 7.93 ppm/°C and 3.3pJ/Hz in −40 °C to 125 °C Temperature Range. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–26 February 2022; pp. 1–3. [Google Scholar]

- Asano, H.; Hirose, T.; Ozaki, T.; Kuroki, N.; Numa, M. An area-efficient, 0.022-mm2, fully integrated resistor-less relaxation oscillator for ultra-low power real-time clock applications. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems, Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar]

- Paidimarri, A.; Griffith, D.; Wang, A.; Chandrakasan, A.P.; Burra, G. A 120 nW 18.5 kHz RC oscillator with comparator offset cancellation for ±0.25% temperature stability. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 184–185. [Google Scholar]

- Lee, J.; Cho, S. A 210 nW 29.3 ppm/°C 0.7 V voltage reference with a temperature range of −50 to 130 °C in 0.13 µm CMOS. In Proceedings of the 2011 Symposium on VLSI Circuits-Digest of Technical Papers, Kyoto, Japan, 15–17 June 2011; pp. 278–279. [Google Scholar]

- Allen, P.E.; Holberg, D.R. CMOS Analog Circuit Design; Oxford University Press: Oxford, UK, 2002. [Google Scholar]

- Denier, U. Analysis and design of an ultralow-power CMOS relaxation oscillator. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 1973–1982. [Google Scholar] [CrossRef]

- Flynn, M.P.; Lidholm, S.U. A 1.2-mum CMOS current-controlled oscillator. IEEE J. Solid-State Circuits 1992, 27, 982–987. [Google Scholar] [CrossRef]

- Seok, M.; Kim, G.; Blaauw, D.; Sylvester, D. A portable 2-transistor picowatt temperature-compensated voltage reference operating at 0.5 V. IEEE J. Solid-State Circuits 2012, 47, 2534–2545. [Google Scholar] [CrossRef]

- Gregoire, B.R.; Moon, U.K. Process-independent resistor temperature-coefficients using series/parallel and parallel/series composite resistors. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 2826–2829. [Google Scholar]

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw-Hill Education: New York, NY, USA, 2005. [Google Scholar]

- Chiang, Y.-H.; Liu, S.-I. Nanopower CMOS Relaxation Oscillators With Sub-100 ppm/°C Temperature Coefficient. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 661–665. [Google Scholar]

- De Vita, G.; Marraccini, F.; Iannaccone, G. Low-Voltage Low-Power CMOS Oscillator with Low Temperature and Process Sensitivity. In Proceedings of the 2007 IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007; pp. 2152–2155. [Google Scholar]

| Component | Size | Component | Size |

|---|---|---|---|

| M1,3 | 10/15 (µm/µm) | M10,12 | 28/12 (µm/µm) |

| M2 | 2.04/1 (µm/µm) | M11,13 | 7/2 (µm/µm) |

| M4 | 2.05/1 (µm/µm) | R1 | 433.3 kΩ |

| M5,7 | 5/4 (µm/µm) | R2 | 1.366 MΩ |

| M6,8 | 6/2 (µm/µm) | C1 | 1.5 pF |

| M9 | 1.5/1 (µm/µm) | C2 | 4 pF |

| Component | Size | Component | Size |

|---|---|---|---|

| M1,2 | 1/0.6 (µm/µm) | M15,16 | 0.5/0.6 (µm/µm) |

| M3,4 | 1/1.2 (µm/µm) | M17,18 | 0.3/0.3 (µm/µm) |

| M5,6 | 0.8/1.2 (µm/µm) | M19,20 | 0.3/0.3 (µm/µm) |

| M7,8 | 0.5/0.6 (µm/µm) | M21 | 20/12 (µm/µm) |

| M9,10 | 0.5/0.6 (µm/µm) | M22 | 5/2 (µm/µm) |

| M11,12 | 1/1.2 (µm/µm) | M23 | 0.36/0.12 (µm/µm) |

| M13,14 | 1.2/1.2 (µm/µm) | M24 | 0.12/0.12 (µm/µm) |

| Component | Size | Component | Size |

|---|---|---|---|

| M1,2 | 0.12/0.04 (µm/µm) | C1,2 | 1.49 pF |

| M3,4 | 0.36/0.04 (µm/µm) |

| Parameter | [7] 2016 | [8] 2017 | [9] 2020 | [10] 2012 | [19] 2017 | [20] 2013 | This Work |

|---|---|---|---|---|---|---|---|

| Technology | 65 nm | 65 nm | 40 nm | 60 nm | 65 nm | 65 nm | 40 nm |

| Frequency (kHz) | 64.4 | 64.2 | 32.7 | 32.7 | 32.5 | 18.5 | 64.6 |

| Supply Voltage (V) | 1.2 | 1.2 | 0.6 | 1.6 | 1.2 | 1 | 1.1 |

| Current_TT (μA) | 3.6 | 7.47 | 0.067 | 2.8 | 0.225 | 0.12 | 0.55 |

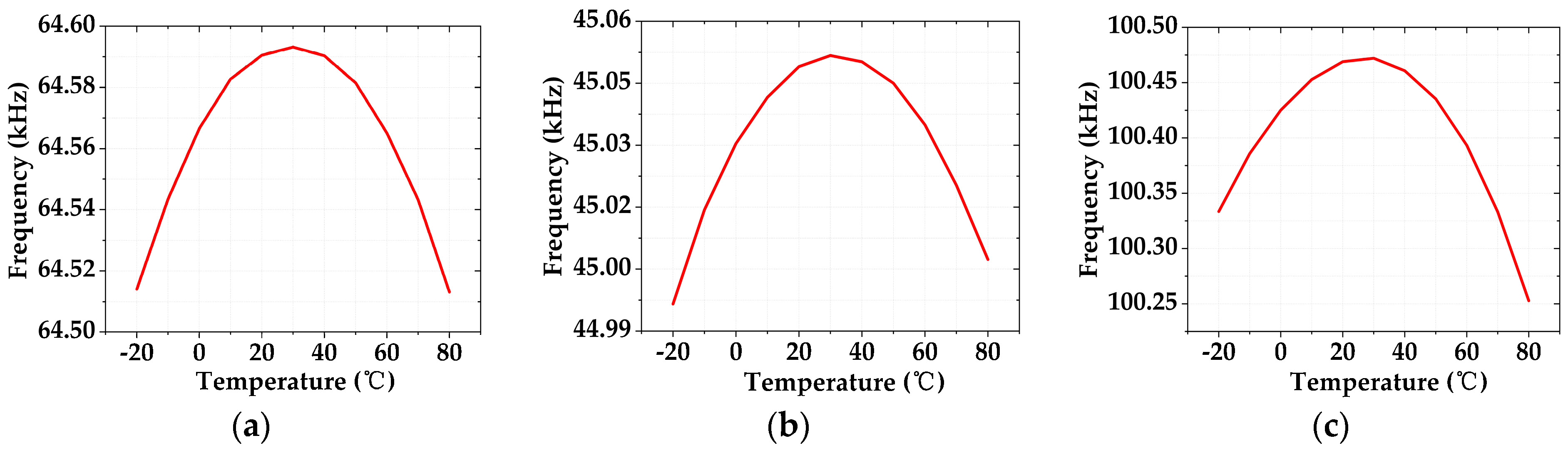

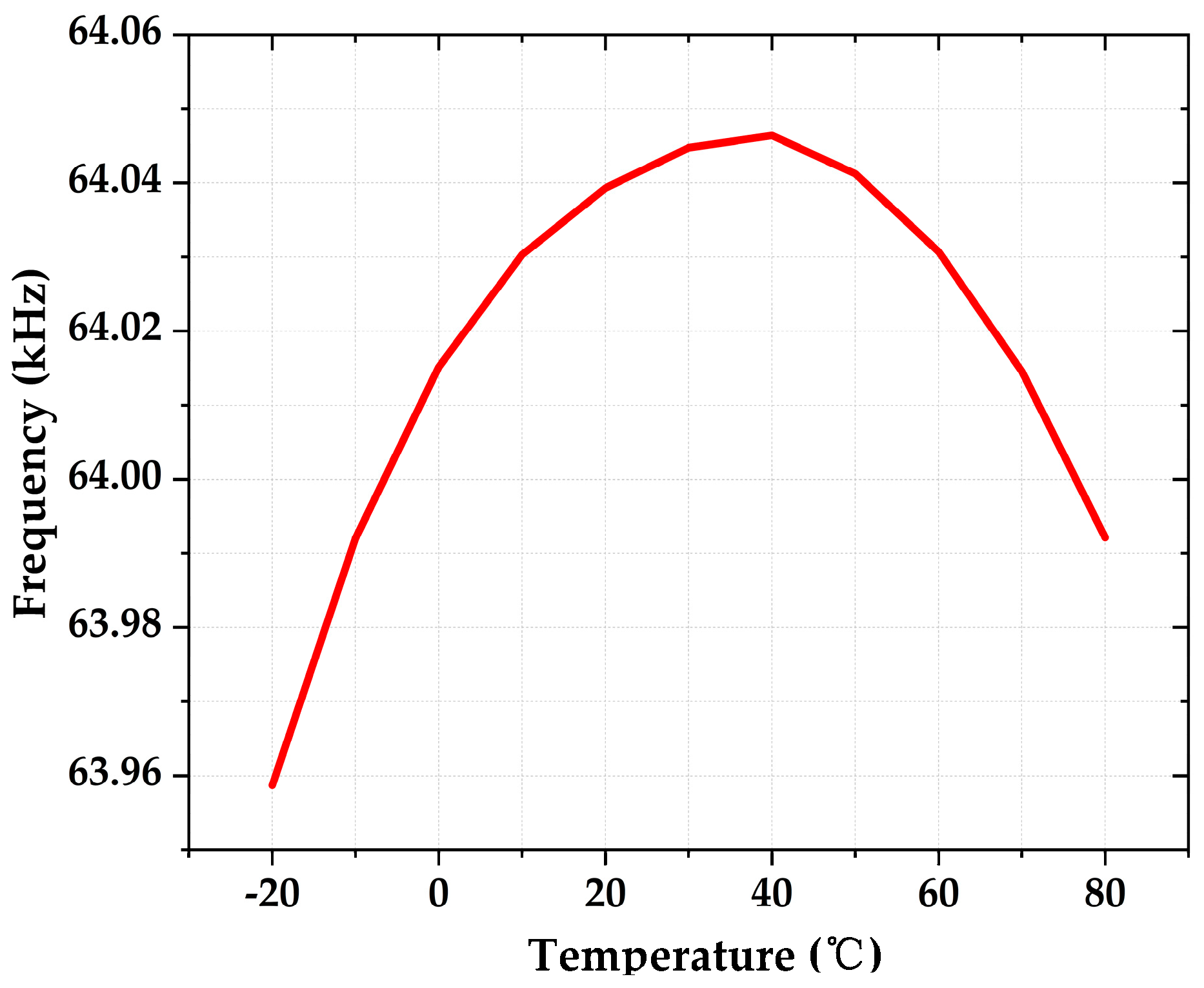

| T.C._TT (ppm/°C) | 144 | 14.7 | 21.7 | 32.4 | 138 | 22 | 12.4 |

| T.C._MC (ppm/°C) | NA | NA | 35.5 | NA | NA | NA | 25 |

| Temp. Range (°C) | −20–100 | −20–100 | −40–125 | −20–100 | −40–80 | 0–90 | −20–80 |

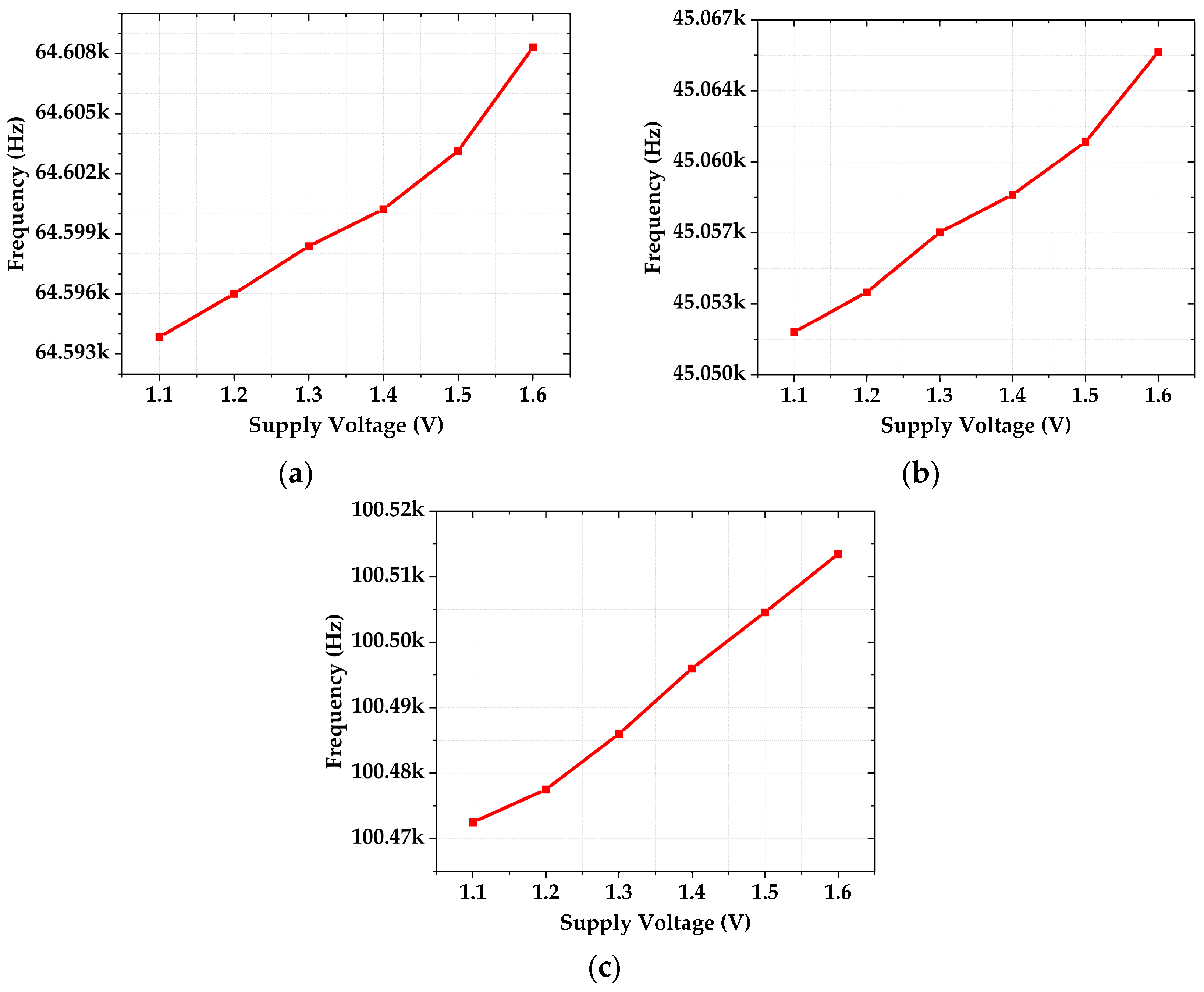

| Line Sens. (%/V) | 0.91 | 0.188 | 0.5 | 0.125 | 1.39 | 1 | 0.045 |

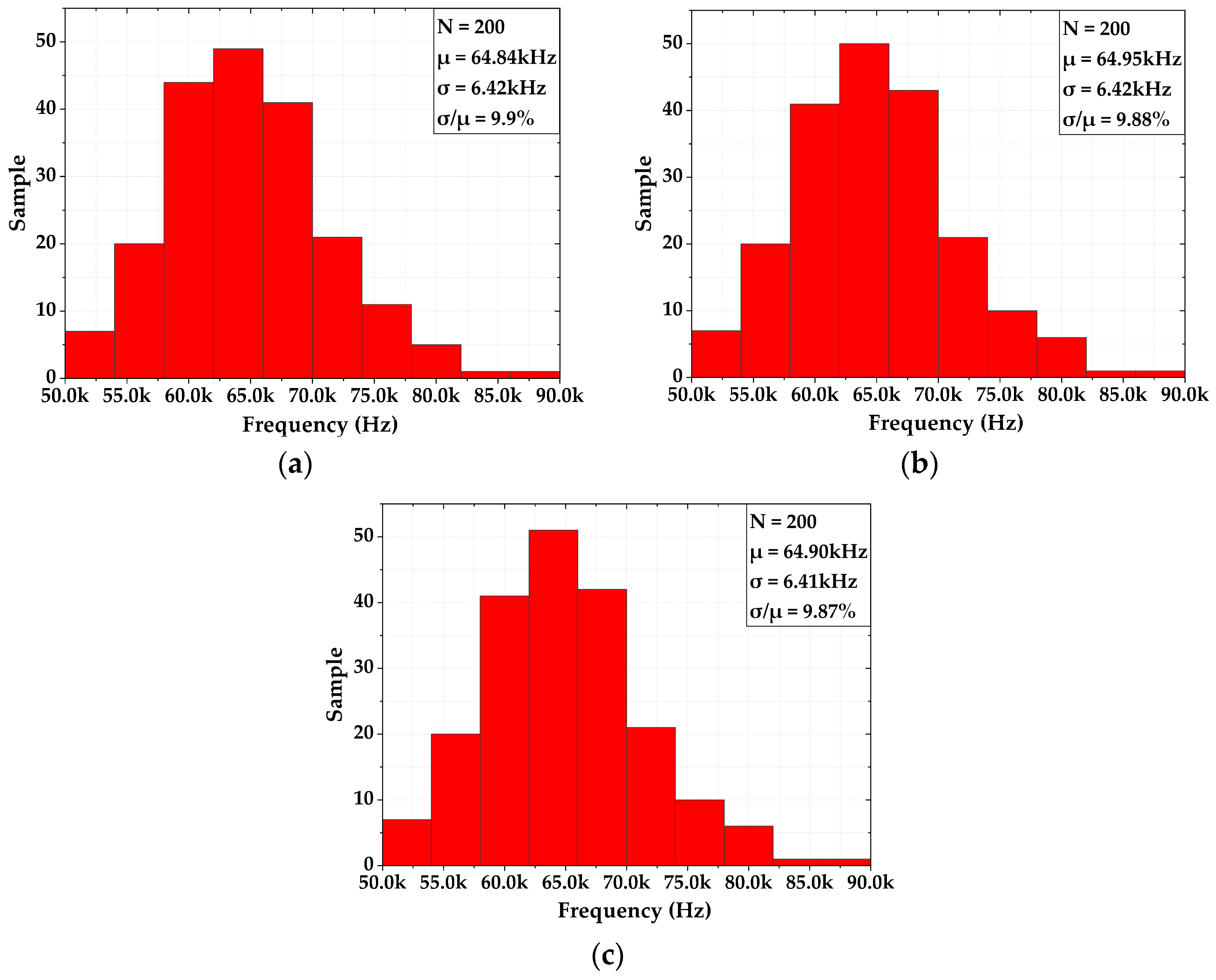

| Process Sen. (σ/µ)% without trimming | 3.66 | NA | 11.73 | NA | 10.4 | NA | 9.86 |

| FoM (%) | 1.549 | 0.169 | 0.247 | 0.344 | 1.54 | 0.32 | 0.129 |

| Result | Simulated | Simulated | Simulated | Measured | Simulated | Measured | Simulated |

| Parameter | [1] 2013 | [23] 2010 | [28] 2014 | [29] 2007 | This Work |

|---|---|---|---|---|---|

| Technology | 180 nm | 350 nm | 180 nm | 350 nm | 40 nm |

| Frequency (kHz) | 32.55 | 3.3 | 28 | 80 | 64.6 |

| Supply Voltage (V) | 1 | 1 | 1.2 | 1 | 1.1 |

| Current_TT (μA) | 0.47 | 0.066 | 0.033 | 1.06 | 0.55 |

| T.C._TT (ppm/°C) | 120 | 260 | 95.5 | 842 | 12.4 |

| T.C._MC (ppm/°C) | NA | NA | NA | NA | 25 |

| Temp. Range (°C) | −40–100 | −20–80 | −20–80 | 0–80 | −20–80 |

| Line Sens. (%/V) | 1.1 | 3.5 | 3 | 2.5 | 0.045 |

| Process Sen. (σ/µ)% without trimming | 1.39 | NA | NA | 3.95 | 9.86 |

| FoM (%) | 1.31 | 2.95 | 1.255 | 8.67 | 0.129 |

| Result | Measured | Measured | Measured | Simulated | Simulated |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liao, Y.; Chan, P.K. A 1.1 V 25 ppm/°C Relaxation Oscillator with 0.045%/V Line Sensitivity for Low Power Applications. J. Low Power Electron. Appl. 2023, 13, 15. https://doi.org/10.3390/jlpea13010015

Liao Y, Chan PK. A 1.1 V 25 ppm/°C Relaxation Oscillator with 0.045%/V Line Sensitivity for Low Power Applications. Journal of Low Power Electronics and Applications. 2023; 13(1):15. https://doi.org/10.3390/jlpea13010015

Chicago/Turabian StyleLiao, Yizhuo, and Pak Kwong Chan. 2023. "A 1.1 V 25 ppm/°C Relaxation Oscillator with 0.045%/V Line Sensitivity for Low Power Applications" Journal of Low Power Electronics and Applications 13, no. 1: 15. https://doi.org/10.3390/jlpea13010015

APA StyleLiao, Y., & Chan, P. K. (2023). A 1.1 V 25 ppm/°C Relaxation Oscillator with 0.045%/V Line Sensitivity for Low Power Applications. Journal of Low Power Electronics and Applications, 13(1), 15. https://doi.org/10.3390/jlpea13010015