1. Introduction

The electrical bioimpedance technique allows for characterizing indirectly the properties of a biological media in a noninvasive way [

1]. An AC excitation signal is applied to the impedance under test,

, and the corresponding response is acquired by means of an instrumentation amplifier [

2], conditioned and processed. This technique is being widely used nowadays to assist in the diagnosis of different diseases extended among the population as well as for monitoring physiological variables [

3,

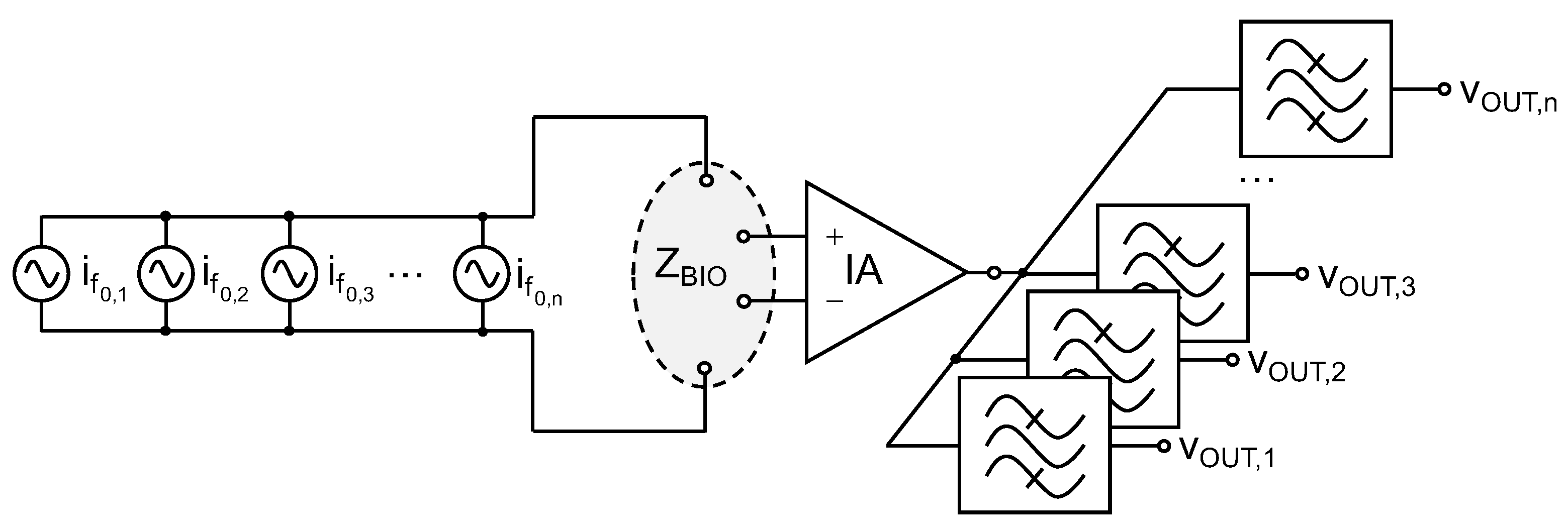

4]. Frequently, the response of the sample is required to be repeated at different frequencies in order to obtain a more complete information, which is known as bioimpedance spectroscopy. The typical frequency range, known as dispersion range, varies from several hundreds of Hz to a few MHz. The frequency analysis can be carried out sequentially, by modifying the frequency of the excitation signal. Nevertheless, when the bioimpedance of the media varies rapidly, a multi-frequency analysis is required in order to obtain all the responses at the same time. In this case, as illustrated in

Figure 1, different AC excitation signals are generated and simultaneously applied to the impedance, being subsequently separated with the help of bandpass filter (BPF) sections, being the

-

C a flexible and suitable approach for monolithic integration [

5,

6,

7,

8,

9,

10,

11,

12,

13,

14,

15]. The resulting solution is susceptible of being incorporated in an Internet of Things (IoT) platform [

16]. Nevertheless, different specifications must be met for this purpose, which can be especially stringent in terms of total power consumption when the overall application is intended to be incorporated into a wearable device.

The bulk-driven technique is well-suited for low-voltage CMOS analog design, as it allows for operation with very low supply voltages and overcomes the non-zero threshold voltage constraint [

10,

17,

18,

19,

20,

21,

22,

23,

24,

25]. Indeed, in a bulk-driven transistor, the DC voltage required to switch the device on and the signal to be processed are decoupled and applied, respectively, to the gate and bulk terminal, which allows for providing and extending the input voltage range with respect to the conventional gate-driven device. Nevertheless, one of the main drawbacks of such technique is the reduction of the effective transconductance, due to the lower value of the bulk transconductance,

, as compared to the gate transconductance,

. As a consequence, an increase of input-referenced magnitudes, such as the offset voltage or the noise, takes place. Different techniques have been proposed to electronically enhance the effective transconductance of a bulk-driven transistor, consequently increasing area and power consumption [

26,

27].

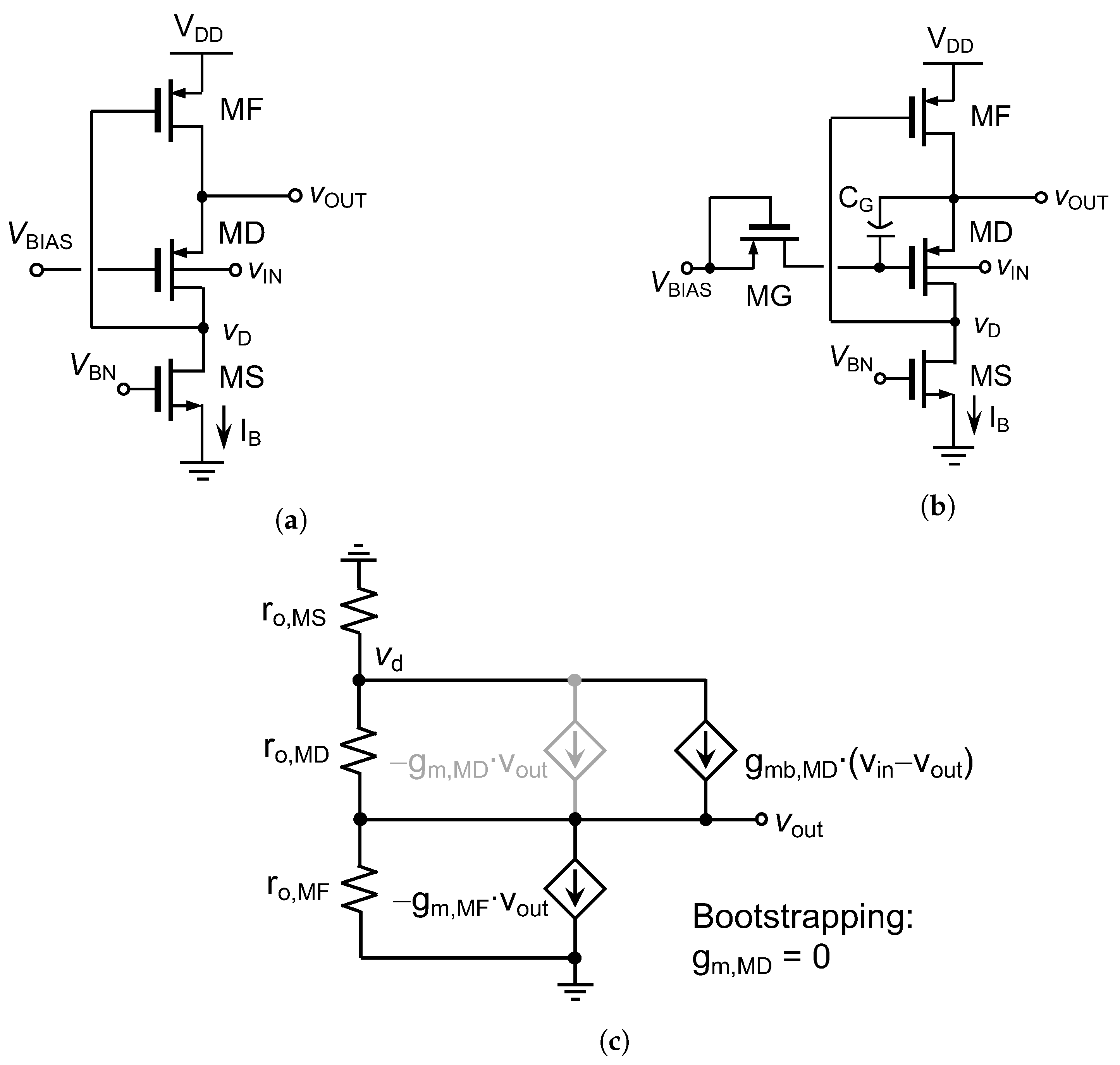

In this contribution, the application of a bootstrapping effect to a bulk-driven MOS transistor to increase its intrinsic voltage gain is proposed. The technique has been used to design a low-voltage voltage buffer, in which the noise contribution is reduced and the linearity is increased. The voltage buffer has been incorporated in the implementation of a linearized transconductor, which, in turn, is the basic building block of a second-order

-

C BPF aimed to signal separation in a multi-frequency bioimpedance measurement system. All the circuits have been designed in 180 nm CMOS technology to operate with a 0.6-V single supply. The rest of the manuscript has been organized as follows: In

Section 2, the voltage buffer is described and analyzed, whereas simulated results are used to confirm its principle of operation. The design of the linearized transconductor is detailed in

Section 3 and the implementation of the filter is presented in

Section 4. Simulated results are provided in

Section 5 and conclusions are drawn in

Section 6.

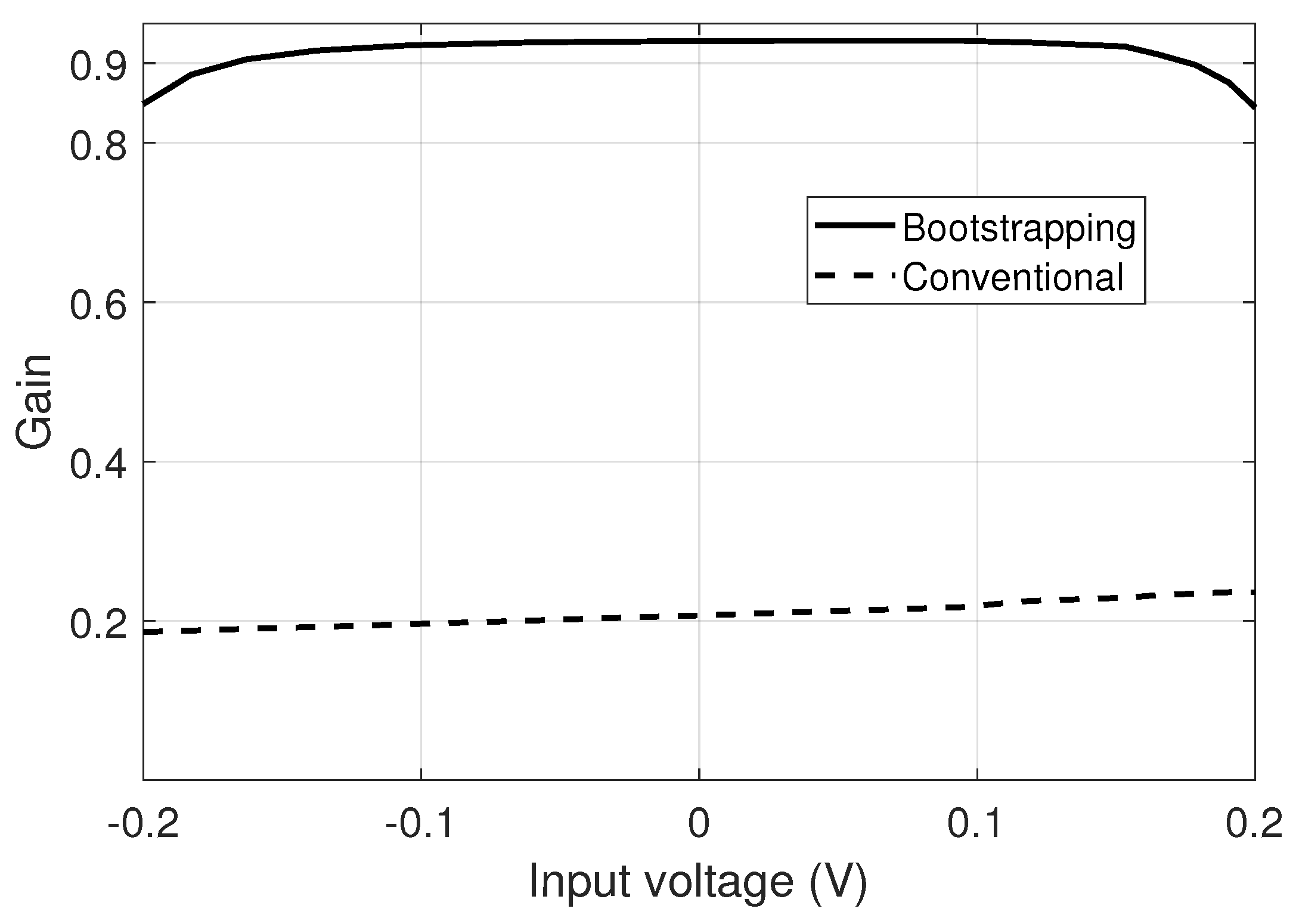

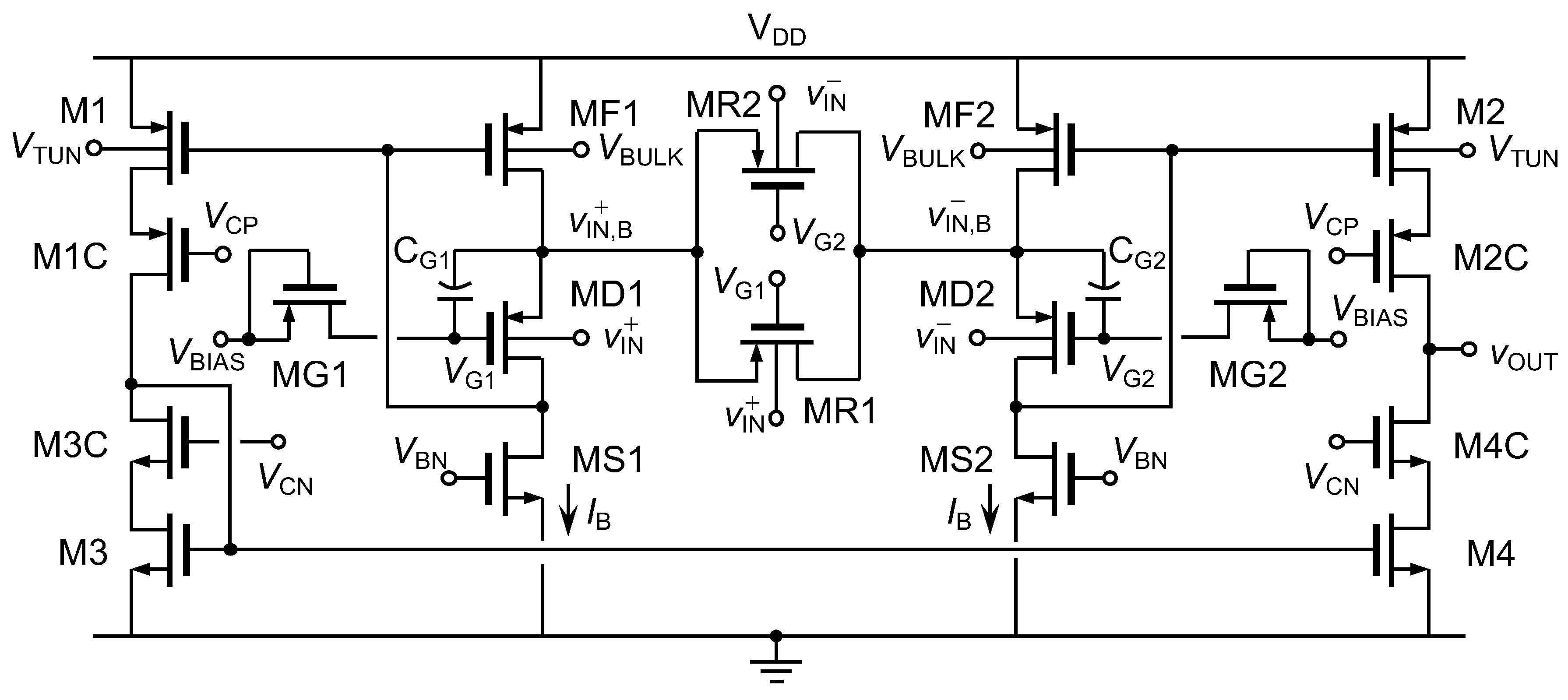

3. Proposed Linearized Transconductor

The circuit schematic of the proposed transconductor, consisting of a linearization resistor and two voltage followers, is illustrated in

Figure 7. The input signals,

and

, are applied to the bulk terminal of the driver transistors MD1 and MD2, producing a buffered replica of these voltages,

and

, at their source terminal. The bootstrapping action applied to the bulk-driven transistors leads to a gain close to unity for the voltage followers, as detailed in the previous section. The corresponding DM signal,

, is applied to a pseudo-resistor, implemented by transistors MR1 and MR2, where voltage-to-current (

V-to-

I) conversion takes place.

Assuming that the parallel connection of transistors MR1 and MR2 leads to a resistor with an approximately constant value

for small values of their source-to-drain voltage, the effective transconductance of the

V-to-

I converter has been determined by means of a hand analysis, and can be expressed as:

where

,

, and

are the bulk transconductance, gate transconductance, and output conductance of transistor M

i, respectively, and

is the intrinsic gain of the bulk-driven follower. In the case of a conventional bulk-driven FVF,

, causing a noticeable signal attenuation that leads to a transconductance degeneration. The signal attenuation can result adequate in a low-voltage environment, as it reduces the signal swing at the intermediate nodes of the transconductor. Nevertheless, this decrease of the effective input transconductance leads to an increase of input-referred magnitudes, such as the noise or the offset voltage. Alternatively, when the proposed bootstrapped bulk-driven FVF is used, it happens that

and, hence, there is an enhancement of the transconductance of the cell.

The response of the transconductor is linearized by connecting the bulk terminals of the transistors in the active resistor, MR1 and MR2, to the input terminals of the transconductor,

and

, whereas the gate terminals are connected to the bootstrapping network in order to also benefit from this effect. This solution, first proposed in [

32] and adapted to operate with bulk-driven transistors in [

22], is modified here to also take advantage of the bootstrapping effect. Indeed, the common connection of the gate, source, and bulk terminals of transistors MD1-MR1 and MD2-MR2 in the core of the transconductor leads to equal

and

voltages for each pair of devices and, hence, to a linearized response that is also insensitive to variations in the input CM voltage [

22]. The general expression of the drain current of a MOS transistor operated in the subthreshold region, given by (

1), can be approximated by means of the Taylor series when the transistor operates in triode, i.e., when

is very small. In particular, the Taylor series can be truncated at the linear term, thus obtaining

Similarly, the expression of the threshold voltage can be linearized as [

23]

Considering the expressions in (

9) and (

10), the output conductance of a MOS transistor biased in the subthreshold region and operated in triode can be written as:

As transistors MR1 and MR2 in

Figure 7 are connected in parallel, the effective conductance of the composite structure,

, is the sum of the individual conductances of both devices. Assuming that the signal

applied at the bulk terminals of devices MR1 and MR2 has a CM DC component,

, and a purely DM signal contribution,

and

, respectively, the value of the linearization resistor can be approximated as:

The odd-power terms of the signal cancel out each other, whereas the even-power terms are summed. Taking into account only the linear term of

signal, the expression of the linearization resistor can be further approximated as

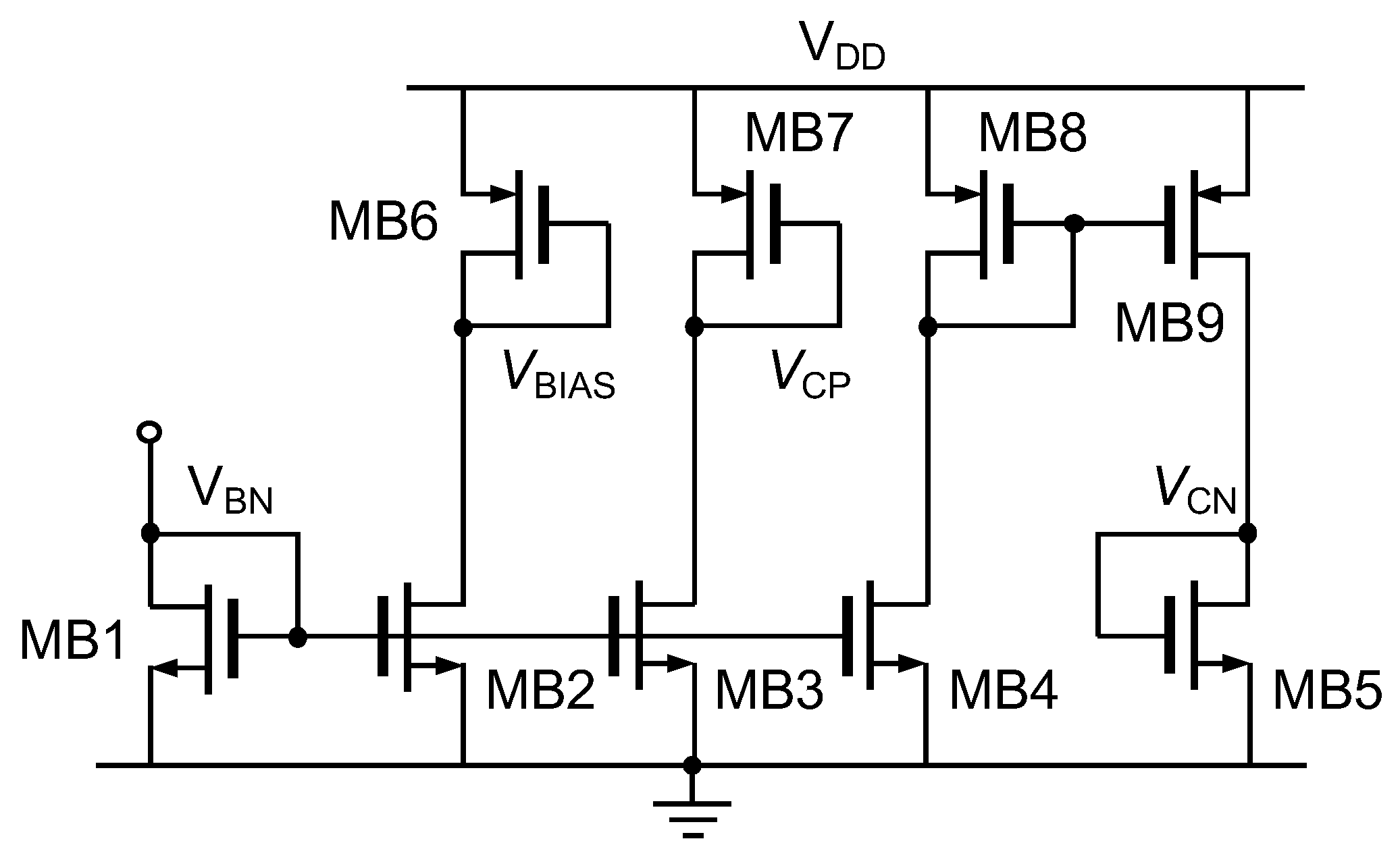

The circuit section used to bias the transconductor is shown in

Figure 8. In particular, voltages

and

are used to generate the different replicas of the biasing current

required in the

V-to-

I converter. Furthermore, voltages

and

allow for biasing NMOS and PMOS cascode devices. An ultra-low-voltage environment connecting the gate of NMOS and PMOS cascode transistors to

and ground, respectively, seems to be a straightforward biasing solution leading to a reduction of the total current consumption. Nevertheless, appropriate bias conditions would be only ensured in typical mean conditions and at the nominal value of the supply voltage and the temperature. The use of the simple and well-known structure in

Figure 8 allows for tracking PVT variations and translate them to the bias voltage of the cascode transistors. A similar situation arises in the biasing of the gates of the bulk-driven MOS transistors through the bootstrapping network, the reason why the DC signal

is also generated.

Conventionally, the transconductance of the

V-to-

I converter illustrated in

Figure 7 is tuned by modifying the value of the tail current of the FVF cells. As current

changes, the

of the driver transistors also does, modifying the effective value of

and, hence, of

. Here, a different tuning mechanism, based on controlling the gain of the PMOS current mirrors formed by transistors MF1-M1 and MF2-M2, is proposed. The bulk terminal of the input transistors of the current mirror, MF1 and MF2, is connected to a fixed DC voltage

, whereas a variable voltage

is applied to the bulk terminal of the output transistors, M1 and M2. When

, the effective threshold voltage of the output transistors is higher and the current flowing though the output branch is lower, thus having a current attenuation. Conversely, for

, the effective value of

of the output transistors of the current mirror becomes lower than that of the input transistors, obtaining a higher output current and, hence, a signal amplification. The voltage

finds its upper bound in the supply voltage

and, theoretically, can be decreased until the ground level is reached. Nevertheless, considering that the source and the bulk of these transistors form a

pn junction, deep forward biasing of this parasitic diode must be avoided. To this end, the exponential behavior of the current flowing through the bulk terminal of a PMOS transistor when the bulk voltage is changed has been considered in order to determine a practical lower bound for the tuning range of voltage

. In particular, in

Figure 9, the bulk current of transistors M1 and M2 in

Figure 7,

, is represented as a function of the tuning variable

. A current level equal to 1% of the biasing current, i.e., 0.01

, has been selected as a reasonable limit in order to avoid deep forward operation of the source-bulk

pn junction of transistors M1 and M2. As a result, a value of 200 mV for

is selected as the lower bound of the tuning variable.

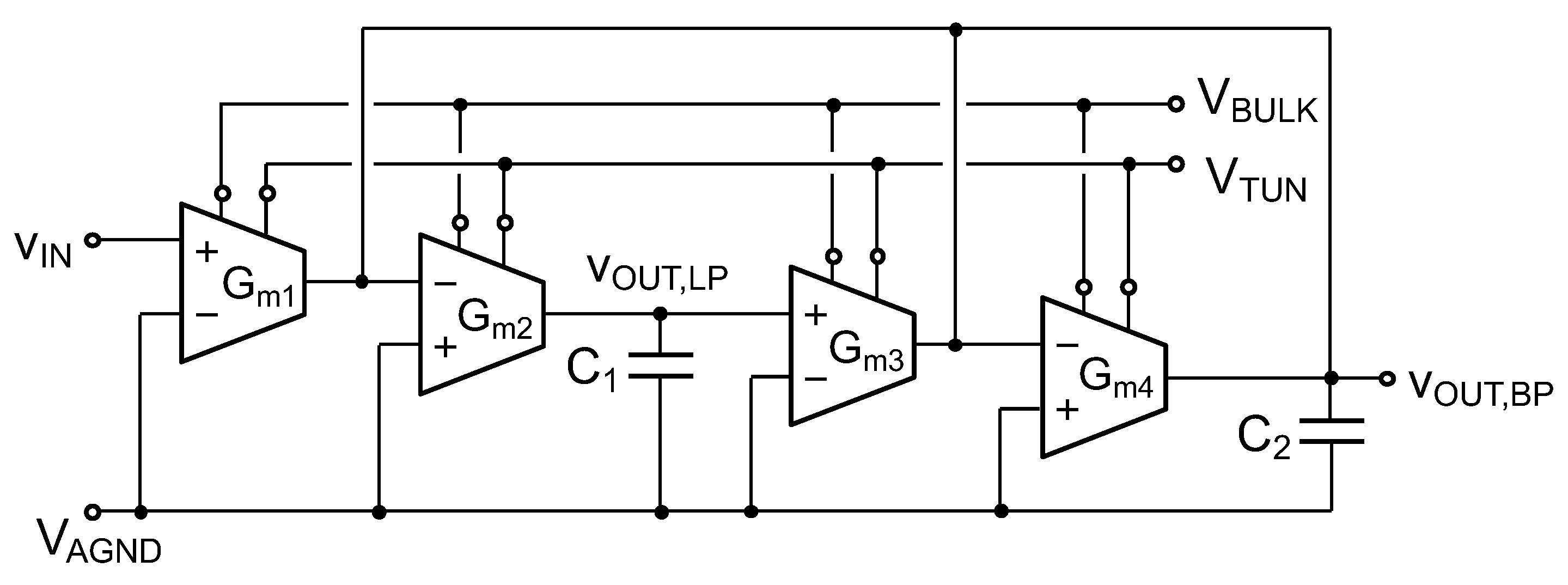

4. Second-Order -C Bandpass Filter

The second-order

-

C BPF illustrated in

Figure 10 has been implemented by using the linearized transconductor described in the previous section and depicted in

Figure 7, which is based in turn on the bootstrapped bulk-driven voltage buffer shown in

Figure 2b. The filter structure incorporates four transconductors in order to be able to set independently the center frequency,

, the gain at the center frequency,

, and the quality factor,

Q. In our application, only

is intended to be swept, whereas

and

Q will have fixed values. Nevertheless, the configuration selected allows for keeping constant a given quality factor while the center frequency is swept. In addition, there is an additional degree of freedom in the structure that allows for maximizing the dynamic range of the BPF. Indeed, the other node in the filter,

in

Figure 10, provides a lowpass response. The lowpass response presents an overdamping at the frequency of the poles that is a function of the quality factor selected for the BPF. As a consequence, a noticeable peak appears at that node at

, thus limiting the dynamic response of the overall biquad. This fact can be avoided with the structure illustrated in

Figure 10, as the value of

Q can be set through the ratios of the active (transconductance) or the passive (capacitor) elements, which allows for decreasing the overall gain of the lowpass response, thus decreasing the maximum signal amplitude achieved at

at the center frequency of the BPF.

The transfer function of the selected BPF can be written as:

where

, with

i = 1 to 4, represents the effective transconductance of the

i-th transconductor and

and

are integrated capacitors. The gain at the center frequency,

, the center frequency,

, and the quality factor,

Q, can be obtained from (

14) in a straightforward manner and expressed as:

The intended application of the BPF is the separation of signals with different frequencies in a multi-frequency bioimpedance measurement system. Thus, the selectivity of the filter must be relatively high, which requires a moderately high value of the quality factor. A hand-analysis of the response at node

of the filter reveals that an optimal choice in order not to limit the dynamic range of the BPF response is obtained when

. Thus, the following equality has been established for the transconductances

so that the factor

Q is equal to parameter

k. In addition, transconductors

and

have been sized to be equal,

, in order to have a gain at the center frequency equal to unity. Therefore, the expressions in (

15a–

15c) can be rewritten as:

The factor k has been achieved by properly sizing the pseudo-resistor in each transconductor, whereas the rest of the V-to-I converter has been kept equal. The response of the BPF, in particular the center frequency, can be programmed by fixing voltage to an appropriate value and by tuning the value of the control voltage around it. For , the transconductors achieve their minimum transconductance value, thus leading to the lowest value of . Conversely, when reaches the minimum reliable value, the is maximized and also is the value of the center frequency.

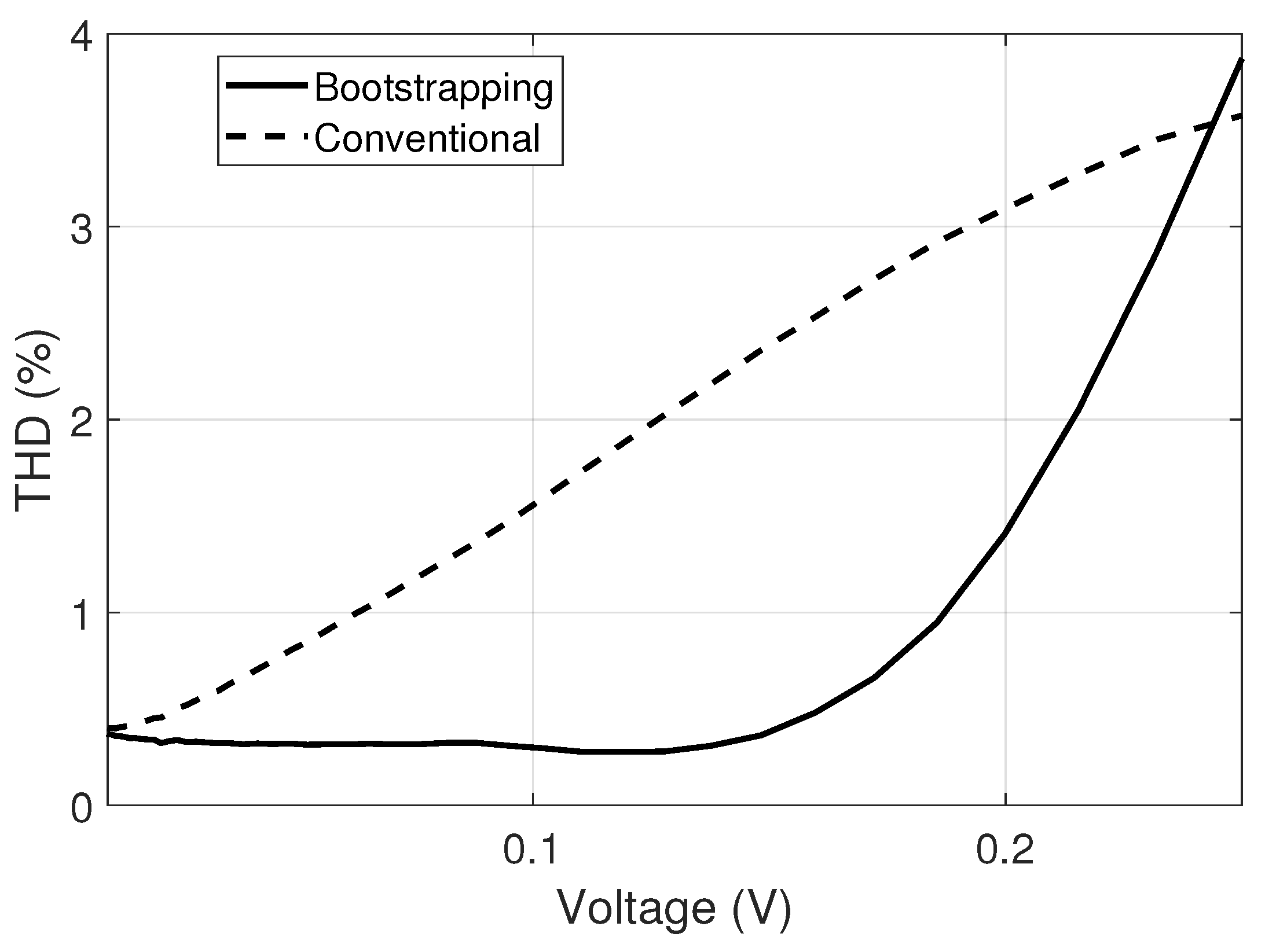

5. Simulated Results

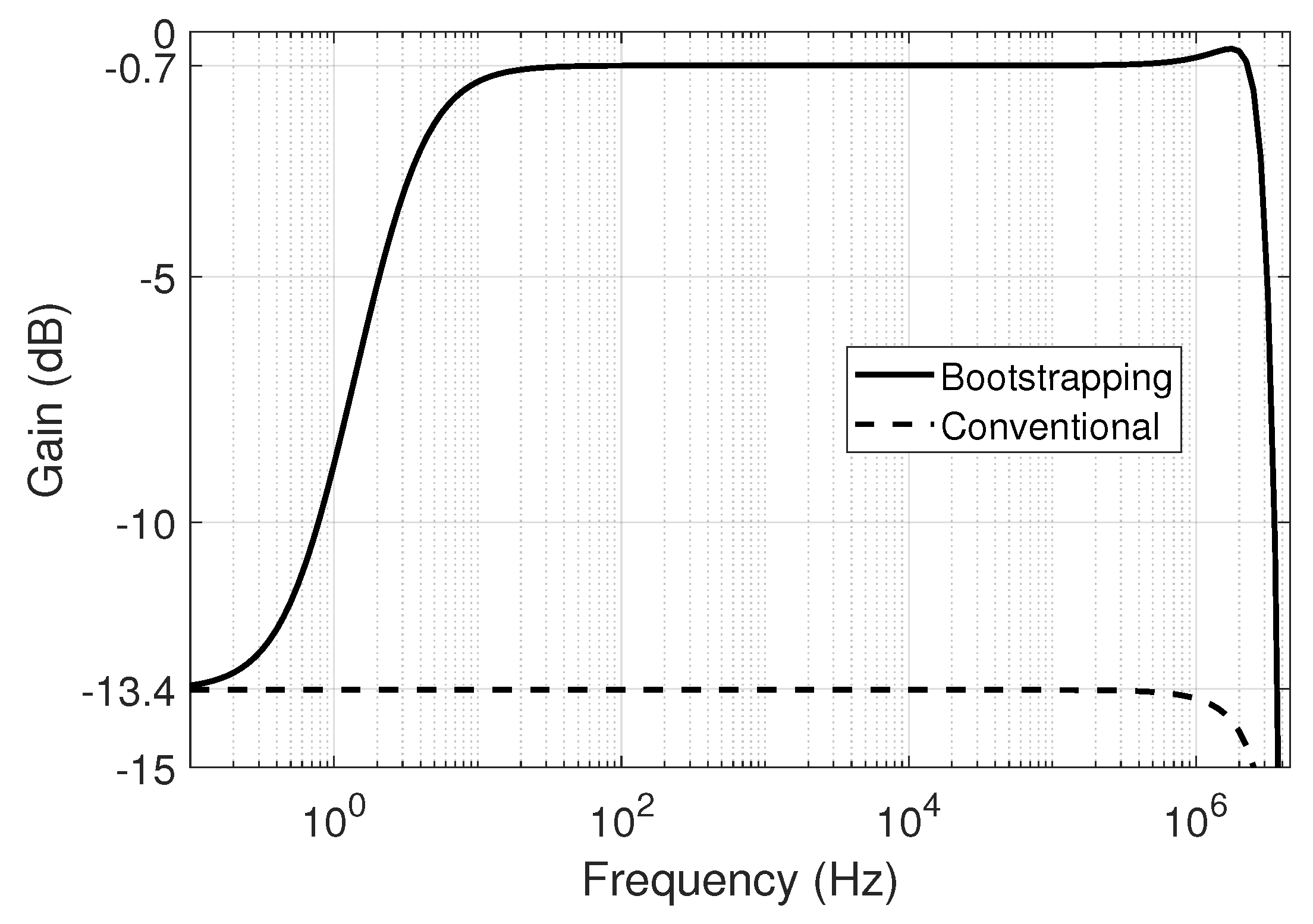

The bootstrapped bulk-driven voltage buffer in

Figure 2b, the linearized transconductor in

Figure 7, and the second-order

-

C BPF in

Figure 10 have been designed in 180 nm CMOS technology to operate with a single-supply of 0.6 V. The simulated results corresponding to the voltage buffer have already been provided in

Section 2 in order to demonstrate its principle of operation and, hence, the metrics corresponding to the other two blocks are described here.

The sizes of the main transistors involved in the implementation of the linearized transconductor are reported in

Table 2, whereas the value of capacitors

and

was set equal to 0.25 pF. The circuit was biased with a current

= 100 nA and the value of the voltages

and

was nominally set equal to 400 mV. In addition, a load capacitor of 1 pF was connected to the output terminal. The transconductor was first characterized at low frequency, as the bootstrapped structure is not DC coupled. The effective transconductance,

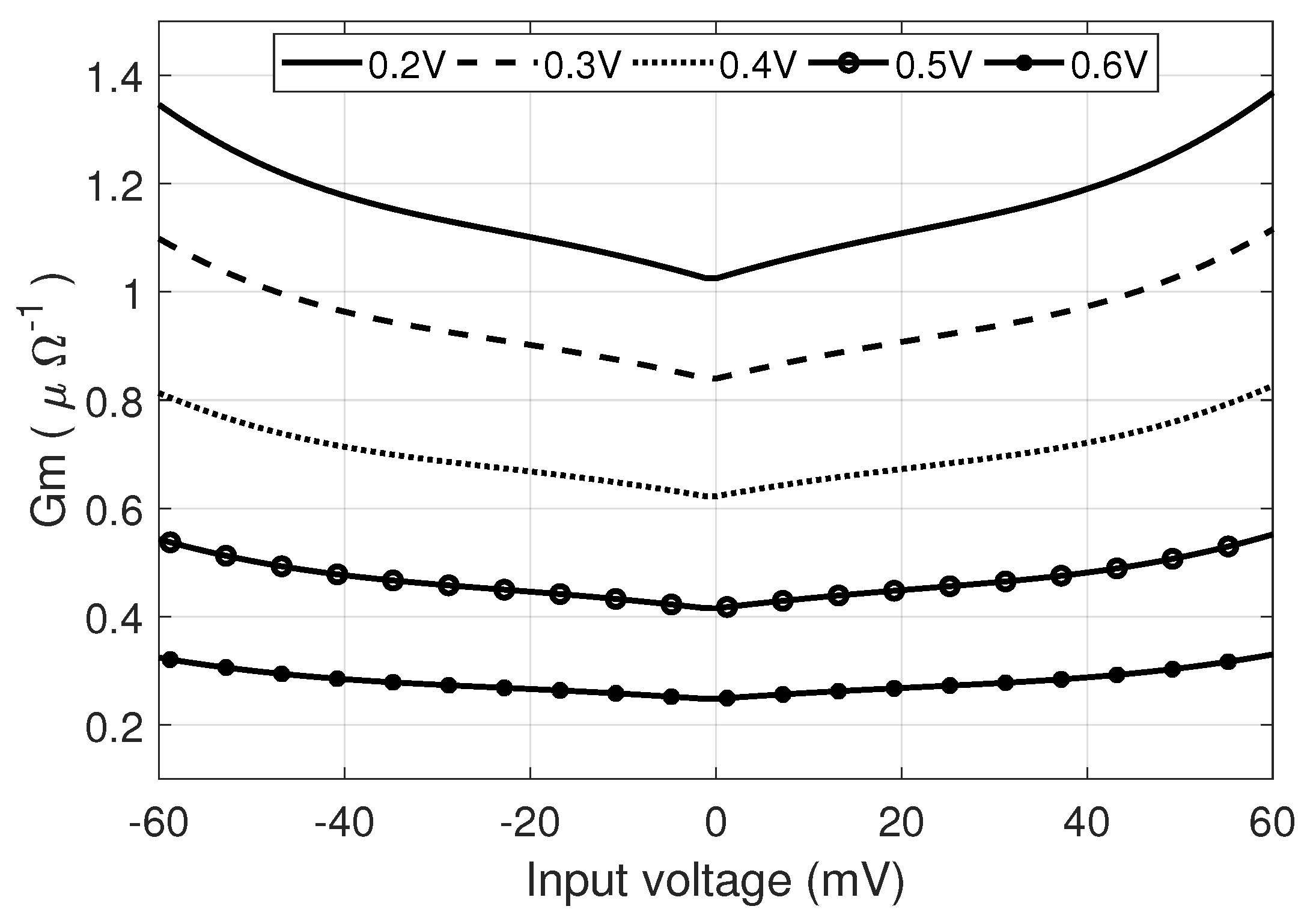

, was simulated and is represented in

Figure 11 as a function of the input DM voltage when the value of the tuning variable

is swept from 200 mV to 600 mV. As observed, the transconductance can be programmed in a range of approximately

, showing a linearized behavior, even though some dependence on the level of the input signal can also be noticed, as predicted by (

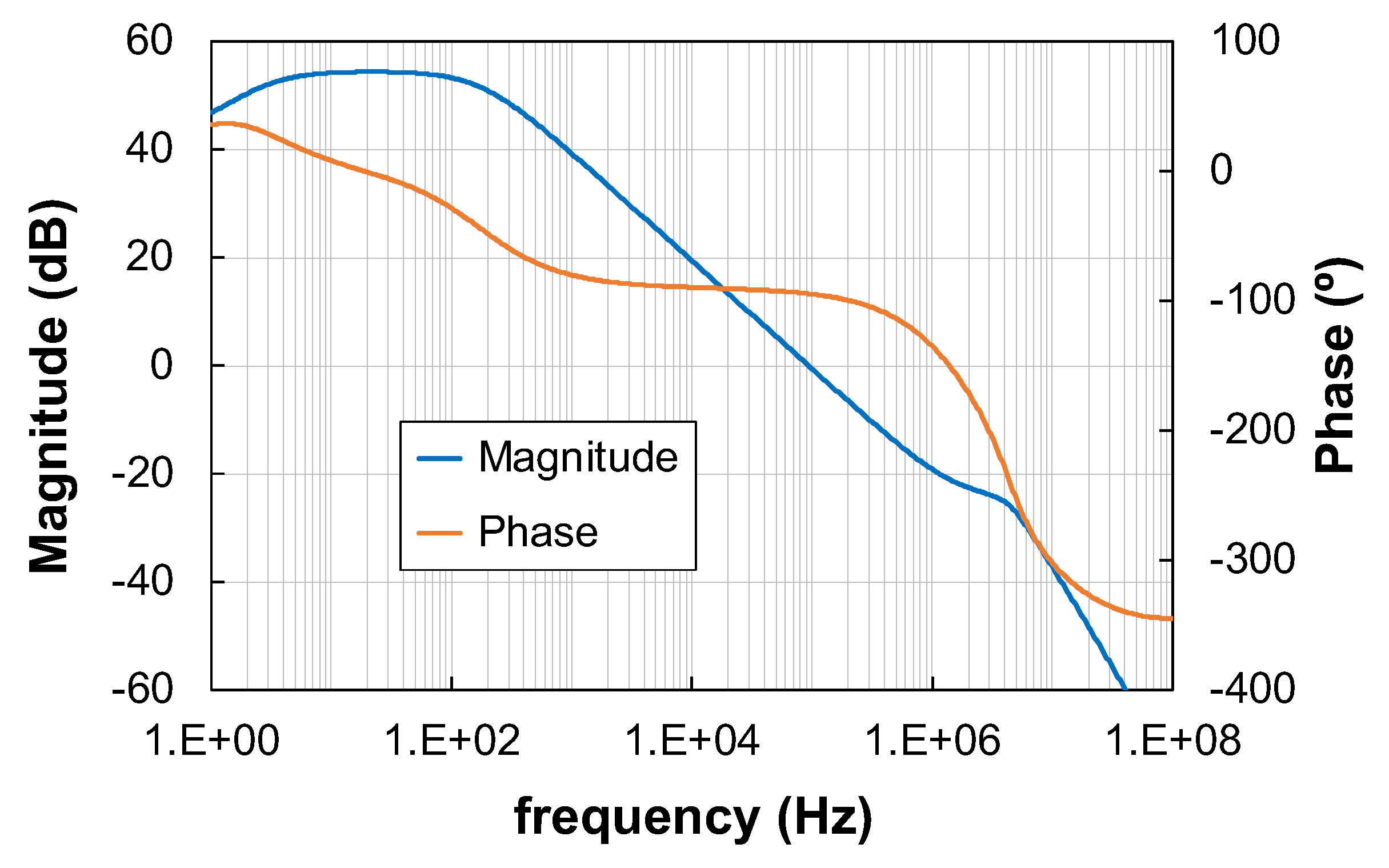

12). The open-loop frequency response of the transconductor is illustrated in

Figure 12, where the magnitude and the phase of the voltage gain are represented. The low frequency corner due to the bootstrapping network is located at around 2.5 Hz, whereas the voltage gain in the low frequency band is 54.2 dB with a unity gain frequency is equal to 94.2 kHz and a phase margin of 85.6°. The low frequency corner achieved is compatible with the frequency range of interest in the intended application. If, for any reason, a lower cutoff frequency is required, a larger value for the gate capacitor

or the pseudo-resistor MG in the bootstrapping network has to be implemented, as already indicated in

Section 2. The stability of the transconductor is easily ensured with the value of the load capacitor selected, as the phase margin ranged between 83.5° and 87.6° when

was swept in the range [200 mV, 600 mV]. The transient behavior to a square wave of the

cell connected in unity-gain non-inverting configuration allowed for confirming its stability.

The robustness of the proposed transconductor has been checked by considering in the simulations mismatches as well as process, voltage, and temperature (PVT) variations. In particular, a 1000-run Monte Carlo analysis with process and mismatch variations in a 3- range has been carried out. Under these stringent mismatch conditions, the values of the open-loop voltage gain, unity-gain frequency, and phase margin were found to be 45.0 ± 12.0 dB, 131.9 ± 17.9 kHz, and 83.7 ± 25.2°. In addition, the closed-loop BW of the transconductor was 110.0 ± 24.1 kHz. In all of these results, the data are represented as the mean value plus/minus the standard deviation. Corner analyses were also run in order to determine the impact of PVT variations on the performance of the transconductor. For the active devices’ typical mean (tt), fast-fast (ff), slow-slow (ss) fast-slow (fs), and slow-fast (sf) conditions were considered, whereas the values of the passive components were varied between the minimum and maximum ranges indicated by the foundry. Additionally, the supply voltage was varied ±10% and the temperature, with nominal value equal to 27 °C, was moved in the range between −20 °C and 80 °C. Considering a total of 45 corners, the open-loop gain, unity-gain frequency, and phase margin varied in the ranges [41.8, 55.6] dB, [84.8, 101.1] kHz, and [84.8, 86.4]°, the closed-loop BW being constrained between 61.4 kHz and 125.4 kHz.

The overall performance of the transconductor is summarized in

Table 3, where is it also compared to other similar solutions previously reported. The following figure-of-merit (FoM) has been used for a fair comparison of the transconductors:

where BW is the bandwidth of the transconductor connected in non-inverting unity-gain configuration,

is the load capacitor, and

P the power consumption. As observed in

Table 3, the proposed low-voltage linearized transconductor is competitive in terms of the

, whereas it presents a high open-loop gain at low frequency and provides the largest BW in the comparative.

The BPF was implemented by using four transconductors exactly equal excluding the linearization active resistor. Indeed, blocks

and

have a nominal transconductance nominally equal to

and, thus, the sizes of devices MR1 and MR2 correspond to those indicated in

Table 2, that is, 1/0.5

m/

m. Nevertheless, as circuit sections

and

were sized with a transconductance equal to 4

, transistors MR1 and MR2 in these cases were provided with aspect ratios equal to 3.8/0.5

m/

m. The biasing current for all the transconductors was set again equal to 100 nA, leading to a total DC power consumption of 2.74

A. The capacitors in the BPF were implemented as metal–insulator–metal devices, with equal values

=

= 25 pF. With these transconductance and capacitor ratios, the quality factor of the BPF was nominally set equal to 4. The reason for selecting relatively high capacitor values is to separate the filter center frequency from the secondary poles of the transconductors, thus avoiding as much as possible any overdamping in the frequency response.

The magnitude response of the BPF over the frequency is depicted in

Figure 13 for different values of the tuning variable

. As observed, the filter center frequency ranges between 6.5 kHz and 37.5 kHz, which demonstrates that the tuning mechanism results are suitable to avoid the parameter variations due to the fabrication process with a very economical implementation. When

=

= 400 mV, the center frequency is equal to 19.1 kHz. The gain of the BPF at the center frequency, nominally set equal to 0 dB as already indicated in (

16a), increases slightly as the value of

is decreased, due to the slight overdamping caused by the approaching of

to the position of the secondary poles in a system with a relatively high quality factor. The noise of the BPF has been integrated in the −3-dB band for the same tuning conditions previously indicated, obtaining a value of 190.5

V

. Furthermore, the −40-dB THD criterion has been used to determine the maximum input signal amplitude that can be processed with a given linearity, obtaining a maximum amplitude of 55 mV. At this point, it is interesting to mention that the large value of the time constant associated with capacitor

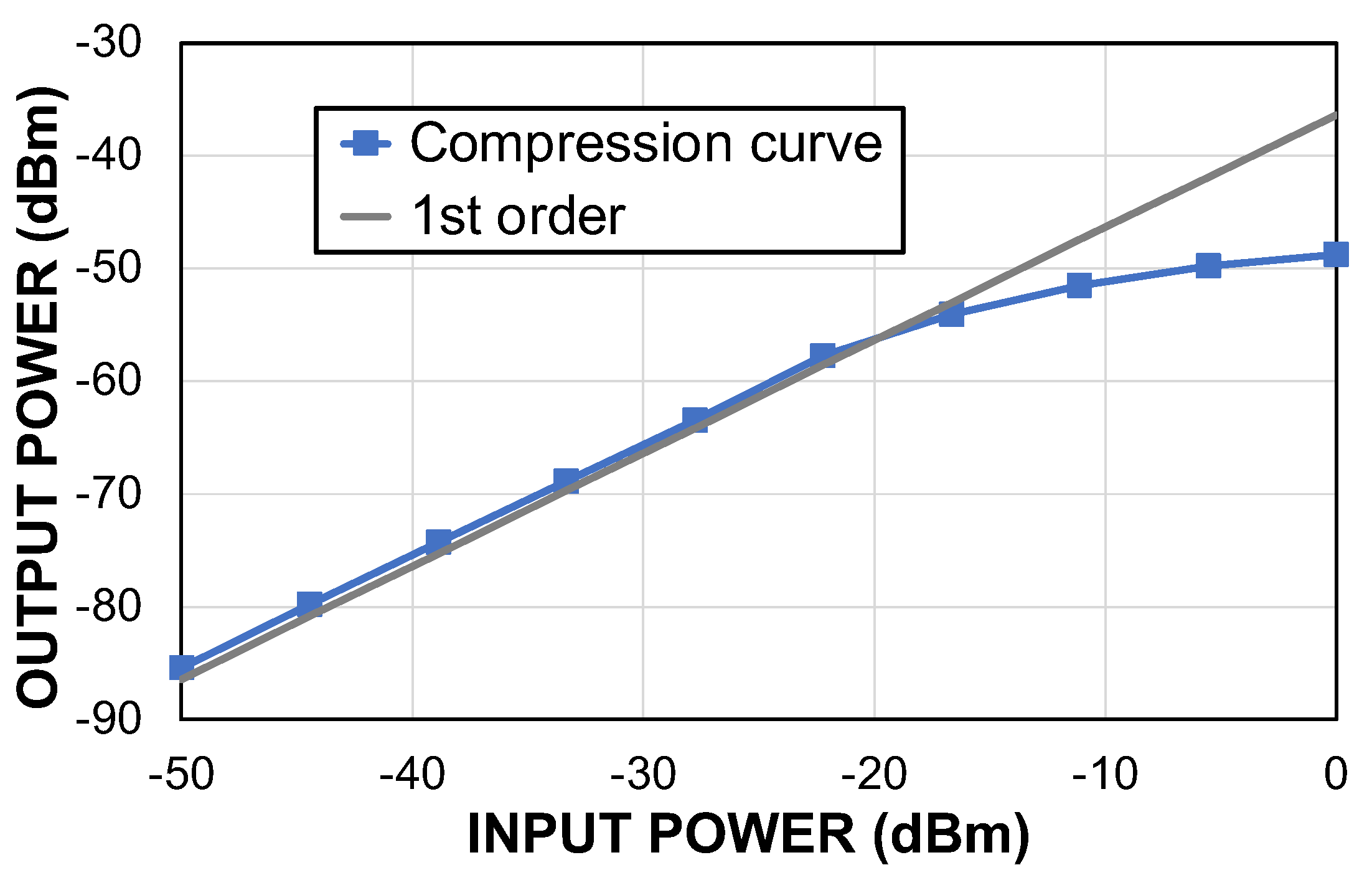

and pseudo-resistor MG in the bootstrapping network leads to a transient response in the BPF output signal of around 1 s before the steady-state regime is achieved. Additionally, the compression curve of the BPF output signal and the third-order intermodulation distortion are represented in

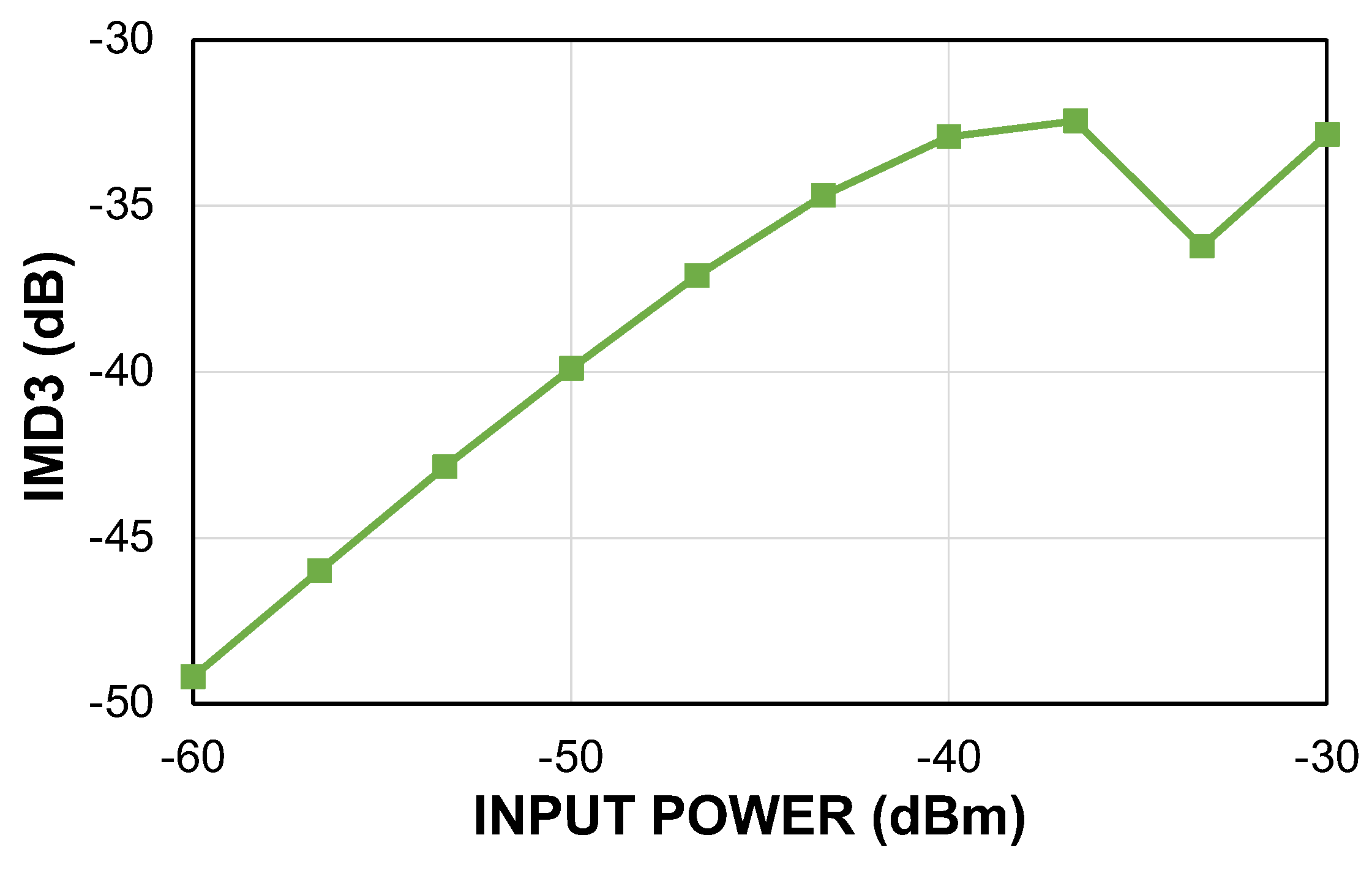

Figure 14 and

Figure 15, respectively. The IMD3 has been obtained by applying two input tones separated ±100 Hz with respect to the BPF center frequency. In addition, from

Figure 14, the input-referred 1-dB compression point has been determined to be −19.13 dBm.

The impact of mismatches and PVT variations on the response of the proposed BPF has been estimated by means of Monte Carlo and corner analyses in the same conditions as described in the case of the linearized transconductor. Regarding Monte Carlo simulations, the center frequency demonstrated itself to be very stable, with a value of 19.4 ± 1.3 kHz, showing worst-case responses equal to 16.1 kHz and 20.7 kHz in the corners.

The performance of the proposed BPF is reported in

Table 4, where it is compared to other similar solutions previously reported. In order to establish an objective comparison between the different BPF structures, the following FoM has been used [

7]

where

P is the power consumption,

the supply voltage,

n the filter order,

the center frequency, and DR the dynamic range. It is worth pointing out that the DR has been calculated as the ratio of the input signal leading to a THD of −40 dB and the in-band input-referred integrated noise. As observed, the proposed approach features a reduced power consumption in a low supply voltage, which results in being very suitable for bioimpedance-based IoT applications. In addition, the FoM is competitive as compared to the other solutions, with an acceptable DR taking into account the stringent operating conditions at the used supply voltage.