Abstract

Tunnel Field-Effect Transistors (TFETs) have been considered one of the most promising technologies to complement or replace CMOS for ultra-low-power applications, thanks to their subthreshold slope below the well-known limit of 60 mV/dec at room temperature holding for the MOSFET technologies. Nevertheless, TFET technology still suffers of ambipolar conduction, limiting its applicability in digital systems. In this work, we analyze through SPICE simulations, the impact of the symmetric and asymmetric ambipolarity in failure and power consumption for TFET-based complementary logic circuits. Our results clarify the circuit-level effects induced by the ambipolarity feature, demonstrating that it affects the correct functioning of logic gates and strongly impacts power consumption. We believe that our outcomes motivate further research towards technological solutions for ambipolarity suppression in TFET technology for near-future ultra-low-power applications.

1. Introduction

In the last 50 years, Moore’s law has boosted the power-performance metrics of integrated circuits. Along with geometrical scaling, the Dennard scaling policy, which consists of scaling the supply and threshold voltage by about the same factor, led to a decrease in the switching power per transistor, such that the power density in a chip remained approximately constant from one technological node to the next. Nowadays, in deep sub-micron technological nodes, the Dennard scaling policy is no more applicable. Indeed, the threshold voltage cannot be further scaled; otherwise it results in an exponential increase in leakage power [1,2]. Consequently, the supply voltage cannot be scaled further without strongly impacting on the system performance. Thus, the power density is no more scaling proportionately, leading to the dark silicon era, characterized by the constraint that all the transistors on a chip cannot be simultaneously powered on at full performance [3].

In this scenario, steep-slope devices such as Tunnel Field-Effect Transistors (TFETs) have emerged as one of the most promising technologies to complement or replace CMOS in ultra-low-power applications [4,5,6], as several comparisons with CMOS demonstrate [7,8,9,10,11,12]. The TFETs exploit Band-To-Band Tunnelling (BTBT) as the main conduction mechanism, thus avoiding the Boltzmann-limited subthreshold swing of Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET). Therefore, TFET technology, thanks to its subthreshold slope below 60 mV/decade, is the key to keep on the scaling down of supply voltage below 0.5 V without affecting the gate over-drive and, thus, the device performance.

Although TFETs present also very low leakage current (IOFF) below pA/μm and an high ON/OFF current ratio ION/IOFF [13,14], the low saturation current (ION) and ambipolarity features still prevent their applicability in low power and high-frequency systems. The low ION of the order of hundreds of μA/μm is due to the limited BTBT probability at the source-channel junction [4]. To improve the ION in these devices, possible solutions relying on bandgap engineering between source and channel, double-gate technology and also on hybrid circuits and increasing the gate-source voltage from a circuit design perspective, were proposed [15,16,17,18,19].

Another disadvantage in TFETs is the presence of ambipolar conduction. Ambipolarity is an intrinsic phenomenon of TFET technology where the conduction occurs for both positive and negative gate voltages. The ambipolar current IAMB flows due to BTBT at the channel-drain junction for negative gate voltage for n-type TFET, and positive for p-type, making TFET technology unsuitable for complementary logic digital systems [19,20,21]. Even if the ambipolar conduction problem in complementary TFET (CTFET) logic is often mentioned in the literature when dealing with device-level engineering, there are still few studies about the specific circuit-level effects of ambipolar conduction and possible solutions to reduce it [19,20,21,22,23,24]. In particular, sometimes it is reported that ambipolarity can lead to circuit failure, but nothing is said about the effects in terms of circuit performance, even in the case of partially suppressed ambipolarity (i.e., when it does not produce evident system failure.

In this article, we consider and analyze a vertical AlGaSb/InAs heterojunction TFET demonstrated experimentally in [25]. Then, by employing the Verilog-A circuital model by Hao Lu et al. [26] we perform SPICE simulations in Cadence Virtuoso to analyze the impact of ambipolarity in malfunctions and power consumption in TFET-based logic gates. Indeed, since is an additive contribution of leakage current, we expect it to cause non-negligible effects on the circuit power dissipation. Our results show that ambipolarity not only affect the correct functioning of logic gates but also strongly impacts on power consumption. These outcomes motivate further research towards technological solutions for ambipolarity suppression in TFET technology for ultra-low-power applications.

2. Theoretical Background and Modeling

2.1. TFET Working Principle

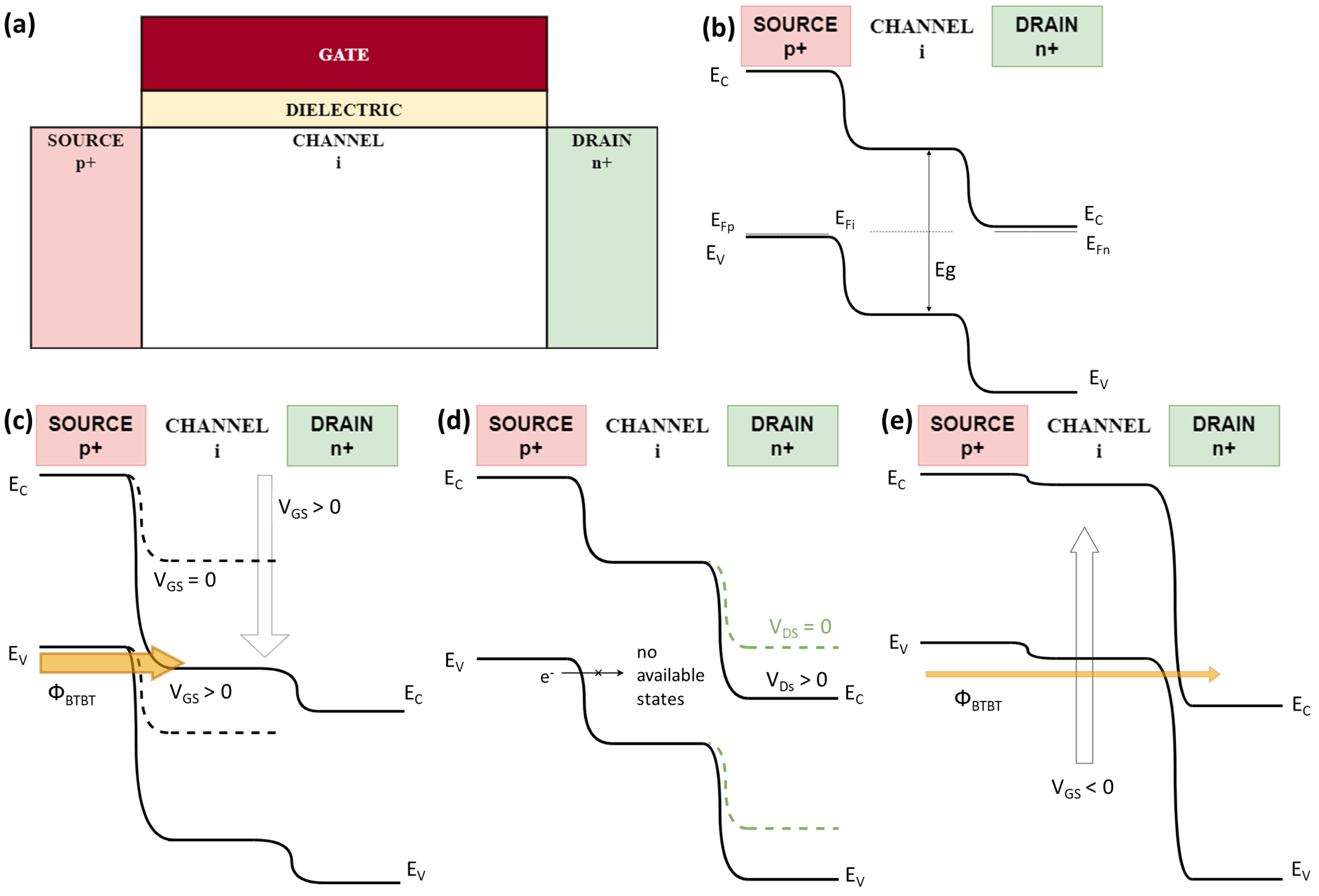

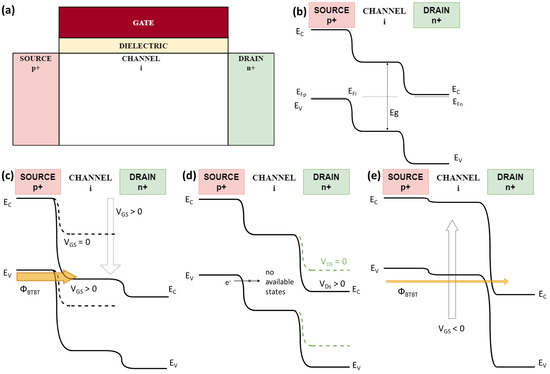

Figure 1 reports the n-type TFET basic structure and the relative band diagrams in its operating regions. The basic n-type TFET device is a p+-i-n+ junction, with an heavily doped p-type source, an intrinsic or lightly doped channel and an heavily doped n-type drain. The channel is underneath the gate oxide and gate contact, that has the capability of shifting and controlling the channel electron bands to switch ON and OFF the device [4]. The p-type TFET presents complementary doping (n+ source, intrinsic channel and p+ drain) with a symmetric voltage device operating mode w.r.t. n-type TFET.

Figure 1.

TFET device conceptual structure and operating principle. (a) Basic n-type TFET device structure; (b) equilibrium band diagram for the device in (a); (c) ON state band diagram for the device in (a); (d) OFF state band diagram for the device in (a); (e) ambipolar state band diagram for the device in (a).

At thermal equilibrium—Figure 1b—the TFET is normally OFF. The Fermi level alignment assures extremely low thermionic leakages of electrons from drain to source and holes from source to drain [4]. The ON state operation is instead represented in Figure 1c. If a sufficiently positive gate voltage is applied (above the threshold), a large amount of electrons can tunnel from the source Valence Band (VB) to the channel Conduction Band (CB), and then by drift they proceed to the drain. Since the tunneling mechanism involves two different bands (VB at source side and CB at channel side) it is referred as Band-To-Band-Tunneling (BTBT). The BTBT phenomenon is indicated in Figure 1c with (orange arrow). The TFET threshold voltage is conventionally defined as the required to have the channel CB edge aligned with the source VB edge, and thus as the onset of the BTBT conduction [4,20,21]. In OFF state (null or slightly negative ) an applied drain voltage has the effect of lowering the drain side bands, with no electron flow happening since no available electron states are present in the intrinsic channel band gap for the source electrons to tunnel in—see Figure 1d. Nevertheless, for enough negative values the channel bands are shifted up and the channel VB becomes populated by the source electrons. In addition, BTBT can happen at drain side from the channel VB to the drain CB, resulting in a large and undesired current, referred as ambipolar current [4,20,21]. The ambipolar state band diagram is depicted in Figure 1e, where (orange arrow) indicates again the BTBT phenomenon. The onset of ambipolar conduction occurs when an enough negative aligns the channel VB edge to the drain CB edge. For more negative values the unwanted BTBT exponentially increases with the decrease. Indeed, the tunneling probability can be often calculated within the Wentzel–Kramer–Brillouin (WKB) approximation as [4,20,21]:

where: is the screening tunneling length, is the electron effective mass, is the channel band-gap, q is the elementary charge, ℏ is the reduced Planck’s constant and is the overlap of the energy bands, i.e., in ON state and in ambipolar state. Since is directly proportional to (through ) the BTBT probability exponentially increases with the applied above the BTBT phenomenon onset.

An interesting peculiarity of TFETs is that it is not possible to have symmetric conduction for positive and negative . Indeed, while in MOSFETs the device structure is completely symmetric and permits to fully exchange source and drain in conduction, in TFETs this is not possible due to the asymmetric p+-i-n+ junction and relative longitudinal asymmetric band structure. Considering also the intrinsically dominant drain capacitance in TFETs and the difficulty in lowering the Miller’s capacitive coupling in layout, the major resulting drawback is that some circuit nodes can overcome the supply voltage (also more than ) or reduce below ground during transients because of the poor capability of discharging capacitances in reversed operating mode [27,28].

2.2. Ambipolarity and Complementary Logic

The great success of digital circuits is established thanks to the principle of design by abstraction levels. Additionally, the usage of abstraction levels is well consolidated for complementary MOSFET (CMOS) logic design and corresponding optimized standard cells. An enormous advantage in TFET-based digital circuits, alongside the compatibility of TFET fabrication processes with CMOS ones, is the possibility of having complementary n-type and p-type devices with fully symmetric transcharacteristics . Indeed, this permits inheriting the design principles and toolchain already developed for CMOS technology. This advantage permits to potentially switch to the novel TFET technology without the burden and the prohibitive cost related to the toolchain re-design, which is otherwise necessary if other kinds of logic are employed or developed for TFETs. Nevertheless, in the case of Complementary TFET (CTFET) logic, the pull-down network (n-type TFETs) and the pull-up network (p-type TFETs) can undergo negative/positive when in OFF states, provoking the undesired ambipolar conduction [20,21].

In this article, we are resolved to clarify the effects of ambipolarity conduction at the circuit level and on complementary digital circuits. In particular, we consider two different kinds of non-ideality effects in TFET transcharacteristics, both leading to an ambipolar conduction for negative/positive values in n-type/p-type devices:

- 1.

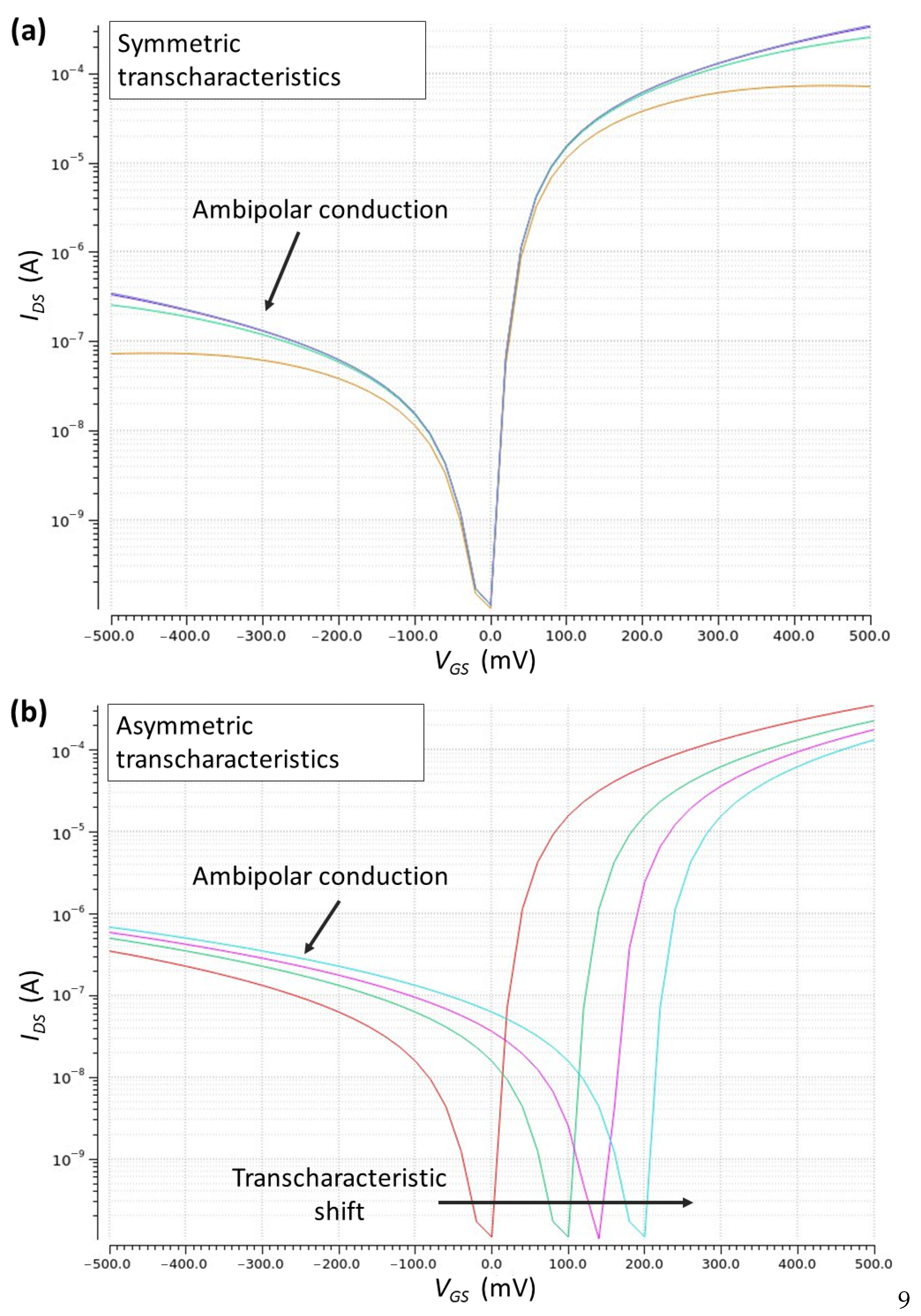

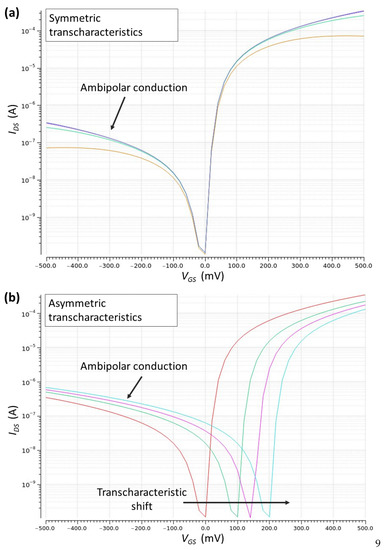

- Ambipolar conduction can originate if the n-type (p-type) TFET device undergoes sufficiently negative (positive) , so that the channel VB edge is shifted above the drain CB edge, with drain-side BTBT, as described in Section 2.1. This is the case of Figure 2a in which various n-type TFET transcharacteristics with different ambipolar current values are reported. In this case, all the transcharacteristics are centered in = 0 V, i.e., the minimum value () is the one obtained with = 0 V. We refer to this case as symmetric ambipolar TFET transcharacteristics, or, to lighten the notation, as the symmetric ambipolarity case.

Figure 2. Examples of ambipolar n-type TFET transcharacteristics. (a) Example of TFET suffering of symmetric ambipolarity: symmetric transcharacteristics with different ambipolar currents; (b) Example of TFET suffering of asymmetric ambipolarity: asymmetric transcharacteristics with different shift w.r.t. ideal (red) one.

Figure 2. Examples of ambipolar n-type TFET transcharacteristics. (a) Example of TFET suffering of symmetric ambipolarity: symmetric transcharacteristics with different ambipolar currents; (b) Example of TFET suffering of asymmetric ambipolarity: asymmetric transcharacteristics with different shift w.r.t. ideal (red) one. - 2.

- In addition, there is the possibility of having non-fully symmetric transcharacteristics. Indeed, it is proved the TFET transcharacteristics to be very sensitive to gate metal workfunction choice, gate stack material engineering, gate fabrication process and variations [27,28]. The main effects is to obtain a shifted TFET transcharacteristic, as depicted in Figure 2b. The detrimental effect is that in normal operating conditions, the slightly negative is already capable of driving the TFET in ambipolar state. We refer to this case as asymmetric ambipolar TFET transcharacteristics, or, to lighten the notation, as the asymmetric ambipolarity case.

2.3. TFET Compact Model

In order to understand the effectiveness of an emerging technology, circuit and system-levels figures of merit need to be estimated and compared with current technology. With this purpose, a variety of compact and semi-empirical circuital models have been developed for novel technologies [29,30,31,32]. In this work, we employ the TFET compact model developed by Hao Lu et al., at the University of Notre Dame (Notre Dame, ID, USA) [26]. It is an analytical model based on the Kane–Sze formula for calculating the current-voltage characteristics under the WKB approximation. Moreover, the Notre Dame model is proved to represent the real TFET device behavior well in all its operating conditions, including the ambipolar state. It is a continuous model in which the transition from a TFET operation state to another one happens with no discontinuity, thanks to a suitable mathematical function developed for this purpose. The model is implemented in Verilog-A and includes an empirical capacitive model to permit complete circuit simulations. Moreover, some model parameters should be fitted to experimental data to represent real devices. Of particular interest in this work is the dimensionless parameter s, that enables ambipolar conduction. The ambipolar current is indeed represented as a scaled and shifted version of the ON current through the parameter s:

By comparison with the ON state current , we notice that the dependence of is the same as for the ON current. Instead, the dependence is modeled by reversing the sign of the applied . For , the ambipolar current results zero for all the (, ) pairs. For increasing s values the ambipolar current increases up to the ON current value , obtained with .

3. Methodology

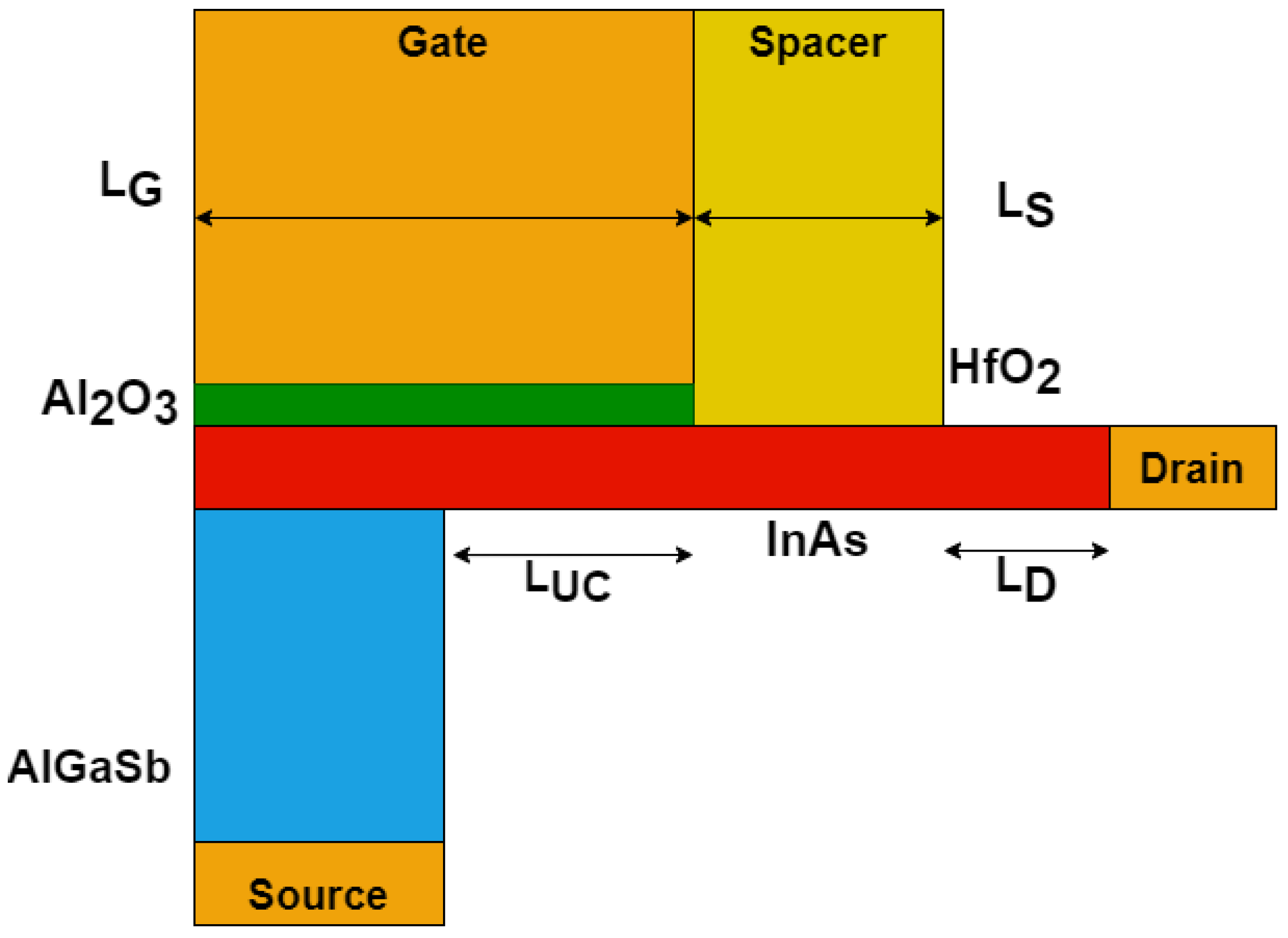

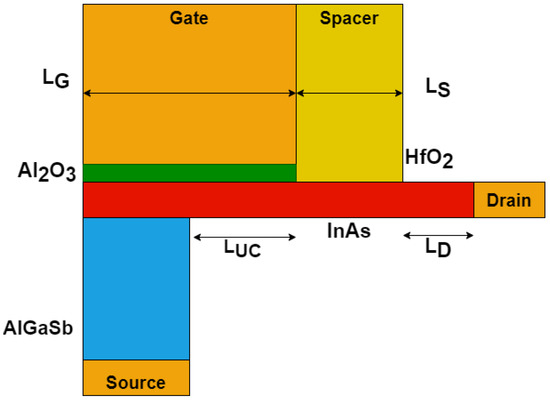

To investigate the effects of symmetric and asymmetric ambipolarity in realistic complementary logic digital circuits we consider the AlGaSb/InAs heterojunction TFET depicted in Figure 3, and we use Cadence Virtuoso with the Verilog-A Hao Lu model to simulate the CTFET logic circuits with such device.

Figure 3.

Structure of vertical AlGaSb/InAs heterojunction TFET. is the gate length, the spacer length, the spacer-drain overlapping length, and the undercut length.

The Hao Lu model is proved to well match the experimental data for the considered AlGaSb/InAs TFET [26]. We set the Hao Lu model fitting parameters as indicated in [26] to have a perfect match of the considered AlGaSb/InAs TFET characteristics with the reference device, according to the Hao Lu provided model library [26,33]. The AlGaSb/InAs heterojunction is used to increase the BTBT efficiency from source to channel and thus improving the [4]. The high-k gate oxide is Al2O3 and the use of the undercut permits to achieve a steep subthreshold slope. The HfO2 spacer with the gate-drain underlap is proved to suppress ambipolarity. This is possible through a reduced gate induced band bending at drain side, thanks to the spacer of length , that reduces the gate-drain coupling. To correctly represent the ambipolar conduction resulting from experimental data the s should be set to [26]. Table 1 reports the device parameters that we employ in all our simulations. These parameters refer to the experimental device and to the library component of the Hao Lu model.

Table 1.

Physical and geometrical parameters of the considered AlGaSb/InAs heterojunction TFET.

We consider complementary logic CMOS-like digital circuit topologies implemented with n-type and p-type AlGaSb/InAs TFETs. We assume a supply voltage of 0.5 V as predicted by the IRDS [6], and calculate the figures of Merit (FoM) of interest as follows:

- the ON current is calculated as the value with ;

- the OFF current is calculated as the value for and ;

- the threshold voltage is calculated starting from its operative definition as the maximum of the second order derivative of the w.r.t. (maximum transconductance method);

- the Subthreshold-Slope () is conventionally calculated as the inverse of the first order derivative w.r.t. in the subthreshold region;

- the Drain-Induced Barrier Lowering () is calculated as:where and are the threshold voltages for equal to and to a low value that we set equal to 0.05 V.

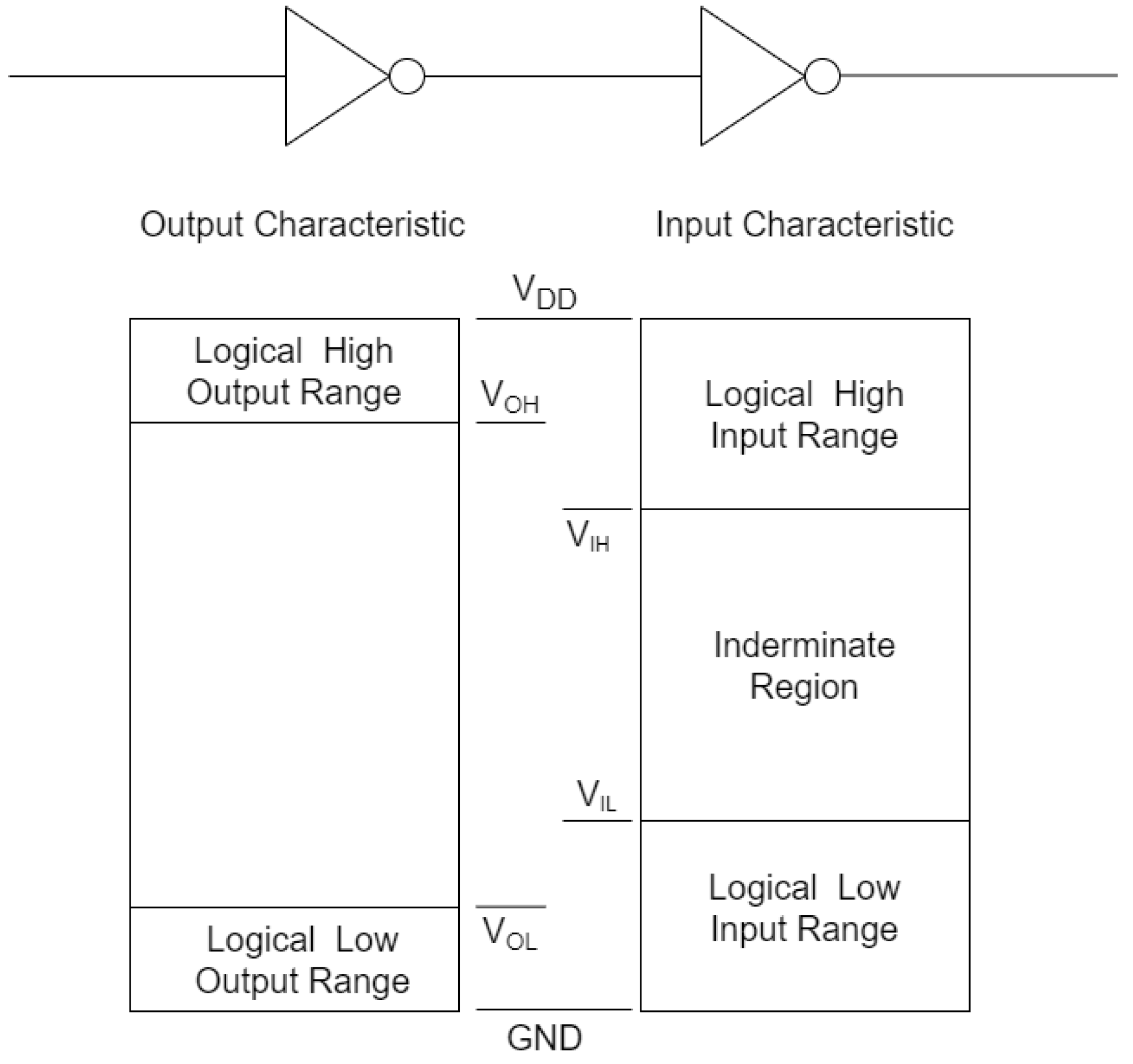

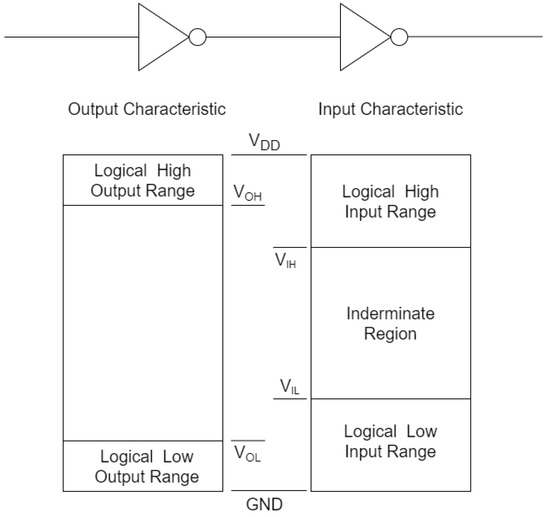

In addition, to evaluate the reliability of the investigated TFET-based logic gates, we quantify the noise margins of the logic gates. The noise margin for logic value ‘1’ (high) is defined as , whereas the noise margin for logic value ‘0’ (low) as , where:

- is the minimum output voltage for the logic value ‘1’ (high);

- is the minimum input voltage for the logic value ‘1’ (high);

- is the maximum input voltage for the logic value ‘0’ (low);

- is the maximum output voltage for the logic value ‘0’ (low).

These parameters are schematized in Figure 4.

Figure 4.

Logical parameters and noise margins definition.

Furthermore, we define and calculate the sensitivity S and the percentage sensitivity of the quantity Q w.r.t. the parameter p as:

where and are the nominal/average parameter and quantity, respectively. Finally, we calculate the average dissipated power by the entire logic gate of interest as:

where is the total current provided by the supply line and T is the considered time interval, set equal to the time required to switch all possible input combinations in sequence with constant clock period of 0.5 ns.

To investigate the effect of symmetric ambipolarity we firstly consider the real ambipolarity present in the considered AlGaSb/InAs TFET, and then we arbitrarily also consider the cases in which and . The first to understand the effect of an enhanced ambipolarity, leading to an comparable with the of the device. The latter to understand the effect of a fully suppressed ambipolarity, i.e., . Even if the considered TFET device experimentally presents a partially suppressed ambipolarity (), we believe a fair comparison should consider the same reference structure with different ambipolar conduction only ( and ). Indeed, by considering different real devices, the structure would be different, making not possible to directly correlate the circuit-level results to the ambipolar conduction only, since many factors would influence it. Whereas, by considering exactly the same reference structure, with enhanced or suppressed ambipolarity leads to fair comparisons, with circuit performance results attributable to ambipolar conduction only.

Furthermore, to investigate the asymmetric ambipolarity effects on circuit functioning and performance, we shift the TFET transcharacteristics by adding a series DC voltage generator on the TFET gates. This has the effect of suitably shifting the TFET transcharacteristics of the desired amount as conceptually described in Figure 2b.

4. Results

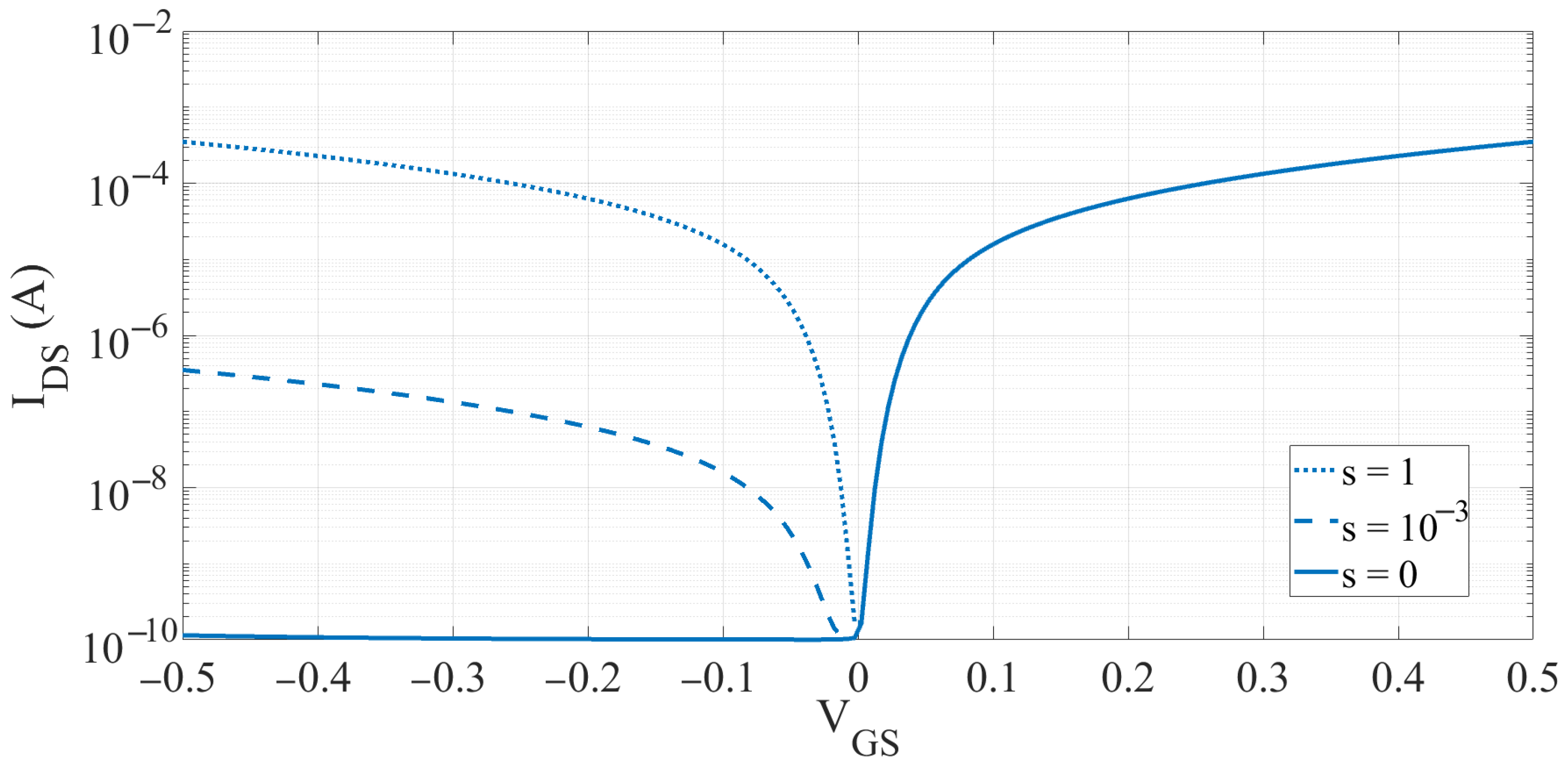

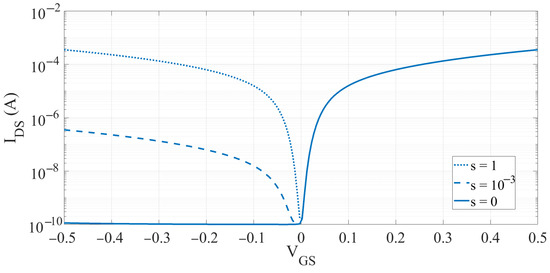

Figure 5 shows the n-TFET transcharacteristic IDS(VGS) at drain-source voltage VDS = VDD = 0.5 V for different values of the symmetric ambipolarity parameter s. Note the suppression of the ambipolarity current for the transcharacteristic having , and a substantial comparable with the for the transcharacteristic having . Table 2 reports the main figures of Merit (FoM) for the n-type TFET device. Similar values are obtained with the p-type TFET, thanks to the full symmetry of the device. The TFET FoMs denote a superior device performance compared with commercial 3D MOSFET such as FinFETs and NS-GAAFETs [34,35,36,37]. In particular, the obtained subthreshold slope (SS) is well beyond the 60 mV/dec room temperature MOSFET limit, with also a very competitive DIBL [34,35]. As expected from the literature [4], the considered TFET also presents a poor , and a considerably reduced value, around one order of magnitude less than MOSFET ones [34,35,36,37].

Figure 5.

The device transcharacteristic IDS(VGS) at VDD for different values of the s parameter.

Table 2.

Calculated FoM for vertical AlGaSb/InAs heterojunction TFET.

4.1. Functional Verification

We verify the functionality of basic logic gates (NOT, XOR, NAND, NOR) and analyze what is the effect of asymmetric ambipolarity on their logic behavior. For all the logic gates, we perform DC and transient simulations by varying , which corresponds to considering different amount of asymmetric ambipolar conduction due to physical and geometrical parameter variations and to process variations, as mentioned in Section 2.1. In the following, we only show the most significant cases related to the digital inverter and NAND gate, where the ambipolarity strongly impact on their fault tolerances.

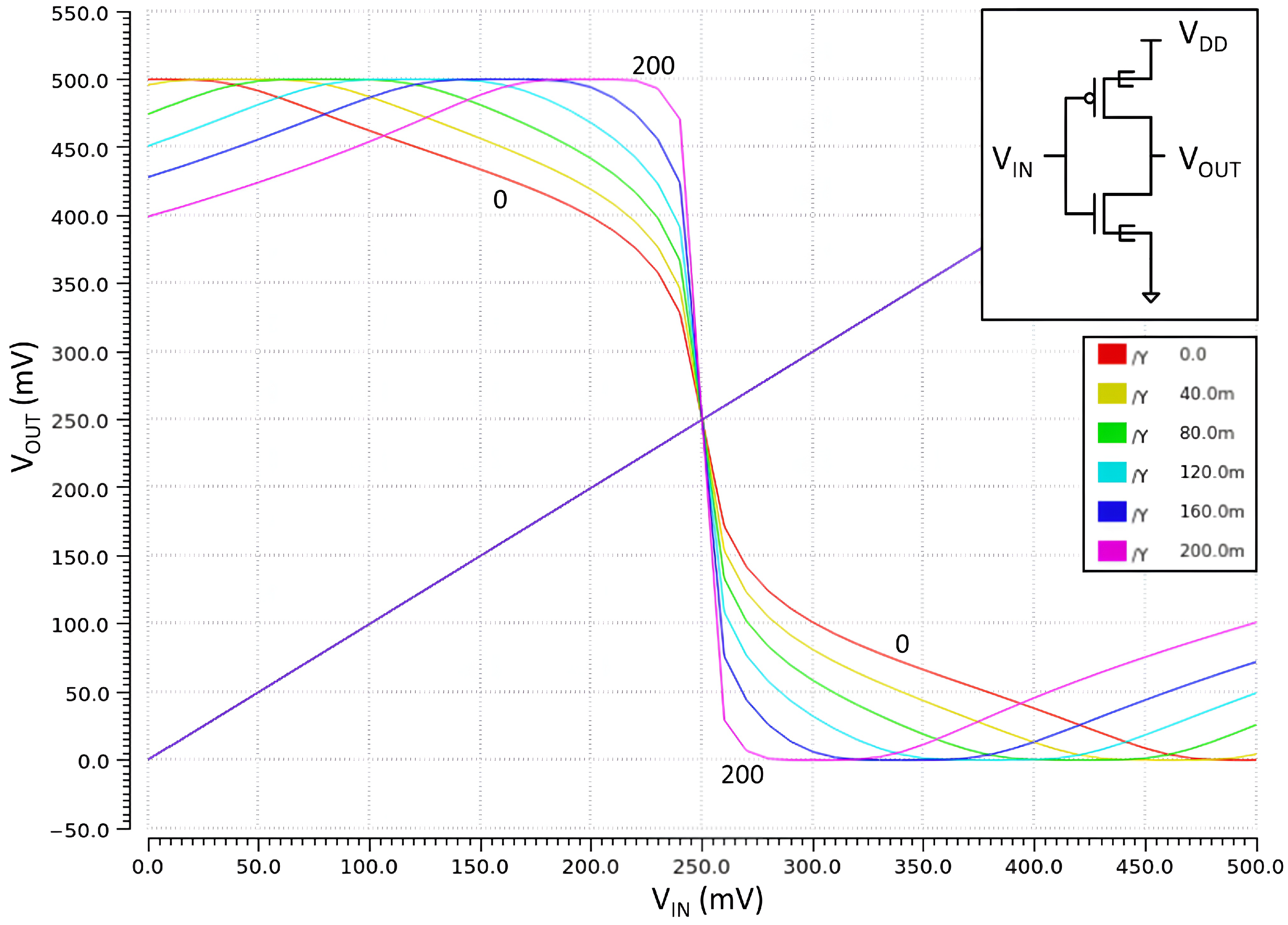

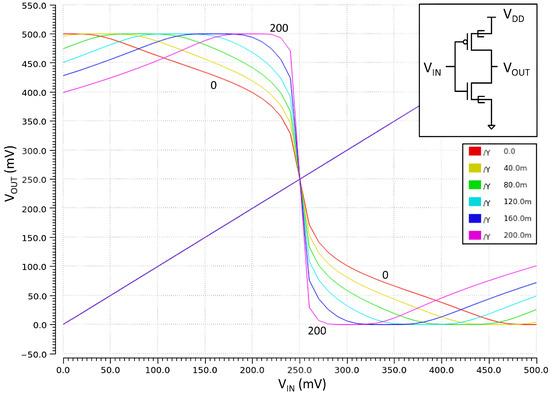

Figure 6 reports the Voltage Transfer Characteristic (VTC) of the TFET-based inverter for null asymmetric ambipolarity (red line), and finite values (other colors). The value is varied up to 200 mV with a fixed step of 40 mV. All the VTCs present poor performances if compared with typical CMOS ones, with very low slopes, thus requiring a large transition region in which (or ) before (or after) the flex point at half of the dynamic voltage swing (0.25 V). Such a large transition region is primarily due to the poor driving strengths of the pull-up (p-type TFETs) and pull-down (n-type TFETs) networks. Indeed, because of the extremely low value, by sweeping the from ground to , a sharp increment of the sub-threshold currents of the OFF networks occurs, and the typical low TFET saturation current values do not compensate such rapid increase of leakage currents.

Figure 6.

TFET-based inverter transcharacteristics at different values: red (null shift), yellow 40 mV, green 80 mV, light blue 120 mV, dark blue 160 mV, purple 200 mV. The blue straight line corresponds to the straight line. The top-right inset shows the CTFET inverter schematic.

For finite values of , the asymmetric ambipolarity gradually affects the output voltage swing of the inverter, by reducing more and more its noise margins with increasing . For low values, the gradual increase of the asymmetric ambipolarity leads to strong increment of the subthreshold current of the pull-down n-type TFET enhancing its driving strength. Because of this, the p-type TFET becomes less effective in pulling up the output line at low values of . Analogous considerations hold for high values of close to : the strong increment of the subthreshold current of the pull-up p-type TFET enhances its driving strength and the n-type TFET becomes less effective in pulling down the output line. A more ideal behavior is instead recovered for greater/lower thanks to a compensation of by itself, causing the increase/decrease before/after the transition at half of dynamic.

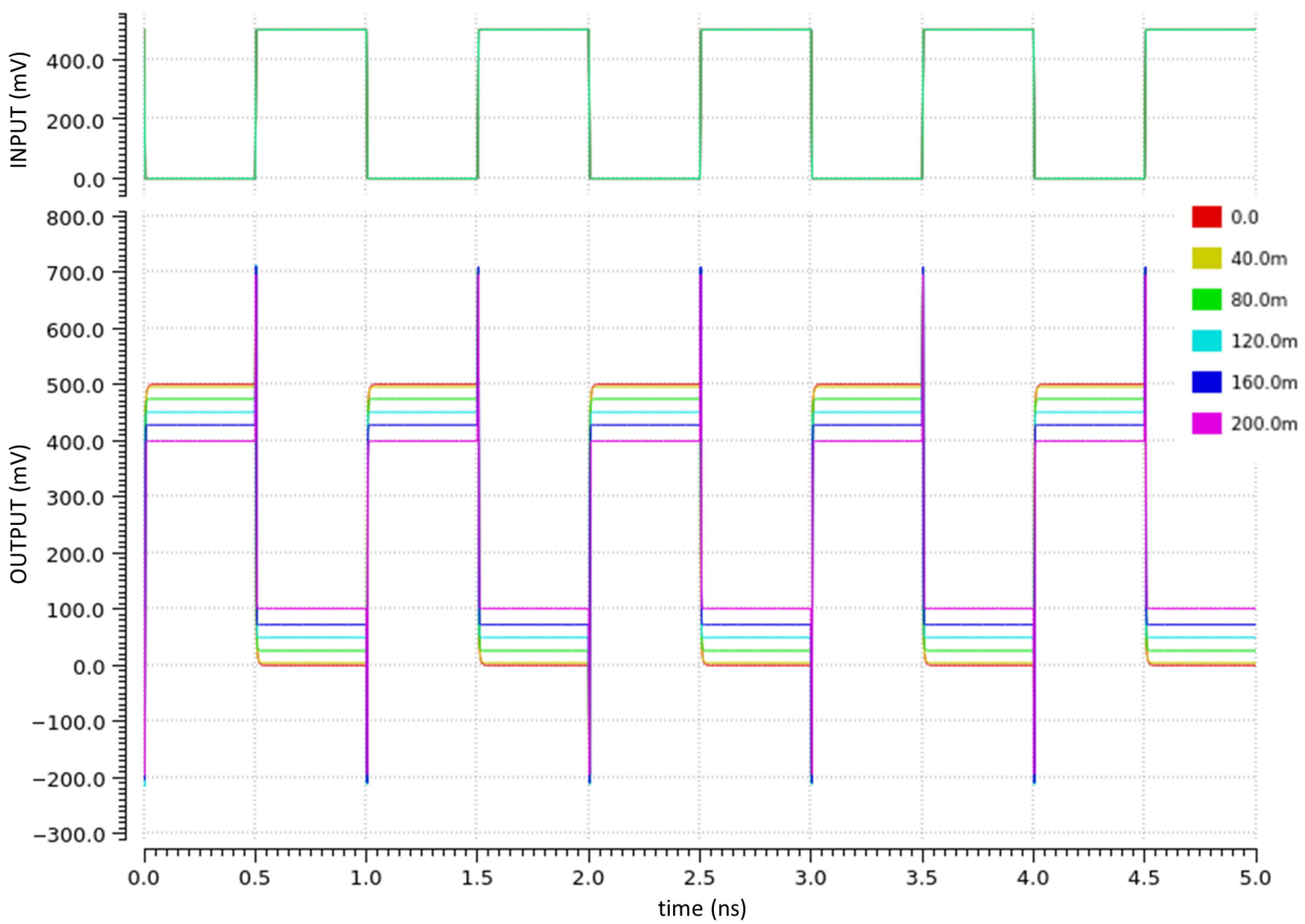

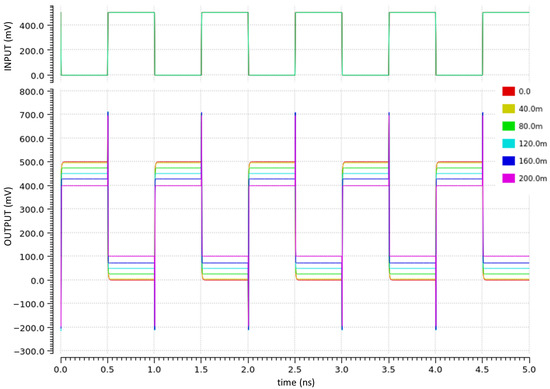

Figure 7 reports the transient simulation of the TFET-based digital inverter for different values of . The evident voltage peaks in the output signals are typical of TFET technology [28], and they are due to the asymmetric TFET structure, as mentioned in Section 2.1. Indeed, while in CMOS technology the symmetric conduction of MOSFETs for both positive and negative permits to discharge capacitively coupled lines, for TFETs this does not happen since a reversed leads to poor TFET conduction and thus long time intervals to dissipate the extra charge [28]. In the inverter case, the output voltage transients are short compared with the supposed clock period (i.e., 0.5 ns), nevertheless they are quite marked with maximum peaks that exceed of 200 mV, i.e., 40% of the itself (analogously for ground with −200 mV reached).

Figure 7.

Transient simulation of the TFET-based digital inverter for different values of : red (null shift), yellow 40 mV, green 80 mV, light blue 120 mV, dark blue 160 mV, purple 200 mV. The green signal is the input signal.

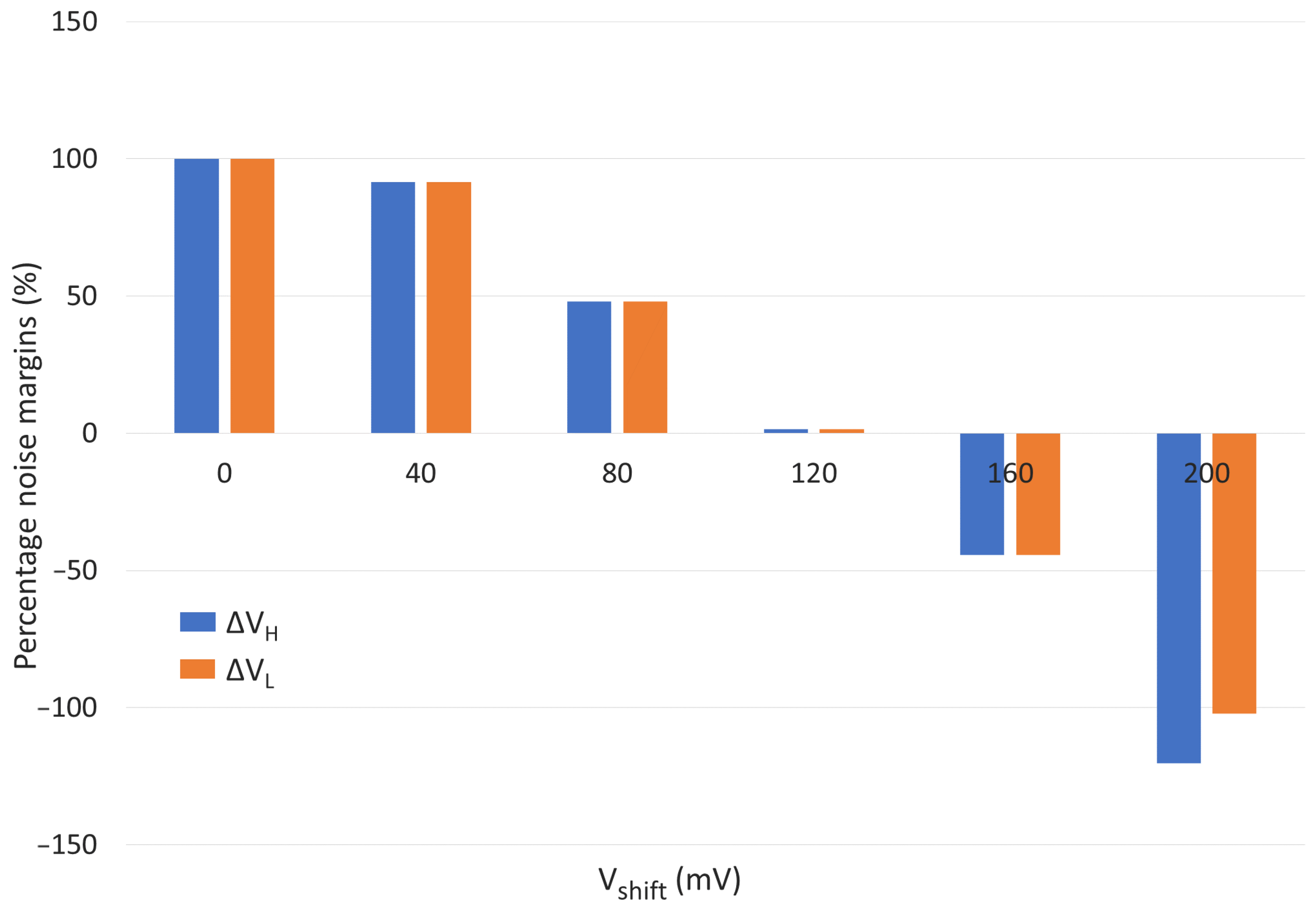

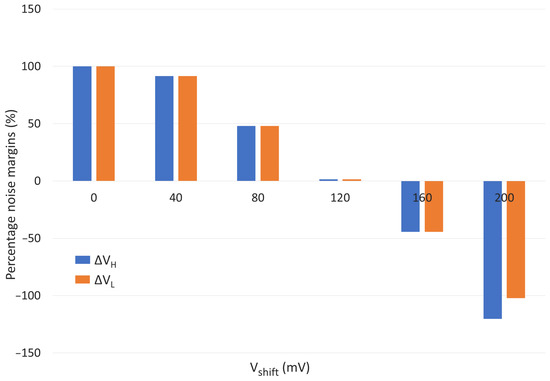

From the inspection of the output voltage dynamic evolution we notice that the effect of the asymmetric ambipolarity is to deteriorate the inverter output logic values ‘1’ () and ‘0’ (). Table 3 report the and values sampled at steady state and the noise margins , of the inverter obtained as described in Section 3 by supposing the input characteristic in Figure 4 not affected by asymmetric ambipolarity () and choosing the input logic values 450 mV and 50 mV, for which an acceptable reduction of the output logic values occurs—Figure 6. The monotonic decrement of and increment of , reported in Table 3 are the causes of the steep reduction of the noise margins for increasing . For suppressed asymetric ambipolarity the noise margins for low and high logic values results about 50 mV, whereas for 80 mV they are almost halved. This 50% reduction potentially causes metastability and misinterpretation of the logic values when propagating throughout cascaded logic gates. The noise margins obtained for 120 mV are almost null and then negative, thus unacceptable for the propagation of the digital information, since the discrimination between the two logic values is no longer possible, and placing cascaded logic gates would cause a failure. This results is better highlighted in Figure 8, in which the percentage noise margins are reported in function of the values.

Table 3.

Output logic values and noise margin of the TFET-based inverter as a function of the asymmetric ambipolarity parameter .

Figure 8.

Noise margins percentage of TFET-based inverter as function of different values of . The orange bar represents the percentage noise margin for low logic value, whereas the blue one the reduction of noise margin for high logic value.

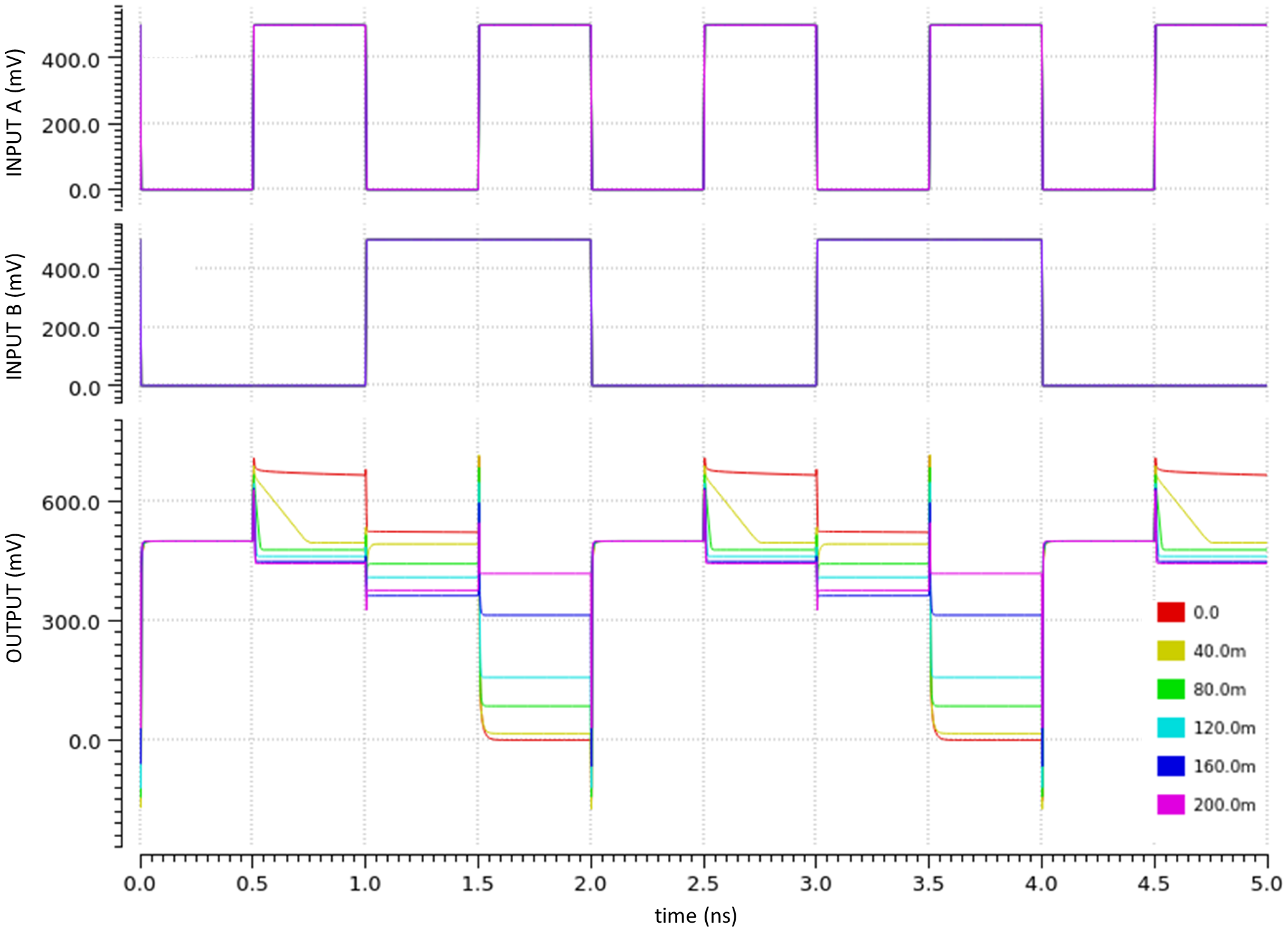

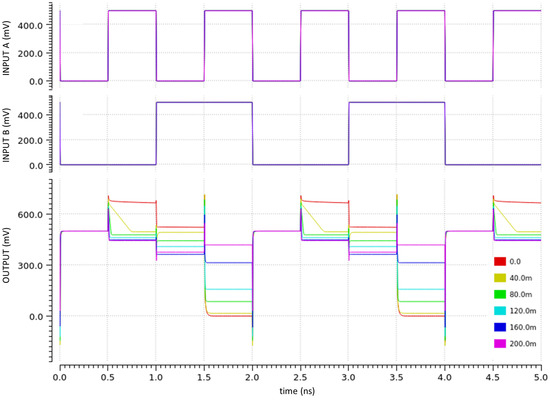

In the following, we also show the effect of asymmetric ambipolarity on NAND gate functioning, and we consider again different values of . The transient simulation of the NAND gate is reported in Figure 9, in which all the possible combinations of inputs are tested. As in the case of the CTFET inverter also the CTFET NAND gate presents output voltage spikes beyond the and below the ground. Nevertheless, for the logic input combination and the output node is kept at a voltage value well beyond for all the clock period, showing a slow exponential decay trend. A similar situation, but much less marked, is present also for the and case. The reasons are again related to the TFET impossible asymmetric conduction w.r.t. the sign of , that permits extra charge discharging only through the drain to source small leakage paths [28].

Figure 9.

NAND gate time transient simulation with different TFET transcharacteristic shift values: red (no shift), yellow 40 mV, green 80 mV, light blue 120 mV, dark blue 160 mV, purple 200 mV.

Concerning instead the effect of the asymmetric ambipolarity, in the case of (suppressed asymmetric ambipolarity) no relevant malfunctioning of the NAND gate occurs, meaning that, analogously to the inverter case, the symmetric ambipolarity does not affect the gate functioning. This is true for all the combinations of the input. Instead, for finite values, there is a significant noise margin reduction, with noticeable failures for large values. Therefore, the asymmetric ambipolarity induces behavioral malfunctions in the NAND gate, making it unusable for logical and arithmetic operations. We report some output voltage values of interest in Table 4—low logic level ‘0’ should be ground (0 V), high logic value ‘1’ should be (500 mV). A significant reduction in noise margins already occur at = 80 mV, with noise margins preventing cascading stages at = 120 mV. The NAND gate does not provide correct logic behavior for larger than 160 mV.

Table 4.

Output voltage in mV for the two-input NAND gate for the considered values. A and B are the two inputs of the NAND gate, logic 0 is encoded through a 0 V voltage value while logic 1 is encoded through an 500 mV voltage value. The chosen input combinations highlight the NAND malfunctioning when is increased.

4.2. Power Analysis

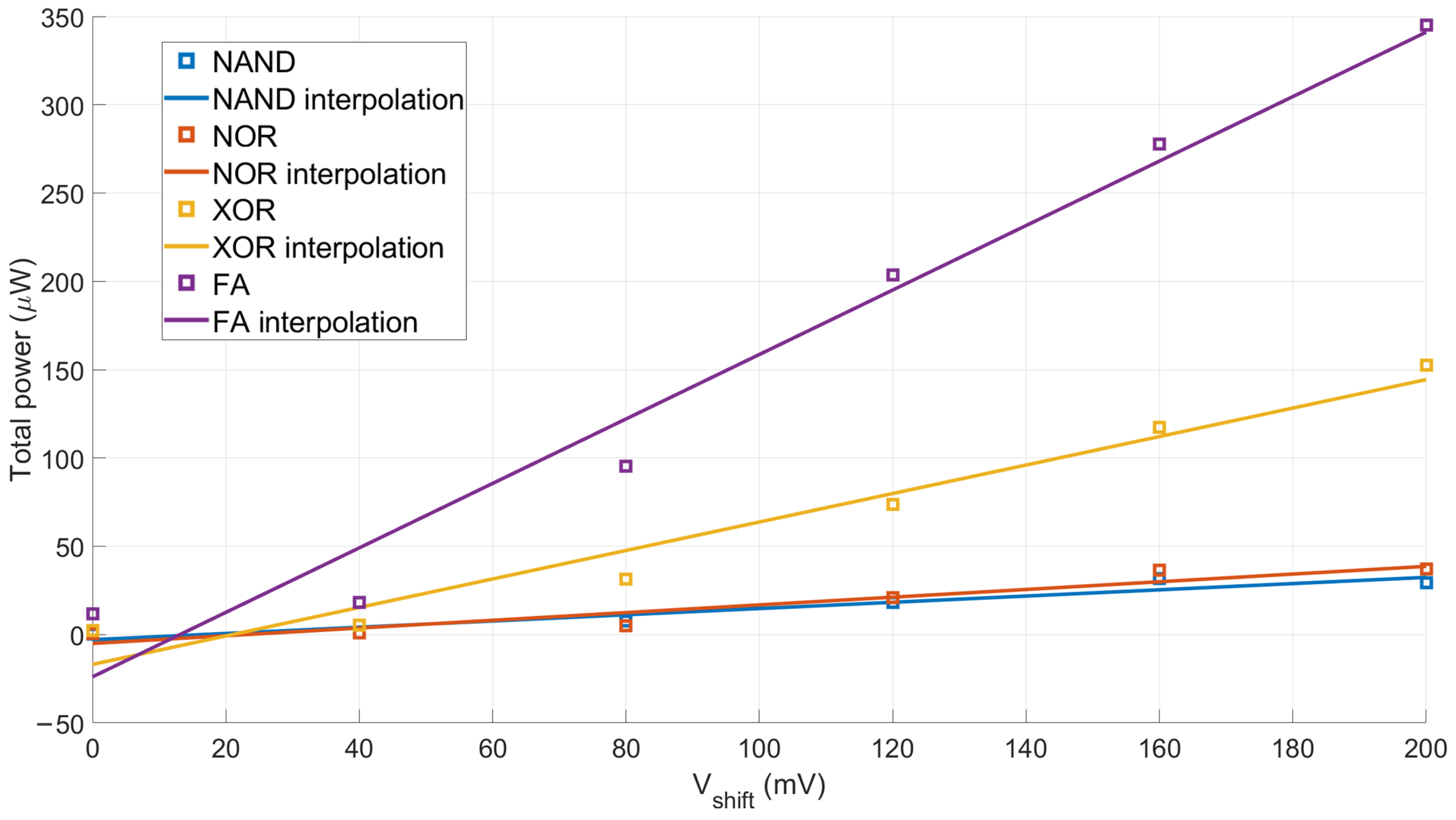

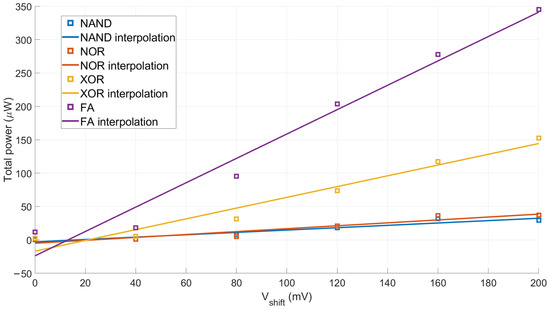

We separately investigate the effect of symmetric and asymmetric ambipolarity on dissipated power in the basic CTFET logic cells. Table 5 reports the total average dissipated power, calculated with Equation (5), in function of for the basic two-input logic gates NAND, NOR, XOR and for the Full Adder (FA). The s parameter is fixed at in all cases. As increases the power consumption increases more than linearly. For example, concerning the NAND gate, by passing from to 40 mV the power consumption is doubled, while from 40 mV to 80 mV it increases of more than seven times and from 80 mV to 160 mV it increases of four times. We attribute this trend to the exponential increasing ambipolar current values that replace the OFF current values when the transcharacteristics are shifted with increasing -refer to Equation (1) and the discussion in Section 2.1.

Table 5.

Total power dissipation depending on the asymmetric ambipolarity for parameter Vshift.

Furthermore, we calculate the percentage sensitivity of the dissipated power w.r.t. starting from the definition of Equation (4) by exploiting the approximation reported in Equation (4). In particular, to extract the values, we interpolate the simulated data sets of Table 5 with straight lines (first order polynomial function) and we assume the angular coefficients of the best fitting straight line (in the least-squares sense) to be equal to (after normalization and multiplication by 100). The interpolations are reported in Figure 10, and the obtained sensitivity values are reported in Table 6. The minimum power consumption sensitivity to the asymmetric ambipolarity is obtained with the NAND gate, with a sensitivity of 17.66%. The sensitivity drammatically increases for more complex logical circuits (XOR and FA), achieving also the 182.52% for the FA case. The greater is the total power consumption of the considered logic gate (from NAND to FA) the larger is also the slope of the interpolating line, i.e., the sensitivity to , and the circuit total power consumption dependence on is dramatically increased if the considered digital architecture dissipates on average more power. In other words, the greater the power consumption, the greater the sensitivity of the dissipated power from the considered digital block.

Figure 10.

Total dissipated power for the basic logic gates as a function of . The markers are the simulated data, the straight lines are the first order polynomial interpolations (least-squares sense). The negative power values obtained for small values-below 20 mV-are artifacts due to the interpolation through a linear polynomial function.

Table 6.

Total dissipated power percentage sensitivity to Vshift, indicated with .

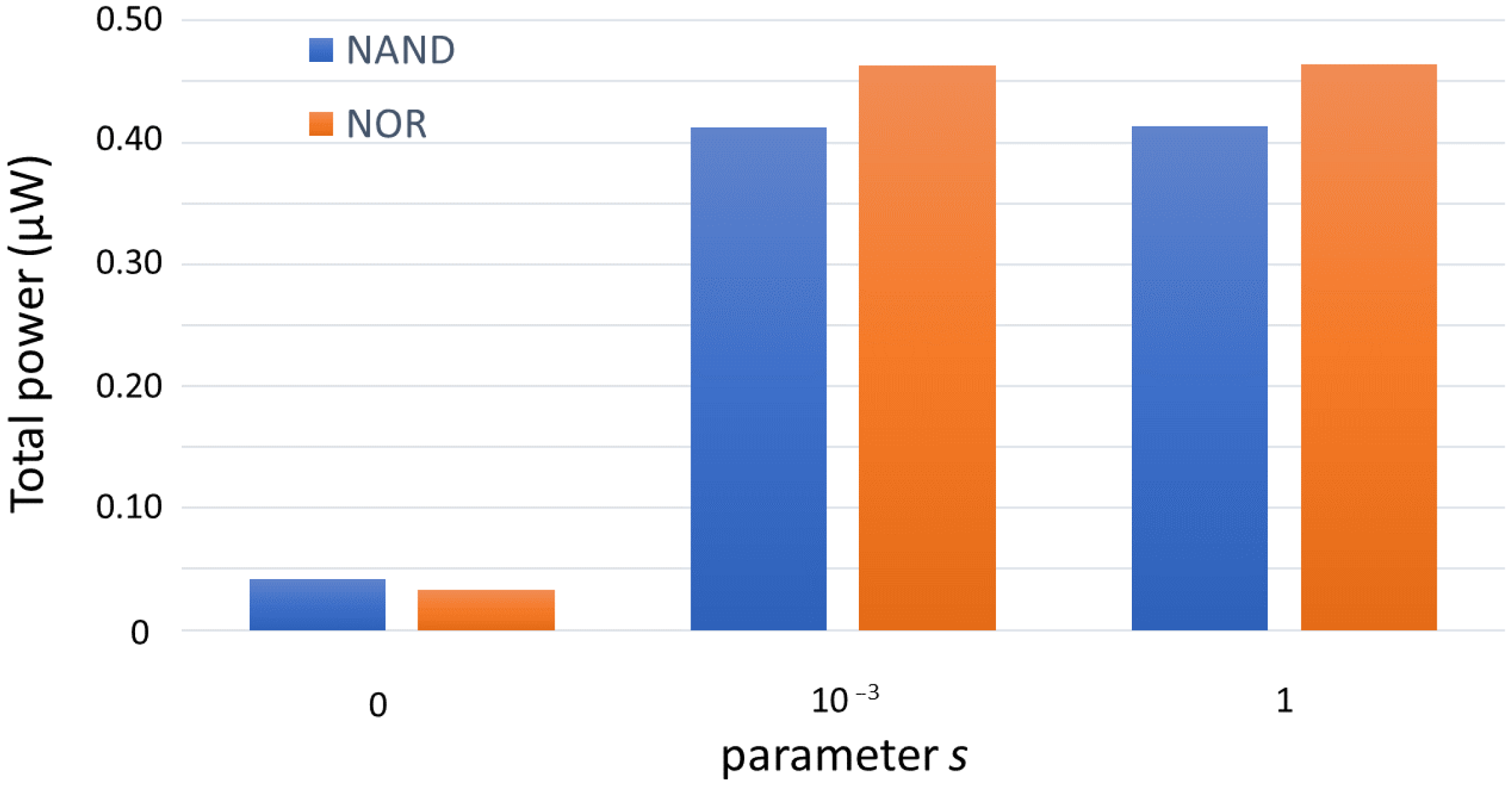

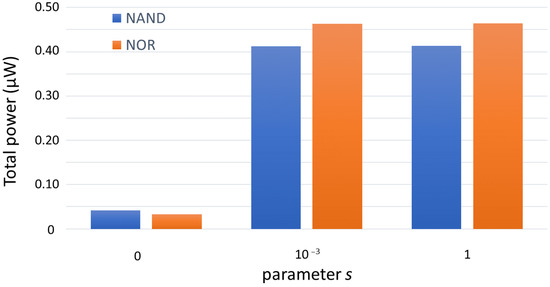

We then consider the effect of the symmetric ambipolarity on the total dissipated power. In this case, we consider only symmetric TFET transcharacteristics, i.e., we fix , whereas we vary the magnitude of the symmetric ambipolar conduction by changing s from 0 to to 1. The results are reported in Table 7. For all the considered digital cells the power consumption significantly increases when s is increased. In particular, it dramatically increases of around one order of magnitude when s is increased from 0 (no ambipolarity) to (suppressed ambipolarity) for the NAND and the NOR gates. Then by further increasing s from (suppressed ambipolarity) to 1 (full ambipolar device) only a slight increase occurs. This trend is well highlighted in Figure 11, where the increase in dissipated power from the case of to the case of is not appreciable.

Table 7.

Total power dissipation depending on the asymmetric ambipolarity for parameter s.

Figure 11.

Total power dissipation in function of the amount of symmetric ambipolarity (s value) for the NAND and the NOR gates.

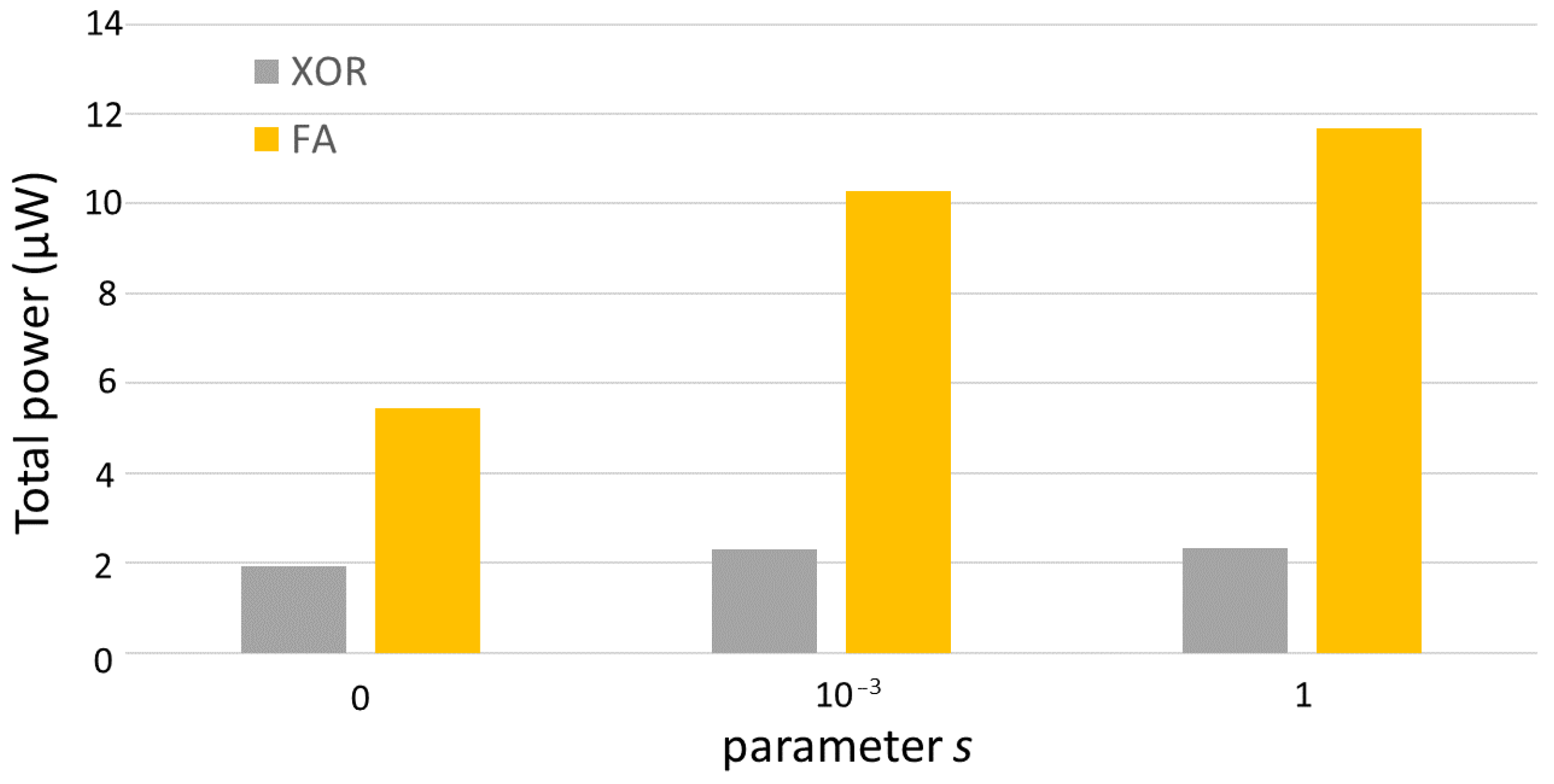

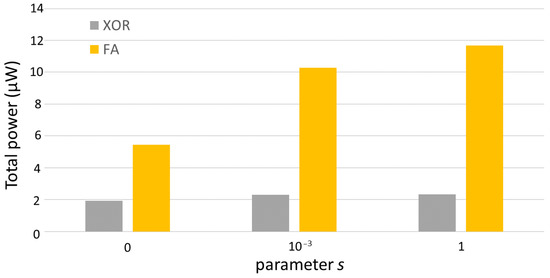

Similar considerations hold for more complex digital cells, namely the XOR and the FA. Nevertheless, we notice that for more complex cells, the increase in power consumption, due to s increase from 0 to , is much less marked than for the simpler NAND and NOR cells, as reported in Figure 12. Thus, we separately calculate the dissipated power sensitivity through Equation (4) for all the considered gates for the s increase from 0 to and for the s increase from and then to 1. We call the first and the latter and we report the result in Table 8. The sensitivity to ambipolar current magnitude is extremely larger for s passing from 0 to than for s passing from to 1. Even if more complex digital blocks present reduced sensitivity to s, the trend is confirmed. Because of the direct proportionality of to s (see Equation (2)) our results reflect in the following: an three orders of magnitude lower than values is still leading to important non-ideality power consumption and the dissipated power is very sensitive to , thus also small reductions of will result in large power consumption reduction.

Figure 12.

Total power dissipation in function of the amount of symmetric ambipolarity (s value) for the XOR and the FA digital circuits.

Table 8.

Total dissipated power percentage sensitivity to s parameter.

5. Conclusions

We investigated through Cadence Virtuoso SPICE simulations the effect of the symmetric and asymmetric ambipolar transcharacteristics in TFET-based complementary logic circuits. We modeled the asymmetric ambipolarity through a DC voltage generator on the TFET gates, to emulate the transcharacteristics shift, whereas we exploited the s parameter employed in Hao Lu Verilog-A model to account for the effect of the symmetric ambipolarity.

Our results show that symmetric ambipolarity has small effect on complementary logic circuit functioning, while asymmetric ambipolarity, if not kept under control, can lead to strong reduction of noise margins and evident behavioral failure.

Alongside behavioral analysis of circuits we also analyzed the effects of ambipolarity on dissipated power in digital circuits. In this case both the symmetric and asymmetric ambipolarity lead to relevant power performance deterioration. Asymmetric ambipolarity doubles the dissipated power for almost all the considered basic logic circuits, already for few tens of mV of transcharacteristic shift. We verified that the digital circuit dissipated power sensitivity to asymmetric ambipolarity increases with system complexity. In the case of symmetric ambipolarity, the dissipated power sensitivity to is extremely high for small variations of when it is order of magnitudes lower than the , whereas the system is less sensible to variations when approaches values. Therefore, even small reductions in can significantly reduce the dissipated power in complementary TFET digital circuits.

We believe our work to clarify the effects of ambipolar conduction on logic failure and power performance of complementary digital circuits based on TFET technology. Moreover, we believe it to motivate future technological efforts to further suppress the ambipolar current in TFETs and to keep under control the TFET transcharacteristic shift due to inaccurate gate engineering and fabrication process variations.

Author Contributions

Conceptualization, G.P., M.V., C.E.S., F.M. and Y.A.; methodology, R.A.C., F.M. and C.E.S.; software/simulations, R.A.C.; formal analysis, C.E.S. and F.M.; investigation, R.A.C., C.E.S. and F.M.; resources, M.R.R. and M.V.; data curation, R.A.C.; writing—original draft preparation, F.M. and C.E.S.; writing—review and editing, Y.A., G.P. and M.V.; visualization, C.E.S. and F.M.; supervision, G.P., M.V., F.M., C.E.S. and Y.A.; project administration, Y.A., G.P., M.V. and M.R.R.; internal funding acquisition, G.P. and M.R.R. All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

All the needed data are reported in the article.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Taur, Y.; Ning, T.H. Fundamentals of Modern VLSI Devices, 2nd ed.; Cambridge University Press: Cambridge, UK, 2009. [Google Scholar] [CrossRef]

- Roy, K.; Prasad, S. Low-Power Cmos Vlsi Circuit Design; Wiley India Pvt. Ltd.: New Delhi, India, 2009. [Google Scholar]

- Shafique, M.; Garg, S.; Henkel, J.; Marculescu, D. The EDA Challenges in the Dark Silicon Era: Temperature, Reliability, and Variability Perspectives. In Proceedings of the 51st Annual Design Automation Conference, San Francisco, CA, USA, 1–5 June 2014; Association for Computing Machinery: New York, NY, USA, 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 2011, 479, 329–337. [Google Scholar] [CrossRef] [PubMed]

- Seabaugh, A.C.; Zhang, Q. Low-Voltage Tunnel Transistors for Beyond CMOS Logic. Proc. IEEE 2010, 98, 2095–2110. [Google Scholar] [CrossRef]

- International Roadmap for Devices and Systems—Executive Report; IEEE: Piscataway, NJ, USA, 2021.

- Aswathy, M.; Biju, N.M.; Komaragiri, R. Comparison of a 30nm Tunnel Field Effect Transistor and CMOS Inverter Characteristics. In Proceedings of the 2013 Third International Conference on Advances in Computing and Communications, Cochin, India, 29–31 August 2013; pp. 149–152. [Google Scholar]

- Núñez, J.; Avedillo, M.J. Comparison of TFETs and CMOS Using Optimal Design Points for Power–Speed Tradeoffs. IEEE Trans. Nanotechnol. 2017, 16, 83–89. [Google Scholar] [CrossRef]

- Rendón, M.; Cao, C.; Landázuri, K.; Garzón, E.; Prócel, L.M.; Taco, R. Performance Benchmarking of TFET and FinFET Digital Circuits from a Synthesis-Based Perspective. Electronics 2022, 11, 632. [Google Scholar] [CrossRef]

- Strangio, S.; Settino, F.; Palestri, P.; Lanuzza, M.; Crupi, F.; Esseni, D.; Selmi, L. Digital and analog TFET circuits: Design and benchmark. Solid-State Electron. 2018, 146, 50–65. [Google Scholar] [CrossRef]

- Strangio, S.; Palestri, P.; Lanuzza, M.; Crupi, F.; Esseni, D.; Selmi, L. Assessment of InAs/AlGaSb Tunnel-FET Virtual Technology Platform for Low-Power Digital Circuits. IEEE Trans. Electron Devices 2016, 63, 2749–2756. [Google Scholar] [CrossRef]

- Lu, H.; Paletti, P.; Li, W.; Fay, P.; Ytterdal, T.; Seabaugh, A. Tunnel FET Analog Benchmarking and Circuit Design. IEEE J. Explor.—Solid-State Comput. Devices Circuits 2018, 4, 19–25. [Google Scholar] [CrossRef]

- Knoll, L.; Zhao, Q.T.; Nichau, A.; Trellenkamp, S.; Richter, S.; Schäfer, A.; Esseni, D.; Selmi, L.; Bourdelle, K.; Mantl, S. Inverters With Strained Si Nanowire Complementary Tunnel Field-Effect Transistors. IEEE Electron Device Lett. 2013, 34, 813–815. [Google Scholar] [CrossRef]

- Tomioka, K.; Yoshimura, M.; Fukui, T. Steep-slope tunnel field-effect transistors using III–V nanowire/Si heterojunction. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 47–48. [Google Scholar] [CrossRef]

- Bhuwalka, K.; Schulze, J.; Eisele, I. Scaling the vertical tunnel FET with tunnel bandgap modulation and gate workfunction engineering. IEEE Trans. Electron Devices 2005, 52, 909–917. [Google Scholar] [CrossRef]

- Boucart, K. Double-Gate Tunnel FET with High-κ Gate Dielectric; IEEE: Piscataway, NJ, USA, 2008. [Google Scholar]

- Toh, E.H.; Wang, G.H.; Samudra, G.; Yeo, Y.C. Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. Appl. Phys. Lett. 2007, 90, 263507. [Google Scholar] [CrossRef]

- Lu, H.; Seabaugh, A. Tunnel Field-Effect Transistors: State-of-the-Art. IEEE J. Electron Devices Soc. 2014, 2, 44–49. [Google Scholar] [CrossRef]

- Lin, Z.; Chen, P.; Ye, L.; Yan, X.; Dong, L.; Zhang, S.; Yang, Z.; Peng, C.; Wu, X.; Chen, J. Challenges and Solutions of the TFET Circuit Design. IEEE Trans. Circuits Syst. Regul. Pap. 2020, 67, 4918–4931. [Google Scholar] [CrossRef]

- Mamidala, J.; Vishnoi, R.; Pandey, P. Tunnel Field-Effect Transistors (TFET): Modelling and Simulation; Wiley: Hoboken, NJ, USA, 2016. [Google Scholar]

- Saurabh, S.; Kumar, M. Fundamentals of Tunnel Field-Effect Transistors; CRC Press: Boca Raton, FL, USA; Taylor & Francis Group: Abingdon, UK, 2016. [Google Scholar]

- Pasupathy, K.R.; Manivannan, T.S.; Lakshminarayanan, G. A Review of Engineering Techniques to Suppress Ambipolarity in Tunnel FET. Silicon 2022, 14, 1887–1894. [Google Scholar] [CrossRef]

- Hraziia; Vladimirescu, A.; Amara, A.; Anghel, C. An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid State Electron. 2012, 70, 67–72. [Google Scholar] [CrossRef]

- Nigam, K.; Kondekar, P.; Sharma, D. Approach for ambipolar behaviour suppression in tunnel FET by workfunction engineering. Micro Nano Lett. 2016, 11, 460–464. [Google Scholar] [CrossRef]

- Zhou, G.; Lu, Y.; Li, R.; Zhang, Q.; Hwang, W.; Liu, Q.; Vasen, T.; Chen, C.; Zhu, H.; Kuo, J.M.; et al. Vertical InGaAs/InP tunnel FETs with tunneling normal to the gate. EEE Electron Device Lett. 2011, 32, 1516–1518. [Google Scholar] [CrossRef]

- Lu, H.; Esseni, D.; Seabaugh, A. Universal analytic model for tunnel FET circuit simulation. Solid-State Electron. 2015, 108, 110–117. [Google Scholar] [CrossRef]

- Avci, U.E.; Morris, D.H.; Hasan, S.; Kotlyar, R.; Kim, R.; Rios, R.; Nikonov, D.E.; Young, I.A. Energy efficiency comparison of nanowire heterojunction TFET and Si MOSFET at Lg = 13nm, including P-TFET and variation considerations. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 33.4.1–33.4.4. [Google Scholar] [CrossRef]

- Morris, D.H.; Avci, U.E.; Rios, R.; Young, I.A. Design of Low Voltage Tunneling-FET Logic Circuits Considering Asymmetric Conduction Characteristics. IEEE J. Emerg. Sel. Top. Circuits Syst. 2014, 4, 380–388. [Google Scholar] [CrossRef]

- Lee, C.S.; Pop, E.; Franklin, A.D.; Haensch, W.; Wong, H.S.P. A Compact Virtual-Source Model for Carbon Nanotube FETs in the Sub-10-nm Regime—Part I: Intrinsic Elements. IEEE Trans. Electron Devices 2015, 62, 3061–3069. [Google Scholar] [CrossRef]

- Liu, H.; Saripalli, V.; Narayanan, V.; Datta, S. III-V Tunnel FET Model; nanoHUB: West Lafayette IN, USA, 2015. [Google Scholar] [CrossRef]

- Mo, F.; Spano, C.E.; Ardesi, Y.; Piccinini, G.; Graziano, M. Beyond-CMOS Artificial Neuron: A Simulation- Based Exploration of the Molecular-FET. IEEE Trans. Nanotechnol. 2021, 20, 903–911. [Google Scholar] [CrossRef]

- Hussain, I.; Riente, F.; Roch, M.R.; Piccinini, G.; Graziano, M. Performance analysis of transistor-based circuits through TAMAMS Web: From bulk to molecular devices. In Proceedings of the 2016 5th International Conference on Electronic Devices, Systems and Applications (ICEDSA), Ras Al Khaimah, United Arab Emirates, 6–8 December 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Lu, Y.; Zhou, G.; Li, R.; Liu, Q.; Zhang, Q.; Vasen, T.; Chae, S.D.; Kosel, T.; Wistey, M.; Xing, H.; et al. Performance of AlGaSb/InAs TFETs with gate electric field and tunneling direction aligned. IEEE Electron Device Lett. 2012, 33, 655–657. [Google Scholar] [CrossRef]

- Choi, Y.K.; Lindert, N.; Xuan, P.; Tang, S.; Ha, D.; Anderson, E.; King, T.J.; Bokor, J.; Hu, C. Sub-20 nm CMOS FinFET technologies. In Proceedings of the International Electron Devices Meeting, Technical Digest (Cat. No.01CH37224), Washington, DC, USA, 2–5 December 2001; pp. 19.1.1–19.1.4. [Google Scholar] [CrossRef]

- Agrawal, A.; Chouksey, S.; Rachmady, W.; Vishwanath, S.; Ghose, S.; Mehta, M.; Torres, J.; Oni, A.; Weng, X.; Li, H.; et al. Gate-All-Around Strained Si0.4Ge0.6 Nanosheet PMOS on Strain Relaxed Buffer for High Performance Low Power Logic Application. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 2.2.1–2.2.4. [Google Scholar] [CrossRef]

- Zhang, J.; Frougier, J.; Greene, A.; Miao, X.; Yu, L.; Vega, R.; Montanini, P.; Durfee, C.; Gaul, A.; Pancharatnam, S.; et al. Full Bottom Dielectric Isolation to Enable Stacked Nanosheet Transistor for Low Power and High Performance Applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.6.1–11.6.4. [Google Scholar] [CrossRef]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T230–T231. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).