Physico-Chemical Origins of Electrical Characteristics and Instabilities in Solution-Processed ZnSnO Thin-Film Transistors

Abstract

1. Introduction

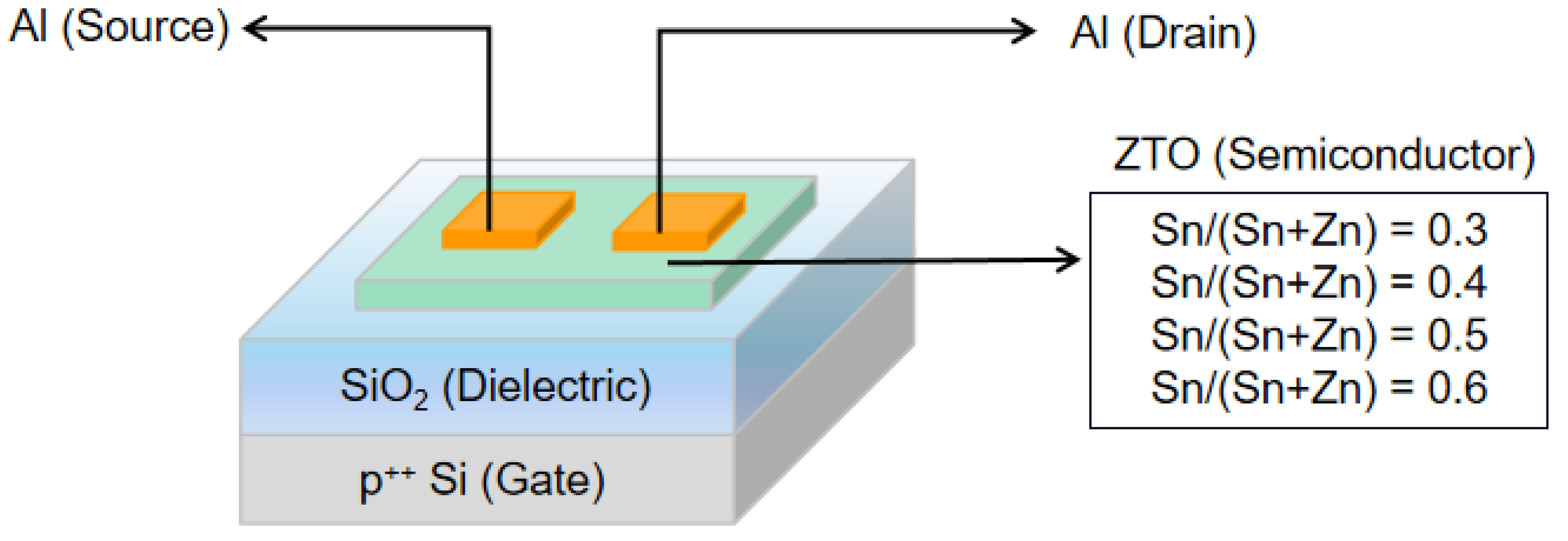

2. Materials and Methods

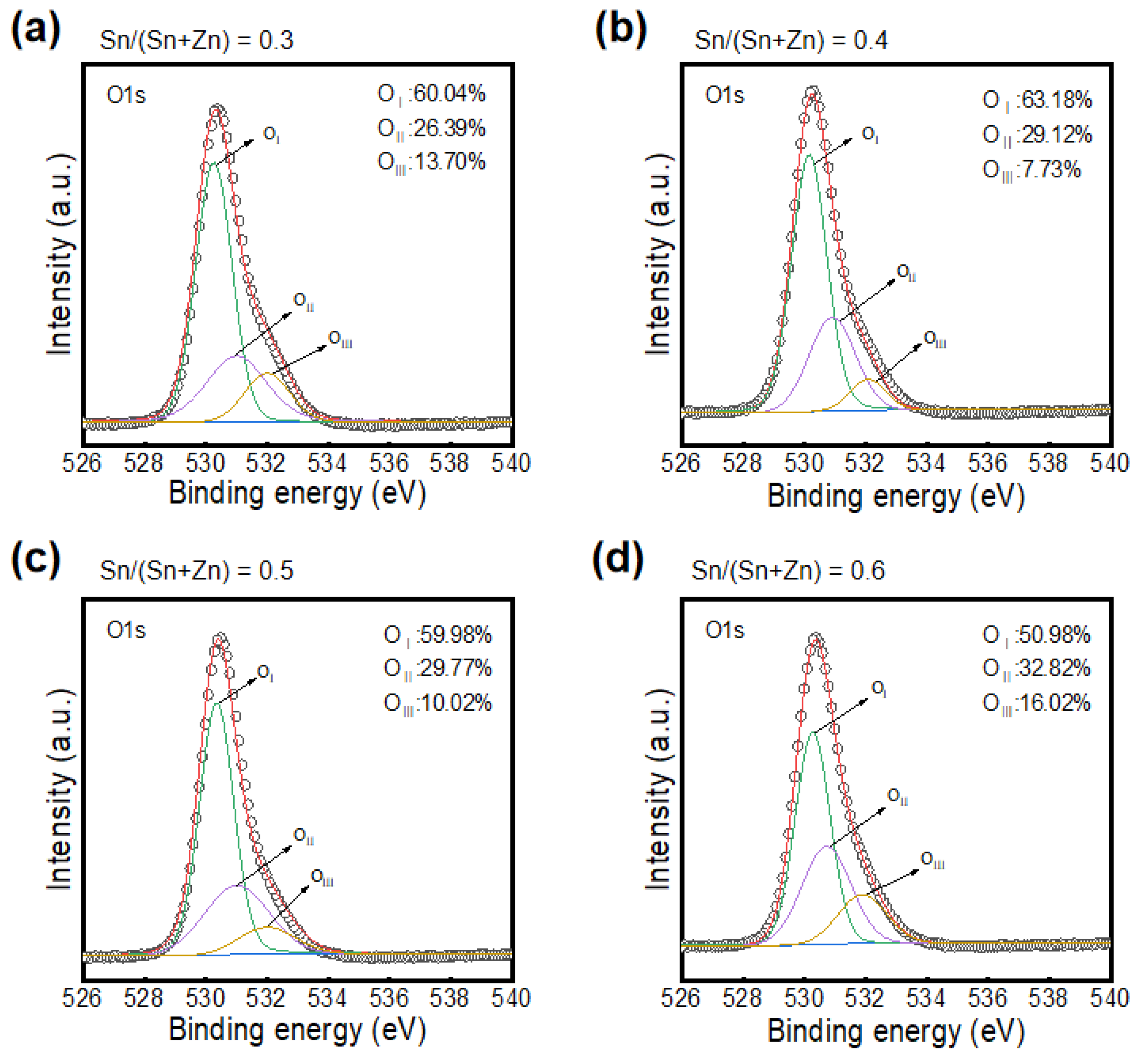

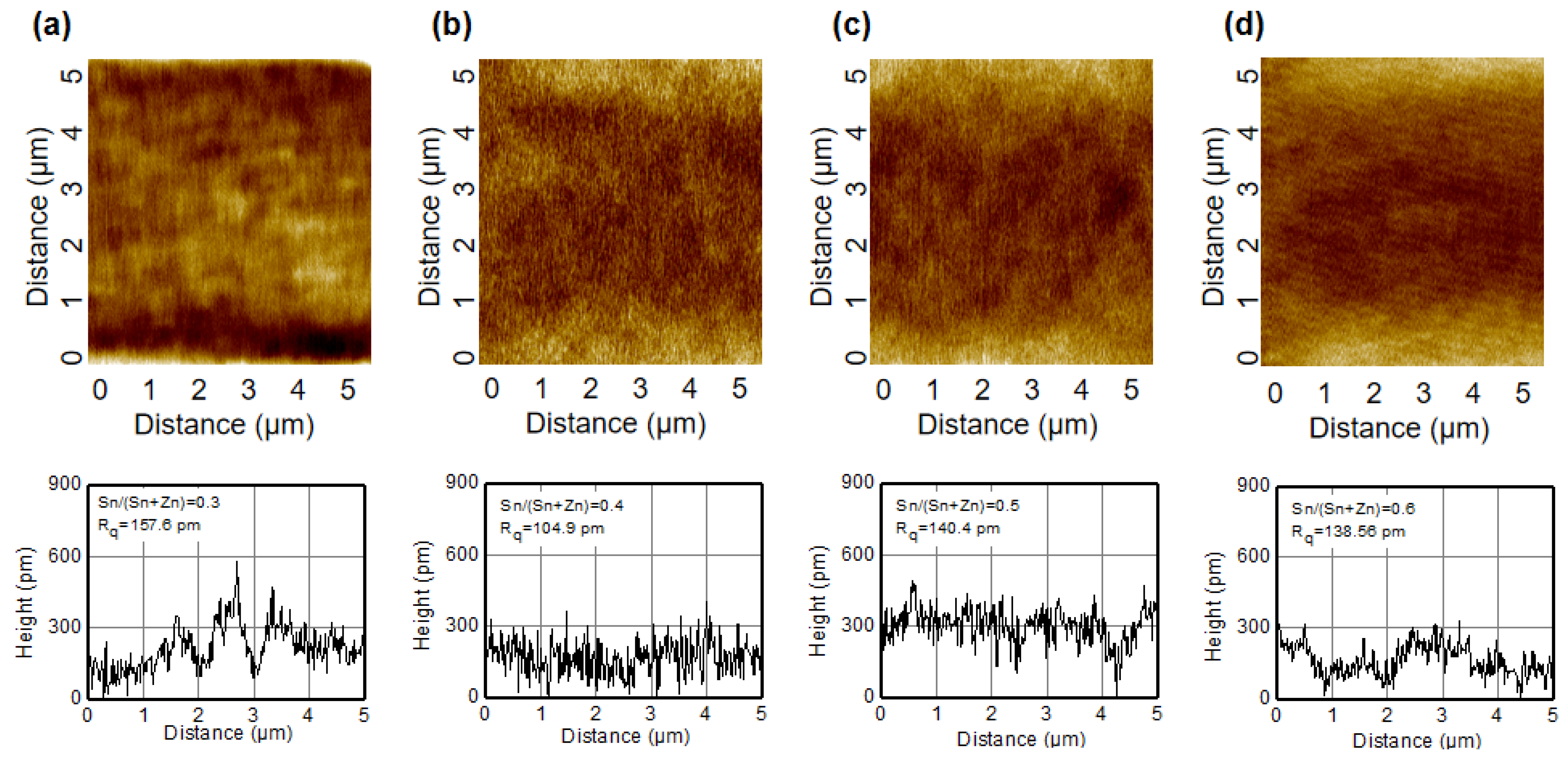

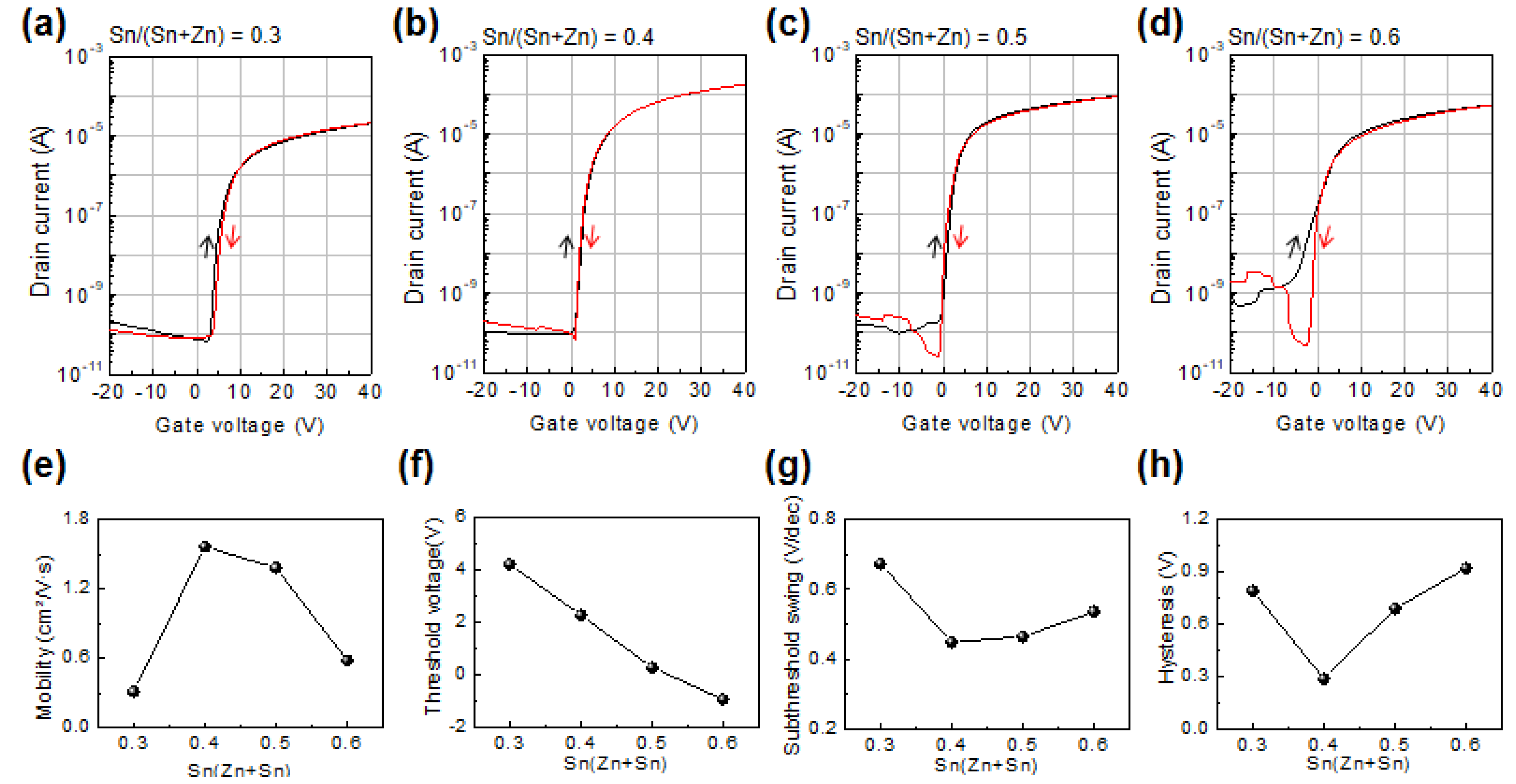

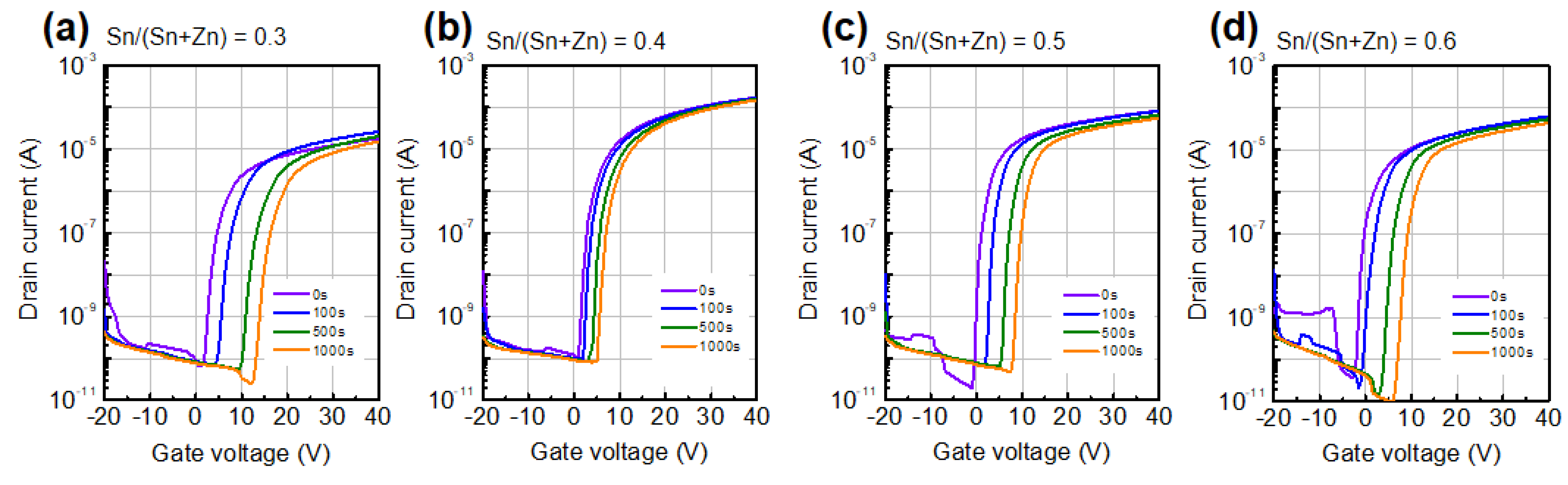

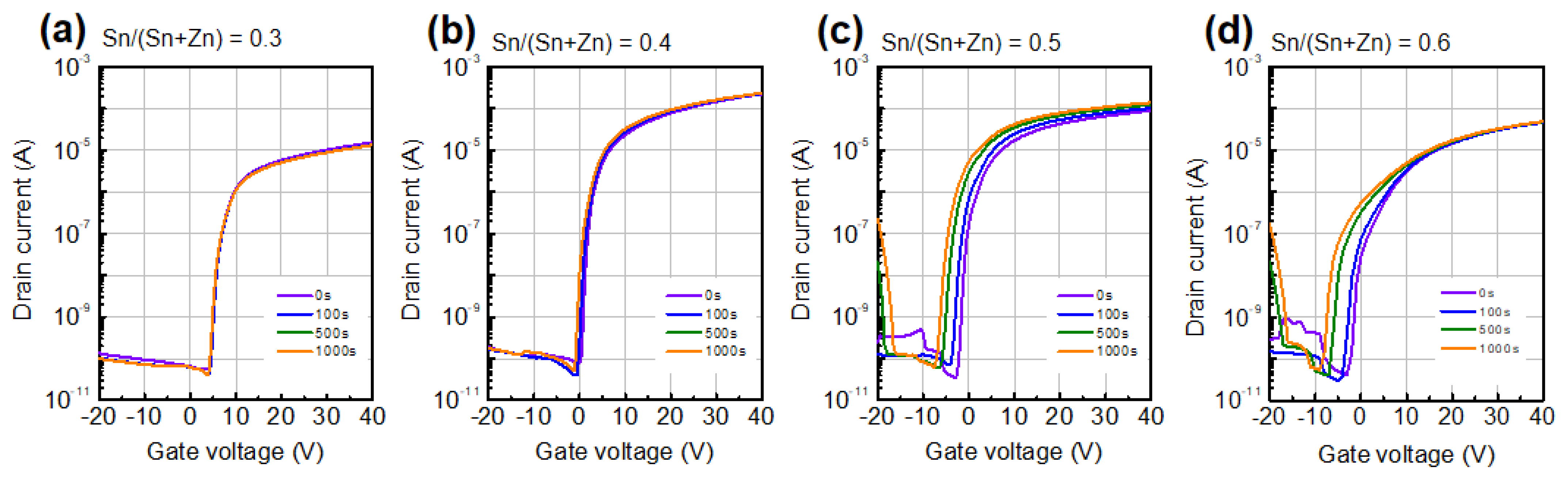

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Jeong, J.K. The status and perspectives of metal oxide thin-film transistors for active matrix flexible displays. Semicond. Sci. Technol. 2011, 26, 034008. [Google Scholar] [CrossRef]

- Shao, F.; Wan, Q. Recent progress on jet printing of oxide-based thin film transistors. J. Phys. D Appl. Phys. 2019, 52, 143002. [Google Scholar] [CrossRef]

- Park, J.W.; Kang, B.H.; Kim, H.J.; Zhang, Z. A Review of Low-Temperature Solution-processed Metal Oxide Thin-Film Transistors for Flexible Electronics. Adv. Funct. Mater. 2021, 30, 1904632. [Google Scholar] [CrossRef]

- Kamiya, T.; Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater. 2010, 2, 15–22. [Google Scholar] [CrossRef]

- Lee, S.Y. Comprehensive Review on Amorphous Oxide Semiconductor Thin Film Transistor. Trans. Electr. Electron. Mater. 2020, 21, 235–248. [Google Scholar] [CrossRef]

- Nomura, K.; Takagi, A.; Kamiya, T.; Ohta, H.; Hirano, M.; Hosono, H. Amorphous Oxide Semiconductors for High Performance Flexible Thin-Film Transistors. Jpn. J. Appl. Phys. 2006, 45, 4303. [Google Scholar] [CrossRef]

- Kumomi, H.; Kamiya, T.; Hosono, H. Advances in Oxide Thin-Film Transistors in Recent Decade and Their Future. ECS Trans. 2015, 67, 3. [Google Scholar] [CrossRef]

- Lee, D.-H.; Chang, Y.-J.; Herman, G.S.; Chang, C.-H. A General Route to Printable High-Mobility Transparent Amorphous Oxide Semiconductors. Adv. Mater. 2007, 19, 843–847. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef]

- Lee, W.-Y.; Lee, H.; Ha, S.; Lee, C.; Bae, J.-H.; Kang, I.-M.; Kim, K.; Jang, J. Effect of Mg doping on the electrical performance of a Sol-Gel-Processed SnO2 thin-film transistor. Electronics 2020, 9, 523. [Google Scholar] [CrossRef]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor thin-film Transistors: A Review of Recent Advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef] [PubMed]

- Zhu, Y.; He, Y.; Jiang, S.; Zhu, L.; Chen, C.; Wan, Q. Indium–gallium–zinc–oxide thin-film transistors: Materials, devices, and application. J. Semicond. 2021, 42, 031101. [Google Scholar] [CrossRef]

- Kim, D.-K.; Park, J.; Vincent, P.; Park, J.-I.; Jang, J.; Kang, I.M.; Kim, H.; Lang, P.; Bae, J.-H. Numerical Design of Carrier Transporting Layer in Top-Gate InGaZnO Thin-Film Transistors for Controlling Potential Energy. J. Nanosci. Nanotechnol. 2021, 21, 3847–3852. [Google Scholar] [CrossRef] [PubMed]

- Park, J.-I.; Kim, D.-K.; Lee, H.; Jang, J.; Park, J.; Kim, H.; Lang, P.; Bae, J.-H. High performance of solution-processed SnO2 thin-film transistors by promotion of photo-exposure time-dependent carrier transport during the pre-annealing stage. Semicond. Sci. Technol. 2020, 35, 065019. [Google Scholar] [CrossRef]

- Allemang, C.R.; Cho, T.H.; Trejo, O.; Ravan, S.; Rodríguez, R.E.; Dasgupta, N.P.; Peterson, R.L. High-Performance Zinc Tin Oxide TFTs with Active Layers Deposited by Atomic Layer Deposition. Adv. Electron. Mater. 2020, 6, 2000195. [Google Scholar] [CrossRef]

- Park, J.S.; Maeng, W.-J.; Kim, H.-S.; Park, J.-S. Review of recent developments in amorphous oxide semiconductor thin-film transistor devices. Thin Solid Films 2021, 520, 1679–1693. [Google Scholar] [CrossRef]

- Sodhani, A.; Goswami, R.; Kandpal, K. Design of Pixel Circuit Using a IGZO TFTs to Enhance Uniformity of AMOLED Displays by Threshold Voltage Compensation. Arab. J. Sci. Eng. 2021, 46, 9663–9672. [Google Scholar] [CrossRef]

- Moffitt, S.L.; Stallings, K.L.; Falduto, A.F.; Lee, W.; Buchholz, D.B.; Wang, B.; Ma, Q.; Chang, R.P.H.; Marks, T.J.; Bedzyk, M.J. Processing, Structure, and Transistor Performance: Combustion versus Pulsed Laser Growth of Amorphous Oxides. ACS Appl. Electron. Mater. 2019, 1, 548–557. [Google Scholar] [CrossRef]

- Kim, S.J.; Yoon, S.; Kim, H.J. Review of solution-processed oxide thin-film transistors. Jpn. J. Appl. Phys. 2014, 53, 02BA02. [Google Scholar] [CrossRef]

- Carlos, E.; Branquinho, R.; Barquinha, P.; Martins, R.; Fortunato, E. Chapter 18—New strategies toward high-performance and low-temperature processing of solution-based metal oxide TFTs. In Chemical Solution Synthesis for Materials Design and Thin Film Device Applications; Elsevier: Amsterdam, The Netherlands, 2021; pp. 585–621. [Google Scholar]

- Jeon, S.-H.; Wang, Z.; Seo, K.-H.; Feng, J.; Zhang, X.; Park, J.; Bae, J.-H. Importance of Solvent Evaporation Temperature in Pre-Annealing Stage for Solution-Processed Zinc Tin Oxide Thin-Film Transistors. Electronics 2022, 11, 2822. [Google Scholar] [CrossRef]

- Zhang, Q.; Xia, G.; Li, L.; Xia, W.; Gong, H.; Wang, S. High-performance Zinc-Tin-Oxide thin film transistors based on environment friendly solution process. Curr. Appl. Phys. 2019, 19, 174–181. [Google Scholar] [CrossRef]

- Hwang, Y.-J.; Kim D.-K.; Jeon, S.-H.; Wang, Z.; Park, J.; Lee, S.-H.; Jang, J.; Kang, I.M.; Bae, J.-H. Importance of Structural Relaxation on the Electrical Characteristics and Bias Stability of Solution-Processed ZnSnO Thin-Film Transistors. Nanomaterials 2022, 12, 3097. [Google Scholar] [CrossRef] [PubMed]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Kamiya, T.; Nomura, K.; Hosono, H. Origins of High Mobility and Low Operation Voltage of Amorphous Oxide TFTs: Electronic Structure, Electron Transport, Defects and Doping. J. Disp. Technol. 2009, 5, 273–288. [Google Scholar] [CrossRef]

- Yao, J.; Xu, N.; Deng, S.; Chen, J.; She, J.; Shieh, H.-P.D.; Liu, P.-T.; Huang, Y.-P. Electrical and Photosensitive Characteristics of a-IGZO TFTs Related to Oxygen Vacancy. IEEE Trans. Electron Devices 2011, 58, 1121–1126. [Google Scholar]

- Kim, J.-H.; Park, E.-K.; Kim, M.S.; Cho, H.J.; Lee, D.-H.; Kim, J.-H.; Khang, Y.; Park, K.; Kim, Y.-S. Bias and illumination instability analysis of solution-processed a-InGaZnO thin-film transistors with different component ratios. Thin Solid Films 2018, 645, 154–159. [Google Scholar] [CrossRef]

- Jain, V.K.; Kumar, P.; Kumar, M.; Jain, P.; Bhandari, D.; Vijay, Y.K. Study of post annealing influence on structural, chemical and electrical properties of ZTO thin films. J. Alloys Compd. 2011, 509, 3541–3546. [Google Scholar] [CrossRef]

- Huang, C.-Y.; Peng, T.-Y.; Hsieh, W.-T. Realization of a Self-Powered InGaZnO MSM UV Photodetector Using Localized Surface Fluorine Plasma Treatment. ACS Appl. Electron. Mater. 2022, 2, 2976–2983. [Google Scholar] [CrossRef]

- Wang, W.; He, G.; Wang, L.; Zhang, X.X.Y. Solution-Driven HfLaOx-Based Gate Dielectrics for Thin Film Transistors and Unipolar Inverters. IEEE. Trans. Electron Devices 2021, 68, 4437–4443. [Google Scholar] [CrossRef]

- Lee, E.; Kim, T.H.; Lee, S.W.; Kim, J.H.; Kim, J.; Jeong, T.G.; Ahn, J.-H.; Cho, B. Improved electrical performance of a sol-gel IGZO transistor with high-k Al2O3 gate dielectric achieved by post annealing. Nano Converg. 2019, 6, 24. [Google Scholar] [CrossRef]

- Kim, K.-S.; Lee, S.-W.; Oh, S.-M.; Cho, W.-J. Development of annealing process for solution-derived high performance InGaZnO thin-film transistors. Mater. Sci. Eng. B Solid-State Mater. Adv. Technol. 2013, 178, 811–815. [Google Scholar] [CrossRef]

- Padma, N.; Sawant, S.N.; Sen, S. Study on post-deposition annealing influenced contribution of hole and electron trapping to threshold voltage stability in organic field effect transistors. Mater. Sci. Semicond. Process. 2015, 30, 18–24. [Google Scholar]

- Kim, Y.J.; Oh, S.; Yang, B.S.; Han, S.J.; Lee, H.W.; Kim, H.J.; Jeong, J.K.; Hwang, C.S.; Kim, H.J. Impact of the cation composition on the electrical performance of solution-processed zinc tin oxide thin-film transistors. ACS Appl. Mater. Interfaces 2014, 6, 14026–14036. [Google Scholar] [CrossRef] [PubMed]

- Chowdhury, M.D.H.; Migliorato, P.; Jang, J. Time-temperature dependence of positive gate bias stress and recovery in amorphous indium-gallium-zinc-oxide thin-film-transistors. Appl. Phys. Lett. 2011, 98, 153511. [Google Scholar] [CrossRef]

- Baek, J.H.; Seol, H.; Cho, K.; Yang, H.; Jeong, J.K. Comparative Study of Antimony Doping Effects on the Performance of Solution-Processed ZIO and ZTO Field-Effect Transistors. ACS Appl. Mater. Interfaces 2017, 9, 10904–10913. [Google Scholar] [CrossRef]

- Qin, H.-M.; Yu, G.; Lu, H.; Wu, C.-F.; Tang, L.-F.; Zhou, D.; Ren, F.-F.; Zhang, R.; Zheng, Y.-L.; Huang, X.-M. Temperature-dependent bias-stress-induced electrical instability of amorphous indium-gallium-zinc-oxide thin-film transistors. Chin. Phys. B 2015, 24, 077307. [Google Scholar] [CrossRef]

- Nomura, K.; Kamiya, T.; Hosono, H. Interface and bulk effects for bias—Light-illumination instability in amorphous-In-Ga-Zn-O thin-film transistors. J. Soc. Inf. Disp. 2010, 18, 789–795. [Google Scholar] [CrossRef]

- Kim, Y.J.; Yang, B.S.; Oh, S.; Han, S.J.; Lee, H.W.; Heo, J.; Jeong, J.K.; Kim, H.J. Photobias Instability of High Performance Solution Processed Amorphous Zinc Tin Oxide Transistors. ACS Appl. Mater. Interfaces 2013, 5, 3255–3261. [Google Scholar] [CrossRef]

- Noh, H.-K.; Chang, K.J.; Ryu, B.; Lee, W.-J. Electronic structure of oxygen-vacancy defects in amorphous In-Ga-Zn-O semiconductors. Phys. Rev. B 2011, 84, 115205. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Z.; Jeon, S.-H.; Hwang, Y.-J.; Lee, S.-H.; Jang, J.; Kang, I.M.; Kim, D.-K.; Bae, J.-H. Physico-Chemical Origins of Electrical Characteristics and Instabilities in Solution-Processed ZnSnO Thin-Film Transistors. Coatings 2022, 12, 1534. https://doi.org/10.3390/coatings12101534

Wang Z, Jeon S-H, Hwang Y-J, Lee S-H, Jang J, Kang IM, Kim D-K, Bae J-H. Physico-Chemical Origins of Electrical Characteristics and Instabilities in Solution-Processed ZnSnO Thin-Film Transistors. Coatings. 2022; 12(10):1534. https://doi.org/10.3390/coatings12101534

Chicago/Turabian StyleWang, Ziyuan, Sang-Hwa Jeon, Yu-Jin Hwang, Sin-Hyung Lee, Jaewon Jang, In Man Kang, Do-Kyung Kim, and Jin-Hyuk Bae. 2022. "Physico-Chemical Origins of Electrical Characteristics and Instabilities in Solution-Processed ZnSnO Thin-Film Transistors" Coatings 12, no. 10: 1534. https://doi.org/10.3390/coatings12101534

APA StyleWang, Z., Jeon, S.-H., Hwang, Y.-J., Lee, S.-H., Jang, J., Kang, I. M., Kim, D.-K., & Bae, J.-H. (2022). Physico-Chemical Origins of Electrical Characteristics and Instabilities in Solution-Processed ZnSnO Thin-Film Transistors. Coatings, 12(10), 1534. https://doi.org/10.3390/coatings12101534