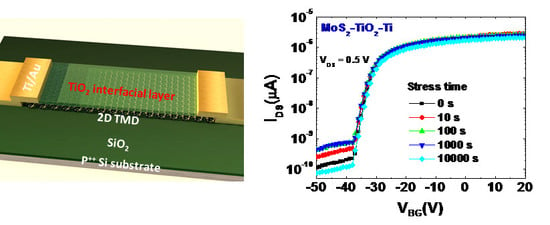

Improvement of the Bias Stress Stability in 2D MoS2 and WS2 Transistors with a TiO2 Interfacial Layer

Abstract

1. Introduction

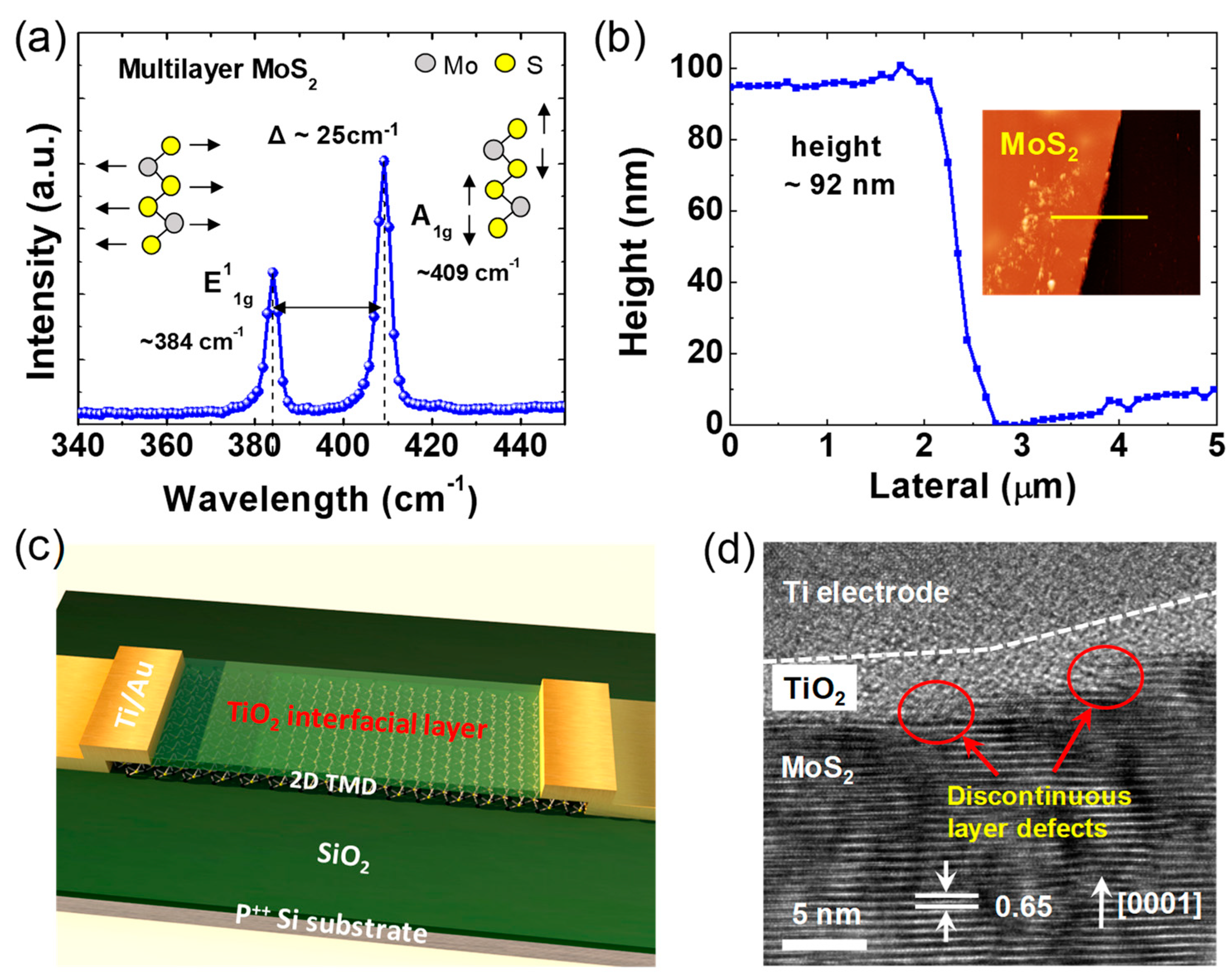

2. Materials and Methods

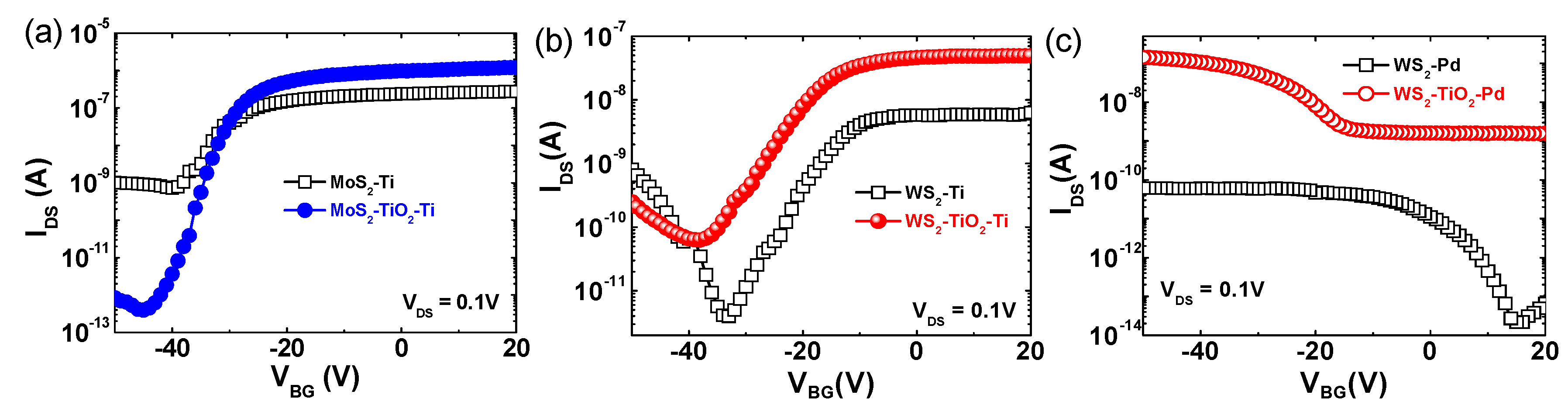

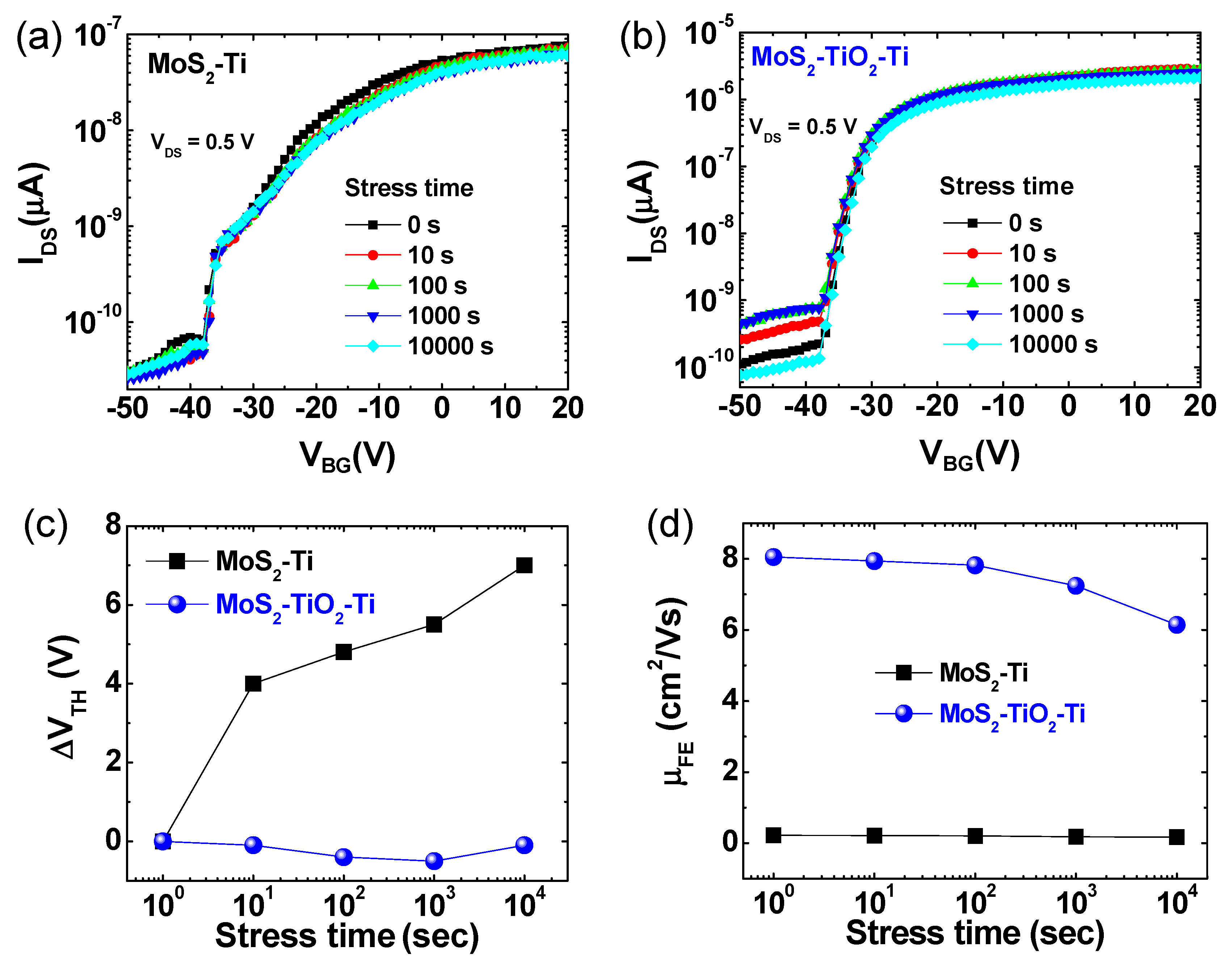

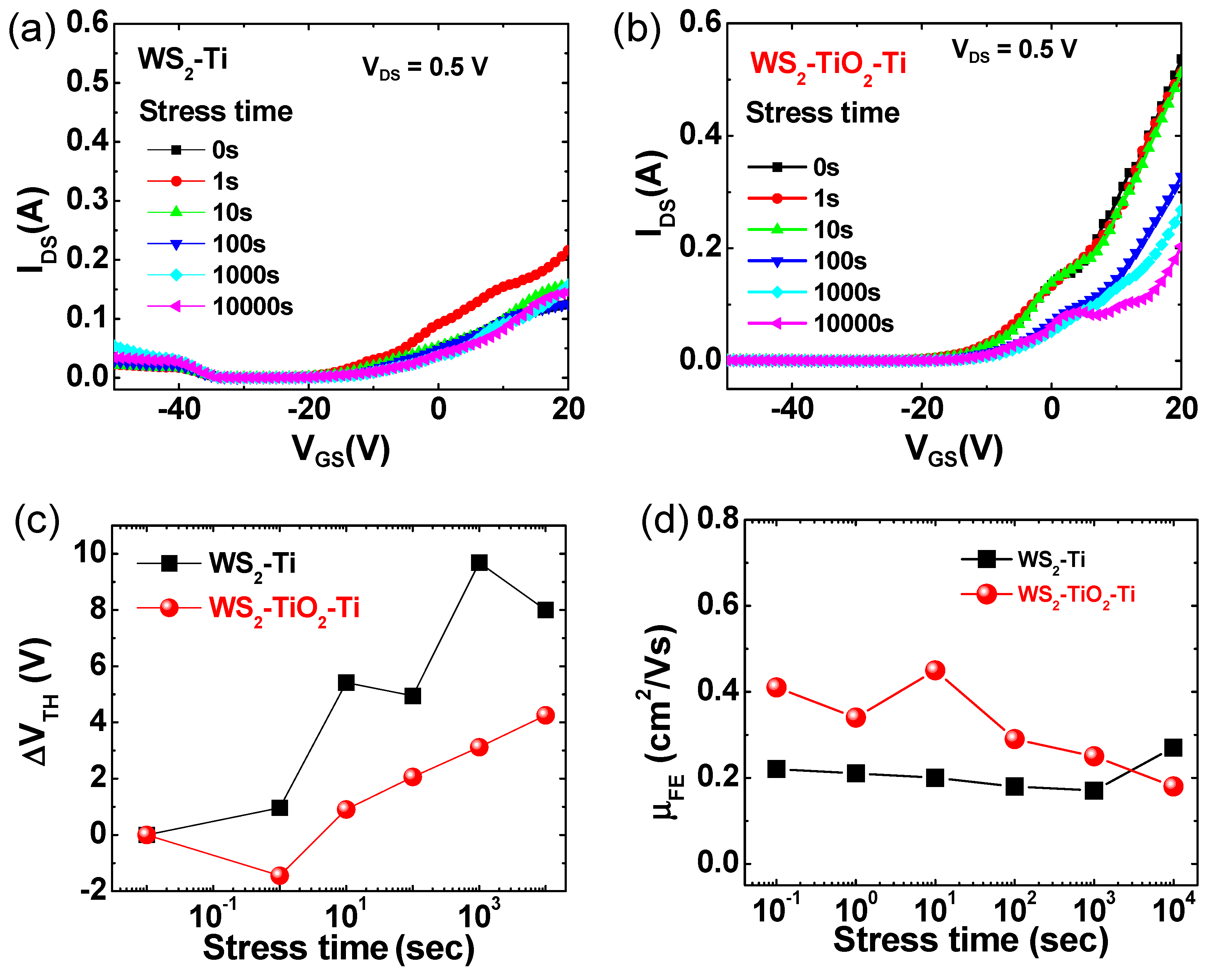

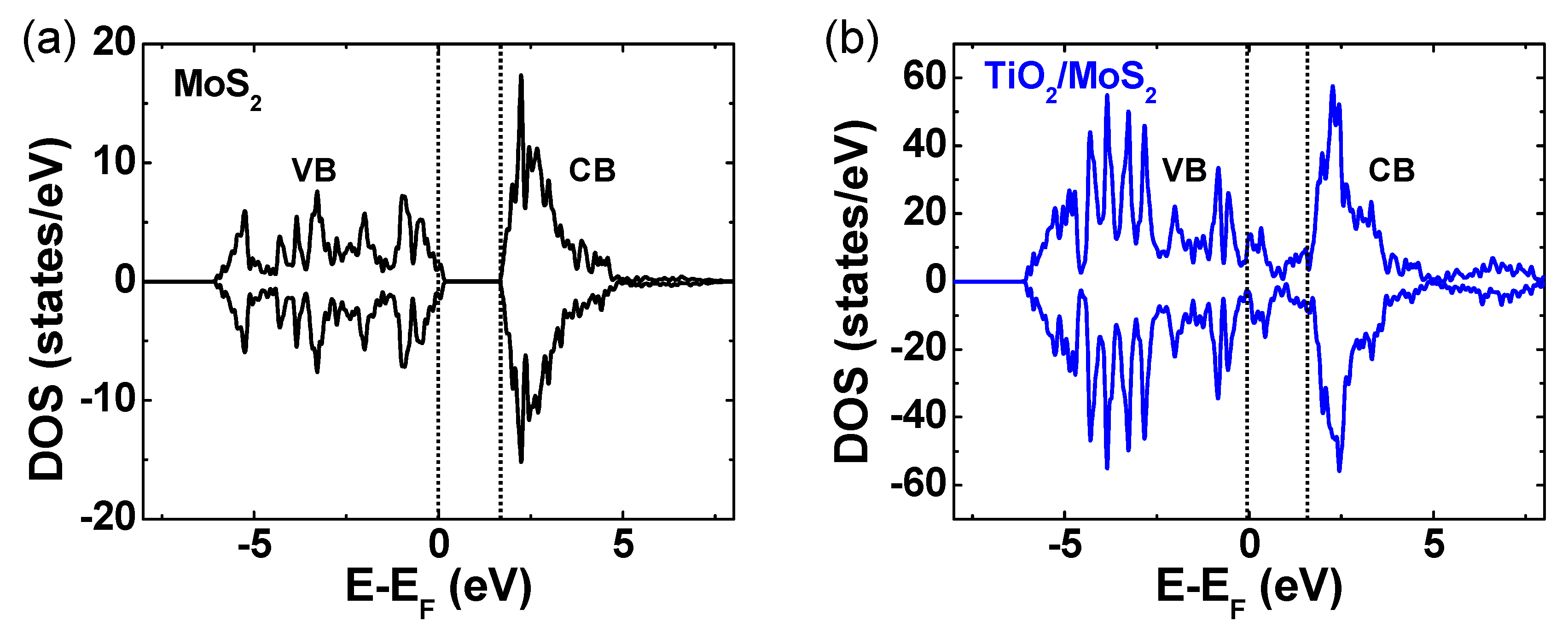

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Conflicts of Interest

References

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147–150. [Google Scholar] [CrossRef] [PubMed]

- Bertolazzi, S.; Brivio, J.; Kis, A. Stretching and Breaking of Ultrathin MoS2. ACS Nano 2011, 5, 9703–9709. [Google Scholar] [CrossRef] [PubMed]

- Yu, W.J.; Li, Z.; Zhou, H.; Chen, Y.; Wang, Y.; Huang, Y.; Duan, X. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nat. Mater. 2013, 12, 246–252. [Google Scholar] [CrossRef] [PubMed]

- Fang, H.; Tosun, M.; Seol, G.; Chang, T.C.; Takei, K.; Guo, J.; Javey, A. Degenerate n-Doping of Few-Layer Transition Metal Dichalcogenides by Potassium. Nano Lett. 2013, 13, 1991–1995. [Google Scholar] [CrossRef] [PubMed]

- Castellanos-Gomez, A.; Poot, M.; Steele, G.A.; van der Zant, H.S.J.; Agraït, N.; Rubio-Bollinger, G. Elastic Properties of Freely Suspended MoS2 Nanosheets. Adv. Mater. 2012, 24, 772–775. [Google Scholar] [CrossRef]

- Salvatore, G.A.; Münzenrieder, N.; Barraud, C.; Petti, L.; Zysset, C.; Büthe, L.; Ensslin, K.; Tröster, G. Fabrication and Transfer of Flexible Few-Layers MoS2 Thin Film Transistors to Any Arbitrary Substrate. ACS Nano 2013, 7, 8809–8815. [Google Scholar] [CrossRef]

- Li, H.; Yin, Z.; He, Q.; Li, H.; Huang, X.; Lu, G.; Fam, D.W.H.; Tok, A.I.Y.; Zhang, Q.; Zhang, H. Fabrication of Single- and Multilayer MoS2 Film-Based Field-Effect Transistors for Sensing NO at Room Temperature. Small 2012, 8, 63–67. [Google Scholar] [CrossRef]

- Radisavljevic, B.; Whitwick, M.B.; Kis, A. Integrated Circuits and Logic Operations Based on Single-Layer MoS2. ACS Nano 2011, 5, 9934–9938. [Google Scholar] [CrossRef]

- Li, H.; Lu, G.; Yin, Z.; He, Q.; Li, H.; Zhang, Q.; Zhang, H. Optical Identification of Single- and Few-Layer MoS2 Sheets. Small 2012, 8, 682–686. [Google Scholar] [CrossRef]

- Roy, T.; Tosun, M.; Cao, X.; Fang, H.; Lien, D.-H.; Zhao, P.; Chen, Y.-Z.; Chueh, Y.-L.; Guo, J.; Javey, A. Dual-Gated MoS2 /WSe2 van der Waals Tunnel Diodes and Transistors. ACS Nano 2015, 9, 2071–2079. [Google Scholar] [CrossRef]

- Wi, S.; Kim, H.; Chen, M.; Nam, H.; Guo, L.J.; Meyhofer, E.; Liang, X. Enhancement of Photovoltaic Response in Multilayer MoS2 Induced by Plasma Doping. ACS Nano 2014, 8, 5270–5281. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.; Konar, A.; Hwang, W.-S.; Lee, J.H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J.-B.; Choi, J.-Y.; et al. High-mobility and low-power thin-film transistors based on multilayer MoS2 crystals. Nat. Commun. 2012, 3, 1011. [Google Scholar] [CrossRef] [PubMed]

- Wang, H.; Yu, L.; Lee, Y.-H.; Shi, Y.; Hsu, A.; Chin, M.L.; Li, L.-J.; Dubey, M.; Kong, J.; Palacios, T. Integrated Circuits Based on Bilayer MoS2 Transistors. Nano Lett. 2012, 12, 4674–4680. [Google Scholar] [CrossRef] [PubMed]

- Jo, S.; Ubrig, N.; Berger, H.; Kuzmenko, A.B.; Morpurgo, A.F. Mono- and Bilayer WS2 Light-Emitting Transistors. Nano Lett. 2014, 14, 2019–2025. [Google Scholar] [CrossRef] [PubMed]

- Lee, H.S.; Min, S.-W.; Park, M.K.; Lee, Y.T.; Jeon, P.J.; Kim, J.H.; Ryu, S.; Im, S. MoS2 Nanosheets for Top-Gate Nonvolatile Memory Transistor Channel. Small 2012, 8, 3111–3115. [Google Scholar] [CrossRef] [PubMed]

- Kwon, J.; Ki Hong, Y.; Kwon, H.-J.; Jin Park, Y.; Yoo, B.; Kim, J.; Grigoropoulos, C.P.; Suk Oh, M.; Kim, S. Optically transparent thin-film transistors based on 2D multilayer MoS2 and indium zinc oxide electrodes. Nanotechnology 2015, 26, 035202. [Google Scholar] [CrossRef] [PubMed]

- Zhang, W.; Chiu, M.-H.; Chen, C.-H.; Chen, W.; Li, L.-J.; Wee, A.T.S. Role of Metal Contacts in High-Performance Phototransistors Based on WSe2 Monolayers. ACS Nano 2014, 8, 8653–8661. [Google Scholar] [CrossRef] [PubMed]

- Yin, Z.; Li, H.; Li, H.; Jiang, L.; Shi, Y.; Sun, Y.; Lu, G.; Zhang, Q.; Chen, X.; Zhang, H. Single-Layer MoS2 Phototransistors. ACS Nano 2012, 6, 74–80. [Google Scholar] [CrossRef] [PubMed]

- Park, J.; Kang, D.-H.; Kim, J.-K.; Park, J.-H.; Yu, H.-Y. Efficient Threshold Voltage Adjustment Technique by Dielectric Capping Effect on MoS2 Field-Effect Transistor. IEEE Electron Device Lett. 2017, 38, 1172–1175. [Google Scholar] [CrossRef]

- Zheng, H.M.; Gao, J.; Sun, S.M.; Ma, Q.; Wang, Y.P.; Zhu, B.; Liu, W.J.; Lu, H.L.; Ding, S.J.; Zhang, D.W. Effects of Al2O3 Capping and Post-Annealing on the Conduction Behavior in Few-Layer Black Phosphorus Field-Effect Transistors. IEEE J. Electron Devices Soc. 2018, 6, 320–324. [Google Scholar] [CrossRef]

- Agrawal, A.; Lin, J.; Zheng, B.; Sharma, S.; Chopra, S.; Wang, K.; Gelatos, A.; Mohney, S.; Datta, S. Barrier Height Reduction to 0.15eV and Contact Resistivity Reduction to 9.1×10−9 Ω-cm2 Using Ultrathin TiO2-x Interlayer between Metal and Silicon. In Proceedings of the 2013 Symposium on VLSI Technology, Kyoto, Japan, 11–14 June 2013. [Google Scholar]

- Yang, L.; Majumdar, K.; Liu, H.; Du, Y.; Wu, H.; Hatzistergos, M.; Hung, P.Y.; Tieckelmann, R.; Tsai, W.; Hobbs, C.; et al. Chloride Molecular Doping Technique on 2D Materials: WS2 and MoS2. Nano Lett. 2014, 14, 6275–6280. [Google Scholar] [CrossRef] [PubMed]

- Park, W.; Kim, Y.; Jung, U.; Yang, J.H.; Cho, C.; Kim, Y.J.; Hasan, S.M.N.; Kim, H.G.; Lee, H.B.R.; Lee, B.H. Complementary Unipolar WS2 Field-Effect Transistors Using Fermi-Level Depinning Layers. Adv. Electron. Mater. 2016, 2, 1500278. [Google Scholar] [CrossRef]

- Park, W.; Kim, Y.; Lee, S.K.; Jung, U.; Yang, J.H.; Cho, C.; Kim, Y.J.; Lim, S.K.; Hwang, I.S.; Lee, B.H. Contact resistance reduction using Fermi level de-pinning layer for MoS2 FETs. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; 2014; pp. 1–4. [Google Scholar]

- Agrawal, A.; Lin, J.; Barth, M.; White, R.; Zheng, B.; Chopra, S.; Gupta, S.; Wang, K.; Gelatos, J.; Mohney, S.E.; et al. Fermi level depinning and contact resistivity reduction using a reduced titania interlayer in n-silicon metal-insulator-semiconductor ohmic contacts. Appl. Phys. Lett. 2014, 104, 112101. [Google Scholar] [CrossRef]

- Das, S.; Chen, H.-Y.; Penumatcha, A.V.; Appenzeller, J. High Performance Multilayer MoS2 Transistors with Scandium Contacts. Nano Lett. 2013, 13, 100–105. [Google Scholar] [CrossRef]

- Noori, A.M.; Balseanu, M.; Boelen, P.; Cockburn, A.; Demuynck, S.; Felch, S.; Gandikota, S.; Gelatos, A.J.; Khandelwal, A.; Kittl, J.A.; et al. Manufacturable Processes for ≤ 32-nm-node CMOS Enhancement by Synchronous Optimization of Strain-Engineered Channel and External Parasitic Resistances. IEEE Trans. Electron Devices 2008, 55, 1259–1264. [Google Scholar] [CrossRef]

- Du, Y.; Liu, H.; Neal, A.T.; Si, M.; Ye, P.D. Molecular Doping of Multilayer MoS2 Field-Effect Transistors: Reduction in Sheet and Contact Resistances. IEEE Electron Device Lett. 2013, 34, 1328–1330. [Google Scholar] [CrossRef]

- Park, W.; Min, J.-W.; Shaikh, S.F.; Hussain, M.M. Stable MoS2 Field-Effect Transistors Using TiO2 Interfacial Layer at Metal/MoS2 Contact. Phys. Status Solidi A 2017, 214, 1700534. [Google Scholar] [CrossRef]

- Late, D.J.; Liu, B.; Matte, H.S.S.R.; Dravid, V.P.; Rao, C.N.R. Hysteresis in Single-Layer MoS2 Field Effect Transistors. ACS Nano 2012, 6, 5635–5641. [Google Scholar] [CrossRef] [PubMed]

- Addou, R.; McDonnell, S.; Barrera, D.; Guo, Z.; Azcatl, A.; Wang, J.; Zhu, H.; Hinkle, C.L.; Quevedo-Lopez, M.; Alshareef, H.N.; et al. Impurities and Electronic Property Variations of Natural MoS2 Crystal Surfaces. ACS Nano 2015, 9, 9124–9133. [Google Scholar] [CrossRef] [PubMed]

- Cho, A.-J.; Yang, S.; Park, K.; Namgung, S.D.; Kim, H.; Kwon, J.-Y. Multi-Layer MoS2 FET with Small Hysteresis by Using Atomic Layer Deposition Al2O3 as Gate Insulator. ECS Solid State Lett. 2014, 3, Q67–Q69. [Google Scholar] [CrossRef]

- Rehman, A.U.; Khan, M.F.; Shehzad, M.A.; Hussain, S.; Bhopal, M.F.; Lee, S.H.; Eom, J.; Seo, Y.; Jung, J.; Lee, S.H. n-MoS2 /p-Si Solar Cells with Al2O3 Passivation for Enhanced Photogeneration. ACS Appl. Mater. Interfaces 2016, 8, 29383–29390. [Google Scholar] [CrossRef] [PubMed]

- Sik Hwang, W.; Remskar, M.; Yan, R.; Protasenko, V.; Tahy, K.; Doo Chae, S.; Zhao, P.; Konar, A.; (Grace) Xing, H.; Seabaugh, A.; et al. Transistors with chemically synthesized layered semiconductor WS2 exhibiting 105 room temperature modulation and ambipolar behavior. Appl. Phys. Lett. 2012, 101, 013107. [Google Scholar] [CrossRef]

- Kang, J.; Liu, W.; Banerjee, K. High-performance MoS2 transistors with low-resistance molybdenum contacts. Appl. Phys. Lett. 2014, 104, 093106. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, W.; Pak, Y.; Jang, H.Y.; Nam, J.H.; Kim, T.H.; Oh, S.; Choi, S.M.; Kim, Y.; Cho, B. Improvement of the Bias Stress Stability in 2D MoS2 and WS2 Transistors with a TiO2 Interfacial Layer. Nanomaterials 2019, 9, 1155. https://doi.org/10.3390/nano9081155

Park W, Pak Y, Jang HY, Nam JH, Kim TH, Oh S, Choi SM, Kim Y, Cho B. Improvement of the Bias Stress Stability in 2D MoS2 and WS2 Transistors with a TiO2 Interfacial Layer. Nanomaterials. 2019; 9(8):1155. https://doi.org/10.3390/nano9081155

Chicago/Turabian StylePark, Woojin, Yusin Pak, Hye Yeon Jang, Jae Hyeon Nam, Tae Hyeon Kim, Seyoung Oh, Sung Mook Choi, Yonghun Kim, and Byungjin Cho. 2019. "Improvement of the Bias Stress Stability in 2D MoS2 and WS2 Transistors with a TiO2 Interfacial Layer" Nanomaterials 9, no. 8: 1155. https://doi.org/10.3390/nano9081155

APA StylePark, W., Pak, Y., Jang, H. Y., Nam, J. H., Kim, T. H., Oh, S., Choi, S. M., Kim, Y., & Cho, B. (2019). Improvement of the Bias Stress Stability in 2D MoS2 and WS2 Transistors with a TiO2 Interfacial Layer. Nanomaterials, 9(8), 1155. https://doi.org/10.3390/nano9081155