Abstract

The creation of carbon nanotubes has sparked a paradigm shift in the post-silicon era because of their decent electronic and optical properties. However, interface traps pose an obstacle in the realization of high-performance carbon nanotube field-effect transistors (CNTFETs). Herein, we systematically investigate the C−V characteristics of CNTFETs and propose a small-signal equivalent model to decouple the effects arising from interface traps. Moreover, intrinsic parameters associated with interface traps can be feasibly extracted using this approach. An analytical capacitance model is further developed to be incorporated into the well-established CNTFET virtual source model, and excellent agreement has been achieved between our simulation and the measured results of the as-fabricated MOSCAP. The models developed here help to gain insight into the physical properties of high-κ dielectric interface traps subjected to different processes and inform strategies to achieve high-performance CNTFETs.

1. Introduction

Data-intensive computing applications have driven the continuous reduction of critical dimensions to improve transistor density. The shrinking bottleneck of silicon technology has stimulated research interest into low-dimensional materials, such as carbon nanotubes (CNTs), due to their decent electrical properties. CNTs have demonstrated their superiority in implementing high-performance field-effect transistors (FETs) and integrated circuits over the past two decades [1,2,3,4,5,6,7,8,9]. However, the presence of traps at the dielectric and channel interface significantly erodes gate control and reduces device reliability, thus preventing CNTs from unleashing their full potential in practical applications. Extensive efforts have been devoted to investigate the physical origin of substantial interface traps of carbon nanotube field-effect transistors (CNTFETs), which should be ascribed to the perfect surface of CNTs, which are free of dangling bonds and are unable to provide nucleation sites for high-κ dielectrics (e.g., HfO2). Moreover, optimization strategies for the suppression of interface traps have also been broadly explored [10,11,12,13,14,15,16,17,18]. To enable a comprehensive evaluation of the interface trap effects at both the device and circuit levels for optimization strategies, a compact CNTFET model that accurately incorporates these traps is essential [19,20,21,22,23,24,25,26]. Although the virtual-source model of CNTFETs (VSCNTFET) published by Stanford University is well-established and widely used in the research community, the impact of interface traps is still lacking [27,28,29], potentially limiting its accuracy for frequency-dependent or transient circuit simulations where interface states are influential.

This study proposes a small-signal equivalent circuit model for CNTFETs that incorporates the effects of interface traps, enabling the agile extraction of crucial gate capacitance parameters such as quantum capacitance, interface trap density, and trap-time constants to capture and emit carriers. Based on these extracted parameters, analytical expressions for quantum capacitance and interface trap capacitance can be well established. Subsequently, the VSCNFET model is upgraded to include the impact of interface traps on both C−V and I−V characteristics, effectively capturing the frequency dispersion observed in the C−V characteristics of CNT-based metal-oxide-semiconductor capacitors (MOSCAP). Finally, the validity of this compact model is demonstrated by showing excellent agreement with measured C−V characteristics obtained from the fabricated CNTFET MOSCAP devices.

The manuscript is organized as follows: First, we present the CNT MOSCAP structure and its small-signal model to emulate the behavior of the total−gate capacitance. Subsequently, the proposed small-signal model is used to analyze the measured C−V data, along with a comparison with the conventional high-frequency/low-frequency approach. Next, the paper focuses on developing analytical models for each component of the total-gate capacitance and updating the VSCNFET compact model to incorporate these effects. Finally, we demonstrate the accuracy of the model by comparing it with the measured C−V characteristics of the fabricated CNTFET MOSCAP devices.

2. Theoretical Concept

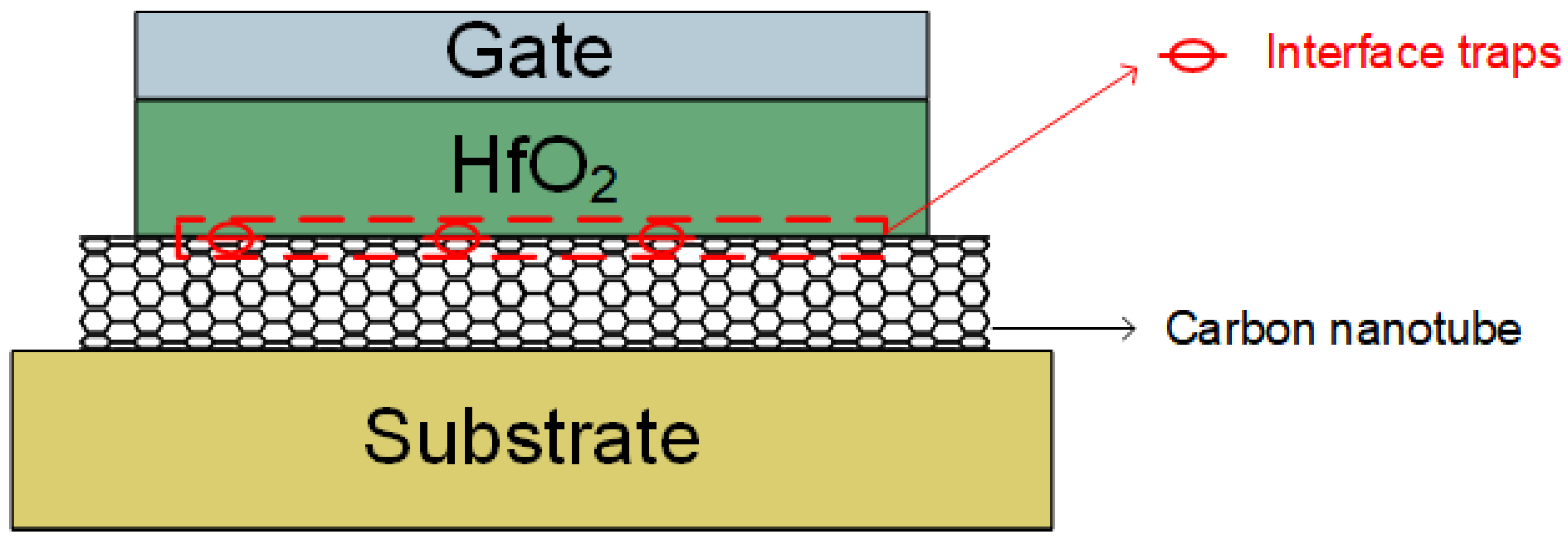

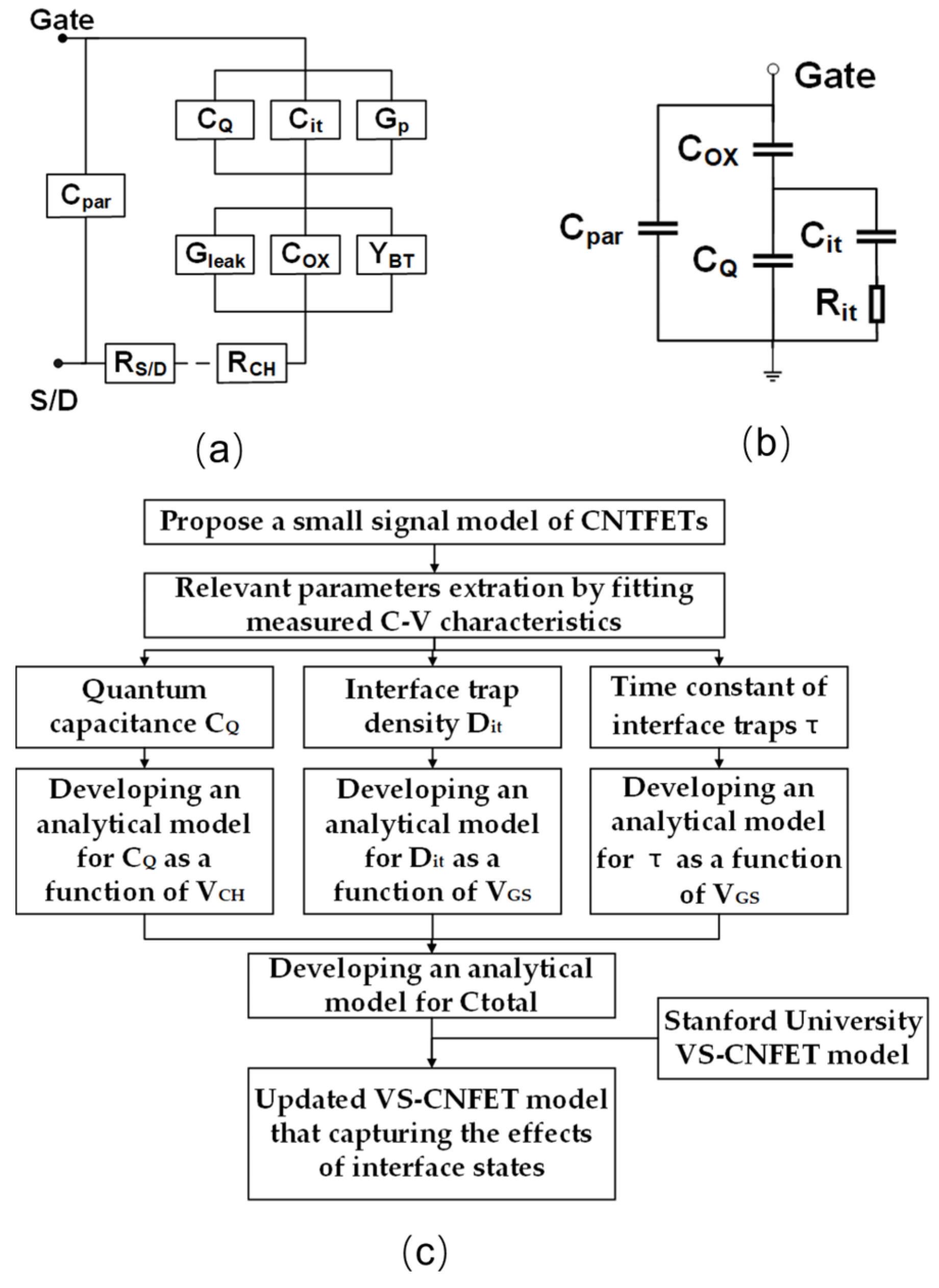

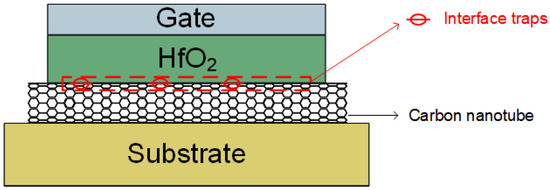

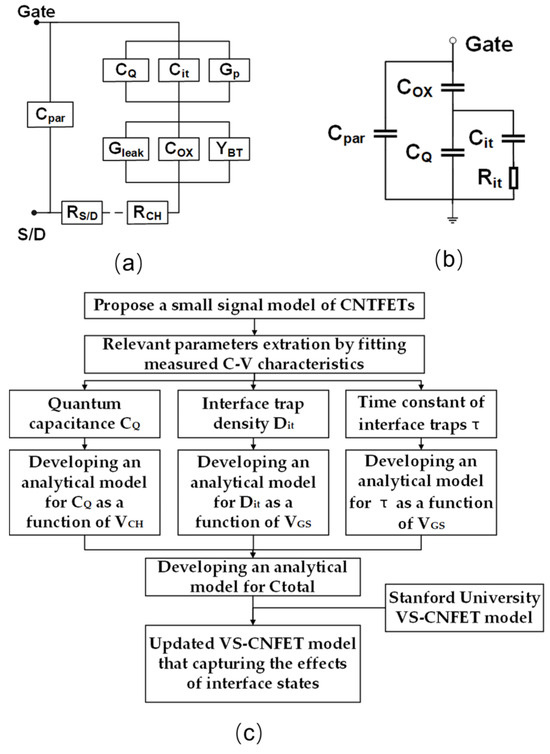

Figure 1 illustrates the cross section of CNT MOS structure that we investigate in this work. The device utilizes an aligned carbon nanotube array as the channel of L = 100 nm and W = 1 µm, with 9 nmHfO2/4 nm Ti serving as the gate stack. Figure 2a illustrates the full gate composition of CNTFET, encompassing effects from interface traps, quantum confinement, fringe-electric field, contact resistance, and so forth [30]. This research primarily focuses on the analysis of quantum capacitance and interface-trap effects, which have the most significant impact, with a simplified equivalent circuit shown in Figure 2b. Extensive efforts have been devoted to investigate the quantum confinement effect in CNTs, which results in a remarkable quantum capacitance that cannot be omitted [31]. Fundamentally, this quantum capacitance arises from the limited density of states available for charge carriers; therefore, it is closely related to the CNT’s electronic structure, specifically its diameter and chirality. Additionally, considerable interface traps exist at the heterogeneous interface between the channel and atomic layer deposition (ALD)-grown high-κ dielectric HfO2, which trap channel carriers and deteriorate the gate control through an equivalent network of capacitors and resistors in series, denoted as Cit and Rit, respectively [32]. The interface-trap density (Dit) determines the capability of interface traps to capture carriers, and the time constant of interface traps (τ) represents the characteristic time needed for these traps to exchange carriers with the CNT bands, based on the Shockley−Read−Hall (SRH) recombination process. When the period (inverse of frequency) of the small-signal voltage is shorter than the time constant (τ), the interface traps gradually become unable to respond to the signal, leading to a reduction in the number of captured carriers.

Figure 1.

CNT-Based MOS Capacitor Structure.

Figure 2.

Gate composition of the CNTFET device and modelling flowchart. (a) Transmission line network between the gate and source/drain. (b) A simplified equivalent gate capacitance model of interest in this work. (c) The flowchart showcasing the process of developing the updated VS-CNFET model that incorporates the effects of interface states.

3. Results and Discussion

Figure 2c sheds light on the overall flow to develop the gate capacitance model. Generally, relevant parameters were first extracted from the measured C−V characteristics and then fed into the proposed analytical gate capacitance model.

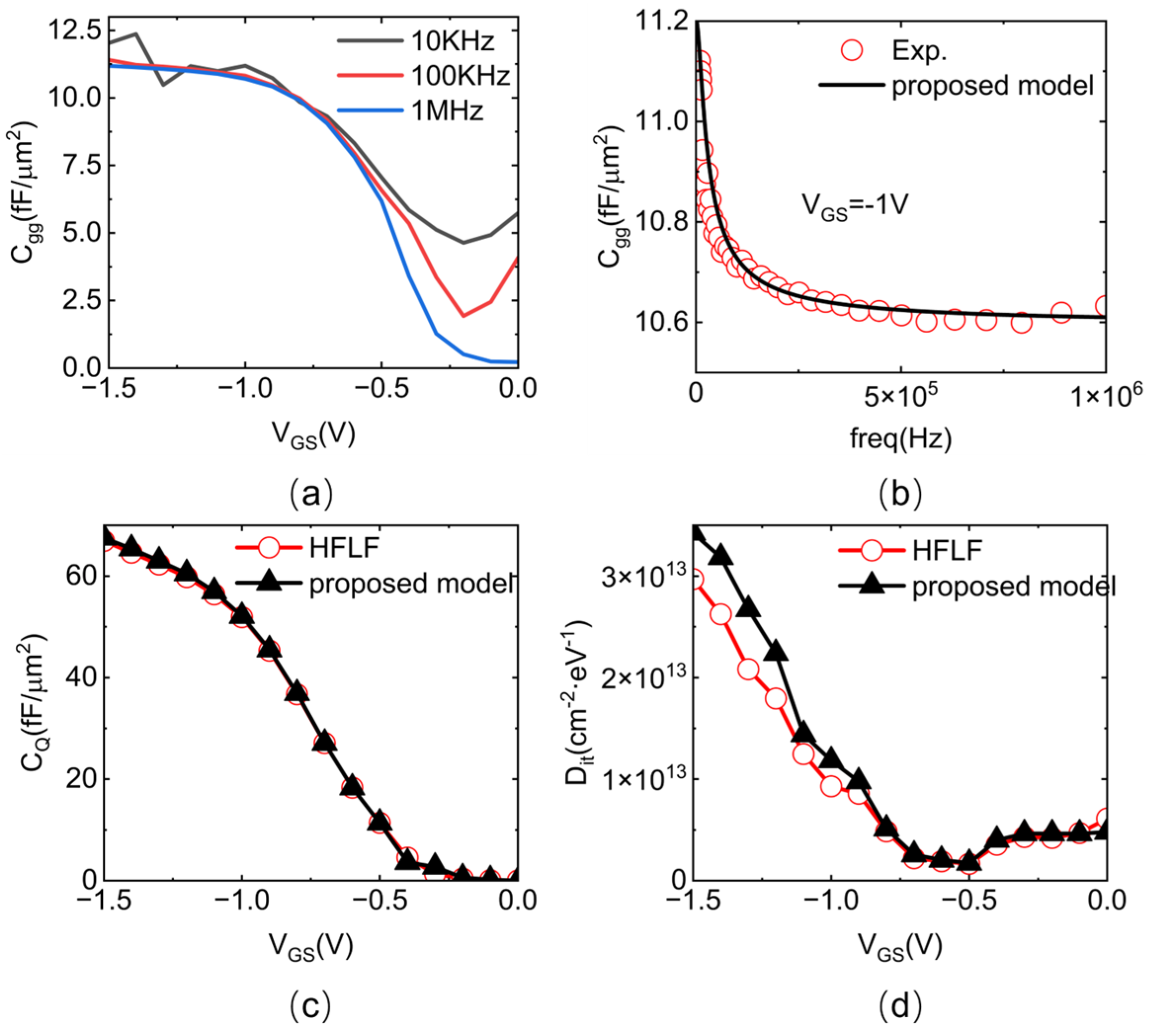

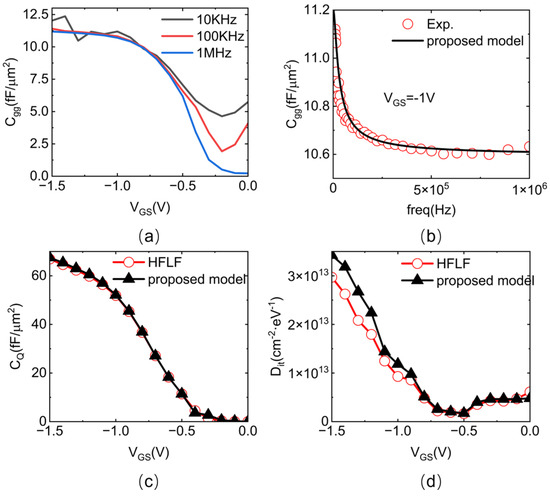

The measured C−V characteristics of a CNT MOSCAP were borrowed from the previous work by our group with normalized results, as shown in Figure 3a. More details about device fabrication and measurement can be found in Reference [33]. Prior to the analysis, the values of the two bias- and frequency-independent capacitance components, COX and Cpar, were first determined using an empirical approach [34]. COX is approximately equal to 1.2 times the maximum value of the high-frequency C−V characteristic, which is 13.5 fF/um2 in this work. Cpar can be determined as the minimum value of high-frequency C−V characteristics, which reads as 0.7 fF/µm2 from Figure 3a (including the parasitic capacitance at both the source and drain terminals, which are eliminated in the following analysis).

Figure 3.

C−V characteristics and extracted parameters. (a) As-measured multifrequency C−V curves. (b) Illustration of the proposed model fitting method at VGS = −1 V. (c) Comparison of the CQ parameter values obtained by extraction using the HFLF method and model fitting. (d) Comparison of Dit parameter values obtained by extraction using the HFLF method and model fitting.

As shown in Figure 2b, the gate oxide capacitance (COX) is in series with the parallel combination of the quantum capacitance (CQ) and interface-trap effects, denoted as a cascade of capacitance Cit and resistance Rit. Note that the RC equivalent sub-circuit characterizes the frequency dependence of interface traps, where Cit = q2 × Dit and Rit × Cit = τ−1. Therefore, Ctotal of the gate capacitance can be expressed as Equation (1) [35]:

where q represents the elementary charge; Dit represents the interface trap density; τ represents the time constant; q2Dit(2fπτ)−1arctan(2πf) is a compact mathematical representation of the RC sub-circuit, as above mentioned; and f is the frequency of the small-signal AC voltage applied to the device.

3.1. Parameter Extraction

Generally, several methods for evaluating the effects of the interface trap include the subthreshold swing (SS) method, the high-frequency and low-frequency capacitance (HFLF) method, and the gate conductance (Gp) method. The SS method is the easiest method, but it sacrifices accuracy, where the interface traps are equivalent into a capacitor in series with the gate oxide capacitance. The Gp method, which involves measuring the gate impedance, provides sufficient accuracy but is complicated to implement. The HFLF method, implemented as a reference in this work, serves as the tradeoff between the. SS and Gp methods, which provides both acceptable accuracy and feasibility of operation.

Thus, we first extract Dit and CQ through the HFLF method based on the C−V curves presented in Figure 3a. In practice, CQ and Dit are typically calculated using Equations (2) and (3) [36,37]:

where A is the effective channel area of CNTFET and CLF and CHF are the specific capacitance measured at 10 kHz and 1 MHz, respectively.

We first calibrated the proposed total-gate capacitance model with the experimental results of capacitance versus frequency. Generally, Ctotal decreases with increasing frequency because interface traps cannot completely respond to high frequencies. Ultimately, Ctotal saturates at a value determined by (1/COX + 1/CQ). The fitting procedure was conducted iteratively until our proposed model achieved excellent agreement with the experimental data. Several parameters could eventually be extracted, e.g., the quantum capacitance (CQ), interface trap density (Dit), and time constant (τ).

As shown in Figure 3c,d, the extracted CQ and Dit versus the gate-source voltage using our proposed model coincided well with the results obtained by the well-settled HFLF approach, implying the validity of our model. Note that our methodology further enables the extraction of the time constant (τ) through the measured C−V characteristics—a crucial dynamic parameter inaccessible in the conventional HFLF method.

3.2. Analytical Model Development

In order to implement the proposed total capacitance network in the compact model of CNTFETs, accurate analytical expressions for each component are essential.

For the sake of simplicity, the aligned CNT array could be assumed to be similar to the two-dimensional material, using established 2D quantum capacitance models to bypass 1D inter-tube coupling calculations. In this 2D equivalence framework, key parameters like density of states and carrier concentration represent statistical averaging across the CNT array.

The quantum capacitance CQ can thus be determined theoretically from the Fermi−Dirac distribution and the density of states (DOS) of 2D materials, the explicit form of which is expressed as Equations (4) and (5) [38]:

where Eg is the band gap of CNT, VCH is the surface potential of the CNTFET, gs = 2 is the spin degeneracy factor, gv = 2 is the valley degeneracy factor, ħ is the reduced Plank constant, and m* is the effective mass for electrons of the carbon nanotube. Furthermore, the channel potential, VCH, is described by the following empirical model, as shown in Equation (6) [39]:

where Vgt = VGS − Vth is the gate overdrive voltage; parameter SFn allows for adjusting the slope, i.e., the proportionality with VGS;, the voltage parameters VFnt and VFnB determine the smoothness of the transitions; parameter βFn allows for modeling the deviation after the transition from Boltzmann to Fermi statistics.

Recognizing that the virtual source model parameters depend solely on terminal voltages (VGS and VDS), both the interface trap density and carrier lifetime can be accurately represented as functions of VGS in our experimental data. To this end, we utilize a Fourier function to model the interface trap density (Dit) and a polynomial function to model the carrier lifetime (τ), respectively.

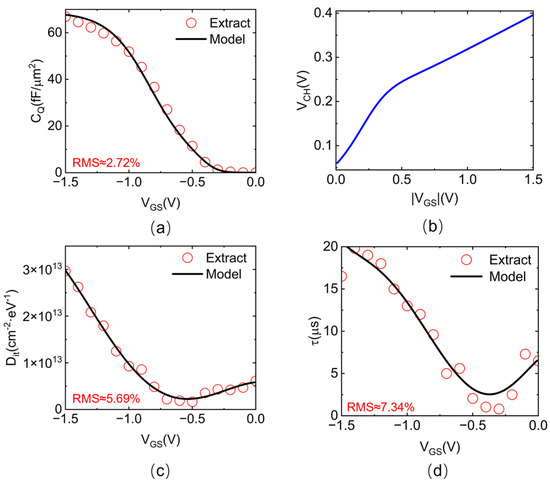

where a0~2, b1~2, ω, and p1~6 are empirical fitting parameters extracted through nonlinear least-squares regression using MATLAB (2021b) Curve Fitting Toolbox (cftool). It should be noted that the fifth-order polynomial function was selected for its ability to achieve a high fitting accuracy, demonstrating a root mean square (RMS) error of less than 8%. Figure 4 shows the fitting results of each gate component, exhibiting the accuracy of our proposed models.

Figure 4.

The validation of the proposed analytical models for each parameter presented in the Ctotal expression. (a) Fitting results of the analytical model for CQ versus extracted values from the measured C−V characteristics. (b) The extracted surface potential for CNTFETs. (c) Fitting results of the analytical model for Dit versus extracted values from the measured C−V characteristics. (d) Fitting results of the analytical model for the time constant τ versus extracted values from the measured C−V characteristics.

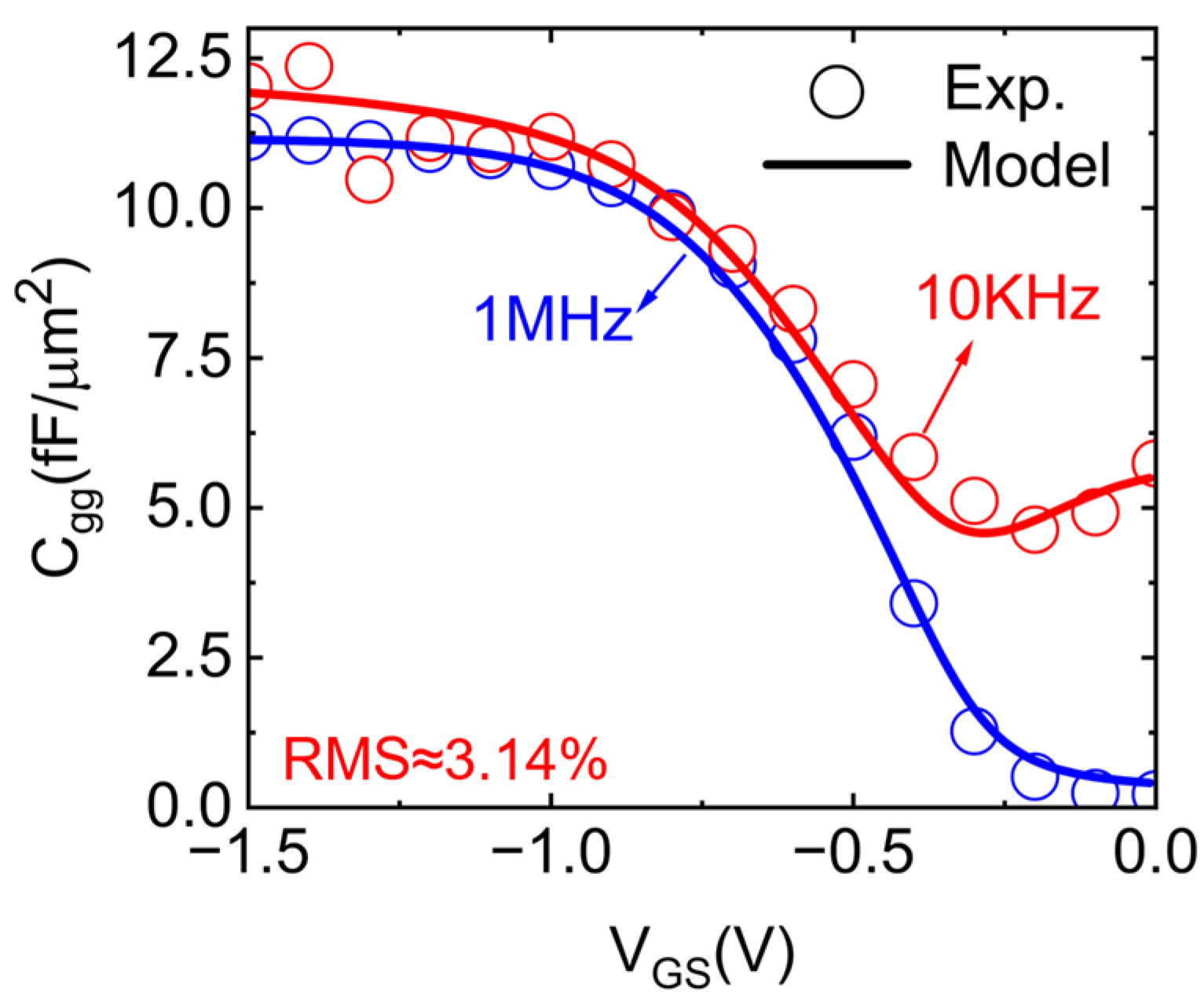

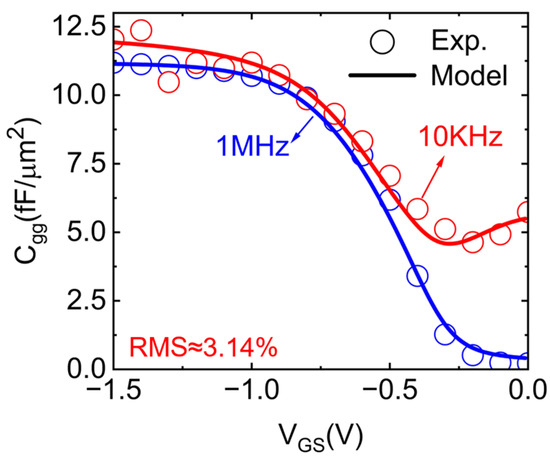

We finally arrived at an analytical expression for the total capacitance with each item being figured out. As shown in Figure 5, the proposed Ctotal model accurately captured the frequency-dependent dispersion characteristics of the CNTFET gate. The model exhibited good agreement with the C−V characteristics of the fabricated MOSCAP, confirming the accuracy of the analytical model.

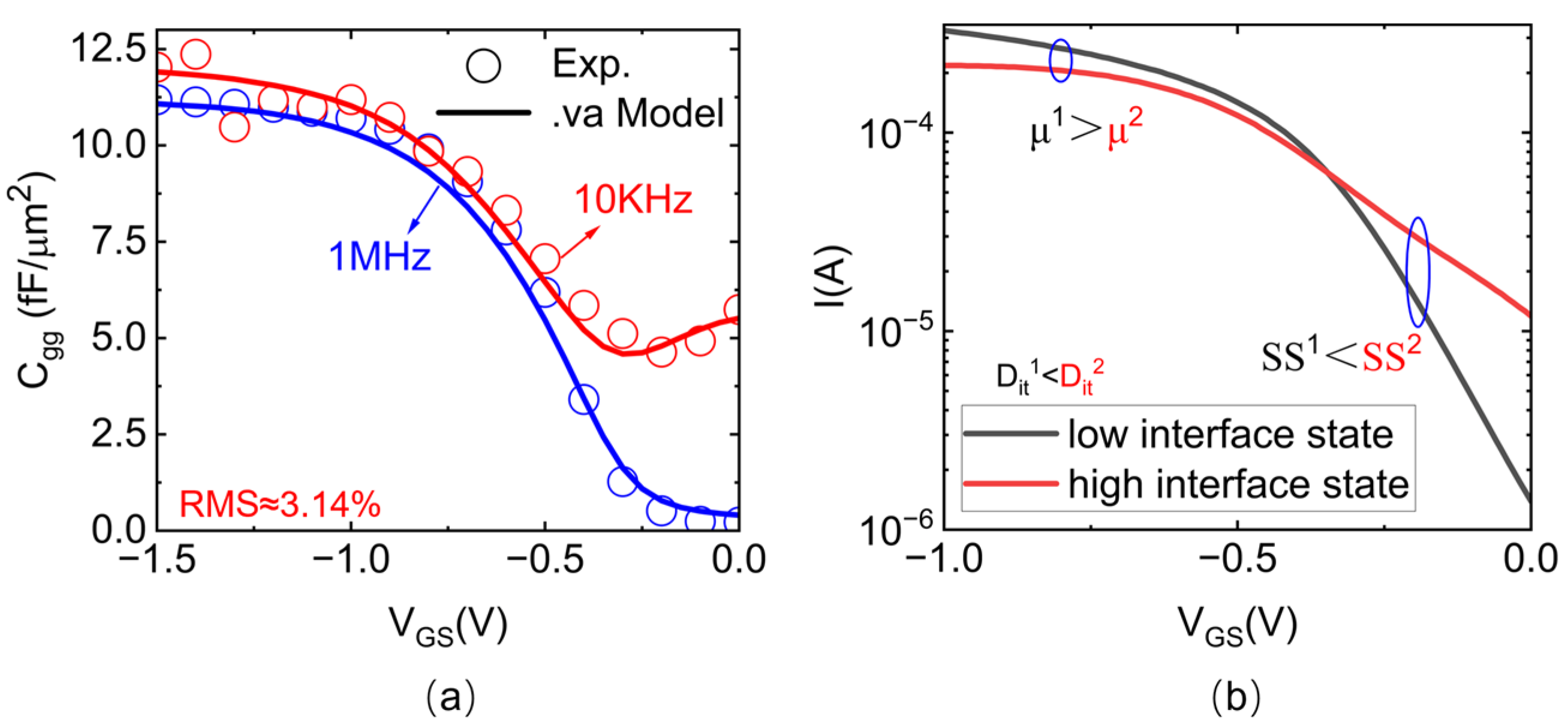

Figure 5.

Comparison of the comprehensive gate model with experimental 10 kHz and 1 MHz CV data.

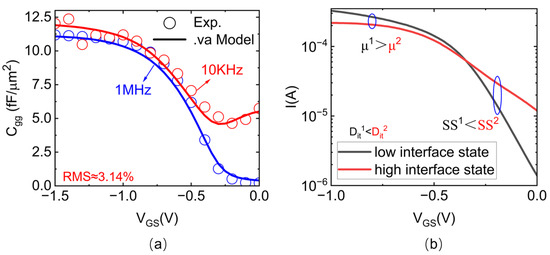

3.3. VSCNFET Model Enhancement

Subsequently, we extended the Stanford University VS-CNFET model [27,28] to develop a compact CNTFET model that accounts for interface- trap effects, as derived in the above sections. As shown in Figure 6a, the updated VS-CNFET model accurately fits the measured C−V characteristics of the fabricated CNTFET MOSCAP. Additionally, the model incorporates a VDS-dependent source-drain charge partitioning, transitioning from a 1:1 ratio at low VDS to a 3:2 ratio at high VDS. Furthermore, the model accounts for the influence of the interface trap on the I−V characteristics, specifically the sub-threshold swing and effective mobility, by considering the carrier allocation between the interface trap capacitance and the channel capacitance. Further, the proposed CNTFET capacitance model exhibits strong generality across device architectures. The gate capacitance network topology is compatible with most common CNTFET configurations, while key parameters such as COX, CQ, Dit, and τ are empirically modeled from the measured C−V characteristics without relying on specific device geometries. This framework enables consistent characterization of the. interface-trap effects in CNTFETs with varying structures and dimensions, as validated through both large-area MOSCAP measurements and scaled device analyses.

Figure 6.

The characteristics of the updated VS-CNFET model. (a) Comparison of C−V characteristics between the updated VS-CNFET model and experimental data at 10 kHz and 1 MHz, respectively. (b) Influence of interface traps on the transfer characteristics of CNTFETs projected by the model.

4. Conclusions

In this work, we propose a small-signal network for the total-gate capacitance of CNTFETs to interpret the influences from interface-trap states and quantum confinement effects. With several extracted parameters from the measured C−V characteristics, explicit expressions for each component of the network have also been determined, successfully capturing the observed frequency dispersion features. Further, we upgrade the well-established virtual source model for CNTFETs by implementing the proposed total-gate capacitance network into it, yielding a promoted version that agrees well with our measured C−V characteristics and successfully incorporates several traits associated with interface traps, such as the degradation of subthreshold swing and mobility. Besides, the proposed CNTFET capacitance model exhibits strong generality across the device architectures. The gate capacitance network topology is compatible with most common CNTFET configurations, while key parameters such as COX, CQ, Dit, and τ are empirically modeled from measured C−V characteristics without relying on specific device geometries. This framework enables consistent characterization of interface-trap effects in CNTFETs with varying structures and dimensions, as validated through both large-area MOSCAP measurements and scaled device analyses.

Author Contributions

Investigation, R.Z. and Z.T.; data curation, Y.X.; project administration, J.J. and X.H.; writing—original draft, B.Z.; writing—review and editing, P.Z. All authors have read and agreed to the published version of the manuscript.

Funding

We thank the National Key Laboratory of Integrated Circuits and Microsystems for funding the research project (NICL2024KF2004).

Data Availability Statement

Dataset available on request from the authors.

Acknowledgments

We thank the Key Laboratory for the Physics and Chemistry of Nanodevices and Center for Carbon-Based Electronics of Peking University for providing us with carbon nanotube devices and test data.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Tans, S.J.; Verschueren, A.R.; Dekker, C. Room-temperature transistor based on a single carbon nanotube. Nature 1998, 393, 49–52. [Google Scholar] [CrossRef]

- Javey, A.; Guo, J. Ballistic carbon nanotube field-effect transistors. Nature 2003, 424, 654–657. [Google Scholar] [CrossRef] [PubMed]

- Heinze, S.; Tersoff, J. Carbon Nanotubes as Schottky Barrier Transistors. Phys. Rev. Lett. 2002, 89, 106801. [Google Scholar] [CrossRef]

- Zhong, D.; Zhang, Z. Gigahertz integrated circuits based on carbon nanotube films. Nat. Electron. 2018, 1, 40–45. [Google Scholar] [CrossRef]

- Deng, J.; Wong, H.-S.P. Modeling and Analysis of Planar-Gate Electrostatic Capacitance of 1-D FET With Multiple Cylindrical Conducting Channels. IEEE Trans. Electron. Devices 2007, 54, 2377–2385. [Google Scholar] [CrossRef]

- Zhao, C.; Zhong, D. Exploring the Performance Limit of Carbon Nanotube Network Film Field-Effect Transistors for Digital Integrated Circuit Applications. Adv. Funct. Mater. 2019, 29, 1808574. [Google Scholar] [CrossRef]

- Si, J.; Xu, L. Advances in High-Performance Carbon-Nanotube Thin-Film Electronics. Adv. Funct. Mater. 2019, 5, 1900122. [Google Scholar] [CrossRef]

- Long, G.; Jin, W. Carbon nanotube-based flexible high-speed circuits with sub-nanosecond stage delays. Nat. Commun. 2022, 13, 6734. [Google Scholar] [CrossRef]

- Chen, B.; Zhang, P. Highly Uniform Carbon Nanotube Field-Effect Transistors and Medium Scale Integrated Circuits. Nano Lett. 2016, 16, 5120–5128. [Google Scholar] [CrossRef]

- Xia, P.; Feng, X. Impact and Origin of Interface States in MOS Capacitor with Monolayer MoS2 and HfO2 High-k Dielectric. Sci. Rep. 2017, 7, 40669. [Google Scholar] [CrossRef]

- Illarionov, Y.Y.; Konbloch, T. Insulators for 2D nanoelectronics: The gap to bridge. Nat. Commun. 2020, 11, 3385. [Google Scholar] [CrossRef] [PubMed]

- Park, R.S.; Shulaker, M.M. Hysteresis in Carbon Nanotube Transistors: Measurement and Analysis of Trap Density, Energy Level, and Spatial Distribution. ACS Nano 2016, 10, 4599–4608. [Google Scholar] [CrossRef] [PubMed]

- Wang, C.; Chien, J.-C. Extremely Bendable, High-Performance Integrated Circuits Using Semiconducting Carbon Nanotube Networks for Digital, Analog, and Radio-Frequency Applications. Nano Lett. 2012, 12, 1527–1533. [Google Scholar] [CrossRef] [PubMed]

- Yoon, J.; Choi, B. Evaluation of interface trap densities and quantum capacitance in carbon nanotube network thin-film transistors. Nanotechnology 2016, 27, 295704. [Google Scholar] [CrossRef]

- Cai, L.; Zhang, S. Capacitance-Voltage Characteristics of Thin-film Transistors Fabricated with Solution-Processed Semiconducting Carbon Nanotube Networks. Nanoscale Res. Lett. 2015, 10, 291. [Google Scholar] [CrossRef]

- Xu, L.; Gao, N.; Zhang, Z.; Peng, L.M. Lowering interface state density in carbon nanotube thin film transistors through using stacked Y2O3/HfO2 gate dielectric. Appl. Phys. Lett. 2018, 113, 083105. [Google Scholar] [CrossRef]

- Leong, C.H.; Chun, M.W. Compact device modelling of interface trap charges with quantum capacitance in MoS2-based field-effect transistors. Semicond. Sci. Technol. 2020, 35, 045023. [Google Scholar] [CrossRef]

- Stemmer, S.; Chobpattana, V. Frequency dispersion in III-V metal-oxide-semiconductor capacitors. Appl. Phys. Lett. 2012, 100, 233510. [Google Scholar] [CrossRef]

- Deng, J.; Wong, H.-S.P. A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application—Part I: Model of the Intrinsic Channel Region. IEEE Trans. Electron. Devices 2007, 54, 3186–3194. [Google Scholar] [CrossRef]

- Deng, J.; Wong, H.-S.P. A Compact SPICE Model for Carbon-Nanotube Field-Effect Transistors Including Nonidealities and Its Application—Part II: Full Device Model and Circuit Performance Benchmarking. IEEE Trans. Electron. Devices 2007, 54, 3195–3205. [Google Scholar] [CrossRef]

- Claus, M.; Haferlach, M. Critical review of CNTFET compact models. TechConnect Briefs 2012, 2, 770–775. [Google Scholar]

- Bejenari, I.; Schröter, M. Analytical drain current model for non-ballistic Schottky-Barrier CNTFETs. In Proceedings of the 2017 47th European Solid-State Device Research Conference (ESSDERC), Leuven, Belgium, 11–14 September 2017; pp. 90–93. [Google Scholar]

- Fregonese, S.; Cazin d’Honincthun, H. Computationally Efficient Physics-Based Compact CNTFET Model for Circuit Design. IEEE Trans. Electron. Devices 2008, 55, 1317–1327. [Google Scholar] [CrossRef]

- Maneux, C.; Fregonese, S. Multiscale simulation of carbon nanotube transistors. Solid-State Electron. 2013, 89, 26–67. [Google Scholar] [CrossRef]

- Annamalai, M.; Schröter, M. A Physics-Based Compact Model for the Static Drain Current in Heterojunction Barrier CNTFETs—Part I: Barrier-Related Current. IEEE Trans. Electron. Devices 2024, 71, 23–29. [Google Scholar] [CrossRef]

- Annamalai, M.; Schröter, M. A Physics-Based Compact Model for the Static Drain Current in Heterojunction Barrier CNTFETs—Part II: Scattering, High-Field Effects, and Model Verification. IEEE Trans. Electron. Devices 2024, 71, 30–36. [Google Scholar] [CrossRef]

- Lee, C.-S.; Pop, E. A Compact Virtual-Source Model for Carbon Nanotube FETs in the Sub-10-nm Regime—Part I: Intrinsic Elements. IEEE Trans. Electron. Devices 2015, 62, 3061–3069. [Google Scholar] [CrossRef]

- Lee, C.-S.; Pop, E. A Compact Virtual-Source Model for Carbon Nanotube FETs in the Sub-10-nm Regime—II: Extrinsic Elements, Performance Assessment, and Design Optimization. IEEE Trans. Electron. Devices 2015, 62, 3070–3078. [Google Scholar] [CrossRef]

- Lundstrom, M.S.; Antoniadis, D.A. Compact Models and the Physics of Nanoscale FETs. IEEE Trans. Electron. Devices 2014, 61, 225–233. [Google Scholar] [CrossRef]

- Gaur, A.; Agarwal, T. A MOS capacitor model for ultra-thin 2D semiconductors: The impact of interface defects and channel resistance. 2D Mater. 2020, 7, 035018. [Google Scholar] [CrossRef]

- Ilani, S.; Donev, L.A.K. Measurement of the quantum capacitance of interacting electrons in carbon nanotubes. Nat. Phys. 2006, 2, 687–691. [Google Scholar] [CrossRef]

- Xiao, H.; Liu, Y. Interface and Border Traps in the Gate Stack of Carbon Nanotube Film Transistors with an Yttria Dielectric. ACS Appl. Electron. Mater. 2023, 5, 3908–3916. [Google Scholar] [CrossRef]

- Liu, Y.; Ding, S. Interface States in Gate Stack of Carbon Nanotube Array Transistors. ACS Nano 2024, 18, 19086–19098. [Google Scholar] [CrossRef] [PubMed]

- Xiu, F.; Meyer, N. Quantum Capacitance in Topological Insulators. Sci. Rep. 2012, 2, 669. [Google Scholar] [CrossRef] [PubMed]

- Fang, N.; Nagashio, K. Band tail interface states and quantum capacitance in a monolayer molybdenum disulfide field-effect-transistor. J. Phys. D Appl. Phys. 2018, 51, 065110. [Google Scholar] [CrossRef]

- Castagné, R.; Vapaille, A. Description of the SiO2/Si interface properties by means of very low frequency MOS capacitance measurements. Surf. Sci. 1971, 28, 157–193. [Google Scholar] [CrossRef]

- Nicollian, E.H.; Goetzberger, A. The si-sio, interface—Electrical properties as determined by the metal-insulator-silicon conductance technique. Bell Syst. Tech. J. 1967, 46, 1033–1055. [Google Scholar] [CrossRef]

- Bennett, R.K.A.; Pop, E. How Do Quantum Effects Influence the Capacitance and Carrier Density of Monolayer MoS2 Transistors. Nano Lett. 2023, 23, 1666–1672. [Google Scholar] [CrossRef]

- Annamalai, M.; Schröter, M. Compact Formulation for the Bias Dependent Quasi-Static Mobile Charge in Schottky-Barrier CNTFETs. IEEE Trans. Nanotechnol. 2021, 20, 754–760. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).