Interfacial Chemical and Electrical Performance Study and Thermal Annealing Refinement for AlTiO/4H-SiC MOS Capacitors

Abstract

1. Introduction

2. Experimental Preparation

3. Results and Discussion

3.1. Surface Topographic Analysis

3.2. XPS Depth Profiling Analysis

3.3. Band Alignment Calculation

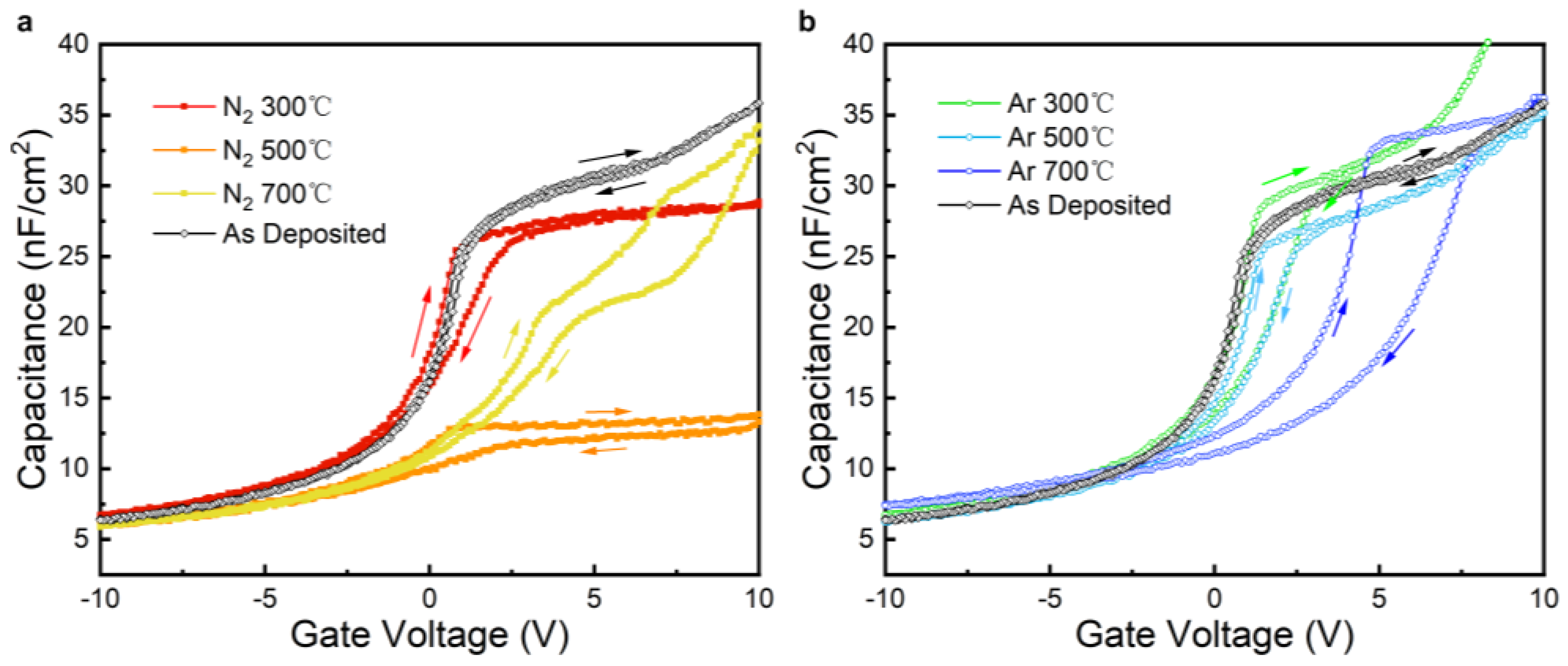

3.4. Electronic JV and CV Analysis

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: Berlin/Heidelberg, Germany, 2008; pp. 23–31. [Google Scholar]

- Cooper, J.A.; Kimoto, T. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices, and Applications; Wiley-IEEE: Singapore, 2014; pp. 16–30. [Google Scholar]

- Chen, Y.; Zhang, X.; Zhao, Q.; He, L.; Huang, C.; Xie, Z. P-type 3C-SiC nanowires and their optical and electrical transport properties. ChemComm 2011, 47, 6398–6400. [Google Scholar] [CrossRef] [PubMed]

- Sugita, T.; Hiramatsu, K.; Ikeda, S.; Matsumura, M. Fabrication of pores in a silicon carbide wafer by electrochemical etching with a glassy-carbon needle electrode. Acs Appl. Mater. Interfaces 2013, 5, 2580–2584. [Google Scholar] [CrossRef] [PubMed]

- Yano, H.; Kanafuji, N.; Osawa, A.; Hatayama, T.; Fuyuki, T. Threshold Voltage Instability in 4H-SiC MOSFETs With Phosphorus-Doped and Nitrided Gate Oxides. IEEE Trans. Electron Devices 2015, 62, 324. [Google Scholar] [CrossRef]

- Phan, H.P.; Dao, D.V.; Tanner, P.; Han, J.; Nguyen, N.T.; Dimitrijev, S.; Walker, G.; Wang, L.; Zhu, Y. Thickness dependence of the piezoresistive effect in p-type single crystalline 3C-SiC nanothin films. J. Mater. Chem. C 2014, 2, 7176–7179. [Google Scholar] [CrossRef]

- Lipkin, L.A.; Palmour, J.W. Insulator investigation on sic for improved reliability. IEEE Trans. Electron Devices 1999, 46, 525–532. [Google Scholar] [CrossRef]

- Nawaz, M. On the evaluation of gate dielectrics for 4H-SiC based power MOSFETs. Act. Passive Electron. Compon. 2015, 2015, 651527. [Google Scholar] [CrossRef]

- Tanner, C.M.; Perng, Y.C.; Frewin, C.; Saddow, S.E.; Chang, J.P. Electrical performance of Al2O3 gate dielectric films deposited by atomic layer deposition on 4H-SiC. App. Phys. Lett. 2007, 91, 203510. [Google Scholar] [CrossRef]

- Hosoi, T.; Konzono, K.; Uenishi, Y.; Mitani, S.; Nakano, Y.; Nakamura, T.; Shimura, T.; Watanabe, H. Investigation of surface and interface morphology of thermally grown SiO2 dielectrics on 4H-SiC(0001) substrates. Mater. Sci. Forum 2011, 679–680, 342–345. [Google Scholar] [CrossRef]

- Fiorenza, P.; Giannazzo, F.; Roccaforte, F. Characterization of SiO2/4H-SiC Interfaces in 4H-SiC MOSFETs: A Review. Energies 2019, 12, 2310. [Google Scholar] [CrossRef]

- Hallén, A.; Usman, M.; Suvanam, S.; Henkel, C.; Linnarsson, M.K. Passivation of sic device surfaces by aluminum oxide. IOP Conference 2014, 56, 012007. [Google Scholar] [CrossRef]

- Kang, J.; Xu, K.; Lee, H.; Bhattacharya, S.; Zhao, Z.; Wang, Z.; Sankaran, M.R.; Zhu, W. High Ion/Ioff ratio 4H-SiC MISFETs with stable operation at 500 °C using SiO2/SiNx/Al2O3 gate stacks. Appl. Phys. Lett. 2023, 122, 082906. [Google Scholar] [CrossRef]

- Schilirò, E.; Fiorenza, P.; Lo Nigro, R.; Galizia, B.; Greco, G.; Di Franco, S.; Bongiorno, C.; La Via, F.; Giannazzo, F.; Roccaforte, F. Al2O3 Layers Grown by Atomic Layer Deposition as Gate Insulator in 3C-SiC MOS Devices. Materials 2023, 16, 5638. [Google Scholar] [CrossRef] [PubMed]

- Heo, S.C.; Lim, D.; Jung, W.S.; Choi, R.; Yu, H.Y.; Choi, C. Remote plasma atomic layer deposited Al2O3 4H-SiC MOS capacitor with remote H2 plasma passivation and post metallization annealing. Microelectron. Eng. 2015, 147, 239–243. [Google Scholar] [CrossRef]

- Usman, M.; Suvanam, S.S.; Yazdi, M.G.; Göthelid, M.; Sultan, M.; Hallén, A. Stoichiometry of the ALD-Al2O3/4H–SiC interface by synchrotron-based XPS. J. Phys. D 2016, 49, 255308. [Google Scholar] [CrossRef]

- Liu, G.; Jaegermann, W.; He, J.; Sundström, V.; Sun, L. XPS and UPS Characterization of the TiO2/ZnPcGly Heterointerface: Alignment of Energy Levels. J. Phys. Chem. B 2002, 106, 5814–5819. [Google Scholar] [CrossRef]

- Seo, S.; Woo, W.J.; Lee, Y.; Yoon, H.; Kim, M.; Oh, I.K.; Chung, S.M.; Kim, H.; Shong, B. Reaction Mechanisms of Non-hydrolytic Atomic Layer Deposition of Al2O3 with a Series of Alcohol Oxidants. J. Phys. Chem. C 2021, 125, 18151–18160. [Google Scholar] [CrossRef]

- Gulseren, M.E.; Kurt, G.; Ghobadi, T.G.; Ghobadi, A.; Salkim, G.; Ozturk, M.; Butun, B.; Ozbay, E. Investigation of angstrom-thick aluminium oxide passivation layers to improve the gate lag performance of GaN HEMTs. Mater. Res. Express 2019, 6, 095052. [Google Scholar] [CrossRef]

- Ma, J.W.; Lee, W.J.; Bae, J.M.; Jeong, K.S.; Oh, S.H.; Kim, J.H.; Kim, S.H.; Seo, J.H.; Ahn, J.P.; Kim, H.; et al. Carrier Mobility Enhancement of Tensile Strained Si and SiGe Nanowires via Surface Defect Engineering. Nano Lett. 2015, 15, 7204–7210. [Google Scholar] [CrossRef]

- Itokawa, H.; Maruyama, T.; Miyazaki, S.; Hirose, M. Determination of Bandgap and Energy Band Alignment for High-Dielectric-Constant Gate Insulators Using High-Resolution X-ray Photoelectron Spectroscopy. ICSSDM 1999, 1999, 158–159. [Google Scholar]

- Zhang, F.; Sun, G.; Zheng, L.; Liu, S.; Liu, B.; Dong, L.; Wang, L.; Zhao, W.; Liu, X.; Yan, G.; et al. Interfacial study and energy-band alignment of annealed Al2O3 films prepared by atomic layer deposition on 4H-SiC. J. Appl. Phys. 2013, 113, 044112. [Google Scholar] [CrossRef]

- Ye, G.; Wang, H.; Ji, R. Band alignment between 4H-SiC and atomic-layer-deposited ZrO2 determined by X-ray photoelectron spectroscopy. Appl. Phys. Express 2015, 8, 091302. [Google Scholar] [CrossRef]

- Sun, Q.J.; Zhang, Y.M.; Song, Q.W.; Tang, X.Y.; Zhang, Y.M.; Li, C.Z.; Zhao, Y.L.; Zhang, Y.M. Near-interface oxide traps in 4H–SiC MOS structures fabricated with and without annealing in NO*. Chin. Phys. B 2017, 26, 127701. [Google Scholar] [CrossRef]

- Idris, M.I.; Weng, M.H.; Chan, H.K.; Murphy, A.E.; Clark, D.T.; Young, R.A.; Ramsay, E.P.; Wright, N.G.; Horsfall, A.B. Instability of phosphorous doped SiO2 in 4H-SiC MOS capacitors at high temperatures. J. Appl. Phys. 2016, 120, 214902. [Google Scholar] [CrossRef]

- Lo Nigro, R.; Schilirò, E.; Fiorenza, P.; Roccaforte, F. Nanolaminated Al2O3/HfO2 Dielectrics for Silicon Carbide Based Devices. J. Vac. Sci. Technol. A 2020, 38, 032410. [Google Scholar] [CrossRef]

- Khosa, R.Y.; Thorsteinsson, E.B.; Winters, M.; Rorsman, N.; Karhu, R.; Hassan, J.; Sveinbjörnsson, E.Ö. Electrical Characterization of Amorphous Al2O3 Dielectric Films on N-Type 4H-SiC. AIP Advances 2018, 8, 025304. [Google Scholar] [CrossRef]

- Kosiel, K.; Król, K.; Taube, A.; Guziewicz, M.; Gołaszewska-Malec, K.; Kruszka, R.; Kamińska, E.; Piotrowska, A. Characterization of Al2O3 /4H-SiC and Al2O3/SiO2/4H-SiC MOS Structures. Bull. Pol. Ac. Tech 2016, 64, 547–551. [Google Scholar]

- Suvanam, S.S.; Usman, M.; Martin, D.; Yazdi, M.G.; Linnarsson, M.; Tempez, A.; Götelid, M.; Hallén, A. Improved Interface and Electrical Properties of Atomic Layer Deposited Al2O3/4H-SiC. Appl. Surf. Sci. 2018, 433, 108–115. [Google Scholar] [CrossRef]

| Dielectric | EBR (MV/cm) | JD (A/cm2) | Dit (eV/cm2) | Neff (−QF) (cm−2) | Ref. | Year |

|---|---|---|---|---|---|---|

| Al2O3/SiO2 | - | - | - | 2.07 × 1012 | [26] | 2020 |

| Al2O3 | 3 | 4 × 10−6 | 1.5 × 1011 | 4.5 × 1012 | [27] | 2018 |

| Al2O3 | 7.5 | 0.9 | 1 × 1012 | 2.7 × 1012 | [28] | 2018 |

| Al2O3 | 7.5 | 2 × 10−4 | 5 × 1010 | 1.5 × 1011 | [29] | 2018 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zeng, Y.-X.; Huang, W.; Ma, H.-P.; Zhang, Q.-C. Interfacial Chemical and Electrical Performance Study and Thermal Annealing Refinement for AlTiO/4H-SiC MOS Capacitors. Nanomaterials 2025, 15, 814. https://doi.org/10.3390/nano15110814

Zeng Y-X, Huang W, Ma H-P, Zhang Q-C. Interfacial Chemical and Electrical Performance Study and Thermal Annealing Refinement for AlTiO/4H-SiC MOS Capacitors. Nanomaterials. 2025; 15(11):814. https://doi.org/10.3390/nano15110814

Chicago/Turabian StyleZeng, Yu-Xuan, Wei Huang, Hong-Ping Ma, and Qing-Chun Zhang. 2025. "Interfacial Chemical and Electrical Performance Study and Thermal Annealing Refinement for AlTiO/4H-SiC MOS Capacitors" Nanomaterials 15, no. 11: 814. https://doi.org/10.3390/nano15110814

APA StyleZeng, Y.-X., Huang, W., Ma, H.-P., & Zhang, Q.-C. (2025). Interfacial Chemical and Electrical Performance Study and Thermal Annealing Refinement for AlTiO/4H-SiC MOS Capacitors. Nanomaterials, 15(11), 814. https://doi.org/10.3390/nano15110814