Emerging Copper-to-Copper Bonding Techniques: Enabling High-Density Interconnects for Heterogeneous Integration

Abstract

1. Introduction

- (a)

- Heterogeneous Integration as an Option for More Moore and More Than Moore

- (b)

- Copper-based Interconnect Technology for Heterogeneous Integration

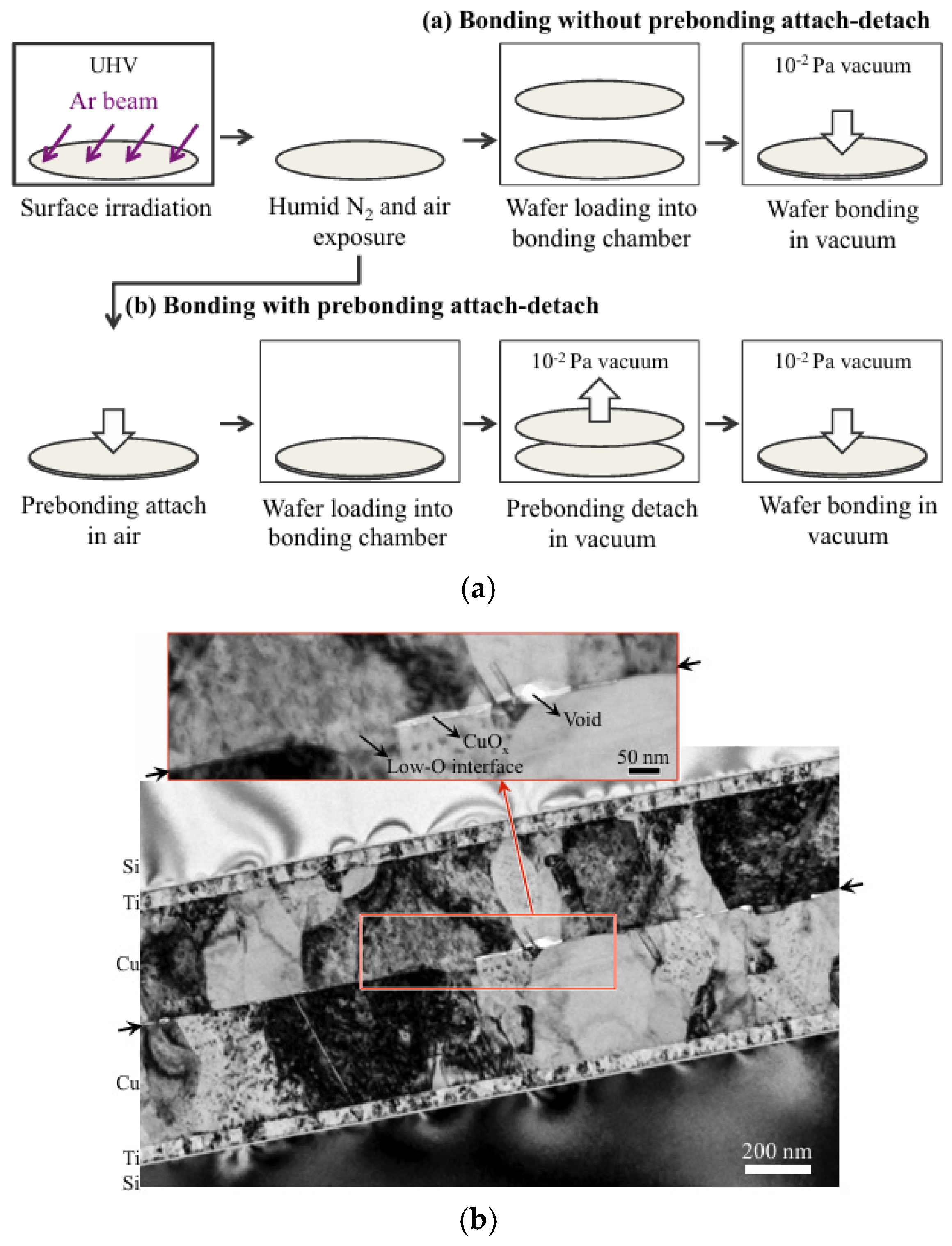

2. Surface Plasma Activation

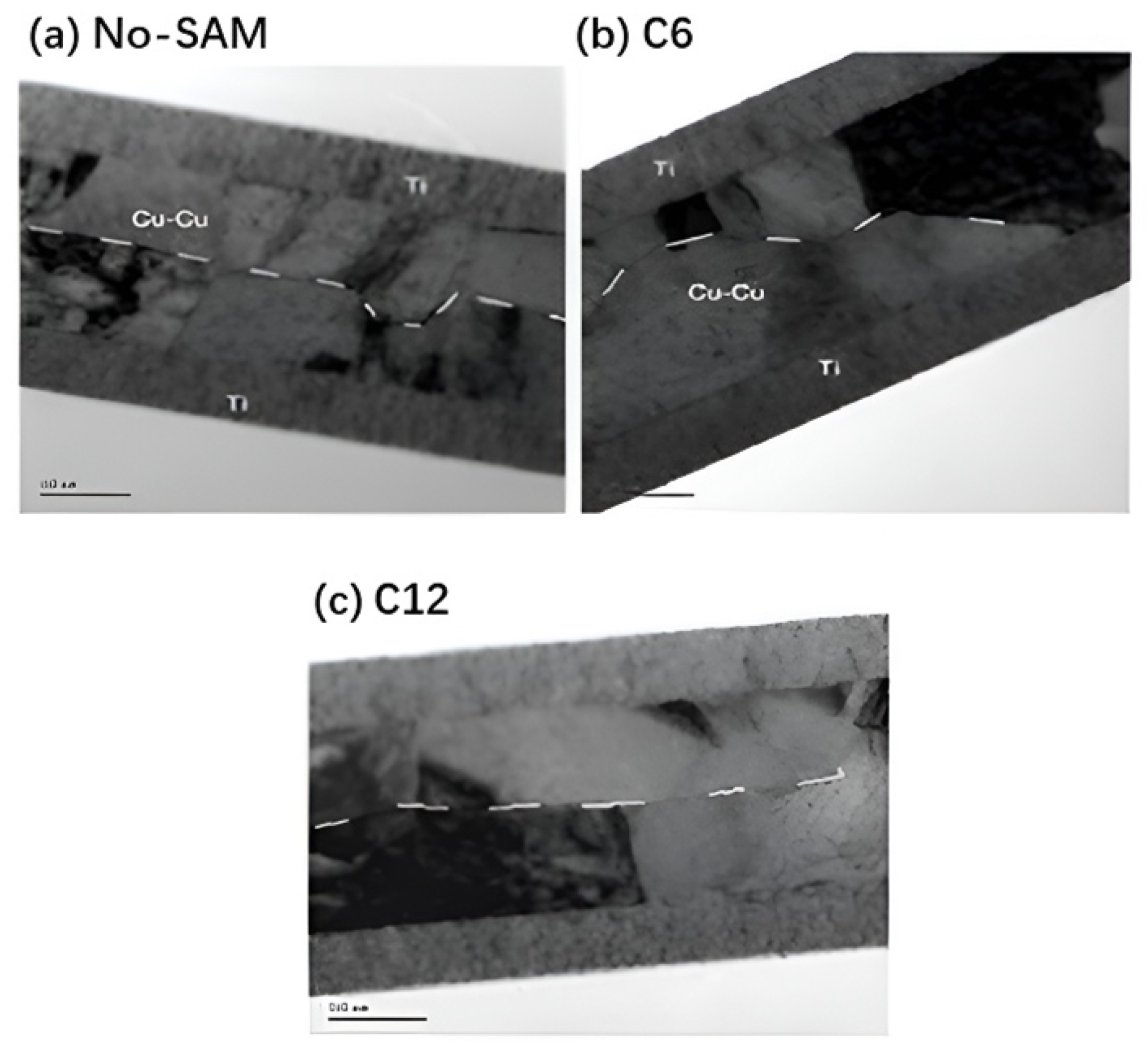

3. Passivation

4. Copper Geometry Optimization

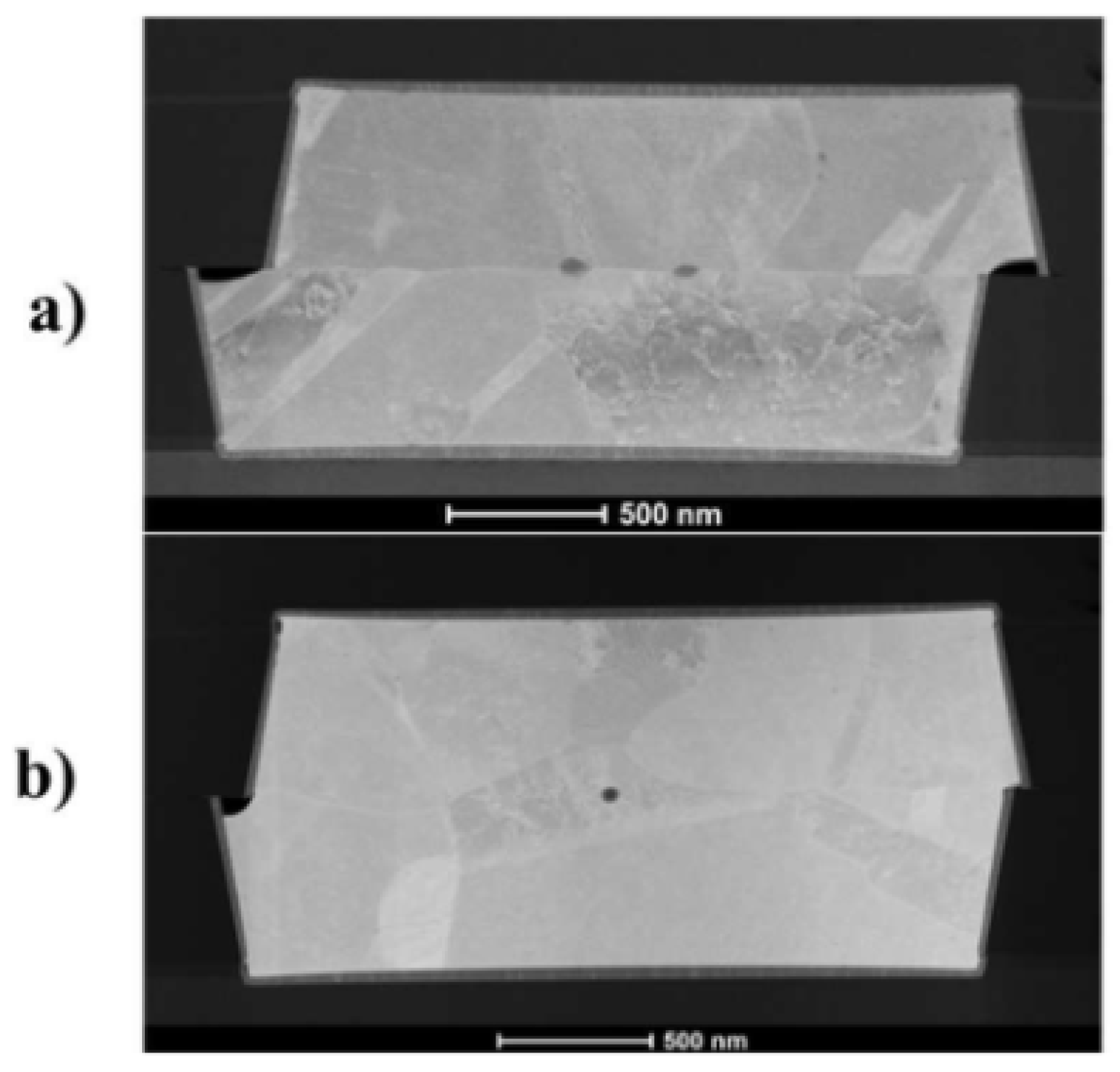

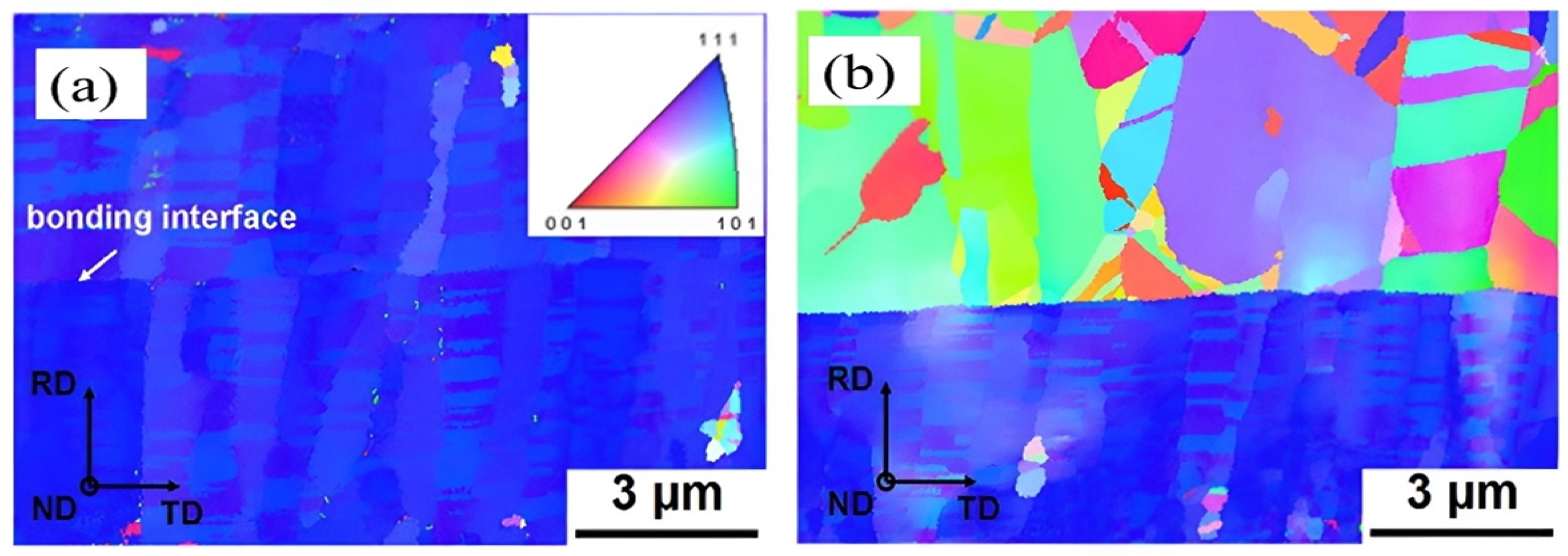

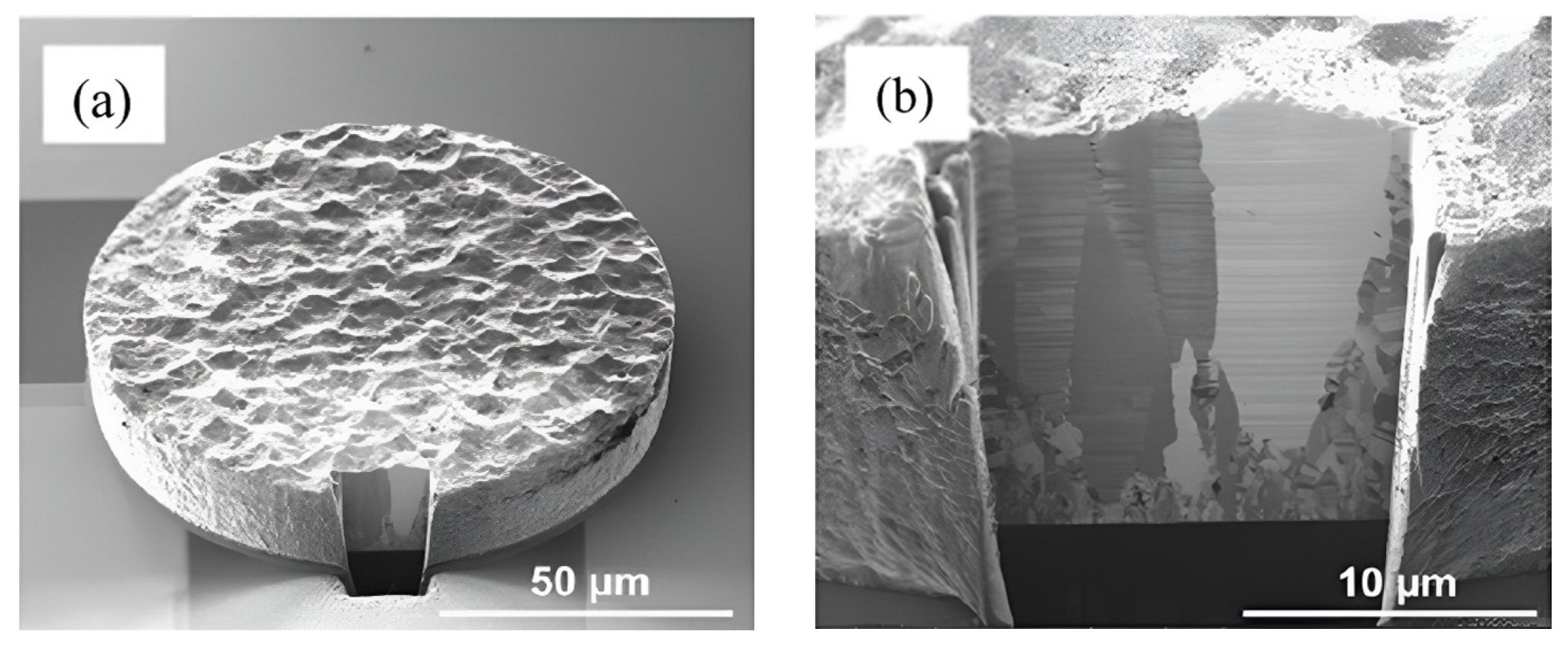

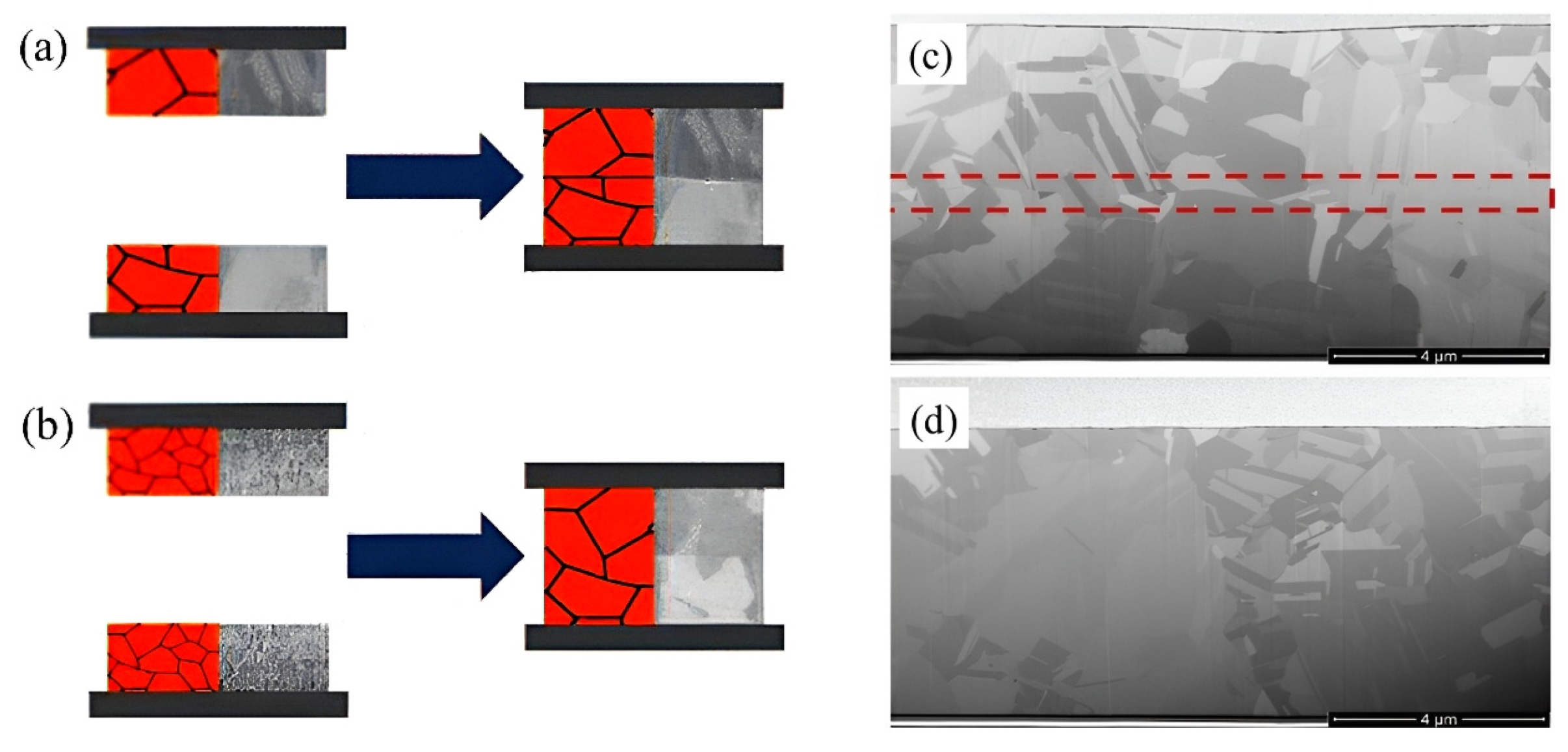

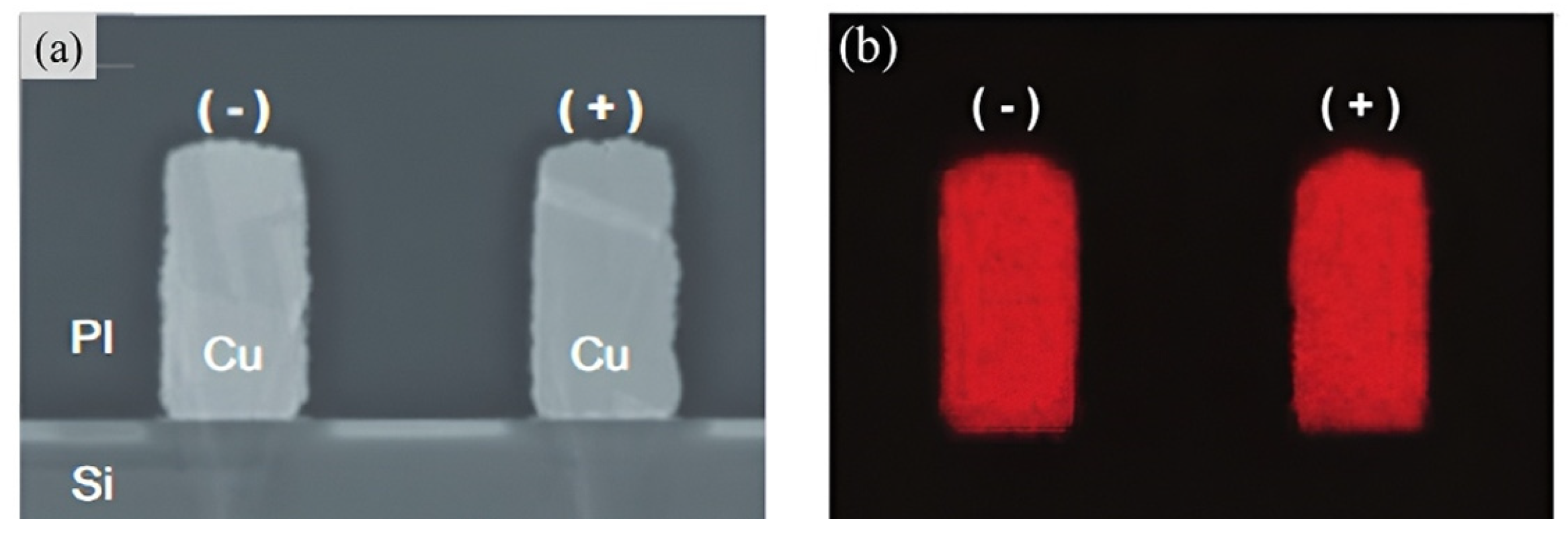

5. Copper Microstructure Optimization

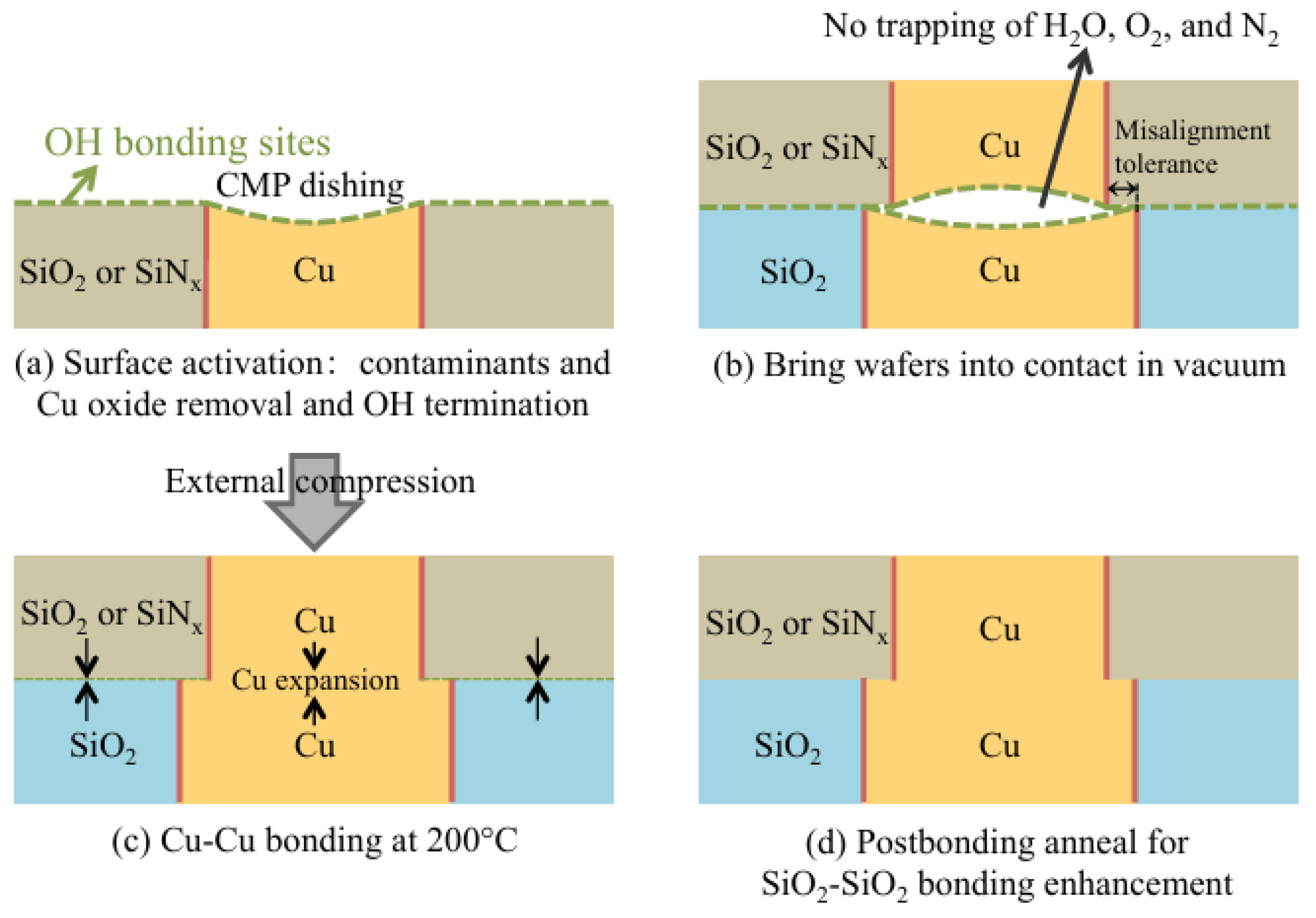

6. Cu/Dielectric Hybrid Bonding

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lau, J.H. Heterogeneous Integrations; Springer: Berlin/Heidelberg, Germany, 2019. [Google Scholar] [CrossRef]

- Lau, J.H. Chiplet Design and Heterogeneous Integration Packaging; Springer: Singapore, 2023. [Google Scholar] [CrossRef]

- Wong, H.; Zhang, J.; Liu, J. Contacts at the Nanoscale and for Nanomaterials. Nanomaterials 2024, 14, 386. [Google Scholar] [CrossRef]

- Wong, H.; Zhang, J.; Liu, J. Quest for more Moore at the end of Device Downsizing. J. Circuits Syst. Comput. 2024. [Google Scholar] [CrossRef]

- Lau, J.H. Recent Advances and New Trends in Flip Chip Technology. J. Electron. Packag. 2016, 138, 030802. [Google Scholar] [CrossRef]

- Shigetou, A.; Itoh, T.; Matsuo, M.; Hayasaka, N.; Okumura, K.; Suga, T. Bumpless interconnect through ultrafine Cu electrodes by means of surface-activated bonding (SAB) method. IEEE Trans. Adv. Packag. 2006, 29, 218–226. [Google Scholar] [CrossRef]

- Chew, S.A.; De Vos, J.; Beyne, E. Wafer-to-wafer hybrid bonding at 400-nm interconnect pitch. Nat. Rev. Electr. Eng. 2024, 1, 71–72. [Google Scholar] [CrossRef]

- Lin, Y.; Bex, P.; Kennes, K.; Derakhshandeh, J.; Dhakras, P.; Suhard, S.; Gerets, C.; Dewilde, S.; Georgieva, V.; Jourdain, A.; et al. Direct Die-to-Wafer Hybrid Bonding Using Plasma Diced Dies and Bond Pad Pitch Scaling Down to 2 µm. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; pp. 40–44. [Google Scholar] [CrossRef]

- Kagawa, Y.; Fujii, N.; Aoyagi, K.; Kobayashi, Y.; Nishi, S.; Todaka, N.; Takeshita, S.; Taura, J.; Takahashi, H.; Nishimura, Y.; et al. Novel stacked CMOS image sensor with advanced Cu2Cu hybrid bonding. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 8.4.1–8.4.4. [Google Scholar] [CrossRef]

- Kamei, T.; Yoshioka, H.; Hiratsuka, T.; Sakamoto, A.; Shimizu, K.; Iwamoto, H. Development of high reliability 6 µm-pitch Cu-Cu connections using over-400 mm2-large Chip on Wafer bonding process. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 1285–1290. [Google Scholar] [CrossRef]

- Chia, H.J.; Tai, S.P.; Cui, J.J.; Wang, C.T.; Tung, C.H.; Yee, K.C.; Yu, D.C.H. Ultra High Density Low Temperature SoIC with Sub-0.5 μm Bond Pitch. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Jouve, A.; Balan, V.; Bresson, N.; Euvrard-Colnat, C.; Fournel, F.; Exbrayat, Y.; Mauguen, G.; Sater, M.A.; Beitia, C.; Arnaud, L.; et al. 1 μm Pitch direct hybrid bonding with <300 nm wafer-to-wafer overlay accuracy. In Proceedings of the 2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 16–19 October 2017; pp. 1–2. [Google Scholar] [CrossRef]

- Oi, K.; Otake, S.; Shimizu, N.; Watanabe, S.; Kunimoto, Y.; Kurihara, T.; Koyama, T.; Tanaka, M.; Aryasomayajula, L.; Kutlu, Z. Development of new 2.5D package with novel integrated organic interposer substrate with ultra-fine wiring and high density bumps. In Proceedings of the 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 348–353. [Google Scholar] [CrossRef]

- Seo, H.; Park, H.; Kim, S.E. Comprehensive Analysis of a Cu Nitride Passivated Surface That Enhances Cu-to-Cu Bonding. IEEE Trans. Compon. Pack. Manuf. Technol. 2020, 10, 1814–1820. [Google Scholar] [CrossRef]

- Wong, H. Abridging CMOS Technology. Nanomaterials 2022, 12, 4245. [Google Scholar] [CrossRef]

- Li, C.; Pan, Z.; Li, X.; Hao, W.; Miao, R.; Wang, A. Selective Overview of 3D Heterogeneity in CMOS. Nanomaterials 2022, 12, 2340. [Google Scholar] [CrossRef]

- Jeon, H.J.; Hong, S.J. Ammonia Plasma Surface Treatment for Enhanced Cu–Cu Bonding Reliability for Advanced Packaging Interconnection. Coatings 2024, 14, 1449. [Google Scholar] [CrossRef]

- Jeong, J.; Geum, D.-M.; Kim, S. Heterogeneous and Monolithic 3D Integration Technology for Mixed-Signal ICs. Electronics 2022, 11, 3013. [Google Scholar] [CrossRef]

- Gomes, W.; Khushu, S.; Ingerly, D.B.; Stover, P.N.; Chowdhury, N.I.; O’Mahony, F. Lakefield and Mobility Compute: A 3D Stacked 10nm and 22FFL Hybrid Processor System in 12 × 12mm2, 1 mm Package-on-Package. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 144–146. [Google Scholar] [CrossRef]

- Simakov, N.A.; Jones, M.D.; Furlani, T.R.; Siegmann, E.; Harrison, R.J. First Impressions of the NVIDIA Grace CPU Superchip and NVIDIA Grace Hopper Superchip for Scientific Workloads. In Proceedings of the HPCAsia’24 Workshops: Proceedings of the International Conference on High Performance Computing in Asia-Pacific Region Workshops, Nagoya, Japan, 25–27 January 2024; pp. 36–44. [Google Scholar] [CrossRef]

- Hybrid Bonding Process Flow—Advanced Packaging Part 5, Semi Analysis Website. Available online: https://semianalysis.com/2024/02/09/hybrid-bonding-process-flow-advanced/ (accessed on 24 February 2025).

- Save, D.; Braud, F.; Torres, J.; Binder, F.; Muller, C.; Weidner, J.O.; Hasse, W. Electromigration resistance of copper interconnects. Microelectron. Eng. 1997, 33, 75–84. [Google Scholar] [CrossRef]

- Chen, K.N.; Lee, S.H.; Andry, P.S.; Tsang, C.K.; Topol, A.W.; Lin, Y.M.; Lu, J.Q.; Young, A.M.; Leong, M.; Haensch, W.; et al. Structure, design and process control for Cu bonded interconnects in 3D integrated circuits. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar] [CrossRef]

- Lu, T.-F.; Cheng, Y.-F.; Wang, P.-W.; Yen, Y.-T.; Wu, Y.-C. Eliminating Cu–Cu Bonding Interfaces Using Electroplated Copper and (111)-Oriented Nanotwinned Copper. Materials 2024, 17, 3467. [Google Scholar] [CrossRef] [PubMed]

- Niu, T.; Xu, K.; Shen, C.; Sun, T.; Oberst, J.; Handwerker, C.A.; Subbarayan, G.; Wang, H.; Zhang, X. In Situ Study on Cu-to-Cu Thermal Compression Bonding. Crystals 2023, 13, 989. [Google Scholar] [CrossRef]

- Suga, T. Feasibility of surface activated bonding for ultra-fine pitch interconnection—A new concept of bump-less direct bonding for system level packaging. In Proceedings of the 50th Electronic Components & Technology Conference (ECTC 01), Las Vegas, NV, USA, 21–24 May 2000; pp. 702–705. [Google Scholar] [CrossRef]

- Roshanghias, A.; Kaczynski, J.; Rodrigues, A.; Karami, R.; Pires, M.; Burggraf, J.; Schmidt, A. 3D Integration via D2D Bump-Less Cu Bonding with Protruded and Recessed Topographies. ECS J. Solid State Sci. Technol. 2023, 12, 084001. [Google Scholar] [CrossRef]

- Tong, Q.-Y.; Fountain, G.G., Jr.; Enquist, P.M. Method for Low-Temperature Bonding and Bonded Structure. World Patent No WO2001061743A1, 23 August 2008. [Google Scholar]

- Di Cioccio, L.; Baudin, F.; Gergaud, P.; Delaye, V.; Jouneau, P.-H.; Rieutord, F.; Signamarcheix, T.J.E.T. Modeling and integration phenomena of metal-metal direct bonding technology. ECS Trans. 2014, 64, 339. [Google Scholar] [CrossRef]

- Utsumi, J.; Ide, K.; Ichiyanagi, Y. Room temperature bonding of SiO2 and SiO2 by surface activated bonding method using Si ultrathin films. Jpn. J. Appl. Phys. 2016, 55, 4. [Google Scholar] [CrossRef]

- He, R.; Fujino, M.; Yamauchi, A.; Suga, T. Combined Surface Activated Bonding Technique for Hydrophilic SiO2-SiO2 and Cu-Cu Bonding. In Proceedings of the Symposium on Semiconductor Wafer Bonding-Science, Technology and Applications 14 held during the RiME Joint Int Meeting of The Electrochemical-Society, the Electrochemical-Society-of-Japan, and the Korean-Electrochemical-Society, Honolulu, HI, USA, 2–7 October 2016; pp. 117–128. [Google Scholar] [CrossRef]

- Renaud, P.; Abadie, K.; Fournel, F.; Dubarry, C.; Baudin, F.; Tauzin, A. SAB-Enabled Room Temperature Hybrid Bonding. ECS Trans. 2023, 112, 83. [Google Scholar] [CrossRef]

- Tan, C.S.; Lim, D.F.; Singh, S.G.; Goulet, S.K.; Bergkvist, M. Cu-Cu diffusion bonding enhancement at low temperature by surface passivation using self-assembled monolayer of alkane-thiol. Appl. Phys. Lett. 2009, 95, 3. [Google Scholar] [CrossRef]

- Tan, C.S.; Lim, D.F. Cu Surface Passivation with Self-Assembled Monolayer (SAM) and Its Application for Wafer Bonding at Moderately Low Temperature. In Proceedings of the 12th International Symposium on Semiconductor Wafer Bonding-Science, Technology, and Applications, Honolulu, HI, USA, 4–9 October 2012; pp. 115–123. [Google Scholar] [CrossRef]

- Hong, Z.J.; Liu, D.M.; Hu, H.W.; Lin, M.C.; Hsieh, T.H.; Chen, K.N.; Soc, I.C. Ultra-High Strength Cu-Cu Bonding under Low Thermal Budget for Chiplet Heterogeneous Applications. In Proceedings of the IEEE 71st Electronic Components and Technology Conference (ECTC), Electronic Network, San Diego, CA, USA, 1 June–4 July 2021; pp. 347–352. [Google Scholar] [CrossRef]

- Hong, Z.J.; Liu, D.M.; Hu, H.W.; Cho, C.; Weng, M.W.; Liu, J.H.; Chen, K.N. Investigation of bonding mechanism for low-temperature Cu-Cu bonding with passivation layer. Appl. Surf. Sci. 2022, 592, 153243. [Google Scholar] [CrossRef]

- Hong, Z.J.; Liu, D.M.; Hu, H.W.; Hsiung, C.K.; Cho, C.I.; Chen, C.H.; Liu, J.H.; Weng, M.W.; Hsu, M.P.; Hung, Y.C.; et al. Low-temperature hybrid bonding with high electromigration resistance scheme for application on heterogeneous integration. Appl. Surf. Sci. 2023, 610, 155470. [Google Scholar] [CrossRef]

- Park, H.; Seo, H.; Kim, S.E. Anti-oxidant copper layer by remote mode N2 plasma for low temperature copper-copper bonding. Sci. Rep. 2020, 10, 21720. [Google Scholar] [CrossRef]

- Hahn, S.H.; Kim, W.; Shin, D.; Lee, Y.; Kim, S.; Choi, W.; Lim, K.; Moon, B.; Rhee, M. Contamination-Free Cu/SiCN Hybrid Bonding Process Development for Sub-μm Pitch Devices with Enhanced Bonding Characteristics. In Proceedings of the IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 1390–1396. [Google Scholar] [CrossRef]

- Agrawal, M.; Manohar, B.M.; Nagarajaiah, K. Cu-Cu thermo compression wafer bonding techniques for micro-system integration. Indian J. Eng. Mat. Sci. 2021, 28, 142–151. [Google Scholar]

- Chou, T.C.; Yang, K.M.; Li, J.C.; Yu, T.Y.; Yang, Y.T.; Hu, H.W.; Liu, Y.W.; Ko, C.T.; Chen, Y.H.; Tseng, T.J.; et al. Investigation of Pillar-Concave Structure for Low-Temperature Cu-Cu Direct Bonding in 3-D/2.5-D Heterogeneous Integration. IEEE Trans. Compon. Pack. Manuf. Technol. 2020, 10, 1296–1303. [Google Scholar] [CrossRef]

- Bhushan, B. Frictional heating and contact temperatures. In Modern Tribology Handbook; CRC Press: Boca Raton, FL, USA, 2000. [Google Scholar]

- Sahoo, K.; Ren, H.X.; Iyer, S.S. A High Throughput Two- Stage Die-to-Wafer Thermal Compression Bonding Scheme for Heterogeneous Integration. In Proceedings of the IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 362–366. [Google Scholar] [CrossRef]

- Kim, S.W.; Fodor, F.; Heylen, N.; Iacovo, S.; De Vos, J.; Miller, A.; Beyer, G.; Beyne, E. Novel Cu/SiCN surface topography control for 1 μm pitch hybrid wafer-to-wafer bonding. In Proceedings of the 70th IEEE Electronic Components and Technology Conference (ECTC), Electronic Network, Orlando, FL, USA, 3–30 June 2020; pp. 216–222. [Google Scholar] [CrossRef]

- Kagawa, Y.; Kamibayashi, T.; Yamano, Y.; Nishio, K.; Sakamoto, A.; Yamada, T.; Shimizu, K.; Hirano, T.; Iwamoto, H. Development of face-to-face and face-to-back ultra-fine pitch Cu-Cu hybrid bonding. In Proceedings of the 72nd IEEE Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May–1 June 2022; pp. 306–311. [Google Scholar] [CrossRef]

- Kagawa, Y.; Kamibayashi, T.; Fujii, N.; Furuse, S.; Yamada, T.; Hirano, T.; Iwamoto, H. Cu-Cu Wiring: The Novel Structure of Cu-Cu Hybrid Bonding. In Proceedings of the IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 103–108. [Google Scholar] [CrossRef]

- Otsuka, T.S.K. Modified SAB Methods for Hybrid and All-Cu Bonding for 3D Integration below 200 °C. ECS Trans. 2023, 112, 103. [Google Scholar] [CrossRef]

- De Messemaeker, J.; Witters, L.; Zhang, B.Y.; Tsau, Y.W.; Fodor, F.; De Vos, J.; Beyer, G.; Croes, K.; Beyne, E. New Cu “Bulge-Out” Mechanism Supporting Sub Micron Scaling of Hybrid Wafer-to-Wafer Bonding. In Proceedings of the IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 109–113. [Google Scholar] [CrossRef]

- Liu, C.M.; Lin, H.W.; Chu, Y.C.; Chen, C.; Lyu, D.R.; Chen, K.N.; Tu, K.N. Low-temperature direct copper-to-copper bonding enabled by creep on highly (111)-oriented Cu surfaces. Scr. Mater. 2014, 78–79, 65–68. [Google Scholar] [CrossRef]

- Tseng, C.H.; Tu, K.N.; Chen, C. Comparison of oxidation in uni-directionally and randomly oriented Cu films for low temperature Cu-to-Cu direct bonding. Sci. Rep. 2018, 8, 10671. [Google Scholar] [CrossRef]

- Shie, K.C.; Gusak, A.M.; Tu, K.N.; Chen, C. A kinetic model of copper-to-copper direct bonding under thermal compression. J. Mater. Res. Technol.-JMRT 2021, 15, 2332–2344. [Google Scholar] [CrossRef]

- Liu, T.C.; Liu, C.M.; Hsiao, H.Y.; Lu, J.L.; Huang, Y.S.; Chen, C. Fabrication and Characterization of (111)-Oriented and Nanotwinned Cu by Dc Electrodeposition. Cryst. Growth Des. 2012, 12, 5012–5016. [Google Scholar] [CrossRef]

- Shie, K.C.; Juang, J.Y.; Chen, C. Instant Cu-to-Cu direct bonding enabled by ⟨111⟩-oriented nanotwinned Cu bumps. Jpn. J. Appl. Phys. 2020, 59, SBBA03. [Google Scholar] [CrossRef]

- Ong, J.J.; Chiu, W.L.; Lee, O.H.; Chiang, C.W.; Chang, H.H.; Wang, C.H.; Shie, K.C.; Yang, S.C.; Tran, D.P.; Tu, K.N.; et al. Low-Temperature Cu/SiO2 Hybrid Bonding with Low Contact Resistance Using (111)-Oriented Cu Surfaces. Materials 2022, 15, 1888. [Google Scholar] [CrossRef]

- Schmidt, R.; Schwarz, C.; Kirbach, U.; Jäger, C.; Soc, I.C. Towards Copper-Copper Direct Bonding: Controlled Crystal Growth of Copper Deposits for Minimization of Interface Formation During Bonding. In Proceedings of the IEEE 71st Electronic Components and Technology Conference (ECTC), Electronic Network, San Diego, CA, USA, 1 June–4 July 2021; pp. 1922–1927. [Google Scholar] [CrossRef]

- Schmidt, R.; Schwarz, C. Optimization of the Cu Microstructure to Improve Copper-to-Copper Direct Bonding for 3D Integration. In Proceedings of the IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 2024–2028. [Google Scholar] [CrossRef]

- He, C.; Zhou, J.Z.; Zhou, R.; Chen, C.; Jing, S.Y.; Mu, K.Y.; Huang, Y.T.; Chung, C.C.; Cherng, S.J.; Lu, Y.; et al. Nanocrystalline copper for direct copper-to-copper bonding with improved cross-interface formation at low thermal budget. Nat. Commun. 2024, 15, 7095. [Google Scholar] [CrossRef] [PubMed]

- Park, J.; Kang, S.; Kim, M.E.; Kim, N.J.; Kim, J.; Kim, S.; Kim, K.M. Advanced Cu/Polymer Hybrid Bonding System for Fine-Pitch 3D Stacking Devices. Adv. Mater. Technol. 2023, 8, 2202134. [Google Scholar] [CrossRef]

- Ji, L.; Che, F.X.; Ji, H.M.; Li, H.Y.; Kawano, M. Modelling and characterization of wafer-to-wafer hybrid bonding technology for 3D IC packaging. In Proceedings of the IEEE 21st Electronics Packaging Technology Conference (EPTC), Singapore, 4–6 December 2019; pp. 87–94. [Google Scholar] [CrossRef]

- Isobe, A. A study of CMP Edge Profile for Production Wafers. In Proceedings of the ICPT 2017, Leuven, Belgium, 11–13 October 2017. [Google Scholar]

- Yoneda, S.; Adachi, K.; Kobayashi, K.; Matsukawa, D.; Sasaki, M.; Itabashi, T.; Shirasaka, T.; Shibata, T.; Soc, I.C. A Novel Photosensitive Polyimide Adhesive Material for Hybrid Bonding Processing. In Proceedings of the IEEE 71st Electronic Components and Technology Conference (ECTC), Electronic Network, San Diego, CA, USA, 1 June–4 July 2021; pp. 680–686. [Google Scholar] [CrossRef]

- Shirasaka, T.; Okuda, T.; Shibata, T.; Yoneda, S.; Matsukawa, D.; Mariappan, M.; Koyanagi, M.; Fukushima, T. Comprehensive Study on Advanced Chip on Wafer Hybrid Bonding with Copper/Polyimide Systems. In Proceedings of the 72nd IEEE Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May–1 June 2022; pp. 317–323. [Google Scholar] [CrossRef]

- Jang, S.; Lee, S.; Park, S.; Kim, S.E. Fly Cutting for Polymer Planarization in Hybrid Cu Bonding. In Proceedings of the ICEP 2024, Toyama, Japan, 17–20 April 2024. [Google Scholar] [CrossRef]

- Kundu, S.; Roy, R.; Rahman, M.S.; Upadhyay, S.; Topaloglu, R.O.; Mohney, S.E.; Huang, S.; Ghosh, S. Exploring Topological Semi-Metals for Interconnects. J. Low Power Electron. Appl. 2023, 13, 16. [Google Scholar] [CrossRef]

- Lanzillo, N.A.; Bajpai, U.; Chen, C.-T. Topological Semimetal Interface Resistivity Scaling for Vertical Interconnect Applications. Appl. Phys. Lett. 2024, 124, 181603. [Google Scholar] [CrossRef]

- Kim, S.H.; Seo, J.; Koo, J.; Chang, J.; Jin, G.; Han, H.J. Topological Semimetals for Advanced Node Interconnects. iScience 2024, 27, 111460. [Google Scholar] [CrossRef]

- Dutta, S.; Chang, S.C.; Kani, N.; Nikonov, D.E.; Manipatruni, S.; Young, I.A.; Naeemi, A. Non-Volatile Clocked Spin Wave Interconnect for Beyond-CMOS Nanomagnet Pipelines. Sci. Rep. 2015, 5, 9861. [Google Scholar] [CrossRef]

| Bonding Method | Pitch (μm) | Bonding Conditions | Key Features | Reference |

|---|---|---|---|---|

| Direct hybrid bonding (Surface plasma activation) | 5 | Room temp., 0.3 MPa | Defect-free and good grinding resistant | [32] |

| Cluster-Ag passivation | ~15 | 150 °C | 3.77 MPa (Pull test) and 21.95 MPa (Shear test) | [37] |

| N2 plasma treatment/Passivation | 0.4–0.7 | NA | Void-free, well Cu-Cu inter-diffused and well-aligned | [39] |

| Pillar–Concave Structure | ~25 | 200 °C, 500 MPa | Early breakdown of polyimide/concave interface in shear test | [41] |

| All-Cu 3D interconnect | 2 | <200 °C | Simple process | [47] |

| High throughput two-stage TCB | 7 | 300 °C and 100 MPa or 400 °C and 50 MPa (annealing) | No bonding interface observed | [43] |

| Cu-Cu Wiring | 1.4 | NA | Simple process | [46] |

| Unequal submicron-sized pads | 0.7 | 230 °C to 350 °C (post-bond annealing) | Complicated in design, variation in contact resistance | [48] |

| Crystalline (111)-Oriented Nano-twinned Cu | 20 | 200 °C, 1.06 MPa | Thermal and electrical stability up to 375 °C | [54] |

| Crystalline metastable microstructure | -- | 200 °C | To monitor grain growth on the bonding surface | [55,56] |

| Photosensitive polyimide adhesive | 20 | 250–350 °C, 2–6 MPa | Shear test 4–4.5 MPa | [61] |

| Citric or ascorbic aqueous treatment | 20 | 250 °C, 5 MPa | Shear test > 20 MPa | [62] |

| Fly cutting (Cu/polymer hybrid bonding) | -- | 200°C | No voids at PI-PI interface, some seams at Cu-Cu interface | [63] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bao, W.; Zhang, J.; Wong, H.; Liu, J.; Li, W. Emerging Copper-to-Copper Bonding Techniques: Enabling High-Density Interconnects for Heterogeneous Integration. Nanomaterials 2025, 15, 729. https://doi.org/10.3390/nano15100729

Bao W, Zhang J, Wong H, Liu J, Li W. Emerging Copper-to-Copper Bonding Techniques: Enabling High-Density Interconnects for Heterogeneous Integration. Nanomaterials. 2025; 15(10):729. https://doi.org/10.3390/nano15100729

Chicago/Turabian StyleBao, Wenhan, Jieqiong Zhang, Hei Wong, Jun Liu, and Weidong Li. 2025. "Emerging Copper-to-Copper Bonding Techniques: Enabling High-Density Interconnects for Heterogeneous Integration" Nanomaterials 15, no. 10: 729. https://doi.org/10.3390/nano15100729

APA StyleBao, W., Zhang, J., Wong, H., Liu, J., & Li, W. (2025). Emerging Copper-to-Copper Bonding Techniques: Enabling High-Density Interconnects for Heterogeneous Integration. Nanomaterials, 15(10), 729. https://doi.org/10.3390/nano15100729