Relation Between Thickness and TFTs Properties of HfO2 Dielectric Layer Synthesized by Plasma-Enhanced Atomic Layer Deposition

Abstract

1. Introduction

2. Materials and Methods

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- De Stefano, S.; Durante, O.; D’orsi, R.; Operamolla, A.; Ambrico, M.; Ambrico, P.F.; Martucciello, N.; Giubileo, F.; Di Bartolomeo, A. Resistive switching memory from dielectric lignin for sustainable electronics. J. Mater. Chem. C 2024, 12, 13621–13631. [Google Scholar] [CrossRef]

- Zhang, J.; Fu, Y.; Wang, C.; Chen, P.-C.; Liu, Z.; Wei, W.; Wu, C.; Thompson, M.E.; Zhou, C. Separated Carbon Nanotube Macroelectronics for Active Matrix Organic Light-Emitting Diode Displays. Nano Lett. 2011, 11, 4852–4858. [Google Scholar] [CrossRef]

- Zhou, L.; Xu, M.; Xia, X.-H.; Zou, J.-H.; Zhang, L.-R.; Luo, D.-X.; Wu, W.-J.; Wang, L.; Peng, J.-B. Power Consumption Model for AMOLED Display Panel Based on 2T-1C Pixel Circuit. J. Disp. Technol. 2016, 12, 1064–1069. [Google Scholar] [CrossRef]

- Meng, Z.; Wong, M. Active-matrix organic light-emitting diode displays realized using metal-induced unilaterally crystallized polycrystalline silicon thin-film transistors. IEEE Trans. Electron Devices 2002, 49, 991–996. [Google Scholar] [CrossRef]

- D’Orsi, R.; Irimia, C.V.; Lucejko, J.J.; Kahraman, B.; Kanbur, Y.; Yumusak, C.; Bednorz, M.; Babudri, F.; Irimia-Vladu, M.; Operamolla, A. Kraft Lignin: From Pulping Waste to Bio-Based Dielectric Polymer for Organic Field-Effect Transistors. Adv. Sustain. Syst. 2022, 6, 2200285. [Google Scholar] [CrossRef]

- Park, J.S.; Maeng, W.-J.; Kim, H.-S.; Park, J.-S. Review of recent developments in amorphous oxide semiconductor thin-film transistor devices. Thin Solid Films 2012, 520, 1679–1693. [Google Scholar] [CrossRef]

- Xu, G.; Liu, M.; Yang, Y.; Cai, L.; Wang, Z.; Wu, Q.; Lu, C.; Zhao, Z.; Zhao, Y.; Geng, D.; et al. Field-Dependent Mobility Enhancement and Contact Resistance in a-IGZO TFTs. IEEE Trans. Electron Devices 2019, 66, 5166–5169. [Google Scholar] [CrossRef]

- Li, X.; Geng, D.; Mativenga, M.; Chen, Y.; Jang, J. Effect of Bulk-Accumulation on Switching Speed of Dual-Gate a-IGZO TFT-Based Circuits. IEEE Electron Device Lett. 2014, 35, 1242–1244. [Google Scholar] [CrossRef]

- Nigro, R.L.; Fiorenza, P.; Greco, G.; Schilirò, E.; Roccaforte, F. Structural and Insulating Behaviour of High-Permittivity Binary Oxide Thin Films for Silicon Carbide and Gallium Nitride Electronic Devices. Materials 2022, 15, 830. [Google Scholar] [CrossRef] [PubMed]

- Buchanan, D.A. Scaling the gate dielectric: Materials, integration, and reliability. IBM J. Res. Dev. 1999, 43, 245–264. [Google Scholar] [CrossRef]

- Kingon, A.I.; Maria, J.-P.; Streiffer, S.K. Alternative dielectrics to silicon dioxide for memory and logic devices. Nature 2000, 406, 1032–1038. [Google Scholar] [CrossRef]

- Xie, J.; Zhu, Z.; Tao, H.; Zhou, S.; Liang, Z.; Li, Z.; Yao, R.; Wang, Y.; Ning, H.; Peng, J. Research Progress of High Dielectric Constant Zirconia-Based Materials for Gate Dielectric Application. Coatings 2020, 10, 698. [Google Scholar] [CrossRef]

- Chang, J.P. High-k Gate Dielectric Deposition Technologies. In High Dielectric Constant Materials; Huff, H.R., Gilmer, D.C., Eds.; Springer Series in Advanced Microelectronics; Springer-Verlag: Berlin/Heidelberg, 2005; Volume 16, pp. 379–413. ISBN 978-3-540-21081-8. [Google Scholar]

- Triyoso, D.H.; Hegde, R.I.; Grant, J.; Fejes, P.; Liu, R.; Roan, D.; Ramon, M.; Werho, D.; Rai, R.; La, L.B.; et al. Film properties of ALD HfO2 and La2O3 gate dielectrics grown on Si with various pre-deposition treatments. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. 2004, 22, 2121–2127. [Google Scholar] [CrossRef]

- Zhang, X.-Y.; Han, J.; Peng, D.-C.; Ruan, Y.-J.; Wu, W.-Y.; Wuu, D.-S.; Huang, C.-J.; Lien, S.-Y.; Zhu, W.-Z. Crystallinity Effect on Electrical Properties of PEALD–HfO2 Thin Films Prepared by Different Substrate Temperatures. Nanomaterials 2022, 12, 3890. [Google Scholar] [CrossRef]

- Chen, Q.-Z.; Shi, C.-Y.; Zhao, M.-J.; Gao, P.; Wu, W.-Y.; Wuu, D.-S.; Horng, R.-H.; Lien, S.-Y.; Zhu, W.-Z. Performance of Transparent Indium-Gallium-Zinc Oxide Thin Film Transistor Prepared by All Plasma Enhanced Atomic Layer Deposition. IEEE Electron Device Lett. 2023, 44, 448–451. [Google Scholar] [CrossRef]

- Li, Z.; Wei, J.; Meng, J.; Liu, Y.; Yu, J.; Wang, T.; Xu, K.; Liu, P.; Zhu, H.; Chen, S.; et al. The Doping Effect on the Intrinsic Ferroelectricity in Hafnium Oxide-Based Nano-Ferroelectric Devices. Nano Lett. 2023, 23, 4675–4682. [Google Scholar] [CrossRef]

- Chen, H.-B.; Hsu, C.-H.; Wu, W.-Y.; Zhang, J.; Zhang, X.-Y.; Gao, P.; Wuu, D.-S.; Lai, F.-M.; Lien, S.-Y.; Zhu, W.-Z. Substrate temperature effects on PEALD HfAlO dielectric films for IGZO-TFT applications. Appl. Surf. Sci. 2024, 665, 160305. [Google Scholar] [CrossRef]

- Vulpe, S.; Nastase, F.; Dragoman, M.; Dinescu, A.; Romanitan, C.; Iftimie, S.; Moldovan, A.; Apostol, N. Physical properties of the ferroelectric capacitors based on Al-doped HfO2 grown via Atomic Layer Deposition on Si. Appl. Surf. Sci. 2019, 483, 324–333. [Google Scholar] [CrossRef]

- Materlik, R.; Künneth, C.; Kersch, A. The origin of ferroelectricity in Hf1−xZrxO2: A computational investigation and a surface energy model. J. Appl. Phys. 2015, 117, 134109. [Google Scholar] [CrossRef]

- Thornton, J.A. Influence of apparatus geometry and deposition conditions on the structure and topography of thick sputtered coatings. J. Vac. Sci. Technol. 1974, 11, 666–670. [Google Scholar] [CrossRef]

- Böscke, T.S.; Müller, J.; Bräuhaus, D.; Schröder, U.; Böttger, U. Ferroelectricity in hafnium oxide thin films. Appl. Phys. Lett. 2011, 99, 102903. [Google Scholar] [CrossRef]

- Hu, J.; Wang, J.; Wei, Y.; Wu, Q.; Zhang, F.; Xu, Q. Effect of film growth thickness on the refractive index and crystallization of HfO2 film. Ceram. Int. 2021, 47, 33751–33757. [Google Scholar] [CrossRef]

- Durante, O.; Di Giorgio, C.; Granata, V.; Neilson, J.; Fittipaldi, R.; Vecchione, A.; Carapella, G.; Chiadini, F.; DeSalvo, R.; Dinelli, F.; et al. Emergence and Evolution of Crystallization in TiO2 Thin Films: A Structural and Morphological Study. Nanomaterials 2021, 11, 1409. [Google Scholar] [CrossRef]

- Hughes, M.P.; Rosenthal, K.D.; Ran, N.A.; Seifrid, M.; Bazan, G.C.; Nguyen, T. Determining the Dielectric Constants of Organic Photovoltaic Materials Using Impedance Spectroscopy. Adv. Funct. Mater. 2018, 28, 1801542. [Google Scholar] [CrossRef]

- Cui, J.; Park, J.; Kim, D.W.; Choi, M.; Chung, H.Y.; Kwon, O.K.; Kwon, J.E.; Park, S.Y. Designing Nonfullerene Acceptors with Oligo (Ethylene Glycol) Side Chains: Unraveling the Origin of Increased Open-Circuit Voltage and Balanced Charge Carrier Mobilities. Chem. Asian J. 2021, 16, 2481–2488. [Google Scholar] [CrossRef]

- Zhao, M.-J.; Wang, Y.-T.; Yan, J.-H.; Li, H.-C.; Xu, H.; Wuu, D.-S.; Wu, W.-Y.; Cho, Y.-S.; Lien, S.-Y. Ultra-low subthreshold swing in oxide TFTs via HiPIMS high-k HfO2 gate dielectric using atmosphere annealing. Appl. Surf. Sci. 2024, 685, 162068. [Google Scholar] [CrossRef]

- Zhang, X.-Y.; Han, J.; Wang, Y.-T.; Ruan, Y.-J.; Wu, W.-Y.; Wuu, D.-S.; Zuo, J.; Lai, F.-M.; Lien, S.-Y.; Zhu, W.-Z. Effect on passivation mechanism and properties of HfO2/crystalline-Si interface under different annealing atmosphere. Sol. Energy Mater. Sol. Cells 2023, 257, 112384. [Google Scholar] [CrossRef]

- Zhang, X.-Y.; Hsu, C.-H.; Cho, Y.-S.; Lien, S.-Y.; Zhu, W.-Z.; Chen, S.-Y.; Huang, W.; Xie, L.-G.; Chen, L.-D.; Zou, X.-Y.; et al. Simulation and Fabrication of HfO2 Thin Films Passivating Si from a Numerical Computer and Remote Plasma ALD. Appl. Sci. 2017, 7, 1244. [Google Scholar] [CrossRef]

- Oulachgar, E.H.; Aktik, C.; Scarlete, M.; Dostie, S.; Sowerby, R.; Gujrathi, S. Electrical and optical characterization of SiONC dielectric thin film deposited by polymer-source chemical vapor deposition. J. Appl. Phys. 2007, 101, 084107. [Google Scholar] [CrossRef]

- Lee, K.-M.; Ju, B.-K.; Choi, S.-H. a-InGaZnO Thin-Film Transistors With Novel Atomic Layer-Deposited HfO2 Gate Insulator Using Two Types of Reactant Gases. IEEE Trans. Electron Devices 2022, 70, 127–134. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef]

- Li, J.; Zhang, Y.; Wang, J.; Yang, H.; Zhou, X.; Chan, M.; Wang, X.; Lu, L.; Zhang, S. Near-Ideal Top-Gate Controllability of InGaZnO Thin-Film Transistors by Suppressing Interface Defects with an Ultrathin Atomic Layer Deposited Gate Insulator. ACS Appl. Mater. Interfaces 2023, 15, 8666–8675. [Google Scholar] [CrossRef]

- Li, P.; Yang, J.; Ding, X.; Li, X.; Zhang, J. High-Performance of InGaZnO TFTs with an Ultrathin 5-nm Al2O3 Gate Dielectric Enabled by a Novel Atomic Layer Deposition Method. IEEE J. Electron Devices Soc. 2024, 12, 121–126. [Google Scholar] [CrossRef]

- Ma, P.; Sun, J.; Liang, G.; Li, Y.; Xin, Q.; Li, Y.; Song, A. Half-volt operation of IGZO thin-film transistors enabled by ultrathin HfO2 gate dielectric. Appl. Phys. Lett. 2018, 113, 063501. [Google Scholar] [CrossRef]

- Chen, H.-B.; Wu, W.-Y.; Wang, Y.-T.; Yan, J.-H.; Zhao, M.-J.; Zhang, X.-Y.; Gao, P.; Wuu, D.-S.; Lai, F.-M.; Lien, S.-Y.; et al. PEALD deposited aluminum hafnium mixed oxide dielectrics for amorphous-IGZO TFTs. Ceram. Int. 2023, 50, 5350–5362. [Google Scholar] [CrossRef]

- Cai, W.; Park, S.; Zhang, J.; Wilson, J.; Li, Y.; Xin, Q.; Majewski, L.; Song, A. One-Volt IGZO Thin-Film Transistors with Ultra-Thin, Solution-Processed AlxOy Gate Dielectric. IEEE Electron Device Lett. 2018, 39, 375–378. [Google Scholar] [CrossRef]

- Yao, R.; Zheng, Z.; Xiong, M.; Zhang, X.; Li, X.; Ning, H.; Fang, Z.; Xie, W.; Lu, X.; Peng, J. Low-temperature fabrication of sputtered high-k HfO2 gate dielectric for flexible a-IGZO thin film transistors. Appl. Phys. Lett. 2018, 112, 103503. [Google Scholar] [CrossRef]

- Fan, C.-L.; Tseng, F.-P.; Tseng, C.-Y. Electrical Performance and Reliability Improvement of Amorphous-Indium-Gallium-Zinc-Oxide Thin-Film Transistors with HfO2 Gate Dielectrics by CF4 Plasma Treatment. Materials 2018, 11, 824. [Google Scholar] [CrossRef]

- Liu, Y.; Yu, Y.; Li, T.; Hu, Y.; Unnithan, R.; Skafidas, E. High Performance and High Yield Solution Processed IGZO Thin Film Transistors Fabricated with Low-Temperature Annealed Hafnium Dioxide Gate Dielectric. Adv. Electron. Mater. 2023, 9, 2300415. [Google Scholar] [CrossRef]

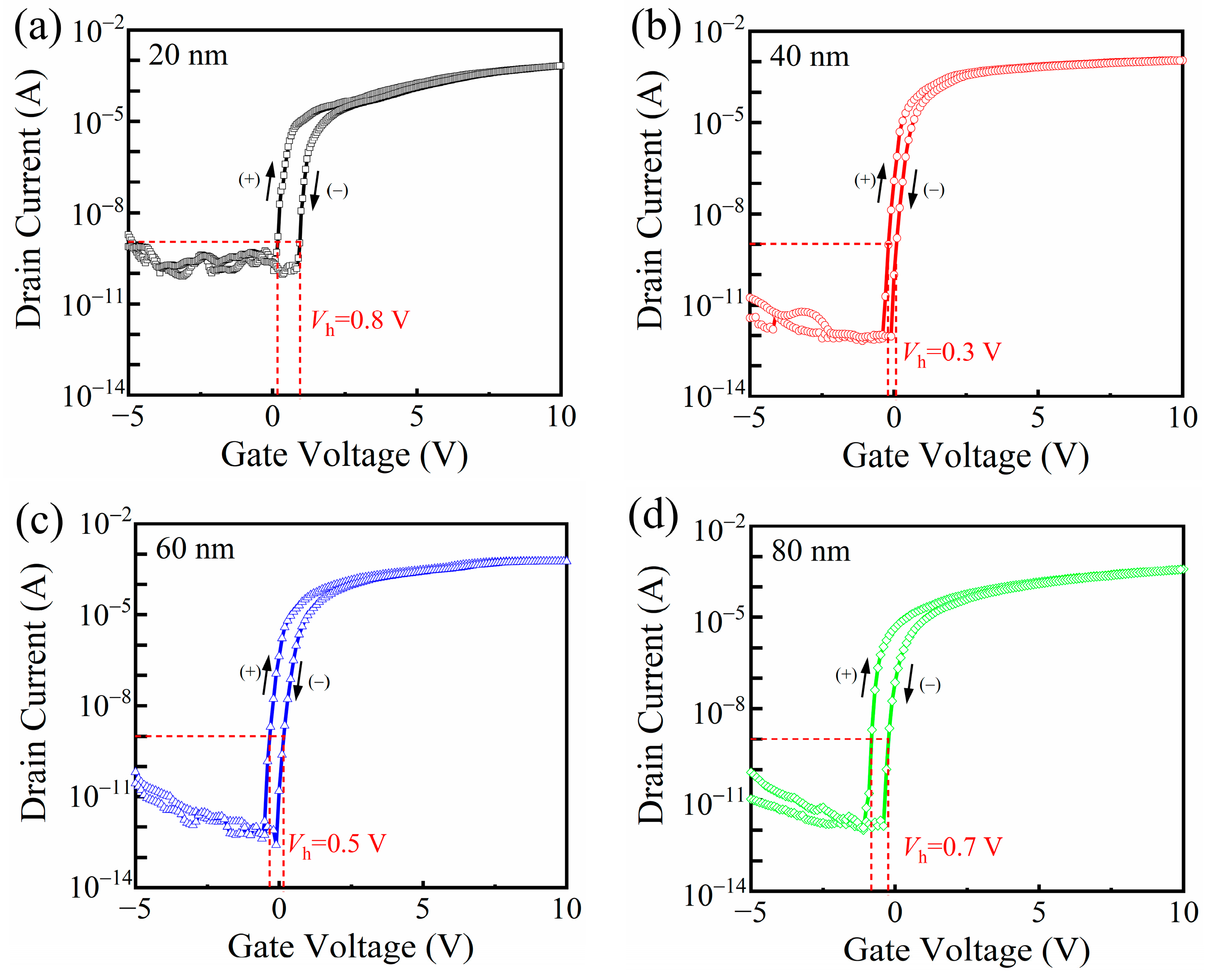

| Thickness (nm) | Vth (V) | Ion/Ioff | μsat (cm−2/Vs) | SS (V/dec) | Nt (/cm2) | Dit | Qf |

|---|---|---|---|---|---|---|---|

| 20 nm | −0.1 ± 0.15 | 7.05 × 106 | 3.76 ± 0.18 | 0.138 ± 0.013 | 3.28 × 1011 | 1.26 × 1011 | 1.88 × 1012 |

| 40 nm | −0.2 ± 0.12 | 1.35 × 109 | 6.76 ± 0.22 | 0.084 ± 0.010 | 1.14 × 1011 | 2.59 × 1011 | 2.15 × 1012 |

| 60 nm | −0.4 ± 0.19 | 1.14 × 109 | 5.84 ± 0.21 | 0.114 ± 0.011 | 1.65 × 1011 | 2.71 × 1011 | 2.35 × 1012 |

| 80 nm | −1.1 ± 0.27 | 3.32 × 108 | 3.25 ± 0.15 | 0.146 ± 0.015 | 1.82 × 1011 | 3.17 × 1011 | 2.76 × 1012 |

| Dielectric Layer | Vth (V) | Ion/Ioff | μ (cm−2/Vs) | SS (V/dec) | Nt (/cm2) | Ref. |

|---|---|---|---|---|---|---|

| HfO2 (ALD) | 0.3 | 8.0 × 106 | 4.6 | 0.075 | N.A. | [35] |

| HfO2 (ALD) | 1.52 | 1.18 × 107 | 16.75 | 0.159 | 1.54 × 1012 | [31] |

| HfO2 (Sputtering) | 1.1 | 4.3 × 107 | 10.3 | 0.28 | N.A. | [38] |

| HfO2 (Sputtering) | 1.5 | 3.5 × 106 | 30.2 | 0.17 | N.A. | [39] |

| HfO2 (Solution) | −0.3 | N.A. | 85 | 0.140 | N.A. | [40] |

| Al2O3 (Solution) | 0.48 | 1.6 × 106 | 5.40 | 0.068 | 8.5 × 1011 | [37] |

| HfO2 (ALD) | −0.2 ± 0.12 | 1.35 × 109 | 6.76 ± 0.22 | 0.084 ± 0.010 | 1.14 × 1011 | This Work |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, Q.; Fu, W.; Han, J.; Zhang, X.; Lien, S.-Y. Relation Between Thickness and TFTs Properties of HfO2 Dielectric Layer Synthesized by Plasma-Enhanced Atomic Layer Deposition. Nanomaterials 2025, 15, 719. https://doi.org/10.3390/nano15100719

Chen Q, Fu W, Han J, Zhang X, Lien S-Y. Relation Between Thickness and TFTs Properties of HfO2 Dielectric Layer Synthesized by Plasma-Enhanced Atomic Layer Deposition. Nanomaterials. 2025; 15(10):719. https://doi.org/10.3390/nano15100719

Chicago/Turabian StyleChen, Qizhen, Wanqiang Fu, Jing Han, Xiaoying Zhang, and Shui-Yang Lien. 2025. "Relation Between Thickness and TFTs Properties of HfO2 Dielectric Layer Synthesized by Plasma-Enhanced Atomic Layer Deposition" Nanomaterials 15, no. 10: 719. https://doi.org/10.3390/nano15100719

APA StyleChen, Q., Fu, W., Han, J., Zhang, X., & Lien, S.-Y. (2025). Relation Between Thickness and TFTs Properties of HfO2 Dielectric Layer Synthesized by Plasma-Enhanced Atomic Layer Deposition. Nanomaterials, 15(10), 719. https://doi.org/10.3390/nano15100719