A Dual-Mode CMOS Power Amplifier with an External Power Amplifier Driver Using 40 nm CMOS for Narrowband Internet-of-Things Applications

Abstract

1. Introduction

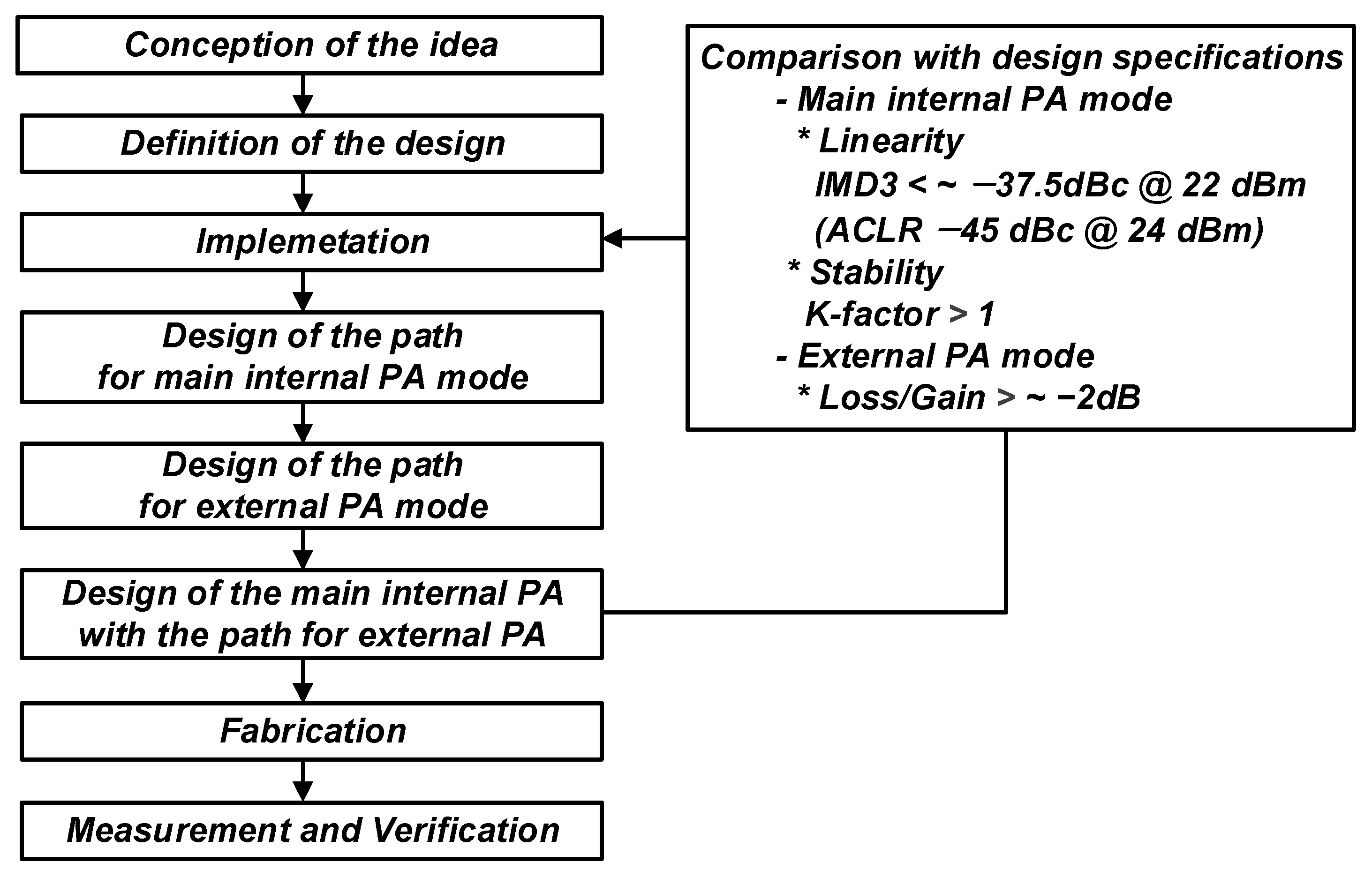

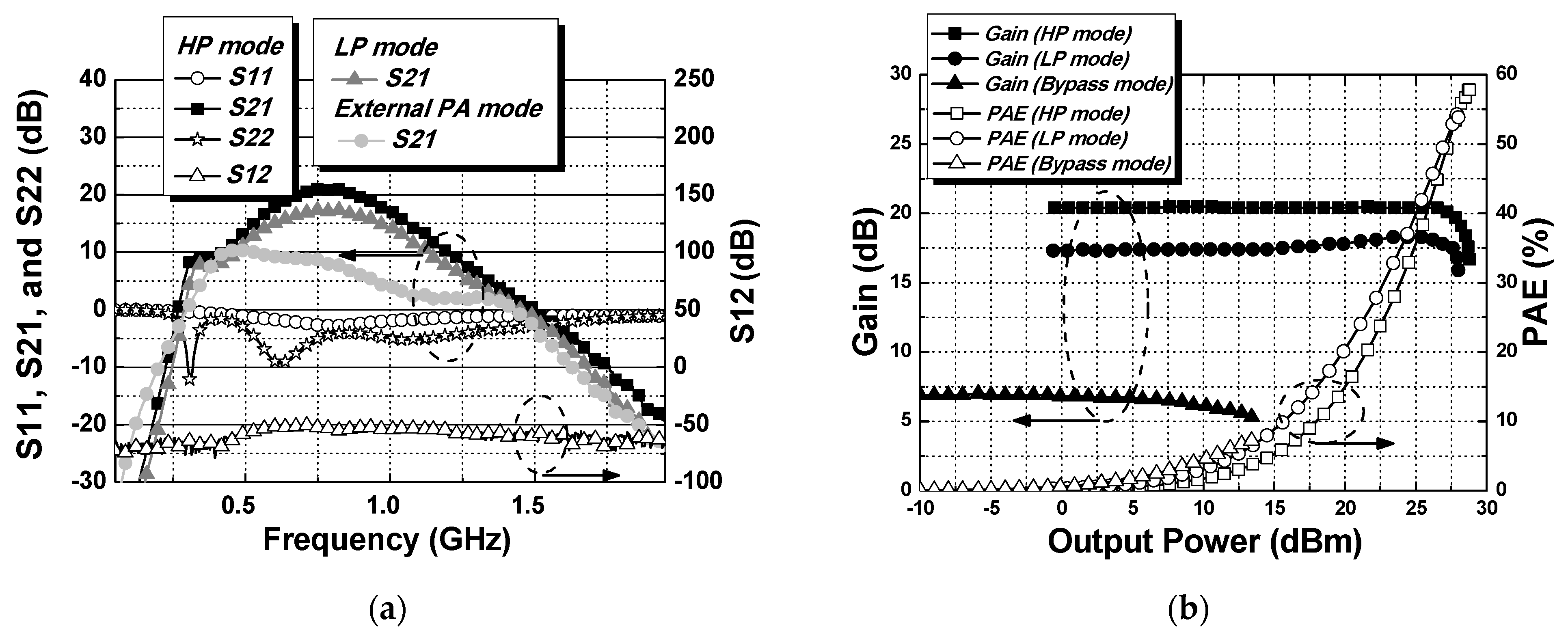

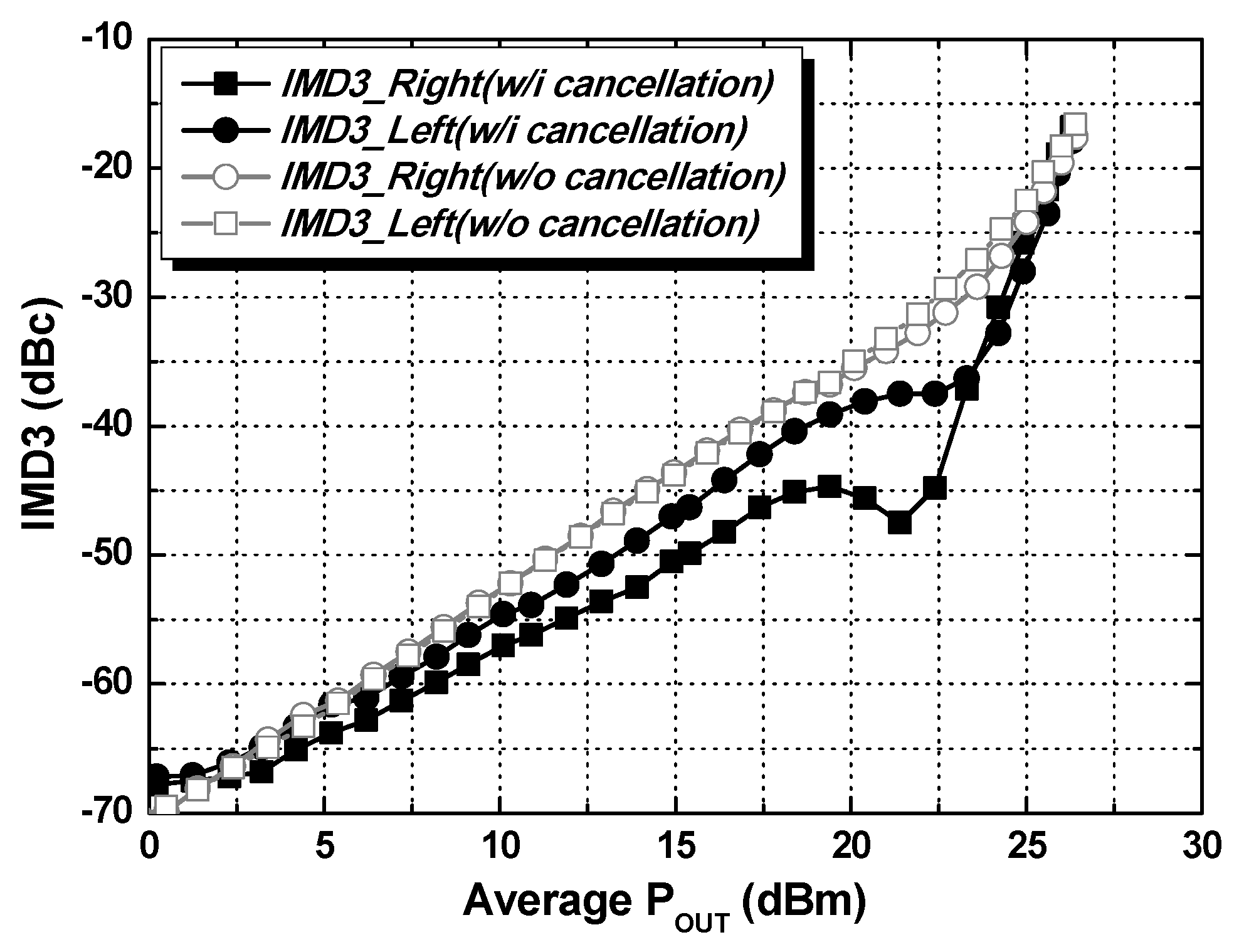

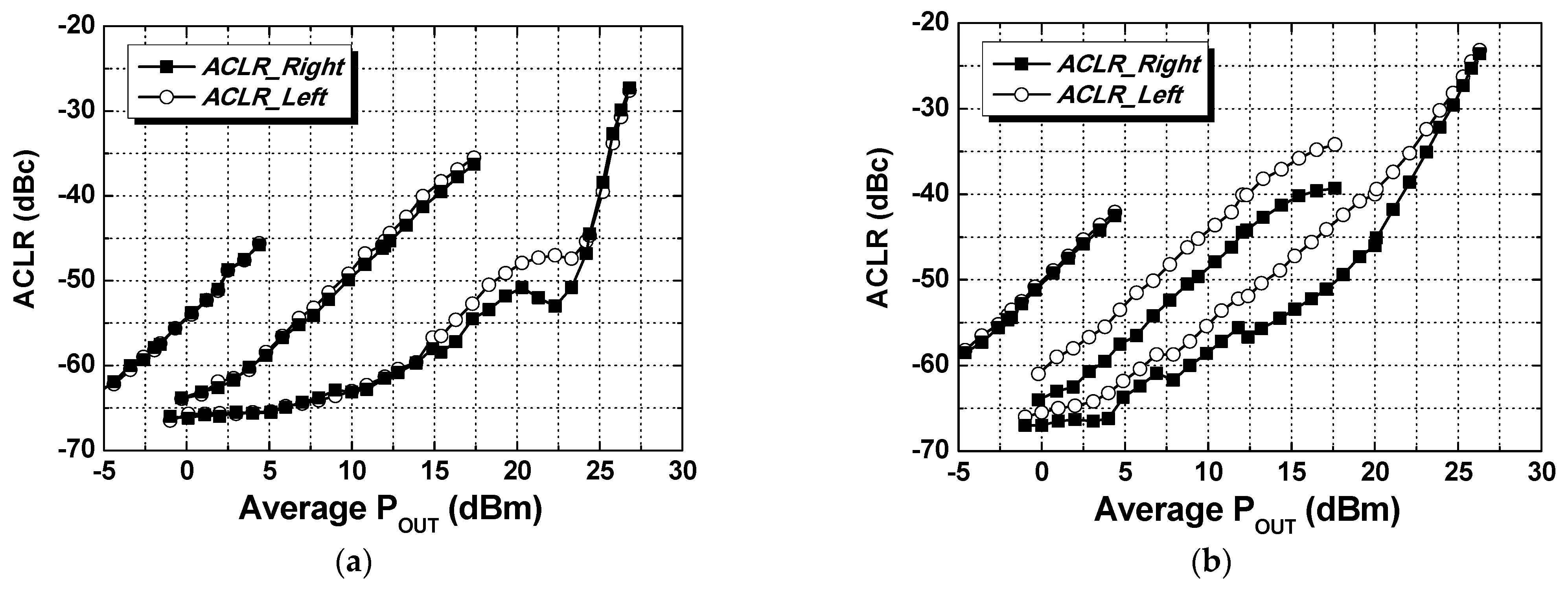

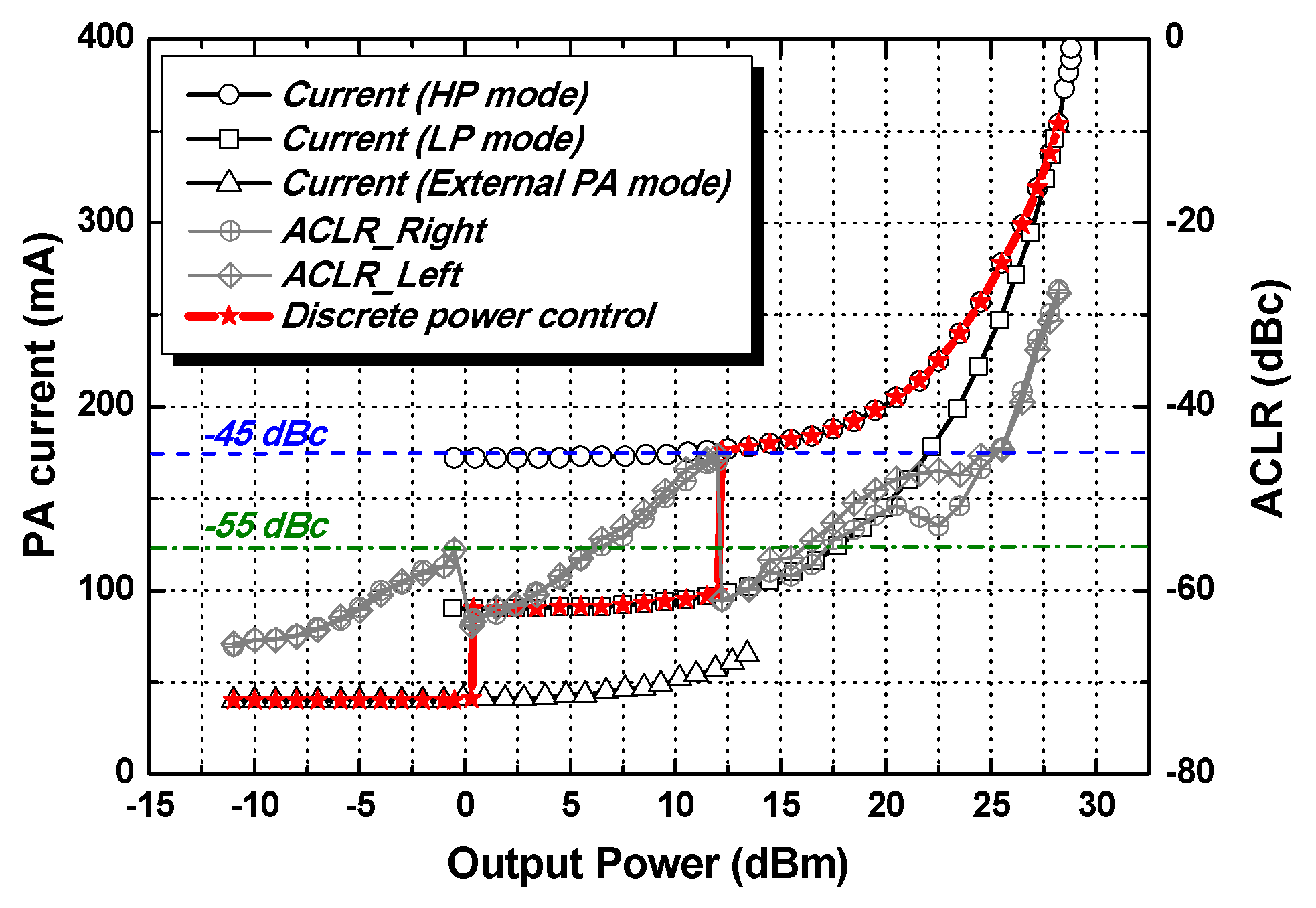

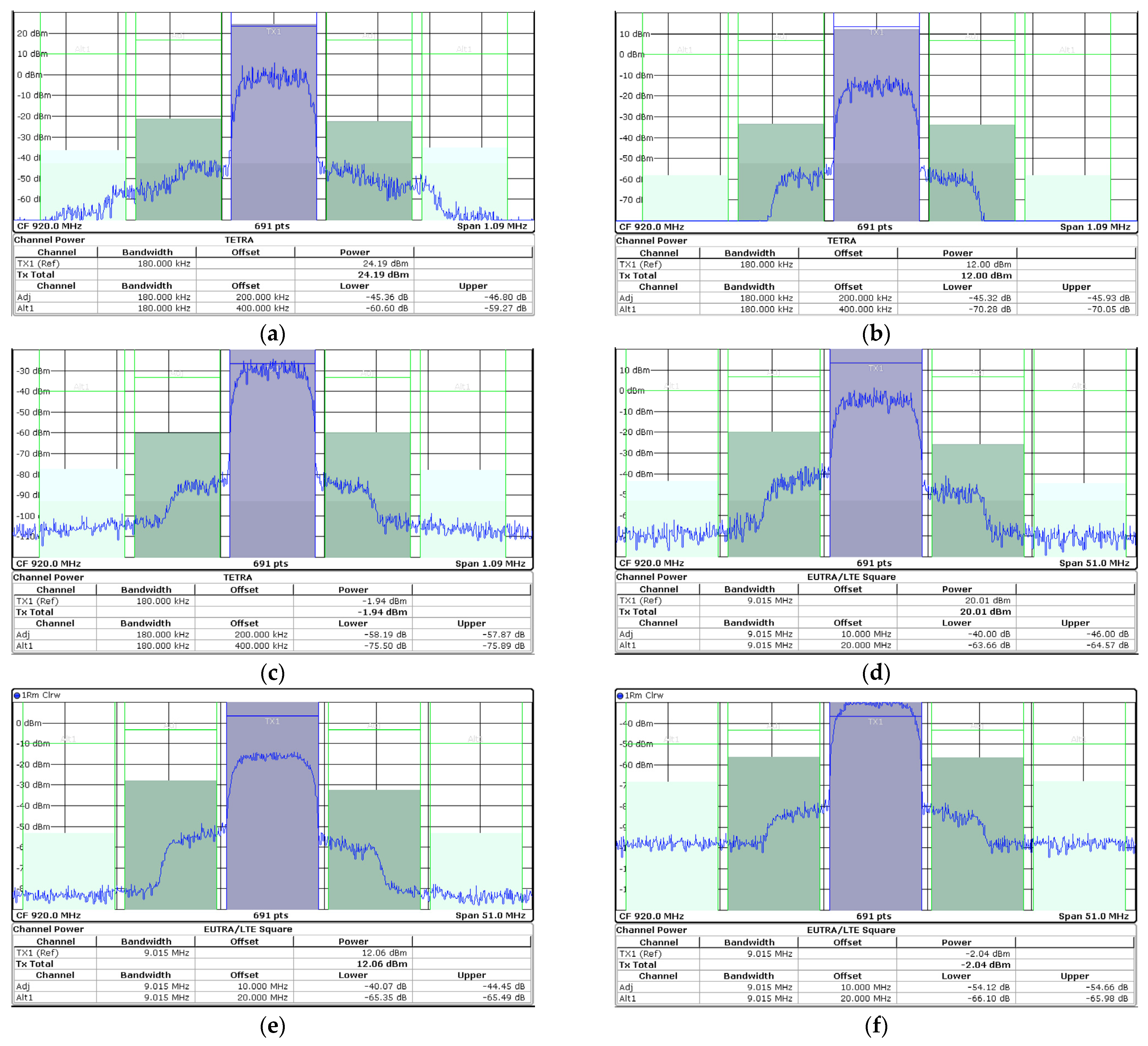

2. Design of Dual-Mode PA with an External PA Driver

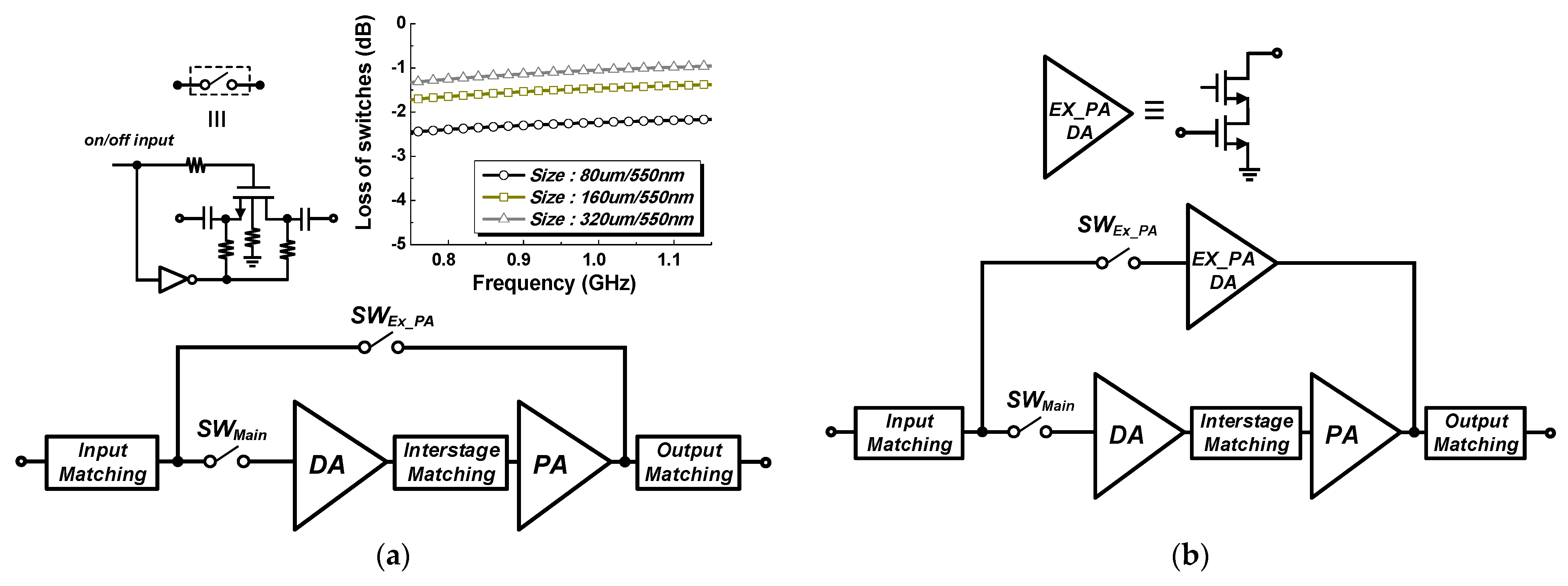

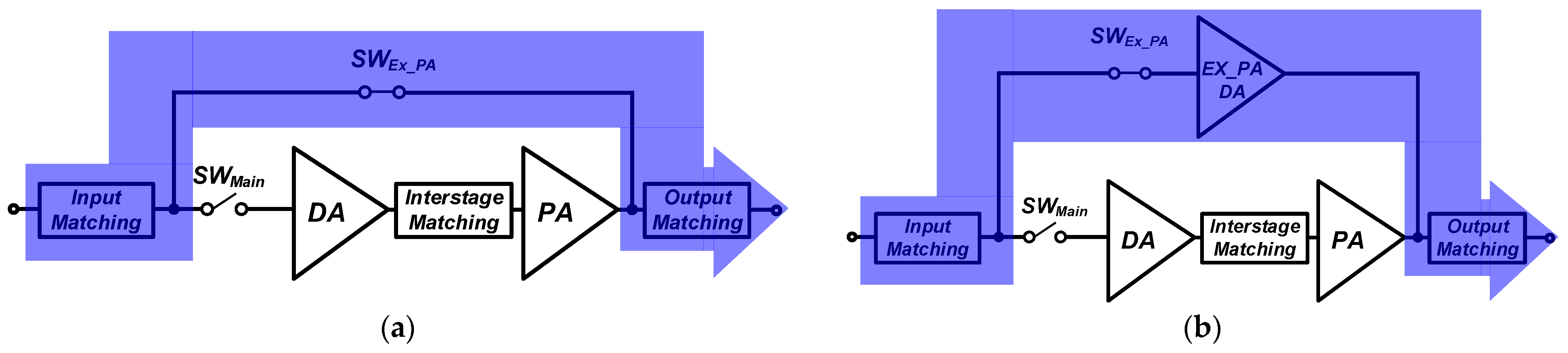

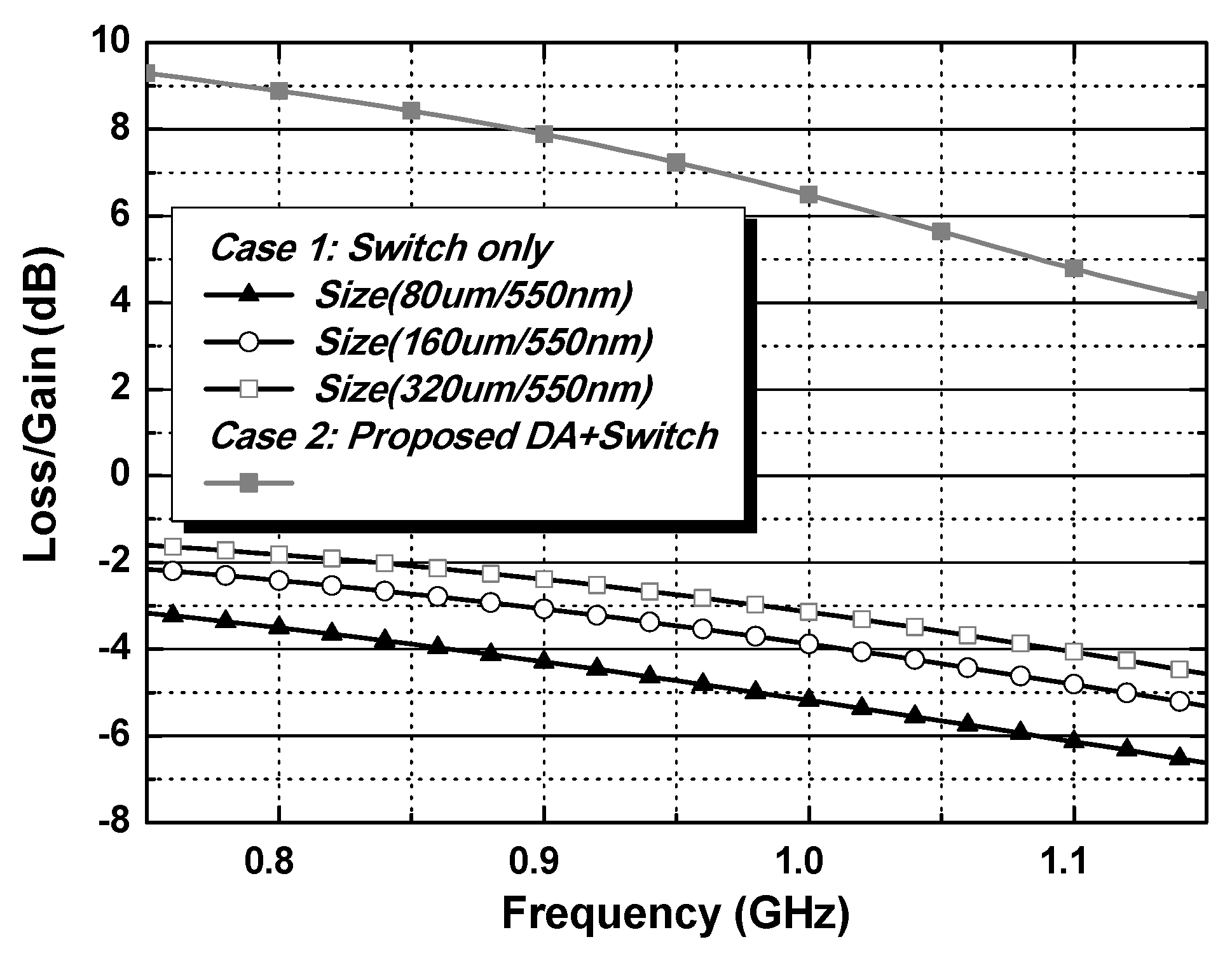

2.1. Supporting External PA Mode

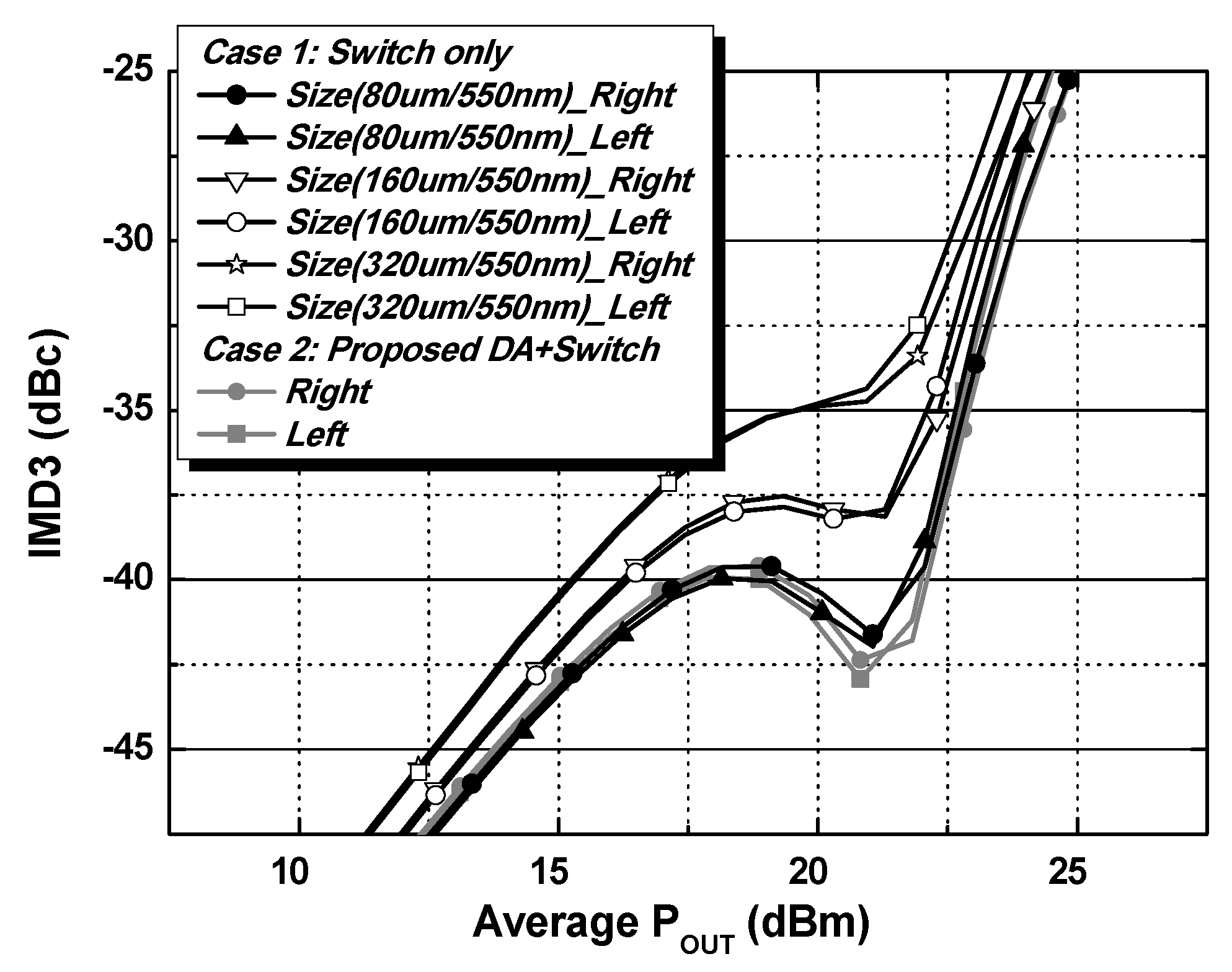

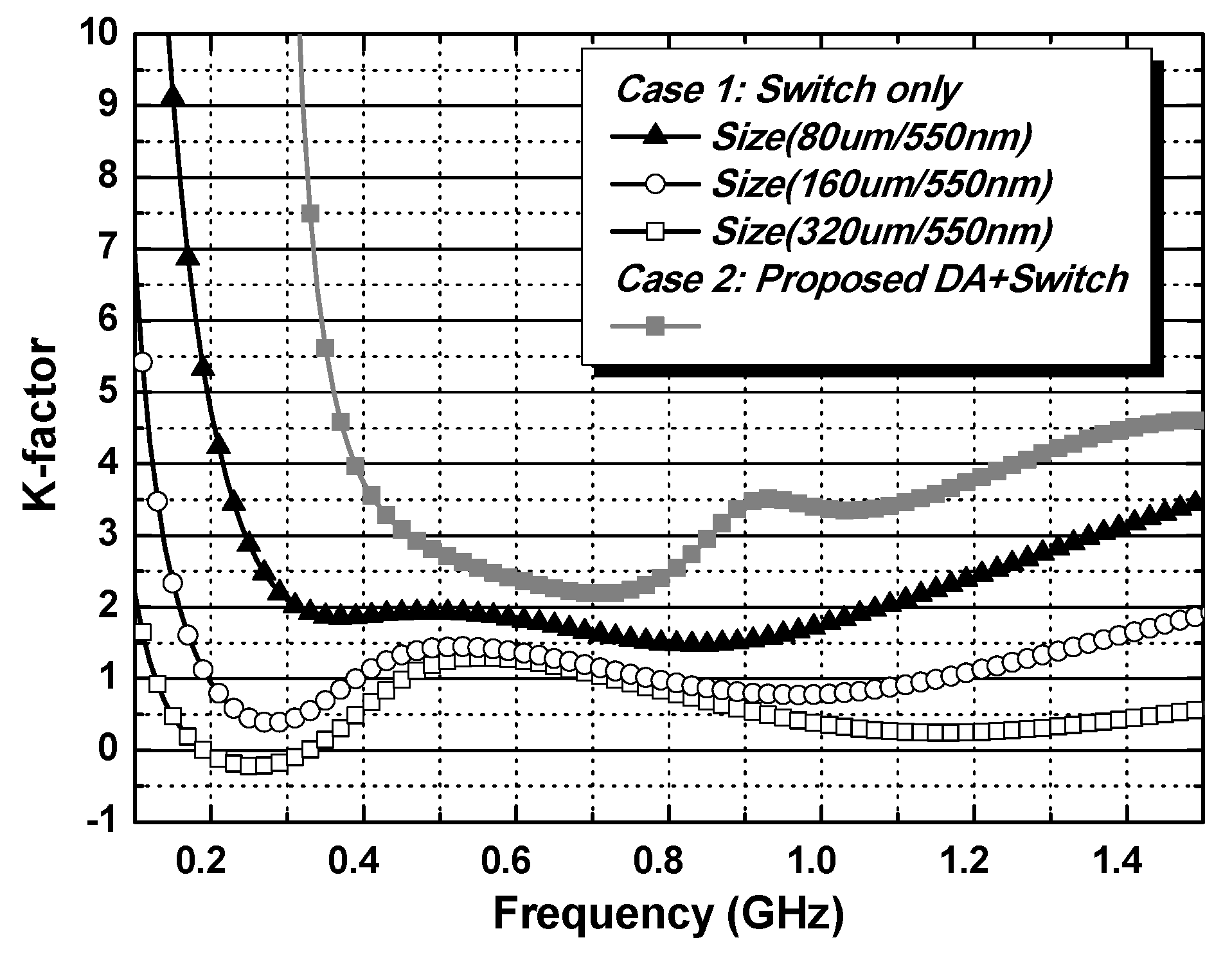

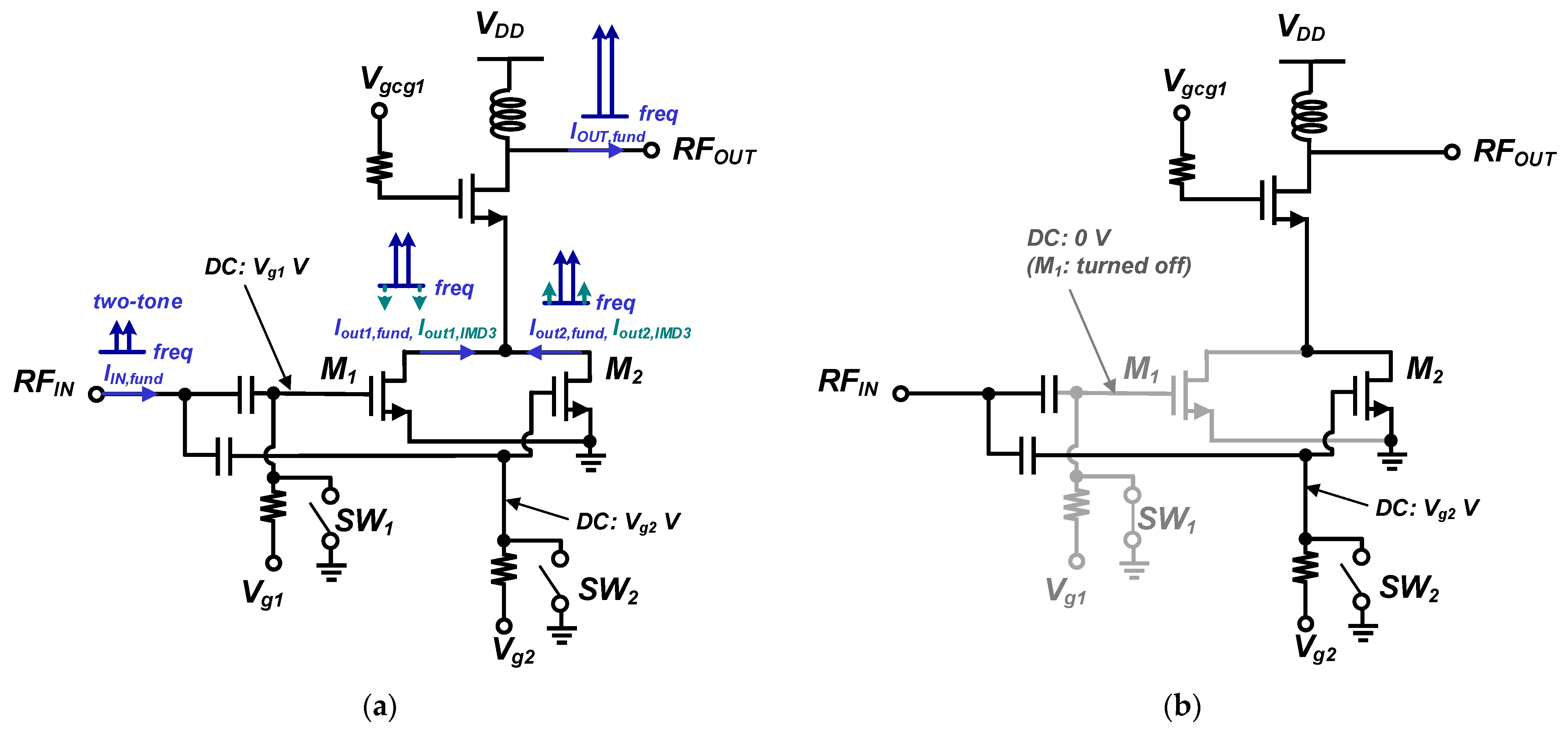

2.2. Design of Dual-Mode with an External PA Driver

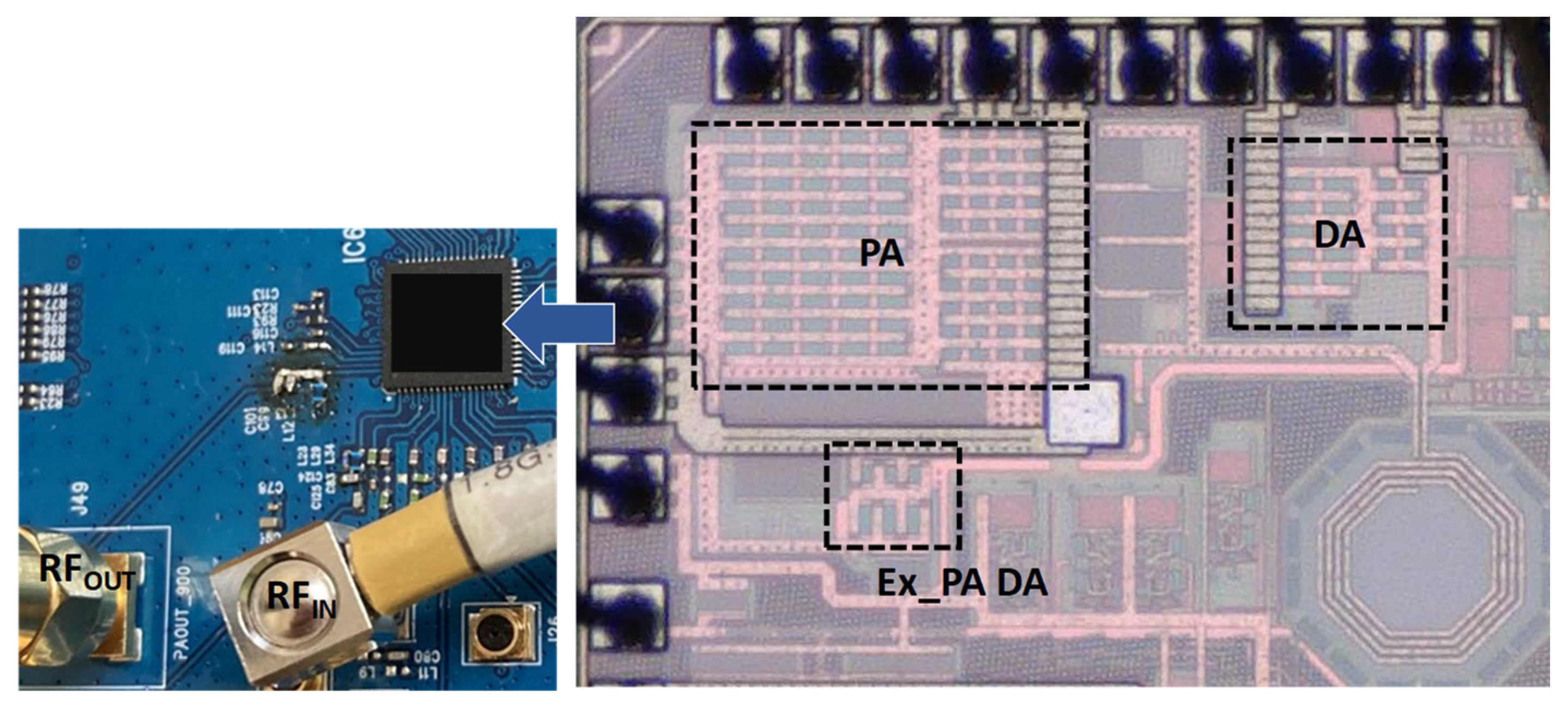

3. Fabrication and Measurement Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chen, M.; Miao, Y.; Hao, Y.; Hwang, K. Narrow band Internet of Things. IEEE Access 2017, 5, 20557–20577. [Google Scholar] [CrossRef]

- Song, Z.; Liu, X.; Zhao, X.; Liu, Q.; Jin, Z.; Chi, B. A low-power NB-IoT transceiver with digital-polar transmitter in 180-nm CMOS. IEEE Trans. Circuits Syst. I 2017, 64, 2569–2581. [Google Scholar] [CrossRef]

- Ratasuk, R.; Vejlgaard, B.; Mangalvedhe, N.; Ghosh, A. NB-IoT system for M2M communication. In Proceedings of the IEEE Wireless Communications and Networking Conference, Doha, Qatar, 1–5 April 2016. [Google Scholar]

- Lee, J.; Han, J.; Lo, C.-L.; Lee, J.; Kim, W.; Kim, S.; Kang, B.; Han, J.; Jung, S.; Nomiyama, T.; et al. NB-IoT and GNSS all-in-one system-on-chip integrating RF transceiver, 23-dBm CMOS power amplifier, power management unit, and clock management system for low cost solution. IEEE J. Solid-State Circuits 2020, 55, 3400–3413. [Google Scholar] [CrossRef]

- Guo, H.; Chan, T.F.; Lai, Y.T.; Wan, K.C.; Chen, L.; Wong, W.P. A SAW-less NB-IoT RF transceiver with hybrid polar and on-chip switching PA supporting power class 3 multi-tone transmission. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 464–466. [Google Scholar]

- Choi, J.; Kim, N.-S. A Spurious and Oscillator Pulling Free CMOS Quadrature LO-Generator for Cellular NB-IoT. IEEE Trans. VLSI Syst. 2021, 29, 2098–2109. [Google Scholar] [CrossRef]

- Ahn, H.; Oh, K.; Nam, I.; Lee, O. Highly efficient HBT power amplifier using high-Q single- and two-winding transformer with IMD3 cancellation. IEEE Access 2021, 9, 85060–85070. [Google Scholar] [CrossRef]

- Nitesh, R.S.; Rajendran, J.; Ramiah, H.; Yarman, B.S. A 0.8 mm2 sub-GHz GaAs HBT power amplifier for 5G application achieving 57.5% PAE and 28.5 dBm maximum linear output power. IEEE Access 2019, 7, 158808–158819. [Google Scholar] [CrossRef]

- Lee, W.; Kang, H.; Lee, H.; Lim, W.; Bae, J.; Koo, H.; Yoon, J.; Hwang, K.C.; Lee, K.Y.; Yang, Y. Broadband InGaP/GaAs HBT power amplifier integrated circuit using cascode structure and optimized shunt inductor. IEEE Trans. Microw. Theory Tech. 2019, 67, 5090–5100. [Google Scholar] [CrossRef]

- Broadcom. Part Number BCM43455. Available online: https://datasheetspdf.com/datasheet/BCM43455.html (accessed on 11 January 2024).

- Qualcomm. Part Number WCN3680B/WCN3660B. Available online: https://dokumen.tips/documents/wcn3680bwcn3660b-device-specification-wcn3680bwcn3660b-ic-ensures-hardware-and.html?page=8 (accessed on 11 January 2024).

- Ahn, H.; Baek, S.; Nam, I.; An, D.; Lee, J.; Jeong, M.; Kim, B.-E.; Lee, Y.-T.; Kim, H.-T.; Ho, Y.-C.; et al. A fully integrated −32-dB EVM broadband 802.11abgn/ac PA with an external PA driver in WLP 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2019, 67, 1870–1882. [Google Scholar] [CrossRef]

- Ryu, N.; Park, B.; Jeong, Y. A fully integrated high efficiency RF power amplifier for WLAN application in 40 nm standard CMOS process. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 382–384. [Google Scholar] [CrossRef]

- Yin, Y.; Xiong, L.; Zhu, Y.; Chen, B.; Min, H.; Xu, H. A compact dual-band digital polar Doherty power amplifier using parallel-combining transformer. IEEE J. Solid-State Circuits 2019, 54, 1575–1585. [Google Scholar] [CrossRef]

- Pozar, D.M. Microwave Engineering, 4th ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2012. [Google Scholar]

- Ding, Y.; Harjani, R. A high-efficiency CMOS +22-dBm linear power amplifier. IEEE J. Solid-State Circuits 2005, 40, 1895–1900. [Google Scholar] [CrossRef]

- Joo, T.; Koo, B.; Hong, S. A WLAN RF CMOS PA with large signal MGTR method. IEEE Trans. Microw. Theory Tech. 2013, 61, 1272–1279. [Google Scholar] [CrossRef]

- Jung, D.; Zhao, H.; Wang, H. A CMOS highly linear Doherty power amplifier with multigated transistors. IEEE Trans. Microw. Theory Tech. 2019, 67, 1883–1891. [Google Scholar] [CrossRef]

- Fowler, T.; Burger, K.; Cheng, N.-S.; Samelis, A.; Enobakhare, E.; Rohlfing, S. Efficiency improvement techniques at lower power levels for linear CDMA and WCDMA power amplifier. In Proceedings of the 2002 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Seattle, WA, USA, 3–4 June 2002; pp. 41–44. [Google Scholar]

- Lim, W.; Kang, H.; Lee, W.; Bae, J.; Oh, S.; Oh, H.; Chae, S.; Hwang, K.C.; Lee, K.-Y.; Yang, Y. Dual-mode CMOS power amplifier based on loadimpedance modulation. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 1041–1043. [Google Scholar] [CrossRef]

- Rawat, A.S.; Rajendran, J.; Marianppan, S.; Shasidharan, P.; Kumar, N.; Yarman, B.S. A 919 MHz—923 MHz, 21 dBm CMOS power amplifier with bias modulation linearization technique achieving PAE of 29% for LoRa application. IEEE Access 2022, 10, 79365–79378. [Google Scholar] [CrossRef]

- Cho, Y.; Moon, K.; Park, B.; Kim, J.; Kim, B. Voltage-combined CMOS Doherty power amplifier based on transformer. IEEE Trans. Microw. Theory Tech. 2016, 64, 3612–3622. [Google Scholar] [CrossRef]

| Reference | This Work | [20] | [21] | [2] | [14] | [22] | [12] | [13] |

|---|---|---|---|---|---|---|---|---|

| CMOS Technology | 40 nm | 55 nm | 0.18 μm | 0.18 μm | 55 nm | 0.18 μm | 40 nm | 40 nm |

| Frequency (MHz) | 920 | 920 | 921 | 750−960 | 850 | 880 | 2450 | 2445 |

| Gain (dB) | 20.4 | 24.0 * | 29.3 | N/A | N/A | 13.3 | 24.8 | 37 |

| PSAT (dBm) | 28.8 | 28.8 * | 27.0 | 24.2 | 28.9 | 31.8 * | 27.9 | 26.5 * |

| PAESAT (%) | 57.8 | 47.5 * | 44.4 | 28.9 | 36.8 | 56.2 * | 39.5 | 38 (DE) |

| Signal | NB-IoT (π/4-DQPSK) 200 kHz / OFDM (64-QAM 10 MHz) | NB-IoT 200 kHz | 16-QAM 20 MHz | NB-IoT (π/4-DQPSK) 3.75 kHz | NB-IoT 180 KHz/ 64-QAM 20MHz | 16-QAM 10 MHz | 802.11ac 256-QAM 20 MHz | 802.11 g 20 MHz |

| PAE (Current) @ Pout with −45 dBc ACLR (NB-IoT Signal) | 31.0%(245mA) @24.2 dBm (HP), 177 mA (HP)/ 97 mA (LP) @12 dBm | 12.8% * @16.5 dBm * | NA | w/−26.1 dB EVM 28.9% @19.1 dBm DPD applied | w/−21.6 dB EVM 29.5% @24.4 dBm DPD applied | NA | NA | NA |

| w/−33.9 dBc ACLR, 44.3% @27.7 dBm | ||||||||

| PAE (Current) @ Pout with −40 dBc ACLR (OFDM Signal) | 14.6% (148 mA) @20.0 dBm (HP), 177 mA (HP)/ 97 mA (LP) @12 dBm | NA | 6.0%* @ 17.0 dBm * | NA | w/−25.3 dB EVM 26.1% @22.9 dBm DPD applied | 7.8% * @7.5 dBm * | 12.9% @19.2 dBm w/−32 dB EVM | 14%(DE) @18.5 dBm w/−25dB EVM |

| w/−30 dBc ACLR, 28.0% * @21 dBm | w/−33 dBc ACLR 47.4% @27 dBm | |||||||

| External Mode | (NB-IoT Signal) <−58 dB ACLR @ −2 dBm (40mA) | - | - | - | - | - | −37 dB EVM @−5 dBm (18mA) | −34.8 dB EVM @−5 dBm * (NA) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ahn, H.; Oh, K.; Choi, S.-E.; Son, D.-H.; Nam, I.; Lim, K.; Lee, O. A Dual-Mode CMOS Power Amplifier with an External Power Amplifier Driver Using 40 nm CMOS for Narrowband Internet-of-Things Applications. Nanomaterials 2024, 14, 262. https://doi.org/10.3390/nano14030262

Ahn H, Oh K, Choi S-E, Son D-H, Nam I, Lim K, Lee O. A Dual-Mode CMOS Power Amplifier with an External Power Amplifier Driver Using 40 nm CMOS for Narrowband Internet-of-Things Applications. Nanomaterials. 2024; 14(3):262. https://doi.org/10.3390/nano14030262

Chicago/Turabian StyleAhn, Hyunjin, Kyutaek Oh, Se-Eun Choi, Dong-Hee Son, Ilku Nam, Kyoohyun Lim, and Ockgoo Lee. 2024. "A Dual-Mode CMOS Power Amplifier with an External Power Amplifier Driver Using 40 nm CMOS for Narrowband Internet-of-Things Applications" Nanomaterials 14, no. 3: 262. https://doi.org/10.3390/nano14030262

APA StyleAhn, H., Oh, K., Choi, S.-E., Son, D.-H., Nam, I., Lim, K., & Lee, O. (2024). A Dual-Mode CMOS Power Amplifier with an External Power Amplifier Driver Using 40 nm CMOS for Narrowband Internet-of-Things Applications. Nanomaterials, 14(3), 262. https://doi.org/10.3390/nano14030262