DC-free Method to Evaluate Nanoscale Equivalent Oxide Thickness: Dark-Mode Scanning Capacitance Microscopy

Abstract

1. Introduction

2. Experimental Details

2.1. Specimen Preparation

2.2. Instruments

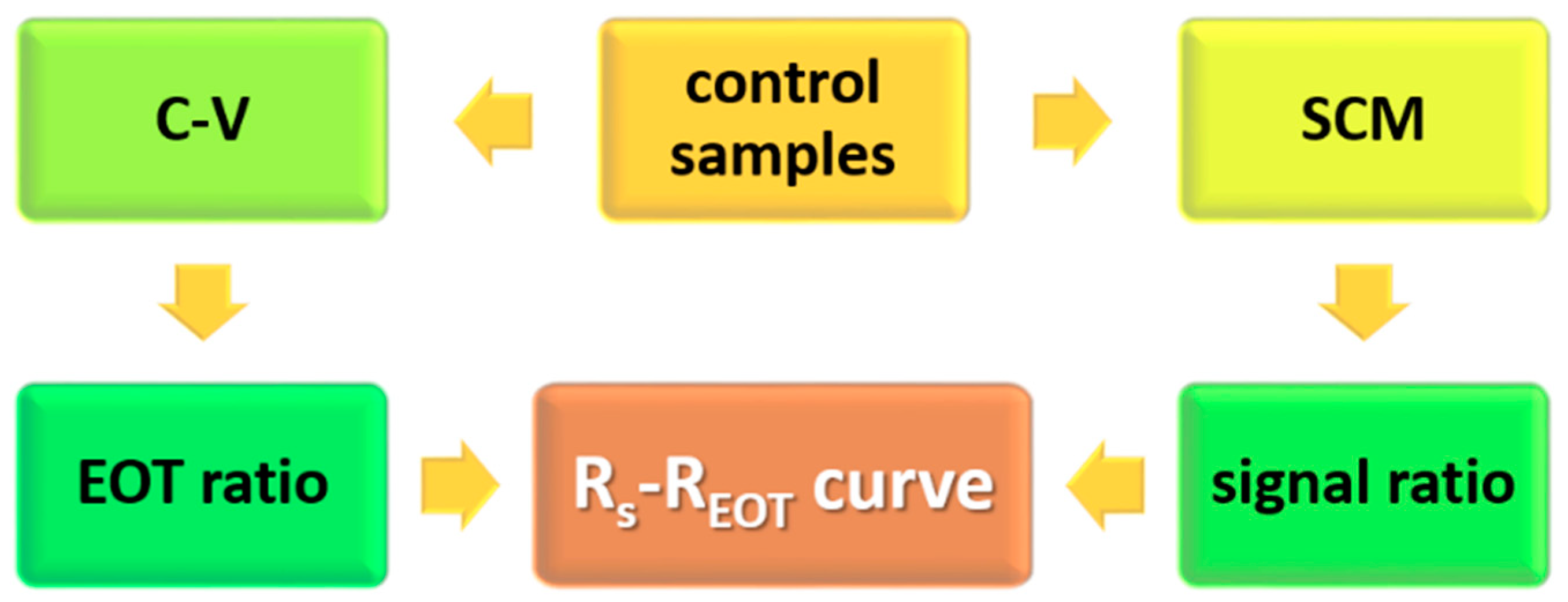

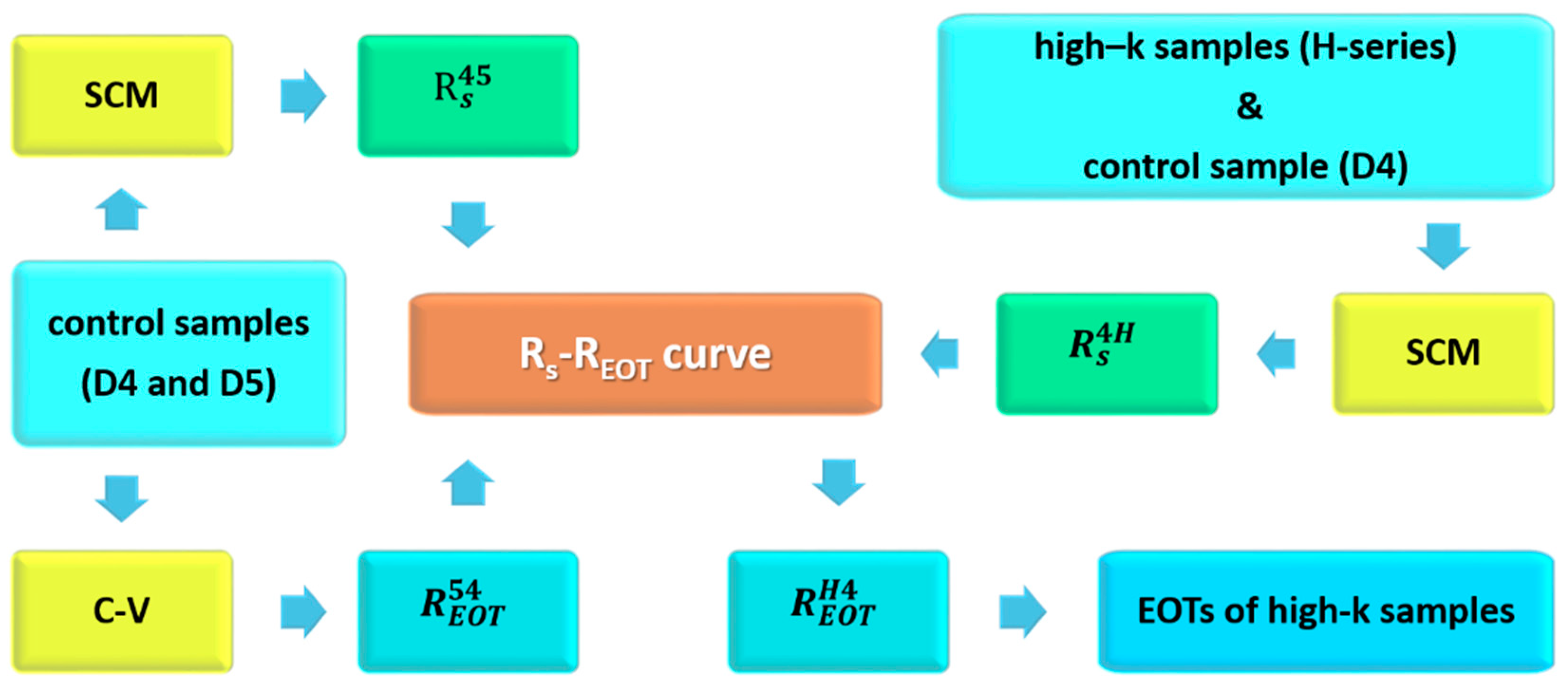

2.3. Method for EOT Evaluation Using DC-Free SCM

3. Results

3.1. EOT Evaluation

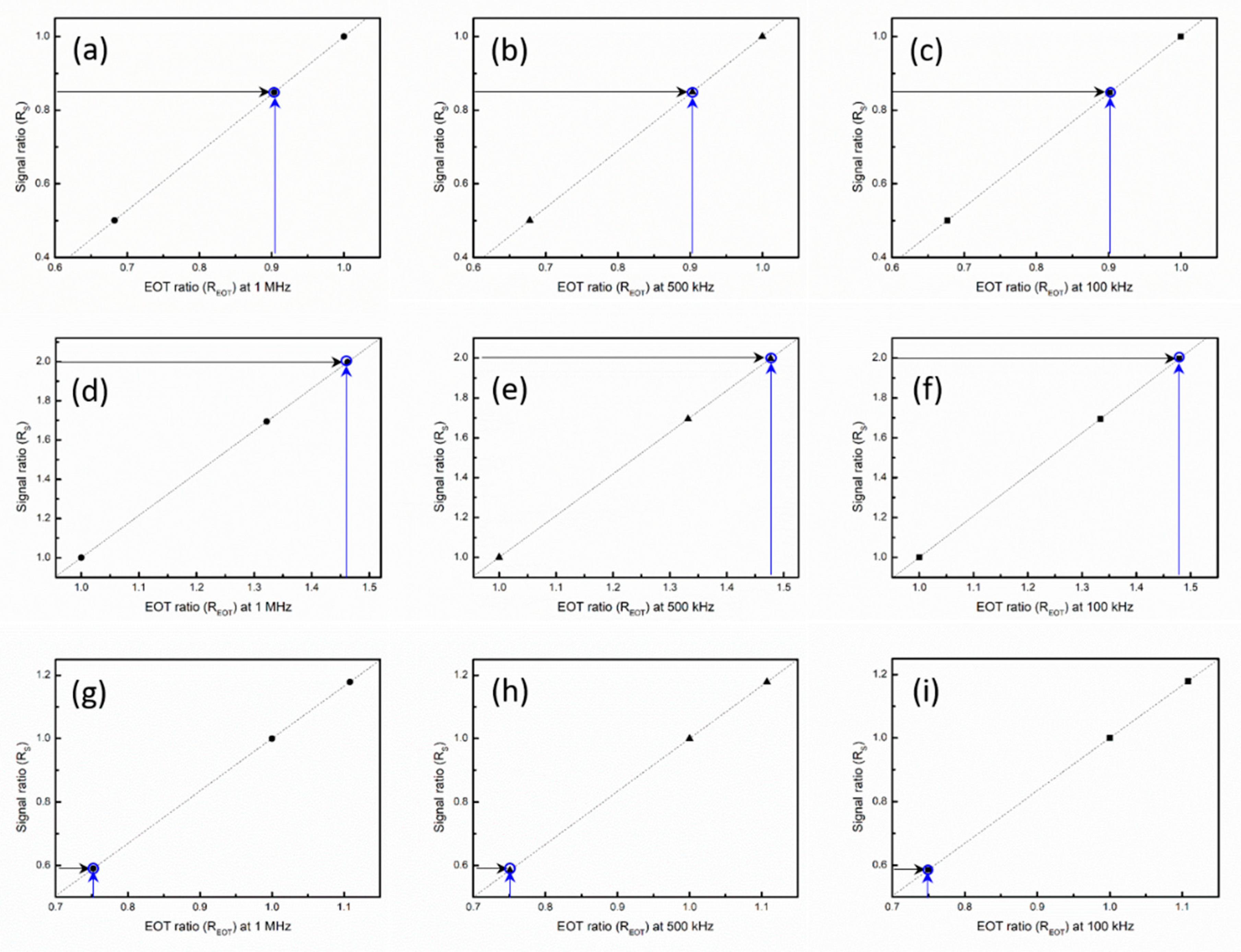

3.1.1. Rs–REOT Linear Relation

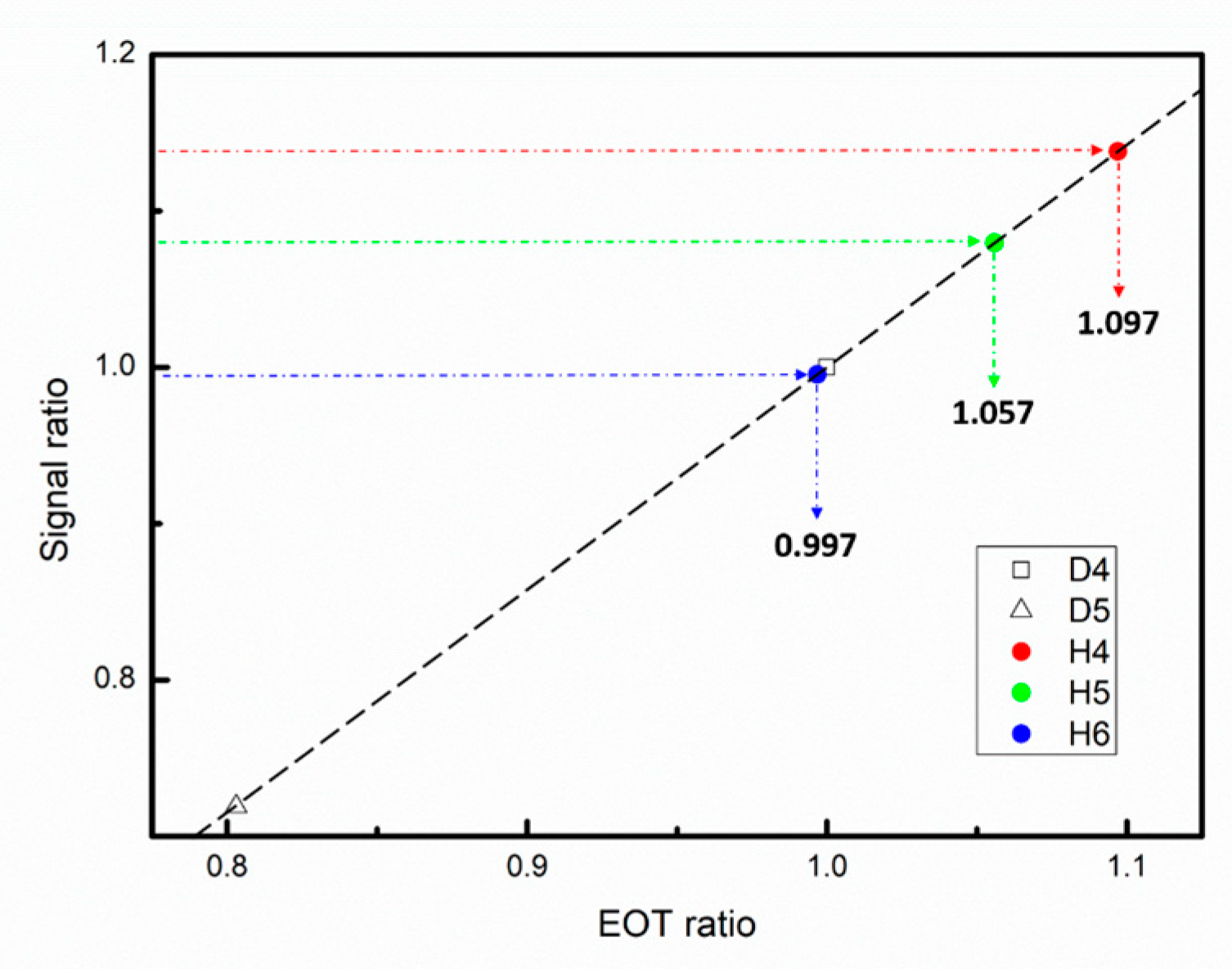

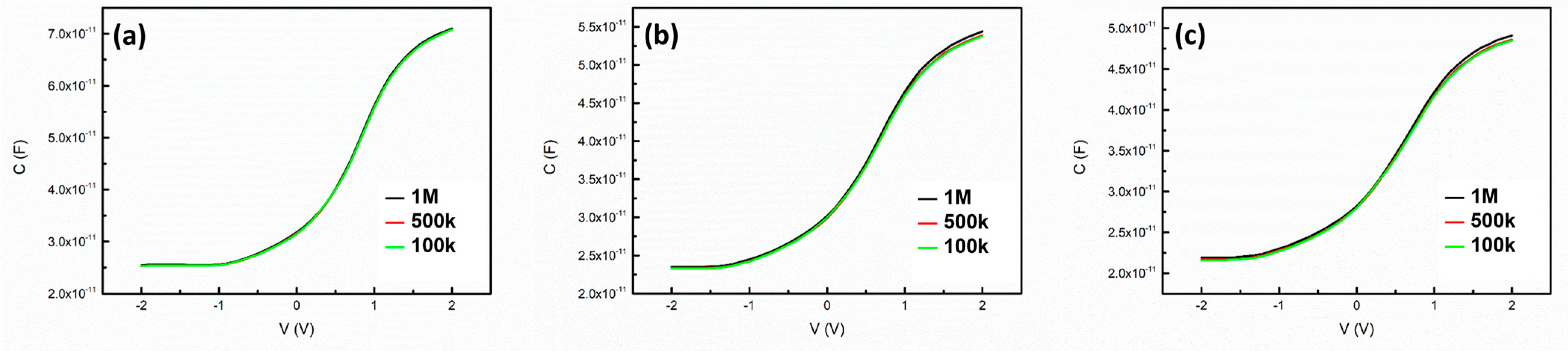

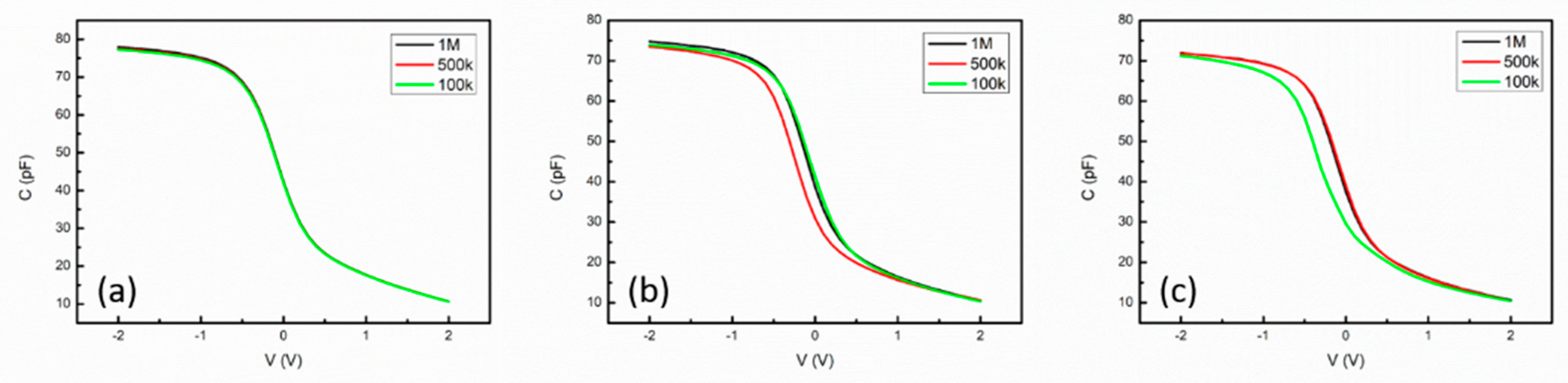

3.1.2. EOT Evaluation of HfO2/SiO2/Si Structures

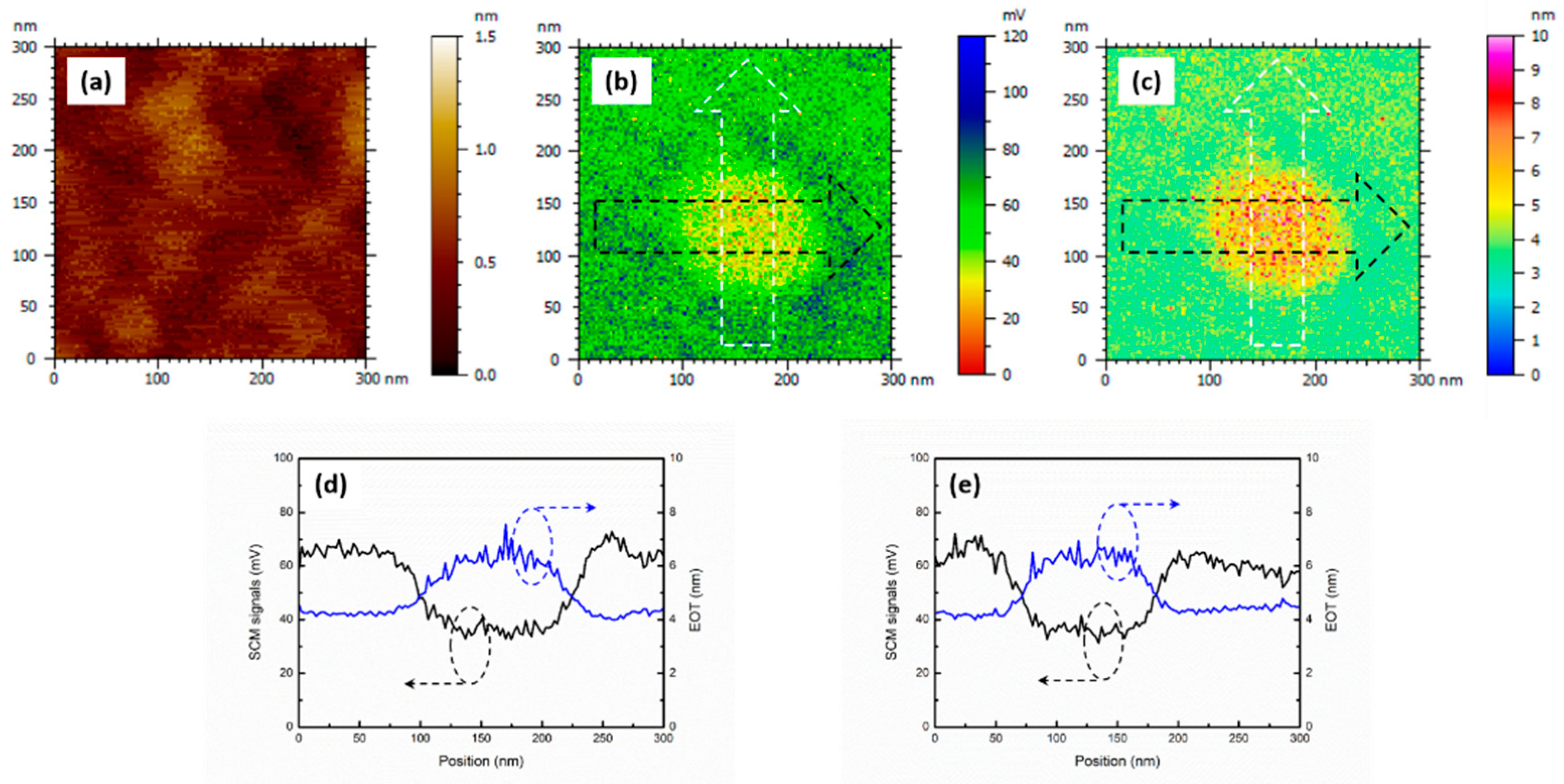

3.2. EOT Mapping

3.2.1. Thermal Oxide Subjected to Dynamic DC Stress

3.2.2. High-k Oxide Subjected to Dynamic DC Stress

4. Discussion

5. Conclusions

6. Patents

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Correction Statement

References

- Ratnesh, R.K.; Goel, A.; Kaushik, G.; Garg, H.; Chandan; Singh, M.; Prasad, B. Advancement and challenges in MOSFET scaling. Mater. Sci. Semicond. Process. 2021, 134, 106002. [Google Scholar] [CrossRef]

- Bhattacharjee, A.; Dasgupta, S. Impact of gate/spacer-channel underlap, gate oxide EOT, and scaling on the device characteristics of a DG-RFET. IEEE Trans. Electron. Devices 2017, 64, 3063–3070. [Google Scholar] [CrossRef]

- Pannu, N.; Parkash, N.R.; Kaur, J. Effect of sizing and scaling on power dissipation and resilience of an RHBD SRAM circuit. J. Electron. Test. 2022, 38, 579–587. [Google Scholar] [CrossRef]

- Lin, H.; Zhao, X.; Luo, X.; Miao, Y.; Zhang, Y.; Kong, Z.; Wang, G.; Yang, H.; Wu, Z.; Shi, Y.; et al. High performance junctionless FDSOI SiGe channel p-FinFET with high ION/IOFF ratio and excellent SS. Mater. Sci. Semicond. Process. 2024, 171, 108007. [Google Scholar] [CrossRef]

- Frank, D.J.; Nowak, E.; Wong, S.H.P. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 2001, 89, 259–288. [Google Scholar] [CrossRef]

- Narula, V.; Agarwal, M. Effect of Gate Oxide Thickness on the Performance of Rectangular Core-shell Based Junctionless Field Effect Transistor. In Proceedings of the 3rd International Conference on Condensed Matter and Applied Physics, Bikaner, India, 14–15 October 2019. [Google Scholar]

- Liu, Z.; Hu, Z.; Zhang, Z.; Shao, H.; Chen, M.; Bi, D.; Ning, B.; Zou, S. Gate length dependence of the shallow trench isolation leakage current in an irradiated deep submicron NMOSFET. J. Semicond. 2011, 32, 064004. [Google Scholar] [CrossRef]

- Morita, Y.; Migita, S.; Mizubayashi, W.; Masahara, M.; Ota, H. Two-step annealing effects on ultrathin EOT higher-k (k = 40) ALD-HfO2 gate stacks. Solid-State Electron. 2013, 84, 58–64. [Google Scholar] [CrossRef]

- Litta, E.D.; Hellström, P.E.; Östling, M. Integration of TmSiO/HfO2 dielectric stack in sub-nm EOT high-k/metal gate CMOS technology. IEEE Trans. Electron. Devices 2015, 62, 934–939. [Google Scholar] [CrossRef]

- Lee, M.C.; Lee, W.L.; Lin, H.R.; Luo, G.L.; Chien, C.H. High-interface-quality Hf-based gate stacks on Si0.5Ge0.5 through aluminum capping. IEEE Electron. Device Lett. 2021, 42, 1723–1726. [Google Scholar] [CrossRef]

- Misra, D.; Chowdhury, N.A. Charge trapping in high-κ gate dielectrics: A recent understanding. ECS Trans. 2006, 2, 311–328. [Google Scholar] [CrossRef]

- Samanta, P.; Cheng, C.L.; Lee, Y.J. Charge trapping related degradation of thin HfAlO/SiO2 gate dielectric stack during constant-voltage stress. J. Electrochem. Soc. 2009, 156, H661–H668. [Google Scholar] [CrossRef]

- Chang, M.N.; Chen, C.Y.; Wan, W.W.; Liang, J.H. The influence of annealing sequence on p+/n junction observed by scanning capacitance microscopy. Appl. Phys. Lett. 2004, 84, 4705–4707. [Google Scholar] [CrossRef]

- O’Malley, M.L.; Timp, G.L.; Moccio, S.V.; Garno, J.P.; Kleiman, R.N. Quantification of scanning capacitance microscopy imaging of the pn junction through electrical simulation. Appl. Phys. Lett. 1999, 74, 272–274. [Google Scholar] [CrossRef]

- Kim, T.H.; Fu, K.; Yang, C.; Zhao, Y.; Yu, E.T. Electronic structure of epitaxially grown and regrown GaN pn junctions characterized by scanning Kelvin probe and capacitance microscopy. J. Appl. Phys. 2022, 131, 015704. [Google Scholar] [CrossRef]

- Fiorenza, P.; Franco, S.D.; Giannazzo, F.; Roccaforte, F. Nanoscale probing of the lateral homogeneity of donors concentration in nitridated SiO2/4H-SiC interfaces. Nanotechnology 2016, 27, 315701. [Google Scholar] [CrossRef] [PubMed]

- Xia, H.; Li, T.X.; Tang, H.J.; Zhu, L.; Li, X.; Gong, H.M.; Lu, W. Nanoscale imaging of the photoresponse in PN junctions of InGaAs infrared detector. Sci. Rep. 2016, 6, 21544. [Google Scholar] [CrossRef] [PubMed]

- Chang, M.N.; Chen, C.Y.; Pan, F.M.; Lai, J.H.; Wan, W.W.; Liang, J.H. Photovoltaic effect on differential capacitance profiles of low-energy-BF2+-implanted silicon wafers. Appl. Phys. Lett. 2003, 82, 3955–3957. [Google Scholar] [CrossRef]

- Chang, M.N.; Hu, C.W.; Chou, T.H.; Lee, Y.J. Contrast distortion induced by modulation voltage in scanning capacitance microscopy. Appl. Phys. Lett. 2012, 101, 083503. [Google Scholar] [CrossRef]

- Chang, M.N.; Chen, Y.K.; Kao, H.Y.; Chen, J.Y.; Liu, C.H.; Lee, Y.J. Voltage modulation efficiency in scanning capacitance microscopy. Ultramicroscopy 2021, 224, 113266. [Google Scholar] [CrossRef]

- Balaji, N.; Park, C.; Chung, S.; Ju, M.; Raja, J.; Yi, J. Effects of low temperature anneal on the interface properties of thermal silicon oxide for silicon surface passivation. J. Nanosci. Nanotechnol. 2016, 16, 4783–4787. [Google Scholar] [CrossRef]

- Taubea, A.; Mroczyński, R.; Korwin-Mikke, K.; Gierałtowska, S.; Szmidt, J.; Piotrowska, A. Effect of the post-deposition annealing on electrical characteristics of MIS structures with HfO2/SiO2 gate dielectric stacks. Mater. Sci. Eng. B 2012, 177, 1281–1285. [Google Scholar] [CrossRef]

| Group 1 | Group 2 | ||||

|---|---|---|---|---|---|

| D1 | D2 | D3 | D4 | D5 | H-Series |

| 2.82 nm | 4.09 nm | 4.85 nm | 4.19 nm | 4.93 nm | 2.51 nm/0.96 nm |

| SCM | C–V @ 100 kHz | |||||

| Samples | D1 | D2 | D3 | D1 | D2 | D3 |

| EOT | 4.28 nm | 5.68 nm | 6.31 nm | 4.26 nm | 5.68 nm | 6.30 nm |

| SCM | C–V @ 500 kHz | |||||

| Samples | D1 | D2 | D3 | D1 | D2 | D3 |

| EOT | 4.29 nm | 5.68 nm | 6.30 nm | 4.27 nm | 5.69 nm | 6.30 nm |

| SCM | C–V @ 1 MHz | |||||

| Samples | D1 | D2 | D3 | D1 | D2 | D3 |

| EOT | 4.23 nm | 5.63 nm | 6.22 nm | 4.25 nm | 5.62 nm | 6.23 nm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chang, M.-N.; Wu, Y.-S.; Lin, C.-J.; Hsueh, Y.-H.; Su, C.-J.; Lee, Y.-J. DC-free Method to Evaluate Nanoscale Equivalent Oxide Thickness: Dark-Mode Scanning Capacitance Microscopy. Nanomaterials 2024, 14, 934. https://doi.org/10.3390/nano14110934

Chang M-N, Wu Y-S, Lin C-J, Hsueh Y-H, Su C-J, Lee Y-J. DC-free Method to Evaluate Nanoscale Equivalent Oxide Thickness: Dark-Mode Scanning Capacitance Microscopy. Nanomaterials. 2024; 14(11):934. https://doi.org/10.3390/nano14110934

Chicago/Turabian StyleChang, Mao-Nan, Yi-Shan Wu, Chiao-Jung Lin, Yu-Hsun Hsueh, Chun-Jung Su, and Yao-Jen Lee. 2024. "DC-free Method to Evaluate Nanoscale Equivalent Oxide Thickness: Dark-Mode Scanning Capacitance Microscopy" Nanomaterials 14, no. 11: 934. https://doi.org/10.3390/nano14110934

APA StyleChang, M.-N., Wu, Y.-S., Lin, C.-J., Hsueh, Y.-H., Su, C.-J., & Lee, Y.-J. (2024). DC-free Method to Evaluate Nanoscale Equivalent Oxide Thickness: Dark-Mode Scanning Capacitance Microscopy. Nanomaterials, 14(11), 934. https://doi.org/10.3390/nano14110934