Investigation of Reducing Interface State Density in 4H-SiC by Increasing Oxidation Rate

Abstract

1. Introduction

2. Materials and Methods

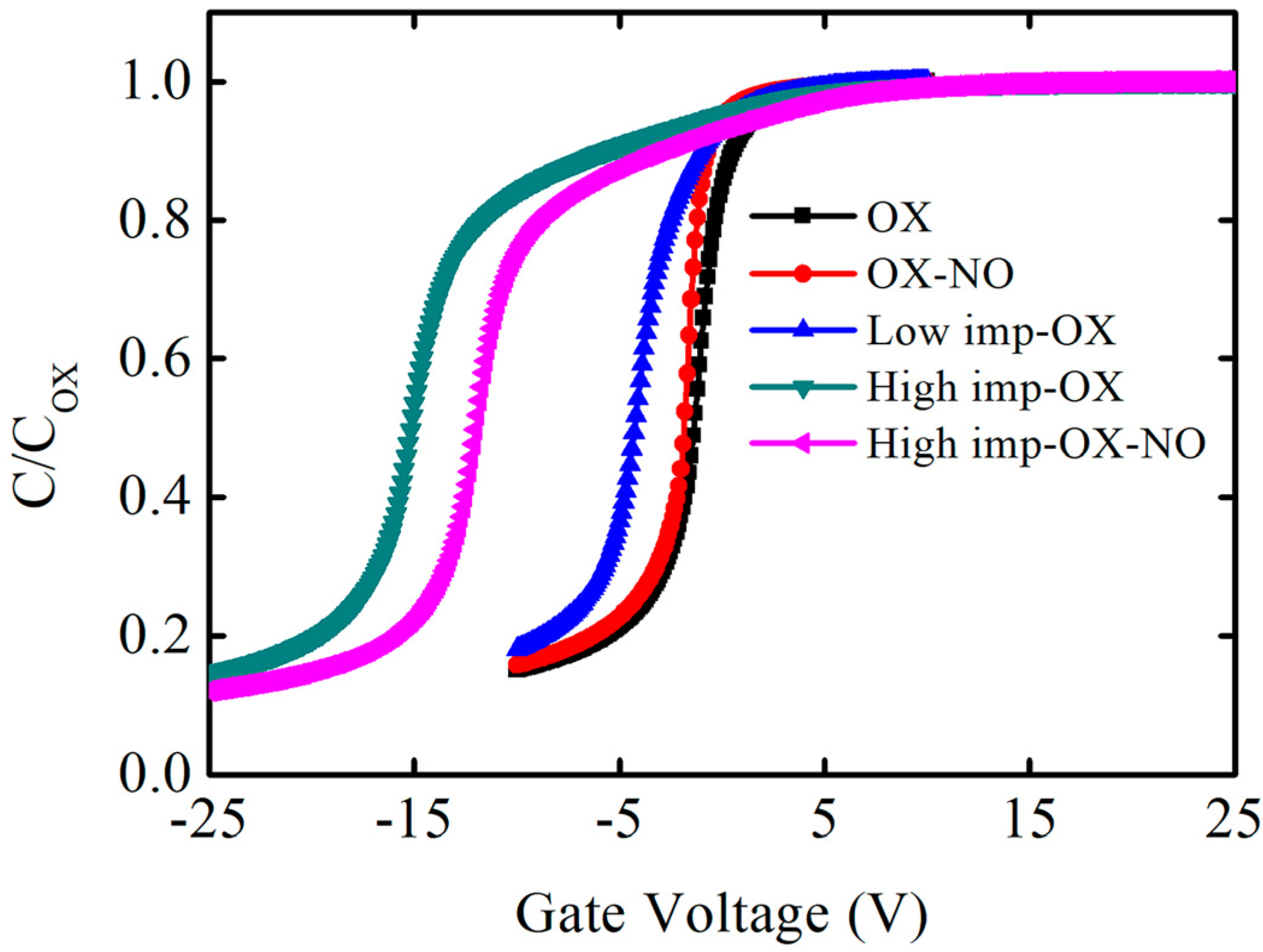

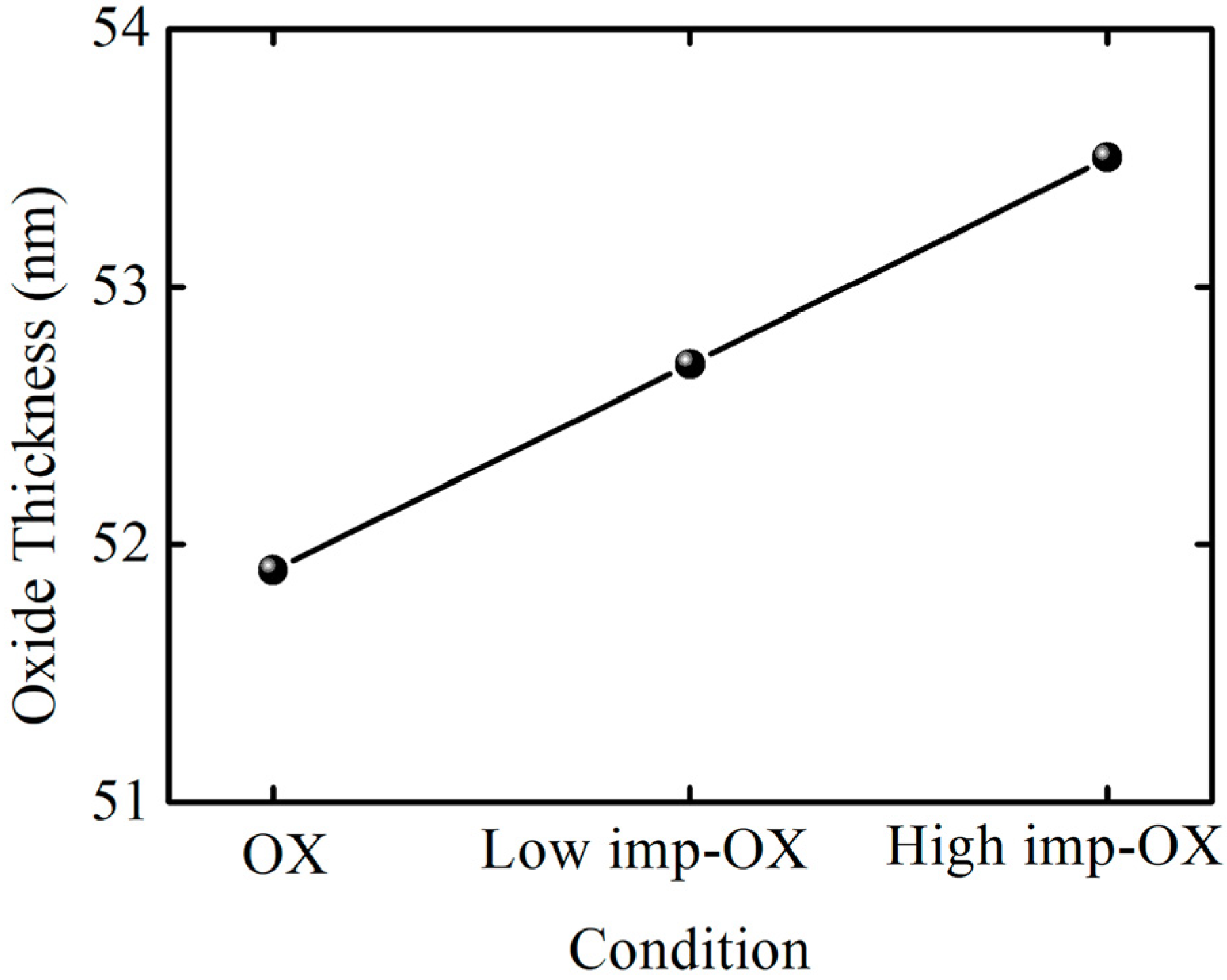

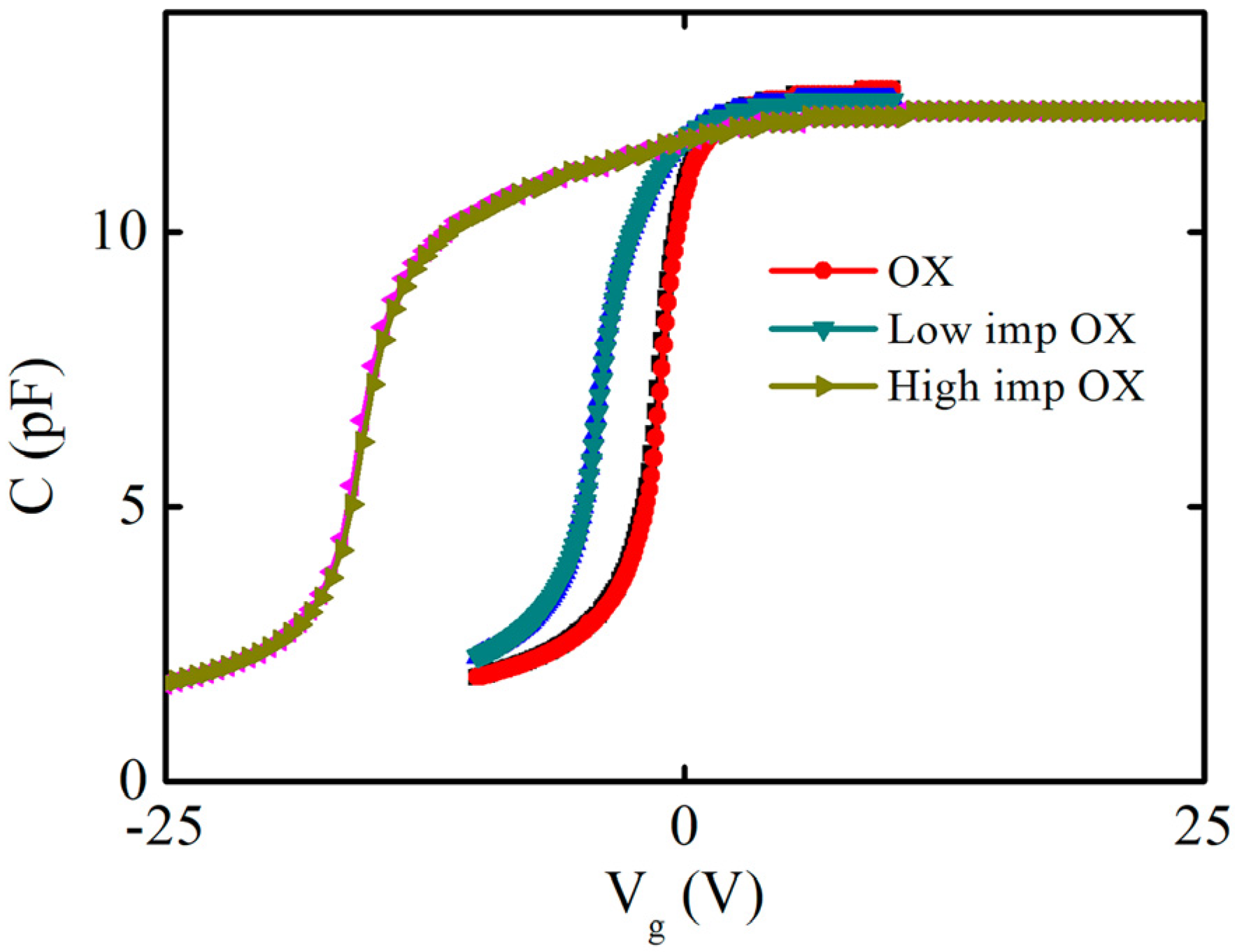

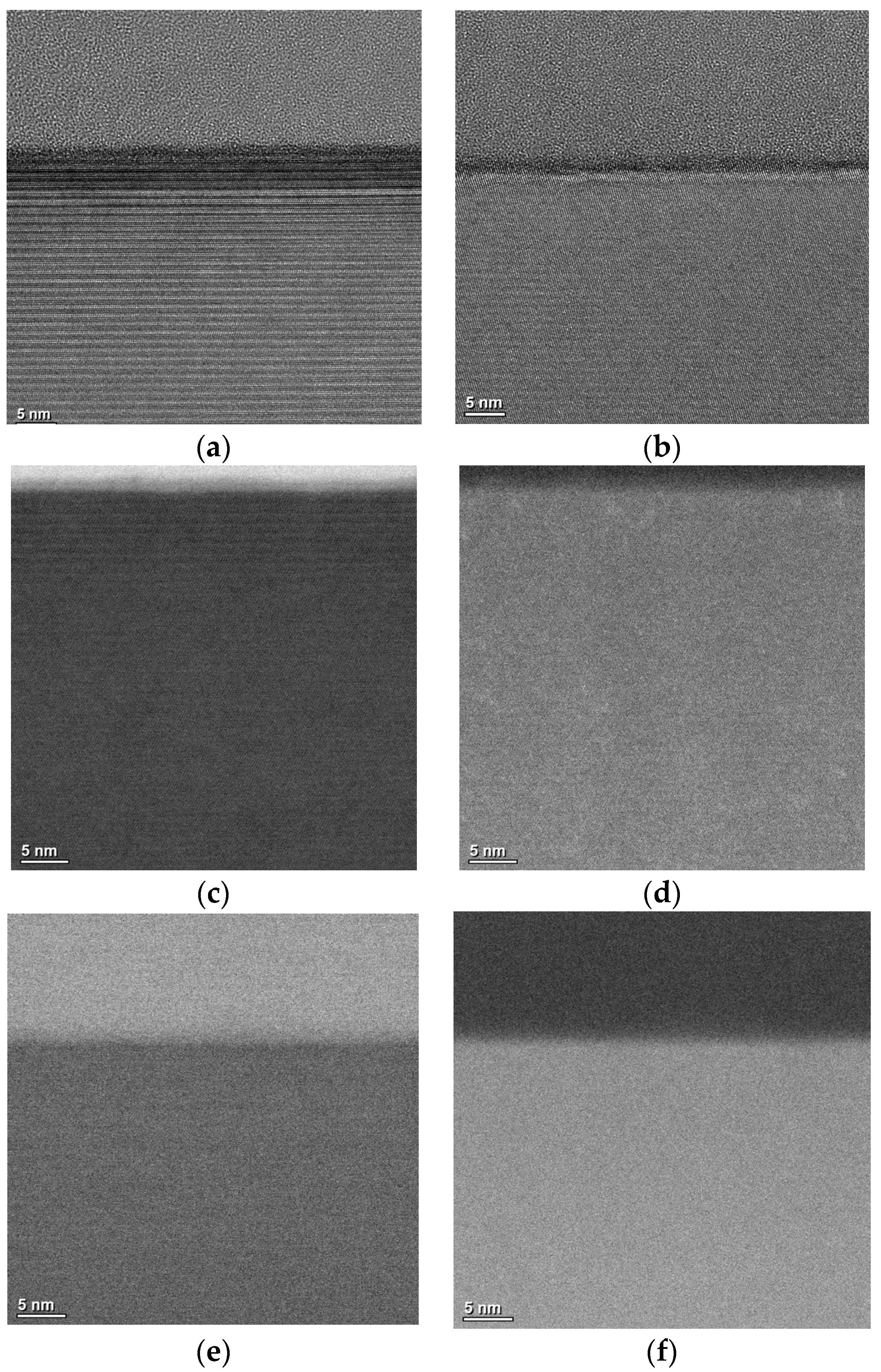

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Lipkin, L.A.; Das, M.K.; Palmour, J.W. N2O processing improves the 4H-SiC: SiO2 Interface. Mat. Sci. Forum. 2002, 389, 985–988. [Google Scholar] [CrossRef]

- Kil, T.; Kita, K. Anomalous band alignment change of SiO2/4H−SiC (0001) and (000–1) MOS capacitors induced by NO-POA and its possible origin. Appl. Phys. Lett. 2020, 116, 122103. [Google Scholar] [CrossRef]

- Devynck, F.; Alkauskas, A.; Broqvist, P.; Pasquarello, A. Defect levels of carbon-related defects at the SiC/SiO2 interface from hybrid functionals. Phys. Rev. B 2011, 83, 195319. [Google Scholar] [CrossRef]

- Knaup, J.M.; Deák, P.; Frauenheim, T. Defects in SiO2 as the possible origin of near interface traps in the SiC/SiO2 system: A systematic theoretical study. Phys. Rev. B 2005, 72, 115323. [Google Scholar] [CrossRef]

- Tilak, V.; Matocha, K.; Dunne, G. Electron-scattering mechanisms in heavily doped silicon carbide MOSFET inversion layers. IEEE Trans. Electron. Devices 2007, 54, 2823–2829. [Google Scholar] [CrossRef]

- Pande, P.; Haasmann, D.; Han, J.; Moghadam, H.A.; Tanner, P.; Dimitrijev, S. Electrical characterization of SiC MOS capacitors: A critical review. Microelectron. Reliab. 2020, 112, 113790. [Google Scholar] [CrossRef]

- Chung, G.Y.; Tin, C.C.; Williams, J.R.; McDonald, K.; Chanana, R.K.; Weller, R.A.; Pantelides, S.T.; Feldman, L.C.; Holland, O.W.; Das, M.K.; et al. Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide. IEEE Electron Device Lett. 2001, 22, 176–178. [Google Scholar] [CrossRef]

- Wang, S.; Dhar, S.; Wang, S.R.; Ahyi, A.C.; Franceschetti, A.; Williams, J.R.; Feldman, L.C.; Pantelides, S.T. Bonding at the SiC-SiO2 interface and the effects of nitrogen and hydrogen. Phys. Rev. Lett. 2007, 98, 026101. [Google Scholar] [CrossRef]

- Koo, S.M.; Jung, S.W.; Moon, K.S.; Lee, S.K.; Kim, S.M. Annealing dependence of nitrogen bias temperature instability (NBTI) in 4H-SiC MOSFETs. J. Nanoelectron. Optoelectron. 2017, 12, 1167–1171. [Google Scholar] [CrossRef]

- Chung, G.; Tin, C.C.; Williams, J.R.; McDonald, K.; Di Ventra, M.; Chanana, R.K.; Pantelides, S.T.; Feldman, L.C.; Weller, R.A. Effects of anneals in ammonia on the interface trap density near the band edges in 4H–silicon carbide metal-oxide-semiconductor capacitors. Appl. Phys. Lett. 2000, 77, 3601–3603. [Google Scholar] [CrossRef]

- Kobayashi, T.; Tachiki, T.; Ito, K.; Kimoto, T. Reduction of interface state density in SiC (0001) MOS structures by low-oxygen-partial-pressure annealing. Appl. Phys. Exp. 2019, 12, 031001. [Google Scholar] [CrossRef]

- Tachiki, T.; Kaneko, M.; Kimoto, T. Mobility improvement of 4H-SiC (0001) MOSFETs by a three-step process of H2 etching, SiO2 deposition, and interface nitridation. Appl. Phys. Exp. 2021, 14, 031001. [Google Scholar] [CrossRef]

- Kobayashi, T.; Okuda, T.; Tachiki, K.; Ito, K.; Matsushita, Y.; Kimoto, T. Design and formation of SiC (0001)/SiO2 interfaces via Si deposition followed by low-temperature oxidation and high-temperature nitridation. Appl. Phys. Exp. 2020, 13, 091003. [Google Scholar] [CrossRef]

- Kobayashi, T.; Suda, J.; Kimoto, T. Reduction of interface state density in SiC (0001) MOS structures by post-oxidation Ar annealing at high temperature. AIP Advances. 2017, 7, 045008. [Google Scholar] [CrossRef]

- Yang, C.; Yin, Z.; Zhang, F.; Su, Y.; Qin, F.; Wang, D. Synergistic passivation effects of nitrogen plasma and oxygen plasma on improving the interface quality and bias temperature instability of 4H-SiC MOS capacitors. Appl. Surface Sci. 2020, 513, 145837. [Google Scholar] [CrossRef]

- Liu, X.; Hao, J.; You, N.; Bai, Y.; Wang, S. High-pressure microwave plasma oxidation of 4H-SiC with low interface trap density. AIP Advances. 2019, 9, 125150. [Google Scholar] [CrossRef]

- Kosugi, R.; Suzuki, S.; Okamoto, M.; Harada, S.; Senzaki, J.; Fukuda, K. Strong dependence of the inversion mobility of 4H and 6H SiC (0001) MOSFETs on the water content in pyrogenic re-oxidation annealing. IEEE Electron Dev. Lett. 2002, 23, 136–138. [Google Scholar] [CrossRef]

- Moon, J.H.; Kang, I.H.; Kim, H.W.; Seok, O.; Bahng, W.; Ha, M.W. TEOS-based low-pressure chemical vapor deposition for gate oxides in 4H–SiC MOSFETs using nitric oxide post-deposition annealing. Current Appl. Phys. 2020, 20, 1386–1390. [Google Scholar] [CrossRef]

- Kimoto, T.; Kawano, H.; Noborio, M.; Suda, J. Improved dielectric and interface properties of 4H-SiC MOS structures processed by oxide deposition and N2O annealing. Mat. Sci. Forum. 2006, 527, 987–990. [Google Scholar] [CrossRef]

- Yano, H.; Furumoto, Y.; Niwa, T.; Hatayama, T.; Uraoka, Y.; Fuyuki, T. Radical nitridation of ultra-thin SiO2/SiC structure. Mat. Sci. Forum. 2004, 457, 1333–1336. [Google Scholar] [CrossRef]

- Yang, X.; Lee, B.; Misra, V. Electrical characteristics of SiO2 deposited by atomic layer deposition on 4H–SiC after nitrous oxide anneal. IEEE Trans. Electron Devices. 2016, 63, 2826–2830. [Google Scholar] [CrossRef]

- Schilirò, E.; Lo Nigro, R.; Fiorenza, P.; Roccaforte, F. Negative charge trapping effects in Al2O3 films grown by atomic layer deposition onto thermally oxidized 4H-SiC. AIP Adv. 2016, 6, 075021. [Google Scholar] [CrossRef]

- Jayawardhena, I.U.; Ramamurthy, R.P.; Morisette, D.; Ahyi, A.C.; Thorpe, R.; Kuroda, M.A.; Feldman, L.C.; Dhar, S. Effect of surface treatments on ALD Al2O3/4H-SiC metal–oxide–semiconductor field-effect transistors. J. App. Phys. 2021, 129, 075702. [Google Scholar] [CrossRef]

- Cheong, K.Y.; Moon, J.H.; Park, T.J.; Kim, J.H.; Hwang, C.S.; Kim, H.J.; Bahng, W.; Kim, N.K. Improved electronic performance of HfO2/SiO2 stacking gate dielectric on 4H SiC. IEEE Trans. Electron Devices. 2007, 54, 3409–3413. [Google Scholar] [CrossRef]

- Liang, L.; Li, W.; Li, S.; Li, X.; Wu, Y. Interface properties study on SiC MOS with high-k hafnium silicate gate dielectric. AIP Adv. 2018, 8, 125314. [Google Scholar] [CrossRef]

- Hosoi1, T.; Azumo, S.; Kashiwagi, Y.; Hosaka, S.; Yamamoto, K.; Aketa, M.; Asahara, H.; Nakamura, T.; Kimoto, T. Comprehensive and systematic design of metal/high-k gate stack for high-performance and highly reliable SiC power MOSFET. Jpn. J. Appl. Phys. 2020, 59, 021001. [Google Scholar] [CrossRef]

- Okamoto, D.; Yano, H.; Hirata, K.; Hatayama, T.; Fuyuki, T. Improved inversion channel mobility in 4H-SiC MOSFETs on Si face utilizing phosphorus-doped gate oxide. IEEE Electron Device Lett. 2010, 31, 710–712. [Google Scholar] [CrossRef]

- Yano, H.; Kanafuji, N.; Osawa, A.; Hatayama, T.; Fuyuki, T. Threshold voltage instability in 4H-SiC MOSFETs with phosphorus-doped and nitrided gate oxides. IEEE Trans. Electron Devices. 2015, 62, 324–332. [Google Scholar] [CrossRef]

- Park, C.J.; Jung, S.M.; Kim, J.H.; Shin, M.W. Conformal doping strategy for fin structures: Tailoring of dopant profile through multiple monolayer doping and capping layer control. Semicond. Sci. Tech. 2020, 35, 055028. [Google Scholar] [CrossRef]

- Barri, C.; Mafakheri, E.; Fagiani, L.; Tavani, G.; Barzaghi, A.; Chrastina, D.; Fedorov, A.; Frigerio, J.; Lodari, M.; Scotognella, F.; et al. Engineering of the spin on dopant process on silicon on insulator substrate. Nanotechnology 2020, 32, 025303. [Google Scholar] [CrossRef]

- Katsumata, R.; Limary, R.; Zhang, Y.; Popere, B.C.; Heitsch, T.A.; Li, M.; Trefonas, P.; Segalman, R.A. Mussel-inspired strategy for stabilizing ultrathin polymer films and its application to spin-on doping of semiconductors. Chem. Mater. 2018, 30, 5285–5292. [Google Scholar] [CrossRef]

- Bollani, M.; Salvalaglio, M.; Benali, A.; Bouabdellaoui, M.; Naffouti, M.; Lodari, M.; Corato, S.D.; Fedorov, A.; Voigt, A.; Fraj, I.; et al. Templated dewetting of single-crystal sub-millimeter-long nanowires and on-chip silicon circuits. Nat. Commun. 2019, 10, 5632. [Google Scholar] [CrossRef] [PubMed]

- Lichtenwalner, D.J.; Cheng, L.; Dhar, S.; Agarwal, A.; Palmour, J.W. High mobility 4H-SiC (0001) transistors using alkali and alkaline earth interface layers. Appl. Phys. Lett. 2014, 105, 182107. [Google Scholar] [CrossRef]

- Liu, M.; Zhang, S.; Yang, X.; Chen, X.; Fan, Z.; Wang, X.; Yang, F.; Ma, C.; He, Z. Enhancing oxidation rate of 4H–SiC by oxygen ion implantation. J. Mater. Sci. 2019, 54, 1147–1152. [Google Scholar] [CrossRef]

- Ishiji, K.; Kawado, S.; Hirai, Y.; Nagamachi, S. Appearance of local strain fields and high electrical conductivity of macro-defects in P+-implanted 4H-SiC. J. Appl. Phys. 2013, 113, 194505. [Google Scholar] [CrossRef]

- Dhar, S.; Davis, R.P.; Feldman, L.C. A novel technique for the fabrication of nanostructures on silicon carbide using amorphization and oxidation. Nanotechnology 2006, 17, 4514–4518. [Google Scholar] [CrossRef]

- Okada, T.; Negoro, Y.; Kimoto, T.; Okamoto, K.; Kujime, N.; Tanaka, N.; Matsunami, H. Defect formation in (0001)-and (1120)-oriented 4H-SiC crystals P+-Implanted at room temperature. Jpn. J. Appl. Phys. 2004, 43, 6884. [Google Scholar] [CrossRef]

- Daas, B.K.; Islam, M.M.; Chowdhury, I.A.; Zhao, F.; Sudarshan, T.S.; Chandrashekhar, M.V.S. Doping dependence of thermal oxidation on n-Type 4H-SiC. IEEE Trans. Electron Devices. 2011, 58, 115–121. [Google Scholar] [CrossRef]

- Kim, H.K.; Kim, S.J.; Buettner, J.; Lim, M.W.; Erlbacher, T.; Bauer, A.J.; Koo, S.M.; Lee, N.S.; Shin, H.K. Surface characterization of ion implanted 4H-SiC epitaxial layers with ion energy and concentration variations. Mater. Sci. Forum. 2019, 963, 429–432. [Google Scholar] [CrossRef]

- Jia, Y.; Lv, H.; Tang, X.; Han, C.; Song, Q.; Zhang, Y.; Zhang, Y.; Dimitrijev, S.; Han, J.; Haasmann, D. Influence of various NO annealing conditions on N-type and P-type 4H-SiC MOS capacitors. J. Mater. Sci. Mater. Electron. 2019, 30, 10302–10310. [Google Scholar] [CrossRef]

- Yen, C.T.; Hung, C.C.; Hung, H.T.; Lee, C.Y.; Lee, L.S.; Huang, Y.F.; Hsu, F.J. Negative bias temperature instability of SiC MOSFET induced by interface trap assisted hole trapping. Appl. Phys. Lett. 2016, 108, 012106. [Google Scholar] [CrossRef]

- Suzuki, S.; Harada, S.; Kosugi, R.; Senzaki, J.; Cho, W.J.; Fukuda, K. Correlation between channel mobility and shallow interface traps in SiC metal–oxide–semiconductor field-effect transistors. J. Appl. Phys. 2002, 92, 6230–6234. [Google Scholar] [CrossRef]

- Zheleva, T.; Lelis, A.; Duscher, G.; Liu, F.; Levin, I.; Das, M. Transition layers at the SiO2/SiC interface. Appl. Phys. Lett. 2008, 93, 022108. [Google Scholar] [CrossRef]

- Caccia, M.; Giuranno, D.; Molina-Jorda, J.M.; Moral, M.; Nowak, R.; Ricci, E.; Sobczak, N.; Narciso, J.; Sanz, J.F. Graphene translucency and interfacial interactions in the gold/graphene/sic system. Phys. Chem. Lett. 2018, 9, 3850–3855. [Google Scholar] [CrossRef]

- Li, H.; Dimitrijev, S.; Sweatman, D.; Harrison, H.B.; Tanner, P. Investigation of nitric oxide and Ar annealed SiO2/SiC interfaces by x-ray photoelectron spectroscopy. J. Appl. Phys. 1999, 86, 4316–4321. [Google Scholar] [CrossRef]

- Kim, D.K.; Jeong, K.S.; Kang, Y.S.; Kang, H.K.; Cho, S.W.; Kim, S.O.; Suh, D.; Kim, S.; Cho, M.H. Controlling the defects and transition layer in SiO2 films grown on 4H-SiC via direct plasma-assisted oxidation. Sci. Rep. 2016, 6, 34945. [Google Scholar] [CrossRef]

| Implantation Condition | Oxide Condition | NO Annealing Condition | ||||

|---|---|---|---|---|---|---|

| Dosage (cm2) | Energy (keV) | Temperature (°C) | Time (min) | Temperature (°C) | Time (min) | |

| OX | - | - | 1400 | 13 | - | - |

| OX-NO | - | - | 1400 | 13 | 1200 | 70 |

| Low-imp-OX | 1012 | 30 | 1400 | 13 | - | - |

| High-imp-OX | 1013 | 30 | 1400 | 13 | - | - |

| High-imp-OX-NO | 1013 | 30 | 1400 | 13 | 1200 | 70 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, S.; Luo, J.; Ye, T. Investigation of Reducing Interface State Density in 4H-SiC by Increasing Oxidation Rate. Nanomaterials 2023, 13, 1568. https://doi.org/10.3390/nano13091568

Li S, Luo J, Ye T. Investigation of Reducing Interface State Density in 4H-SiC by Increasing Oxidation Rate. Nanomaterials. 2023; 13(9):1568. https://doi.org/10.3390/nano13091568

Chicago/Turabian StyleLi, Shuai, Jun Luo, and Tianchun Ye. 2023. "Investigation of Reducing Interface State Density in 4H-SiC by Increasing Oxidation Rate" Nanomaterials 13, no. 9: 1568. https://doi.org/10.3390/nano13091568

APA StyleLi, S., Luo, J., & Ye, T. (2023). Investigation of Reducing Interface State Density in 4H-SiC by Increasing Oxidation Rate. Nanomaterials, 13(9), 1568. https://doi.org/10.3390/nano13091568