A Novel Source/Drain Extension Scheme with Laser-Spike Annealing for Nanosheet Field-Effect Transistors in 3D ICs

Abstract

1. Introduction

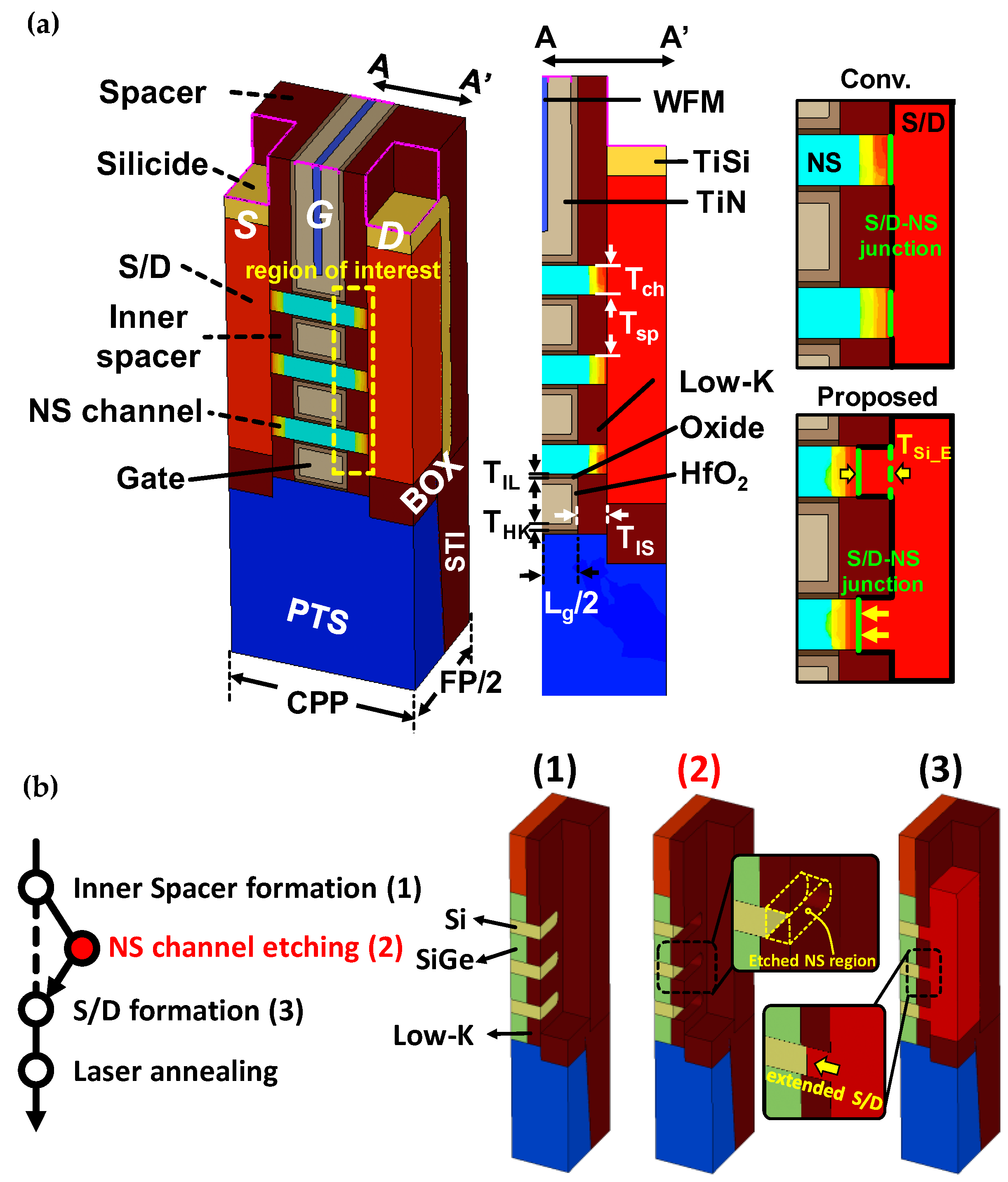

2. Device Structure and Simulation Methodology

- Recombination models (Auger and Shockley–Read–Hall) were used to consider carrier generation and recombination.

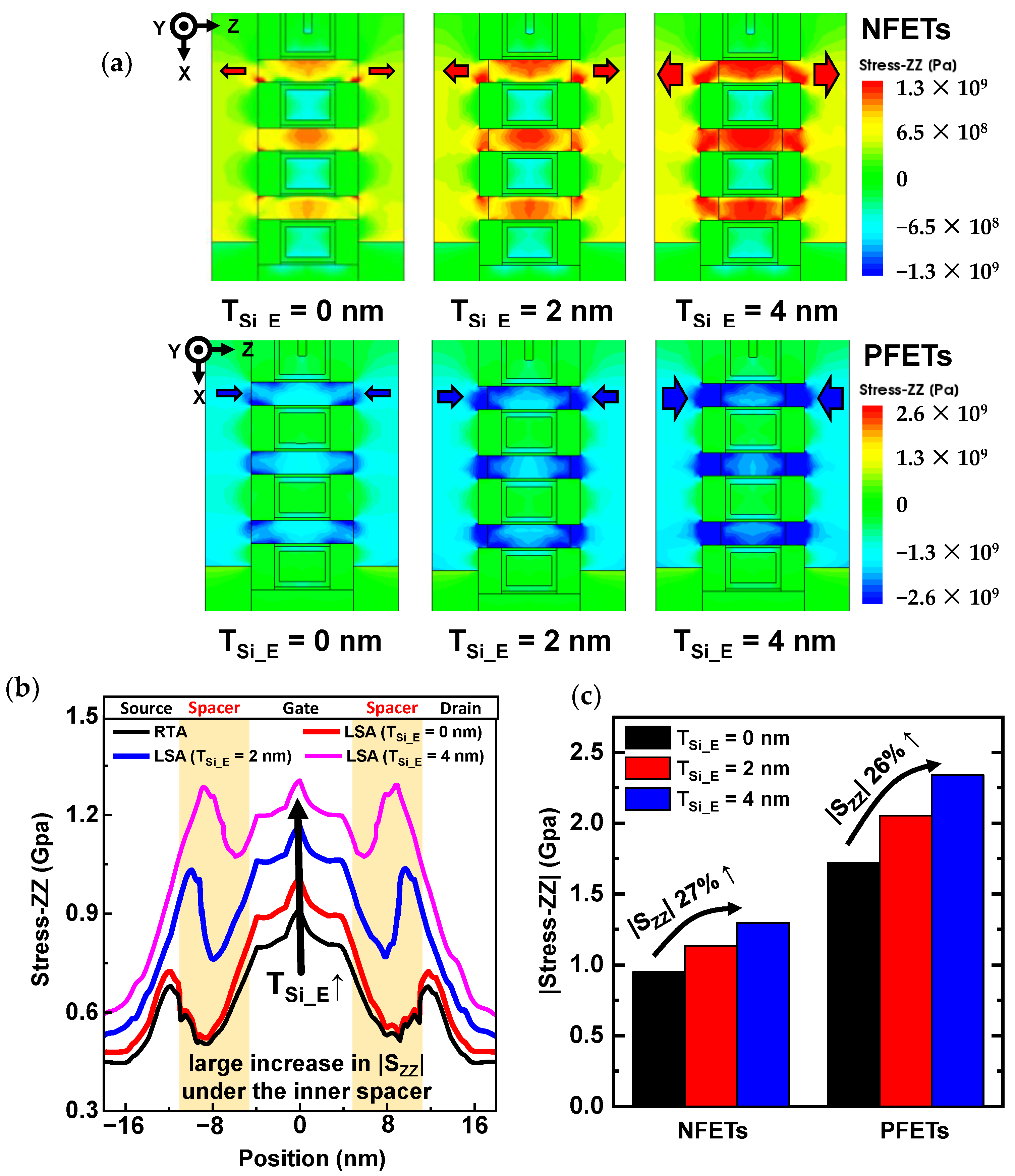

- The deformation potential model was used because the band structure and effective mass of the electron/hole change according to the tensile/compressive stress [31].

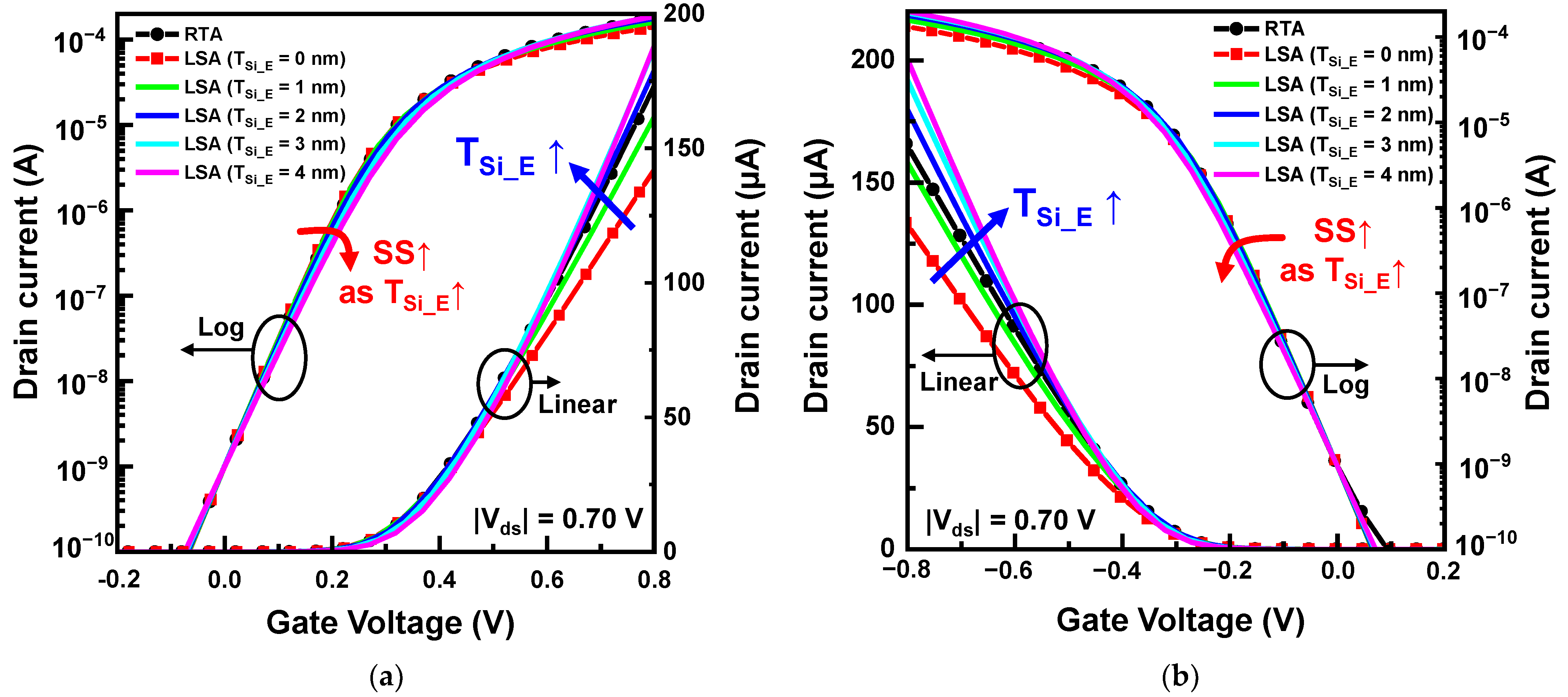

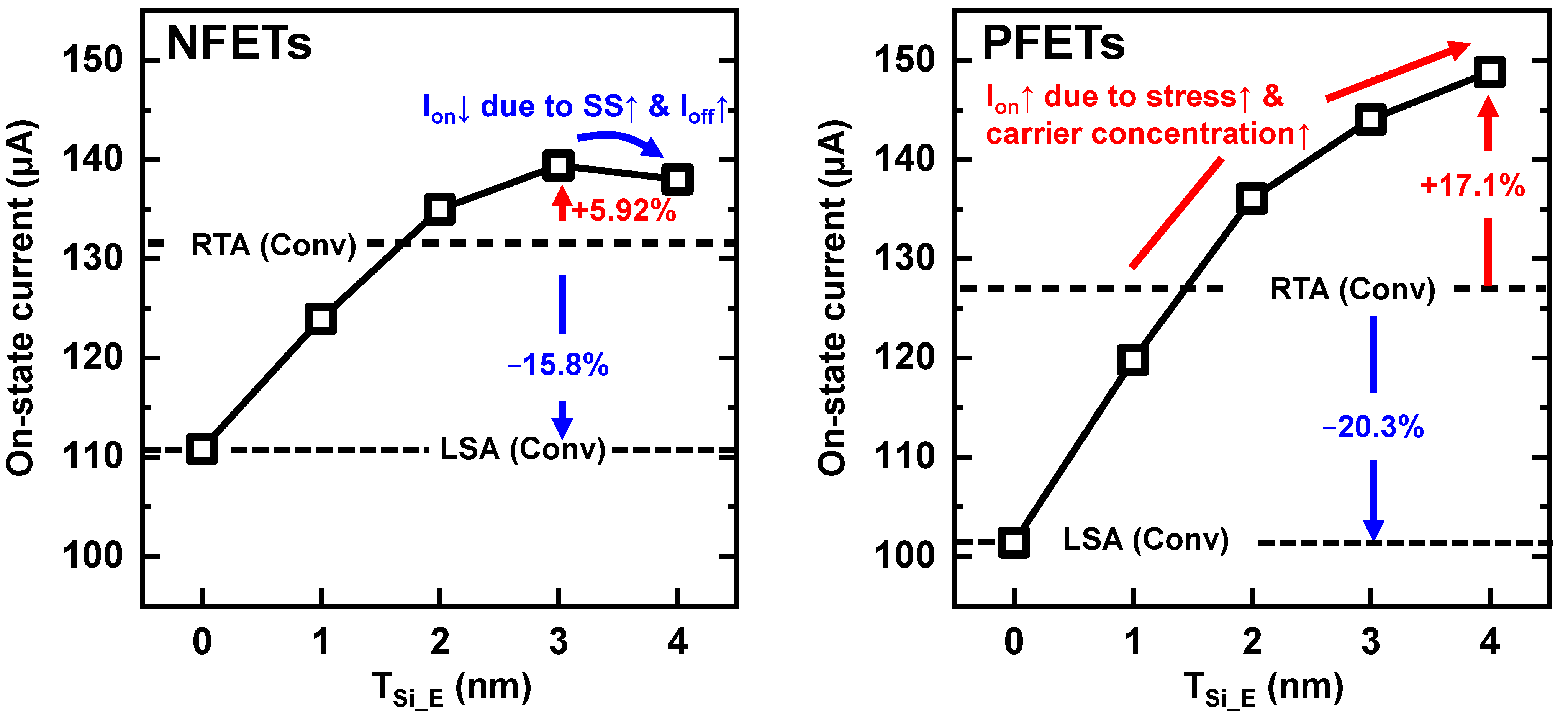

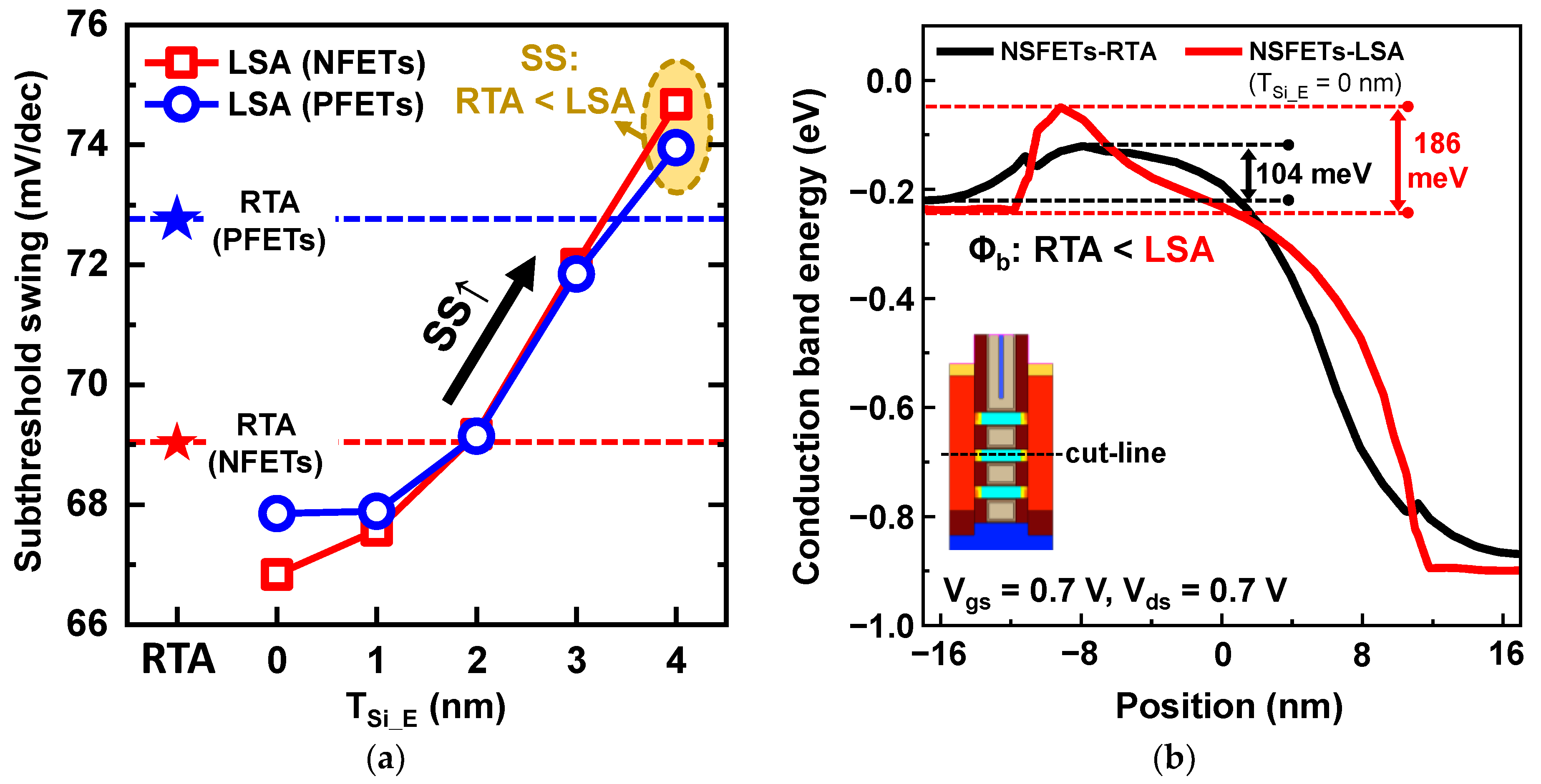

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Ghani, T.; Armstrong, M.; Auth, C.; Bost, M.; Charvat, P.; Glass, G.; Hoffmann, T.; Johnson, K.; Kenyon, C.; Klaus, J.; et al. A 90 nm High Volume Manufacturing Logic Technology Featuring Novel 45 nm Gate Length Strained Silicon CMOS Transistors. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 8–10 December 2003; pp. 11.6.1–11.6.3. [Google Scholar]

- Mistry, K.; Chau, R.; Choi, C.-H.; Ding, G.; Fischer, K.; Ghani, T.; Grover, R.; Han, W.; Hanken, D.; Hattendorf, M.; et al. A 45 nm Logic Technology with High-K+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193 nm Dry Patterning, and 100% Pb-Free Packaging. In Proceedings of the 2007 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 10–12 December 2007; pp. 247–250. [Google Scholar]

- Cheng, K.; Khakifirooz, A.; Kulkarni, P.; Ponoth, S.; Kuss, J.; Shahrjerdi, D.; Edge, L.F.; Kimball, A.; Kanakasabapathy, S.; Xiu, K.; et al. Extremely Thin SOI (ETSOI) CMOS with Record Low Variability for Low Power System-on-Chip Applications. In Proceedings of the Technical Digest—International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 49–52. [Google Scholar]

- Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V.; Ghani, T.; Glassman, T.; et al. A 22 nm High Performance and Low-Power CMOS Technology Featuring Fully-Depleted Tri-Gate Transistors, Self-Aligned Contacts and High Density MIM Capacitors. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; Volume 980, pp. 131–132. [Google Scholar]

- Lin, C.; Greene, B.; Narasimha, S.; Cai, J.; Bryant, A.; Radens, C.; Narayanan, V.; Linder, B.; Ho, H.; Aiyar, A.; et al. High Performance 14 nm SOI FinFET CMOS Technology with 0.0174 μm2 Embedded DRAM and 15 Levels of Cu Metallization. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014; pp. 74–76. [Google Scholar]

- Xie, R.; Montanini, P.; Akarvardar, K.; Tripathi, N.; Haran, B.; Johnson, S.; Hook, T.; Hamieh, B.; Corliss, D.; Wang, J.; et al. A 7 nm FinFET Technology Featuring EUV Patterning and Dual Strained High Mobility Channels. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; Volume 12, pp. 47–50. [Google Scholar]

- Bae, G.; Bae, D.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3nm GAA Technology Featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 28.7.1–28.7.4. [Google Scholar] [CrossRef]

- He, X.; Fronheiser, J.; Zhao, P.; Hu, Z.; Uppal, S.; Wu, X.; Hu, Y.; Sporer, R.; Qin, L.; Krishnan, R.; et al. Impact of Aggressive Fin Width Scaling on FinFET Device Characteristics. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 20.2.1–20.2.4. [Google Scholar]

- Maszara, W.P.; Lin, M. FinFETs-Technology and Circuit Design Challenges. In Proceedings of the 2013 Proceedings of the ESSCIRC (ESSCIRC), Bucharest, Romania, 16–20 September 2013; pp. 3–8.

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked Nanosheet Gate-All-around Transistor to Enable Scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; Volume 5, p. T230. [Google Scholar]

- Harsha Vardhan, P.; Amita; Ganguly, S.; Ganguly, U. Threshold Voltage Variability in Nanosheet GAA Transistors. IEEE Trans. Electron Devices 2019, 66, 4433–4438. [Google Scholar] [CrossRef]

- Barraud, S.; Lapras, V.; Previtali, B.; Samson, M.P.; Lacord, J.; Martinie, S.; Jaud, M.; Athanasiou, S.; Triozon, F. Performance and Design Considerations for gate-all-around stacked-NanoWires FETs. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 1–4. [Google Scholar]

- Shi, J.; Nayak, D.; Ichihashi, M.; Banna, S.; Moritz, C.A. On the Design of Ultra-High Density 14 nm Finfet Based Transistor-Level Monolithic 3d Ics. In Proceedings of the 2016 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Pittsburgh, PA, USA, 11–13 July 2016; pp. 449–454. [Google Scholar] [CrossRef]

- Davis, W.R.; Wilson, J.; Mick, S.; Jian, X.; Hao, H.; Mineo, C.; Sule, A.M.; Steer, M.; Franzon, P.D. Demystifying 3D ICs: The Pros and Cons of Going Vertical. IEEE Des. Test Comput. 2005, 22, 498–510. [Google Scholar] [CrossRef]

- Vandooren, A.; Witters, L.; Franco, J.; Mallik, A.; Parvais, B.; Wu, Z.; Li, W.; Rosseel, E.; Hikkavyy, A.; Peng, L.; et al. Key Challenges and Opportunities for 3D Sequential Integration. In Proceedings of the 2018 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 15–18 October 2018; pp. 2–5. [Google Scholar]

- Fenouillet-Beranger, C.; Previtali, B.; Batude, P.; Nemouchi, F.; Cassé, M.; Garros, X.; Tosti, L.; Rambal, N.; Lafond, D.; Dansas, H.; et al. FDSOI Bottom MOSFETs Stability versus Top Transistor Thermal Budget Featuring 3D Monolithic Integration. Solid. State. Electron. 2015, 113, 2–8. [Google Scholar] [CrossRef]

- Yang, C.; Shieh, J.; Hsieh, T.; Huang, W.; Wang, H.; Wu, T.; Hou, Y.; Chen, Y.; Lee, Y.; Chen, M.; et al. Enabling Low Power BEOL Compatible Monolithic 3D + Nanoelectronics for IoTs Using Local and Selective Far-Infrared Ray Laser Anneal Technology. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 205–208. [Google Scholar]

- Fenouillet-Beranger, C.; Acosta-Alba, P.; Mathieu, B.; Kerdiles, S.; Samson, M.; Previtali, B.; Rambal, N.; Lapras, V.; Ibars, F.; Roman, A.; et al. Ns Laser Annealing for Junction Activation Preserving Inter-Tier Interconnections Stability within a 3D Sequential Integration. In Proceedings of the 2016 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 10–13 October 2016; pp. 1–2. [Google Scholar]

- Henning, A.K.; Rajendran, B.; Cronquist, B.; Or-Bach, Z. Thermal Considerations for Monolithic Integration of Three-Dimensional Integrated Circuits. In Proceedings of the 2013 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Monterey, CA, USA, 7–10 October 2013; pp. 3–4. [Google Scholar] [CrossRef]

- Yoon, J.S.; Rim, T.U.; Kim, J.S.; Kim, K.H.; Baek, C.K.; Jeong, Y.H.A. Statistical Variability Study of Random Dopant Fluctuation on Gate-All-around Inversion- Mode Silicon Nanowire Field-Effect Transistors. Appl. Phys. Lett. 2021, 103507, 6–11. [Google Scholar] [CrossRef]

- Hsu, W.; Wen, F.; Wang, X.; Wang, Y.; Dolocan, A.; Roy, A.; Kim, T.; Tutuc, E.; Member, S.; Banerjee, S.K. Laser Spike Annealing for Shallow Junctions in Ge CMOS. IEEE Trans. Electron Devices 2017, 64, 346–352. [Google Scholar] [CrossRef]

- Sentaurus, Version O-2019.12-SP1; Synopsys Inc.: Mountain View, CA, USA, 2019.

- Ancona, M.G.; Tiersten, H.F. Macroscopic Physics of the Silicon Inversion Layer. Phys. Rev. B 1987, 35, 7959–7965. [Google Scholar] [CrossRef] [PubMed]

- Ancona, M.G.; Iafrate, G.J. Quantum Correction to the Equation of State of an Electron Gas in a Semiconductor. Phys. Rev. B 1989, 39, 9536–9540. [Google Scholar] [CrossRef] [PubMed]

- Slotboom, J.W.; de Graaff, H.C. Measurements of Bandgap Narrowing in Si Bipolar Transistors. Solid State Electron. 1976, 19, 857–862. [Google Scholar] [CrossRef]

- Klaassen, D.B.M.; Slotboom, J.W.; de Graaff, H.C. Unified Apparent Bandgap Narrowing in N- and p-Type Silicon. Solid. State. Electron. 1992, 35, 125–129. [Google Scholar] [CrossRef]

- Shur, M.S. Low Ballistic Mobility in Submicron HEMTs. IEEE Electron Device Lett. 2002, 23, 511–513. [Google Scholar] [CrossRef]

- Canali, C.; Majni, G.; Minder, R.; Ottaviani, G. Electron and Hole Drift Velocity Measurements in Silicon and Their Empirical Relation to Electric Field and Temperatures. IEEE Trans. Electron Devices 1976, 23, 1113. [Google Scholar] [CrossRef]

- Ando, T. Ultimate Scaling of High-κ Gate Dielectrics: Higher-κ or Interfacial Layer Scavenging? Materials 2012, 5, 478–500. [Google Scholar] [CrossRef] [PubMed]

- Mujtaba, S.A. Advanced Mobility Models for Design and Simulation of Deep Submicron MOSFETs. Ph.D. Dissertation, Department Electrical Engineering Stanford University, Stanford, CA, USA, 1996. [Google Scholar]

- Bardeen, J.; Shockley, W. Deformation Potentials and Mobilities in Non-Polar Crystals. Phys. Rev. 1950, 80, 72–80. [Google Scholar] [CrossRef]

- Zhang, J.; Pancharatnam, S.; Adams, C.; Wu, H.; Zhou, H.; Shen, T.; Xie, R.; Sankarapandian, M.; Wang, J.; Watanabe, K.; et al. Full Bottom Dielectric Isolation to Enable Stacked Nanosheet Transistor for Low Power and High Performance Applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 250–253. [Google Scholar] [CrossRef]

- Jeong, J.; Yoon, J.S.; Lee, S.; Baek, R.H. Comprehensive Analysis of Source and Drain Recess Depth Variations on Silicon Nanosheet FETs for Sub 5-Nm Node SoC Application. IEEE Access 2020, 8, 35873–35881. [Google Scholar] [CrossRef]

- Loubet, N.; Kal, S.; Alix, C.; Pancharatnam, S.; Zhou, H.; Durfee, C.; Belyansky, M.; Haller, N.; Watanabe, K.; Devarajan, T. A Novel Dry Selective Etch of SiGe for the Enablement of High Performance Logic Stacked Gate-All-Around NanoSheet Devices. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 242–245. [Google Scholar]

- Yoon, J.S.; Jeong, J.; Lee, S.; Lee, J.; Lee, S.; Baek, R.H.; Lim, S.K. Performance, Power, and Area of Standard Cells in Sub 3 Nm Node Using Buried Power Rail. IEEE Trans. Electron Devices 2022, 69, 894–899. [Google Scholar] [CrossRef]

- Lee, S.; Jeong, J.; Yoon, J.S.; Lee, S.; Lee, J.; Lim, J.; Baek, R.H. Sensitivity of Inner Spacer Thickness Variations for Sub-3-Nm Node Silicon Nanosheet Field-Effect Transistors. Nanomaterials 2022, 12, 3349. [Google Scholar] [CrossRef] [PubMed]

- Mochizuki, S.; Colombeau, B.; Yu, L.; Dube, A.; Choi, S.; Stolfi, M.; Bi, Z.; Chang, F.; Conti, R.A.; Liu, P.; et al. Advanced Arsenic Doped Epitaxial Growth for Source Drain Extension Formation in Scaled FinFET Devices. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 35.2.1–35.2.4. [Google Scholar] [CrossRef]

- Zangenberg, N.R.; Fage-Pedersen, J.; Hansen, J.L.; Larsen, A.N. Boron and Phosphorus Diffusion in Strained and Relaxed Si and SiGe. J. Appl. Phys. 2003, 94, 3883–3890. [Google Scholar] [CrossRef]

| Fixed Parameters | Values |

|---|---|

| Contact poly pitch (CPP) | 42 nm |

| Fin pitch (FP) | 60 nm |

| Gate length (Lg) | 12 nm |

| Spacing thickness (Tsp) | 10 nm |

| NS thickness (Tch) | 5 nm |

| Interfacial layer/HfO2 thickness (TIL/THK) | 0.6 nm/1.1 nm |

| Inner spacer thickness (TIS) | 5 nm |

| S/D doping concentration (NSD) | 4 × 1020 cm−3 |

| PTS doping concentration (NPTS) | 5 × 1018 cm−3 |

| Variable Parameters | Values |

| Etch depth of the NS channel (TSi_E) | 0–4 nm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.; Jeong, J.; Kang, B.; Lee, S.; Lee, J.; Lim, J.; Hwang, H.; Ahn, S.; Baek, R. A Novel Source/Drain Extension Scheme with Laser-Spike Annealing for Nanosheet Field-Effect Transistors in 3D ICs. Nanomaterials 2023, 13, 868. https://doi.org/10.3390/nano13050868

Lee S, Jeong J, Kang B, Lee S, Lee J, Lim J, Hwang H, Ahn S, Baek R. A Novel Source/Drain Extension Scheme with Laser-Spike Annealing for Nanosheet Field-Effect Transistors in 3D ICs. Nanomaterials. 2023; 13(5):868. https://doi.org/10.3390/nano13050868

Chicago/Turabian StyleLee, Sanguk, Jinsu Jeong, Bohyeon Kang, Seunghwan Lee, Junjong Lee, Jaewan Lim, Hyeonjun Hwang, Sungmin Ahn, and Rockhyun Baek. 2023. "A Novel Source/Drain Extension Scheme with Laser-Spike Annealing for Nanosheet Field-Effect Transistors in 3D ICs" Nanomaterials 13, no. 5: 868. https://doi.org/10.3390/nano13050868

APA StyleLee, S., Jeong, J., Kang, B., Lee, S., Lee, J., Lim, J., Hwang, H., Ahn, S., & Baek, R. (2023). A Novel Source/Drain Extension Scheme with Laser-Spike Annealing for Nanosheet Field-Effect Transistors in 3D ICs. Nanomaterials, 13(5), 868. https://doi.org/10.3390/nano13050868