Abstract

Two-dimensional (2D) transition-metal dichalcogenides (TMDs) materials, such as molybdenum disulfide (MoS2), stand out due to their atomically thin layered structure and exceptional electrical properties. Consequently, they could potentially become one of the main materials for future integrated high-performance logic circuits. However, the local back-gate-based MoS2 transistors on a silicon substrate can lead to the degradation of electrical characteristics. This degradation is caused by the abnormal effect of gate sidewalls, leading to non-uniform field controllability. Therefore, the buried-gate-based MoS2 transistors where the gate electrodes are embedded into the silicon substrate are fabricated. The several device parameters such as field-effect mobility, on/off current ratio, and breakdown voltage of gate dielectric are dramatically enhanced by field-effect mobility (from 0.166 to 1.08 cm2/V·s), on/off current ratio (from 4.90 × 105 to 1.52 × 107), and breakdown voltage (from 15.73 to 27.48 V) compared with a local back-gate-based MoS2 transistor, respectively. Integrated logic circuits, including inverters, NAND, NOR, AND, and OR gates, were successfully fabricated by 2-inch wafer-scale through the integration of a buried-gate MoS2 transistor array.

1. Introduction

Graphene, which consists of an atomic thickness arrangement of carbon atoms in a hexagonal lattice, was discovered by Andre Geim and Konstantine Novoselov in 2004 [1,2,3]. Since then, in recent years, graphene has received significant attention as a revolutionary material owing to its excellent mechanical strength and remarkable electrical conductivity, which presents exciting potential for next-generation electronic devices. Furthermore, graphene’s high electron mobility promotes fast electron movement with minimal scattering, offering advantages for high-speed electronic devices [4,5,6]. While graphene lacks intrinsic bandgap, semiconductors usually have a bandgap that allows them to switch between conducting and insulating states. However, the band structure of graphene shows linearity that offers excellent conductivity, but the on/off ratio of graphene-based transistors can be relatively low. Thus, it is difficult to create the off-state and it can cause problems when trying to precisely control current flow, which is critical for digital logic operation. However, there are actively researched approaches for new materials, such as two-dimensional (2D) transition metal dichalcogenides (TMDs) that possess semiconductor properties, thus addressing certain limitations of graphene [7,8,9,10,11]. Also, high-performance organic transistors have been pursued [12,13,14].

Among them, two-dimensional (2D) transition metal dichalcogenides (TMDs) materials, such as molybdenum disulfide (MoS2), tungsten disulfide (WS2), tungsten diselenide (WSe2), and others, are attracting attention as promising materials for next-generation electronic devices [15,16]. Two-dimensional (2D) transition metal dichalcogenides (TMDs) materials are single-layer atomic structures [17,18] exhibiting excellent stability and a wide range of properties due to strong covalent and Van der Waals forces [15,19,20,21]. In addition, they stand out as high-level electrical properties such as tunable band gaps, low power consumption, high field-effect mobility, and switching characteristics owing to the high on/off ratio [22,23]. Therefore, it shows a wide range of applications in the various fields. For example, previous reports on photodetectors [24], optoelectronic memories [25], sensors [26], flexible electronic devices, and logic devices are currently being actively studied [7,27,28,29,30,31].

Specifically, 2D semiconductors such as molybdenum disulfide (MoS2) can be fabricated in high-quality electronic-grade quality on a wafer-scale [27,31,32]. The MoS2 could provide the ultra-thin body of sub-1 nm with an intrinsic flat surface which is immune to the short-channel effect. Moreover, high-electron mobility comparable to the silicon channel has been reported with the development of the chemical vapor deposition (CVD) or metal-organic chemical vapor deposition (MOCVD) growth technique. Therefore, it is a promising 2D material for the potential perspective of more Moore and more than Moore pushing technology [16,33,34,35,36,37,38]. When considering device architectures, several critical factors determine device performance, including contact resistance, dielectric scaling, and conformal gate controllability. In general, the MoS2 field-effect transistor (FET) based on a local back-gate structure results in non-uniform distribution of the gate electric field. This is caused by an abnormal gate shape that occurs during the conventional lift-off process [39,40]. As a result, the intrinsic electrical performance of 2D FETs is significantly degraded.

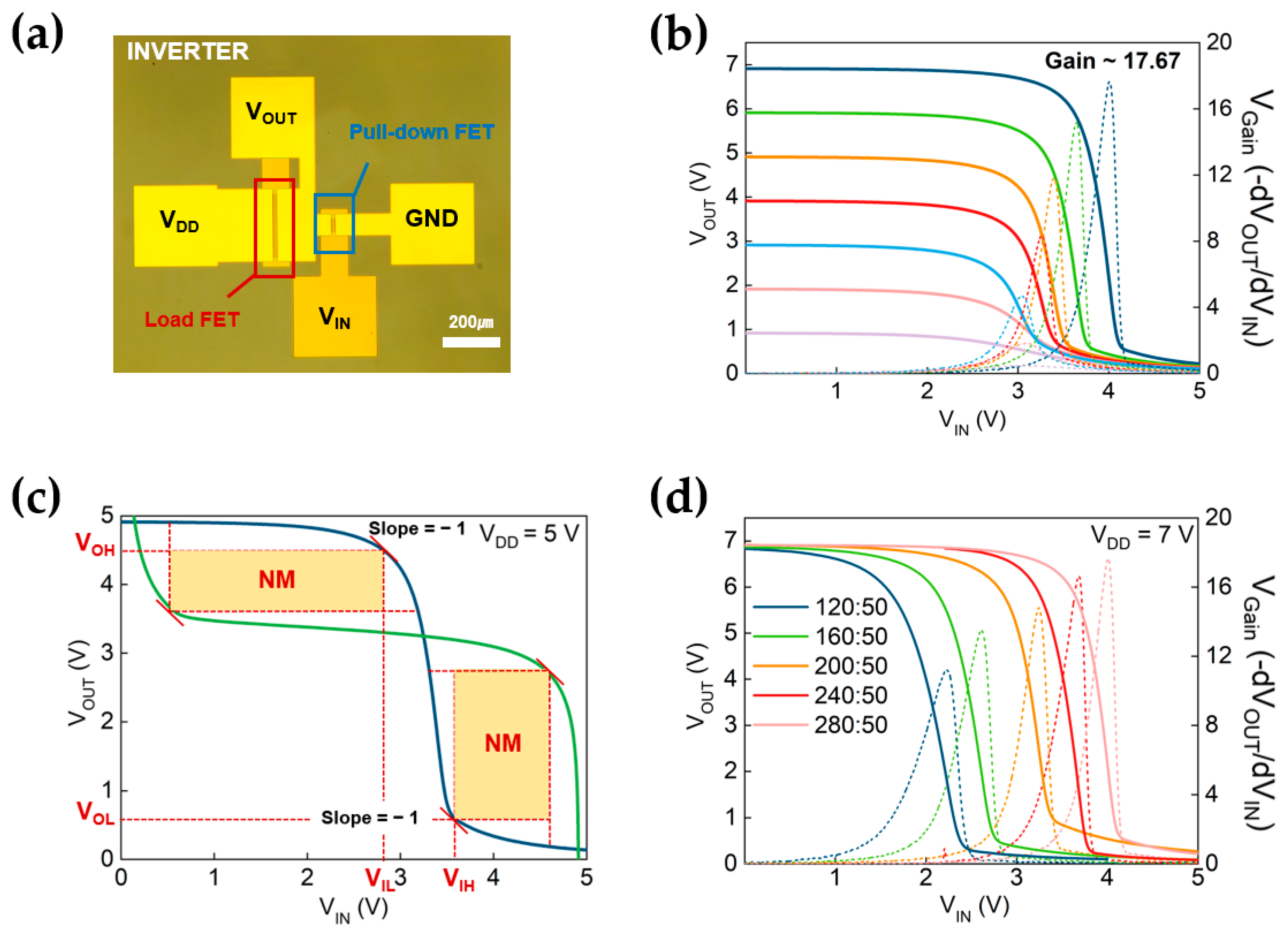

In this study, the implementation of a buried-gate structure for uniform field induction leads to the improvement of the performance of 2D-MoS2 FETs and integrated circuits on a 2-inch scale wafer. By comparing the device performance of local back-gate 2D-MoS2 FETs, some parameters showed significant improvements. For instance, the field-effect mobility increased from 0.166 to 1.08 cm2/V·s (6.5 times increase), the on/off current ratio increased from 4.90 × 105 to 1.52 × 107 (3.1 × 101 times), and the breakdown voltage increased from 15.73 to 27.48 V, respectively. In addition, it was confirmed that the buried-gate structure showed high uniformity and lower dispersion, while maintaining the on-current state. A high-speed inverter was fabricated using two FETs (a Load FET and a Pull-down FET), and it achieved a DC voltage gain of 17.67 at VDD = 7 V. Moreover, using direct-coupled FET logic technology, more complicated logic circuits (NAND, NOR, AND, OR) composed of three or five FETs were successfully fabricated. In addition, the characteristics of the logic circuits were compared with those of the local back-gate, and the confirmed improvement in performance. Transistors with buried-gate structures will play a key role in the device applications that require improved performance and stability as they are extremely scaled down. Additionally, these preliminary integration efforts demonstrate the promising potential of implementing complex ICs using wafer-scale 2D semiconductors.

2. Materials and Methods

2.1. Synthesis of MoS2 Film on 2-Inch Wafer-Scale SiO2 (100 nm)/Si (p++) Substrate

A dry-oxidized SiO2 (100 nm)/Si (p++) wafer was cleaned over ultrasonic cleaning for 5 min in acetone, methanol, and isopropyl alcohol (IPA) each. The two-step method was adopted for synthesizing high-quality MoS2 film. To synthesize a MoS2 film, a layer of MoO3 approximately 2.5 nm thick was deposited onto a cleaned 2-inch scale wafer using a Radio Frequency (RF) magnetron sputtering system. MoS2 was subsequently synthesized by sulfurizing deposited MoO3 using thermal Chemical Vapor Deposition (CVD). During the thermal CVD process, the tube furnace was maintained at a working pressure of 800 Torr. The atmosphere was regulated with a gas mixture of Ar/H2S (0.1%) flowing at a rate of 200 sccm. The sulfurization process was initiated by gradually raising the temperature from room temperature to 900 °C over a ramping period. The temperature was maintained at 900 °C for an hour to promote the growth and crystallization of the MoS2 film. The synthesis process for the MoS2 film is illustrated in Figure S2 (Supplementary Materials). Finally, the temperature inside the tube was allowed to naturally cool down to room temperature (R.T.), thus ensuring the preservation of the structural integrity of the MoS2 film.

2.2. Characterization of MoS2 Film

The confirmation of the layered MoS2 film structure on the SiO2 (100 nm)/Si substrate was conducted using Focused Ion-Beam Transmission Electron Microscope (FIB-TEM). Additionally, the elemental compositions (Mo, S, Si, and O) were determined using Energy-Dispersive X-ray Spectroscopy (EDS) mapping analysis. The Raman spectroscopy of the synthesized MoS2 films was measured using a NANOBASE XperRAM-CS Raman spectrometer with 532 nm laser excitation. The components and chemical composition of the MoS2 film were examined thoroughly using X-ray photoelectron spectroscopy (XPS) with NEXSA equipment. Atomic Force Microscope (AFM) was utilized to investigate the surface roughness of the MoS2 film.

2.3. Device Fabrication

A photoresist (PR, AZ 5214) was coated using a spin coater on a SiO2 (100 nm)/Si substrate. The coated substrate was soft baked for 50 s at 110 °C using a hot plate, followed by UV exposure (MDS-400 s) for gate patterning. Subsequently, the PR was stripped using a developer (AZ 300 MIF) for approximately 35~50 s and then hard baked for 5 min at 90 °C on a hot plate. The SiO2 layer of the gate patterned area was etched using Reactive Ion Etching (RIE) with CF4 gas (30 sccm, 100 W, and 2 min). The depth of the etched SiO2 layer has been confirmed to be approximately 60 nm. Subsequently, a Ti/Au (5/50 nm) layer was deposited using an E-beam evaporator. To achieve stable device operation, it was necessary to remove the PR residues that remained along the sidewalls of the patterned PR, as well as the spiky protruding residue resulting from the gate-metal process. Then, a 30 nm Al2O3 layer was deposited as a gate dielectric layer using Plasma-Enhanced Atomic Layer Deposition (PEALD). In order to transfer the MoS2 films on to the target substrate, synthesized MoS2 film was coated with PMMA (KAYAKU A5). The coated MoS2 film was etched in a 5% HF solution for about 30 s, and the separated PMMA/MoS2 film was carefully rinsed three times with deionized (DI) water for five minutes each. Subsequently, the PMMA/MoS2 film was transferred onto the gate dielectric layer, after placing the wet transferred MoS2 film baking at 110 °C for half a day using the hot plate. The wet-transfer process of the MoS2 film is shown in Figure S3 (Supplementary Materials). In order to remove PMMA, the substrate that was transferred with a MoS2 film was removed using acetone and isopropyl alcohol (IPA). Then, an annealing process was performed at 200 °C in a high vacuum (under 10−6 Torr) for an hour.

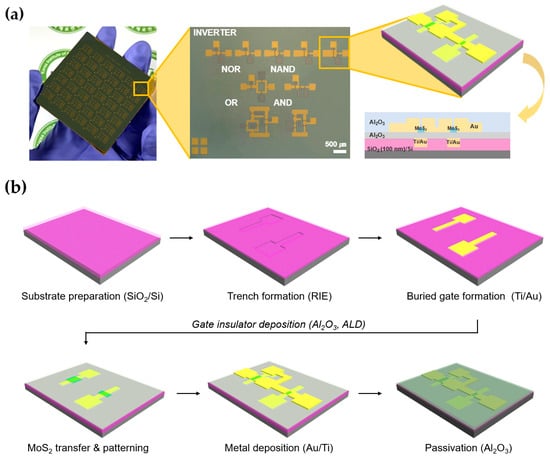

To minimize the PR residue effect on MoS2 film, Au masking fabrication was performed for channel patterning [41,42]. After deposited 20 nm of Au, a channel was formed through the photolithography process. The region excluding the channel was selectively etched using a gold etchant. The active channels of the MoS2 film were formed using Reactive Ion Etching (RIE), and the residual PR was stripped using acetone. This was followed by annealing under the same conditions as described previously. A 50 nm thick layer of Au was deposited on the source/drain using an E-beam evaporator. The pattern-forming process is the same afterwards. Finally, a passivation layer of Al2O3, with a thickness of 30 nm, was deposited using Atomic Layer Deposition (ALD). Figure 1a shows an Optical Microscope (OM) image of the integrated MoS2 logic circuit on a 2-inch wafer, illustrating its components including inverters, NAND, AND, NOR, and OR gates. The fabrication flow scheme for the MoS2 buried-gate inverter is shown in Figure 1b and Figure S1 (Supplementary Materials).

Figure 1.

(a) Optical Microscope (OM) image and schematic of buried-gate-based logic device on 2-inch wafer-scale SiO2 (100 nm)/Si substrate. (b) Schematic of main fabrication process of 2D-MoS2 inverter using buried-gate structure.

2.4. Electrical Measurements

The electrical characteristics of the MoS2 transistor and various logic devices were comprehensively evaluated using a semiconductor parameter analyzer (Keithley-4200 SCS, Keithley, Cleveland, OH, USA) at room temperature (R.T.). A DC voltage bias was applied to VDD using a Source meter (Keithley-2450). Source Measure Units (SMUs) were connected to VIN and VOUT, while the source electrode was connected to GND. The image of the electrical measurement of a logic device using a semiconductor parameter analyzer system is shown in Figure S7 (Supplementary Materials).

3. Results and Discussion

3.1. Characterization of MoS2 on the 2-Inch SiO2 (100 nm)/Si Wafer

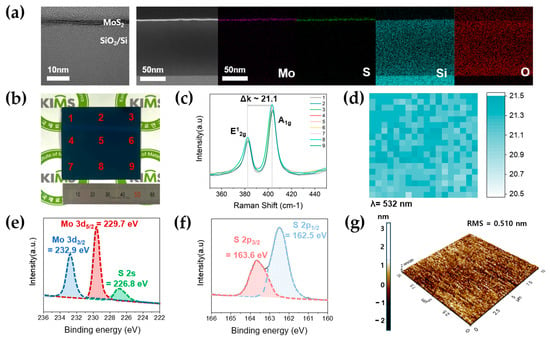

A two-step method was used to achieve the synthesis of high-quality MoS2 films. Figure 2a shows the layered structure of the MoS2 film for ultrathin-cross sections of materials and their subsequent imaging at nanoscale resolutions on the SiO2 (100 nm)/Si substrate, which was confirmed by the focused ion-beam transmission electron microscope (FIB-TEM) image. It provides insights into the internal structure of materials, such as layered structures and interfaces. And, the FIB-TEM tool enables the observation of crystal structures, defects, and nanostructures with atomic-scale resolution [43]. Elemental constituents were identified using Energy-Dispersive X-ray Spectroscopy (EDS) mapping analysis. This method is used in conjunction with electron microscopes such as TEM or SEM to analyze the elemental composition of materials. This is accomplished by detecting the characteristic X-rays emitted as electrons interact with the sample [44]. The synthesized MoS2 film demonstrated a three-layer structure characterized by an atomically smooth and flat morphology. The elements Mo, S, Si, and O were confirmed through EDS elemental mapping. The crystal structure of MoS2 was attributed to the constituents of Mo and S. Figure 2b shows an image of a uniformly synthesized MoS2 film on a 2-inch scale wafer. Figure 2c shows the Raman spectrum of the MoS2 film, which was measured at nine distinct points across the 2-inch wafer-scale. Raman spectroscopy is a non-destructive technique that utilizes laser light scattering to analyze the vibrational and rotational modes of molecules in a sample. The identification of molecular species and chemical bonds allows for the identification of materials [45,46,47,48]. Notably, uniform peaks were consistently observed at these locations. The two pronounced peaks at 382.6 cm−1 and 403.7 cm−1 corresponded to the in-plane vibration (E12g) of Mo and S atoms, and the out-of-plane vibration (A1g) of S atoms. The difference between these peaks, Δk, indicates the number of layers of the MoS2 film. The values exhibited by monolayer and bulk MoS2 Δk are 18.9 cm−1 and 25.2 cm−1, respectively [19,48]. The Δk value of our MoS2 film, measured at 21.1 cm−1, indicates approximately three layers. The Figure S4 (Supplementary Materials) shows the actual Raman mapping image of a 2D-MoS2 film synthesized on a 2-inch scale wafer. The mapping divides an area of 50 × 50 μm2 into sections of 36 points, each with a step size of 10 μm. And, we calculated each of these values ∆k and mapped them to Figure 2d, revealing the values ranging from 20.9 to 21.5 cm−1. The components of the MoS2 film were analyzed using X-ray Photoelectron Spectroscopy (XPS). This measurement tool uses X-ray irradiation to analyze the surface composition and chemical state of materials by measuring the kinetic energy of emitted electrons. XPS analysis can determine the surface concentration of elements [49]. In Figure 2e, the XPS spectra show the peaks at 232.9 eV and 229.7 eV, corresponding to Mo 3d3/2 and Mo 3d5/2, respectively. The peak at 226.8 eV represents S 2s. The XPS spectrum corresponding to S 2p, presented in Figure 2f, displayed prominent peaks at 163.6 eV and 162.5 eV, signifying S 2p3/2 and S 2p1/2, respectively. Figure 2f shows distinct peaks at 163.6 eV and 162.5 eV corresponding to S 2p3/2 and S 2p1/2, respectively [50,51,52]. Furthermore, the determined composition ratio of Mo and S in MoS2 was approximately ~1:2.11. Figure 2g shows an Atomic Force Microscope (AFM) image of the MoS2 film. This provides sub-nanometer resolution of 3D topographic information. It quantifies surface roughness and can detect nanoscale features [53]. The analysis was conducted within a chosen area of 10 μm × 10 μm. The Root Mean Square (RMS) roughness, which serves as a measure of surface uniformity, was measured at 0.510 nm. This confirms that our process enables uniformity on a wafer-scale [54].

Figure 2.

(a) Focused Ion-Beam Transmission Electron Microscope (FIB-TEM) image of transferred MoS2 film on 2-inch wafer-scale SiO2 (100 nm)/Si substrate and mapping of Energy-Dispersive X-ray Spectroscopy (EDS) analysis of MoS2 film. (b) The image of uniformly synthesized MoS2 film on 2-inch scale wafer. A total of 9 Raman mapped locations are indicated. (c) Raman spectrum of MoS2 film on 2-inch SiO2 (100 nm)/Si wafer about 9 points. (d) The mapping image of the MoS2 film represents a value that is calculated from Δk of each data point’s individual value. The mapping divides an area of 50 × 50 μm2 into sections of 36 points, with each section having a step size of 10 μm. (e,f) X-ray Photoelectron Spectroscopy (XPS) spectrum of MoS2 film. (g) The Atomic Force Microscope (AFM) image of MoS2 film.

3.2. Comparative Analysis of Electrical Characteristics between MoS2-Based Transistors with Buried-Gate and Local Back-Gate

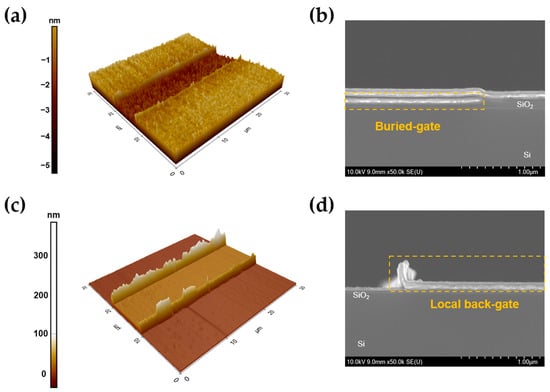

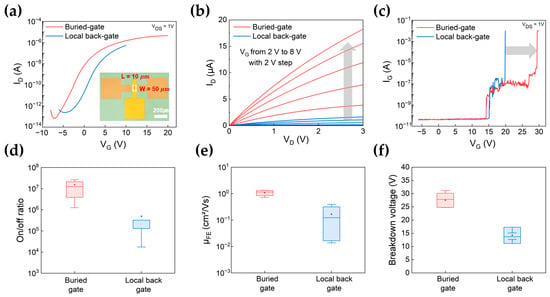

Figure 3a–d show the Atomic Force Microscope (AFM) image and the cross-sectional scanning electron microscope (SEM) image for the buried and local back-gate structure, respectively. The edge of the buried-gate configuration is almost flat. However, the images show that the presence of photoresist (PR) causes the formation of edges in the corner regions, resulting in the development of metallic sidewalls. Figure S5 (Supplementary Materials) shows the height profiles along with the AFM image. Figure S6 (Supplementary Materials) shows SEM images of tilted gate surfaces for the each gate structure. The buried-gate is embedded stably in the etched SiO2 layer and displays a clean edge shape. In contrast, the local back-gate surface features a sidewall at the edge, which leads to the metal being deposited and rolling out, ultimately resulting in a rough surface. When a voltage is applied to the gate, it causes the voltage distribution to become non-uniform and concentrated along the sidewall, resulting in a faster breakdown voltage. This non-uniformity in voltage distribution leads to inconsistent electrical properties and ultimately has a negative impact on device performance when compared to buried-gate structures. The transfer characteristics and output curves in device performance are the fundamental electrical properties for understanding the working principle of MOSFETs. Also, these device characteristics allow for qualitative and quantitative understanding of intrinsic transistor properties such as mobility and carrier density, interface states and contact resistance. Figure 4a shows the transfer characteristic curves (ID − VG) of MoS2 field-effect transistors (FETs) with the buried-gate (red line) and local back-gate (blue line) configurations. Notably, the two types of MoS2 FET devices share identical structures, including channel dimensions (W/L = 50/10 μm), respectively. In terms of representative data, the buried-gate MoS2 FET demonstrates enhanced gate voltage stability and improvement of on-current. The statistical data of the transfer curve of the FETs, according to gate structure, are shown in Figure S8 (Supplementary Materials). Figure 4b shows the output characteristics (ID − VD) of the MoS2 FET. The gate voltage (VG) is varied from 2 to 8 V in steps of 2 V, within VD = 3 V. Notably, the buried-gate FET (red line) shows a higher drain current in comparison to the local back-gate FET (blue line). The gate leakage current and breakdown voltage of the gate dielectric are important factors for determining the stability of the device and the electric field distribution of gate dielectric for MoS2 FET. Figure 4c shows the gate leakage current (IG − VG) behavior of buried-gate and local back-gate FETs. Interestingly, the leakage current over the gate voltage shows the two-step-like behavior indicative of gate dielectric breakdown. For the local back-gate device (blue line), the level of gate leakage current is low, at around 10−11 A within a gate voltage of 15 V. Additionally, the gate leakage current increases up to 10−7 A from 15 to 20 V of gate voltage, indicating a gradual generation of soft breakdown of the Al2O3 gate dielectric due to the enhanced gate voltage [55,56,57]. Finally, the gate leakage current rapidly increases to over 10−3 A at a gate voltage of 20 V, resulting in the occurrence of hard breakdown of the Al2O3 gate dielectric. In this stage, the function of the gate dielectric cannot be further accomplished due to the formation of permanent leakage path. On the other hand, for the buried-gate device (red line), the gate voltage ranges for soft and hard breakdown voltage are drastically enhanced up to a gate voltage of 30 V. By utilizing the optimized buried-gate structure of MoS2 logic, FETs can achieve enhanced drive on-current and prolonged gate voltage stability simultaneously through uniform gate controllability.

Figure 3.

The Atomic Force Microscope (AFM) images of (a) buried-gate and (c) local back-gate. The cross-sectional scanning electron microscope (SEM) images of (b) buried-gate and (d) local back-gate.

Figure 4.

(a) Transfer characteristics (ID − VG) of MoS2-based FET (red line of buried-gate, blue line of local back-gate), the channel length of 10 μm at a drain voltage (VDS) of 1 V. (b) Output curve (ID − VD) of at gate voltage (VG) 2 to 8 V (step of 2 V) (red line of buried-gate, blue line of local back-gate). (c) Gate leakage curve (IG − VG) of MoS2 FET (red line of buried-gate, blue line of local back-gate). Statistical histograms of (d) on/off current ratio, (e) field-effect mobility, and (f) breakdown voltage for buried-gate and local back-gate.

The statistical analysis for various electrical parameters, including the on-off ratio, field-effect mobility, and breakdown voltage, is depicted in Figure 4d–f. Figure 4d,e illustrate the statistical distributions in the on/off ratio and field-effect mobility for buried-gate and local back-gate MoS2 FETs. The estimated average values of on/off ratios were found to be 1.52 × 107 (buried-gate) and 4.90 × 105 (local back-gate). The on/off ratio is derived from the comparison of the maximum on-state current with the off-state current to reflect the device’s switching capabilities and suitability for digital circuit applications [58]. Furthermore, the value of field-effect mobility can be deduced from the linear segment of the transfer curve using Equation (1), as below,

where μ is the field-effect mobility, IDS is the drain current, VBG is the gate voltage, L is the channel length of 10 μm, W is the channel width of 50 μm, and COX is the oxide capacitance per unit area between the channel and gate dielectric layer (Al2O3) [59,60]. The average mobility was calculated to be 1.08 cm2/V·s (buried-gate) and 0.166 cm2/V·s (local back-gate). The improvement in field-effect mobility for the buried-gate structure is approximately 6.5 times higher compared to the local back-gate structure. Figure 4f presents the statistical variation of breakdown voltage. The breakdown field of the gate dielectric in FETs is a critical design consideration because exceeding this breakdown field can lead to irreversible damage to the device and a breakdown in the insulating properties of the oxide layer. The breakdown voltage of the Al2O3 gate dielectric layer in FETs can depend on factors such as the oxide thickness, crystal structure, defects, and the fabrication process. Also, Al2O3 has a high breakdown electric field (5–10 MV/cm) [56,61]. The average values of the breakdown voltage were estimated to be 27.48 V (buried-gate) and 11.75 V (local back-gate), respectively. The breakdown electric field (EBR) is defined as VBR divided by Tox, where VBR is the breakdown voltage across the insulating layer and Tox is the physical thickness of the insulating layer of Al2O3 30 nm. In the breakdown electric field (EBR), the buried-gate shows a high value of 9.16 MV/cm, and the local back-gate shows a value of 3.91 MV/cm, which is about 2.3 times lower.

3.3. Integrated Logic Circuits Characteristics

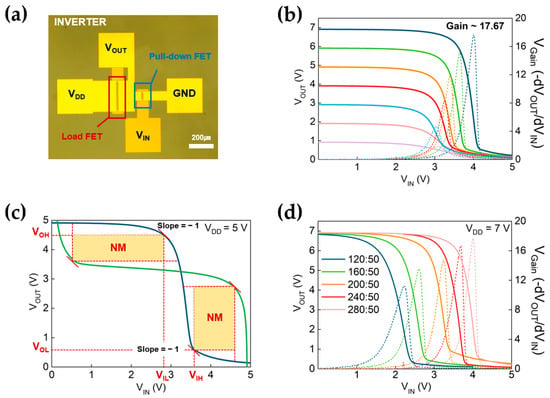

After successfully optimizing uniform and high-performance transistors based on buried-gate device configurations, the inverter logic circuit using direct-coupled FET logic was implemented. Direct-coupled FET logic excels in high-speed operation, making it ideal for microprocessors and high-frequency communication systems. It can be optimized for low power consumption, which benefits battery-operated and power-efficient devices. Direct-coupled FET logic is well suited for noisy environments and long-distance communication. The versatility of this device is enhanced by its ability to function with diverse supply voltages across various applications [31,62,63]. In this inverter configuration, the four electrode terminals are fabricated as input gate voltage (VIN), output voltage (VOUT), drain voltage (VDD), and ground (GND). Two neighboring MoS2 transistors are concretely formed as load and pull-down transistors. The load transistor acts as a variable resistance, while the pull-down transistor operates as an n-type enhancement-mode FET. The input gate electrode of the pull-down MoS2 FET was designated as the input voltage terminal, while the source electrode of the load transistor was connected to the gate electrode via a hole through the Al2O3 gate dielectric layer, thereby serving as the output terminal of the inverter circuit.

Figure 5b shows the inverter performance of the direct-coupled FET logic configuration by the Voltage-Transfer Characteristics (VTC), where VDD spans from 1 to 7 V with voltage steps of 1 V. The corresponding voltage gain of the inverter was calculated using Equation (2) as below,

where d VOUT is the corresponding change in output voltage and d VIN is the corresponding change in input voltage. This equation quantifies how the output voltage changes in response to a change in the input voltage.

Figure 5.

(a) An Optical Microscope (OM) image of the inverter based on two n-type MoS2 FETs (Load FET and Pull-down FET). (b) The Voltage Transfer Curve (VTC) of the inverter is observed with supply VDD from 1 to 7 V, resulting in the best performance of a voltage gain of 17.67. (c) Noise Margin (NM) properties of the inverter at VDD = 5 V, the curve acquired by mirroring the Voltage Transfer Curve (VTC), and the position of slope equals to −1 marked (VOH represents the minimum high-output voltage when the output level is logical “1”; VOL represents the maximum low-output voltage when the output level is logical “0”; VIL represents the maximum low-input voltage, which can be interpreted as logical “0”; VIH represents the minimum high-input voltage, which can be interpreted as logical “1”). (d) Voltage Transfer Curves (VTC) at VDD = 7 V of the inverters with different ratios of load transistor and pull-down transistor width of channel (120/50, 160/50, 200/50, 240/50, and 280/50 μm), and identical channel length of 10 μm.

The distinct signal inversions are observed with high VOUT in low VIN and vice versa. The corresponding voltage gains (Gain = −d VOUT/d VIN) are successfully acquired with various VDD. The maximum gain was recorded as around 17.67 at VDD = 7 V.

Figure 5c shows the noise margin characteristics at VDD = 5 V. In order to assess the noise margin characteristics of the inverter, we investigated both the low-input signal levels (NML) and high-input signal levels (NMH). NML and NMH were determined by extracting VOH, VOL, VIH, and VIL values at the point where the slope equals −1 on the voltage transfer curve (VTC). It can be quantified using Equation (3) as below [64,65],

At VDD = 5 V, the inverter calculated NML and NMH values as 2.24 V and 0.9 V, respectively. The characteristics of inverters made with a local back-gate are shown in Figure S9 (Supplementary Materials).

We further varied the sizes of FETs incorporated into the inverters, observing diverse voltage gains ranging from 1 V to 7 V, and confirmed the shift of the switching threshold voltage. Figure 5d shows the Voltage Transfer Characteristics (VTC) of the inverters, which were evaluated for different ratios of load transistor and pull-down transistor widths, specifically 120/50, 160/50, 200/50, 240/50, and 280/50 μm. All ratios had identical channel lengths of 10 μm. Furthermore, a substantial width ratio between the pull-down and load FETs enhances noise immunity while also shifting the switching threshold voltage to the right. This phenomenon indicates a significant impact on the inverter’s switching behavior, thus illustrating the interconnection between transistor dimensions and their effects on both voltage gain and threshold voltage [66,67].

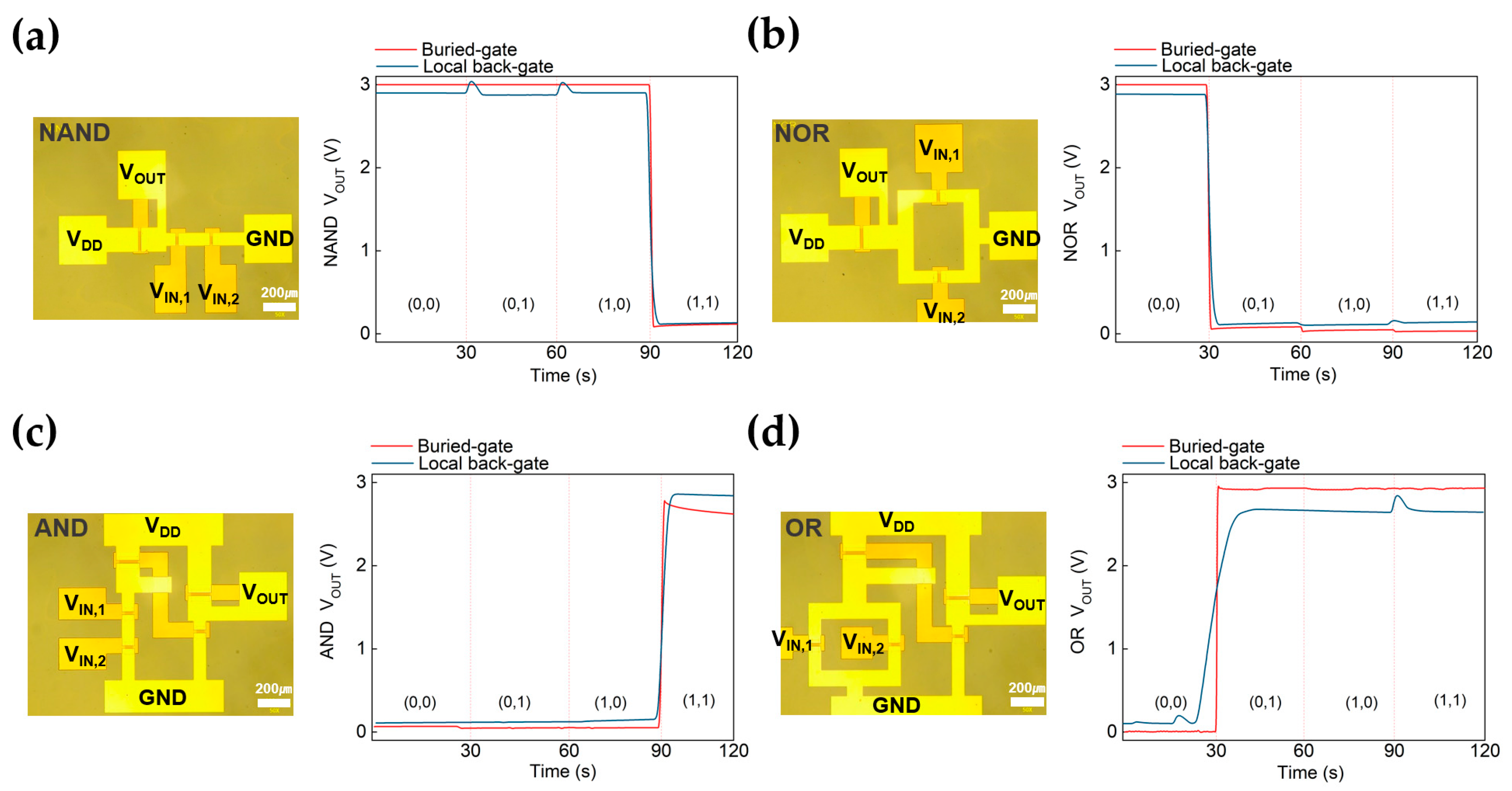

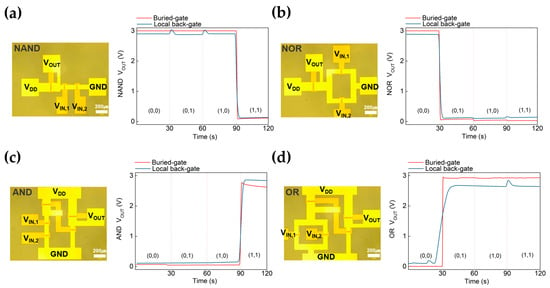

Finally, based on buried-gate FETs and inverter characteristics, we fabricated a series of complex logic devices composed of three or five MoS2-film transistors. Figure 6 shows images of logic circuits using Optical Microscope (OM), consisting of (a) NAND, (b) NOR, (c) AND, (d) OR. The images are displayed on the left, while the corresponding timing diagrams are presented on the right. The channel sizes of the load FET and pull-down FETs are L = 10 μm, WIN = 120 μm, and WOUT = 50 μm, respectively. The gate terminals of two pull-down transistors were connected to the two input terminals, with input voltages of −5 and 10 V corresponding to logical states ‘0’ and ‘1’, respectively. The timing diagrams, which illustrate the buried-gate-based logic circuits, confirm the successful implementation of Boolean expressions [68,69]. They clearly differentiate between a high-output voltage (approximately 3 V) and a low-output voltage (nearly 0 V). In contrast, logic circuits based on the local back-gate were also achieved, but their output state was approximately 2 V. This deviation from the anticipated 3 V is attributed to the negative threshold voltage (Vth) characteristic of MoS2 transistors. The negative Vth leads to an inverter output voltage below VDD at 0 V, causing a delayed dynamic switching behavior. Consequently, logic circuits based on buried-gate, when compared to local back-gate, exhibited a more relaxed and faster response speed.

Figure 6.

Optical microscope (OM) images (left) and Timing diagrams (right) of (a) NAND, (b) NOR, (c) AND, (d) OR gates with comparison between buried-gate (red line) and local back-gate (blue line) at VDD = 3 V. The four typical input states (0, 0), (0, 1), (1, 0), and (1, 1). “0” and “1” of input states represent and −5 and 10 V for input voltage in actual measurement. VOUT results of logic circuits separate the low and high binary output states.

4. Conclusions

We demonstrated the advantages of the buried-gate structure through comparative study with the local back-gate structure. The MoS2 transistors with the buried-gate structure show enhanced electrical characteristics compared with the local back-gate structure (higher on-state current and on/off ratio at 107, elevated field-effect mobility of 1.08 cm2/V·s, and improved breakdown voltage of 27.48 V). In addition, high-quality MoS2 film was synthesized using the two-step method. Inverters and logic circuits were successfully fabricated using a buried-gate structure by applying MoS2 film to a 2-inch wafer-scale. The inverter demonstrated high voltage gain and noise tolerance, while the logic circuits (NAND, NOR, AND, OR) produced the expected Boolean results. These findings underscore the potential of MoS2-based buried-gate devices in advancing logic circuits and integrated circuits.

Supplementary Materials

The following supporting information can be downloaded at: https://www.mdpi.com/article/10.3390/nano13212870/s1, Figure S1. The schematic of fabrication flow for the 2D-MoS2 inverter based on buried-gate structure. Figure S2. The image of sulfurization MoO3 deposited on 2-inch scale SiO2 (100 nm)/Si substrate using thermal Chemical Vapor Deposition (CVD). Figure S3. The image of separated MoS2 film from the SiO2 (100 nm)/Si substrate transferred on to another substrate which has been transferred to the gate dielectric layer. Figure S4. The actual Raman mapping image of a 2D-MoS2 film. The mapping divides an area of 50 × 50 μm2 sections of 36 points, each with a step size of 10 μm. Figure S5. (a,b) Atomic force microscopy (AFM) images and height profiles of the sidewalls of buried-gate and local back-gate filled with gate metal. Figure S6. The scanning electron microscope (SEM) images of tilted gate surfaces of (a) buried-gate and (b) local back-gate. The buried gate is stably embedded in the etched SiO2 layer, displaying a clean edge shape. In contrast, the local back-gate surface has a sidewall at the edge that causes the deposited metal to roll out, resulting in a rough surface. Figure S7. The image of electrical measurement of logic device using a semiconductor parameter analyzer system (Keithley-4200 SCS) at room temperature (R.T.). Figure S8. More data collected from each gate type of MoS2-FETs. Each data shows transfer curves measured from 15 FETs which are randomly located on different positions of the substrate. (a) buried-gate, (b) local back-gate. Figure S9. (a) Voltage Transfer Curve (VTC) of the local back-gate based inverter under supply VDD from 1 to 7 V. The best performance of voltage gain is 12.8 (While the buried-gate is 17.67, the local back-gate shows lower value). (b) Noise Margin (NM) properties of the local back-gate based inverter at VDD = 5 V, the curve acquired by mirroring the Voltage Transfer Curve (VTC), and the position of slope equals to −1 marked. The inverter calculated NML and NMH values of 1.56 V and 0.9 V, respectively.

Author Contributions

J.-A.L. designed and conducted the experiments. J.Y., S.H. and H.H. supported the execution of the experiments and the data analysis. J.-A.L. and J.Y. wrote the paper. J.-D.K. and S.-K.L. supported and guided the experiments and analysis of results. Y.K. conceived the project and supervised the writing of the paper. All authors have read and agreed to the published version of the manuscript.

Funding

This study was supported by the Fundamental Research Program (PNK9020) of the Korean Institute of Materials Science (KIMS) and the Energy Technology Development Program of the Korean Institute of Energy Technology Evaluation and Planning (KETEP) (Grant No. RS-2023-00301944), and Technology Innovation Program (20018106, Development of 8 in. atomic layer deposition system for 2D materials and applications as photosensors and 20022508, Development of ultrahigh temperature activator and core process technology for SiC devices) of the Ministry of Trade, Industry and Energy (MOTIE, Korea). Also, this study was supported by the National Research Council of Science and Technology (NST) grant by the Korean Government (MSIT) (No. CPS22191-100).

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Geim, A.K. Graphene: Status and prospects. Science 2009, 324, 1530–1534. [Google Scholar] [CrossRef] [PubMed]

- Schwierz, F. Graphene transistors. Nat. Nanotechnol. 2010, 5, 487–496. [Google Scholar] [CrossRef] [PubMed]

- Novoselov, K.S.; Geim, A.K.; Morozov, S.V.; Jiang, D.; Zhang, Y.; Dubonos, S.V.; Grigorieva, I.V.; Firsov, A.N. Electric field effect in atomically thin carbon films. Science 2004, 306, 666–669. [Google Scholar] [CrossRef]

- Neto, A.C.; Guinea, F.; Peres, N.M.; Novoselov, K.S.; Geim, A.K. The electronic properties of graphene. Rev. Mod. Phys. 2009, 81, 109. [Google Scholar] [CrossRef]

- Liao, L.; Lin, Y.-C.; Bao, M.; Cheng, R.; Bai, J.; Liu, Y.; Qu, Y.; Wang, K.L.; Huang, Y.; Duan, X.; et al. High-speed graphene transistors with a self-aligned nanowire gate. Nature 2010, 467, 305–308. [Google Scholar] [CrossRef]

- Wu, Y.; Lin, Y.-M.; Bol, A.A.; Jenkins, K.A.; Xia, F.; Farmer, D.B.; Zhu, Y.; Avouris, P. High-frequency, scaled graphene transistors on diamond-like carbon. Nature 2011, 472, 74–78. [Google Scholar] [CrossRef]

- Cheng, R.; Jiang, S.; Chen, Y.; Liu, Y.; Weiss, N.; Cheng, H.-C.; Wu, H.; Huang, Y.; Duan, X. Few-layer molybdenum disulfide transistors and circuits for high-speed flexible electronics. Nat. Commun. 2014, 5, 5143. [Google Scholar] [CrossRef]

- Mas-Balleste, R.; Gomez-Navarro, C.; Gomez-Herrero, J.; Zamora, F. 2D materials: To graphene and beyond. Nanoscale 2011, 3, 20–30. [Google Scholar] [CrossRef]

- Butler, S.Z.; Hollen, S.M.; Cao, L.; Cui, Y.; Gupta, J.A.; Gutiérrez, H.R.; Heinz, T.F.; Hong, S.S.; Huang, J.; Ismach, A.F.; et al. Progress, challenges, and opportunities in two-dimensional materials beyond graphene. ACS Nano 2013, 7, 2898–2926. [Google Scholar] [CrossRef]

- Xu, M.; Liang, T.; Shi, M.; Chen, H. Graphene-like two-dimensional materials. Chem. Rev. 2013, 113, 3766–3798. [Google Scholar] [CrossRef]

- Das, S.; Robinson, J.A.; Dubey, M.; Terrones, H.; Terrones, M. Beyond graphene: Progress in novel two-dimensional materials and van der Waals solids. Annu. Rev. Mater. Res. 2015, 45, 1–27. [Google Scholar] [CrossRef]

- Luo, Z.; Peng, B.; Zeng, J.; Yu, Z.; Zhao, Y.; Xie, J.; Lan, R.; Ma, Z.; Pan, L.; Cao, K.; et al. Sub-thermionic, ultra-high-gain organic transistors and circuits. Nat. Commun. 2021, 12, 1928. [Google Scholar] [CrossRef] [PubMed]

- Borchert, J.W.; Zschieschang, U.; Letzkus, F.; Giorgio, M.; Weitz, R.T.; Caironi, M.; Burghartz, J.N.; Ludwigs, S.; Klauk, H. Flexible low-voltage high-frequency organic thin-film transistors. Sci. Adv. 2020, 6, eaaz5156. [Google Scholar] [CrossRef] [PubMed]

- Zeng, J.; He, D.; Qiao, J.; Li, Y.; Sun, L.; Li, W.; Xie, J.; Gao, S.; Pan, L.; Wan, P.; et al. Ultralow contact resistance in organic transistors via orbital hybridization. Nat. Commun. 2021, 14, 324. [Google Scholar] [CrossRef]

- Chhowalla, M.; Shin, H.S.; Eda, G.; Li, L.-J.; Loh, K.P.; Zhang, H. The chemistry of two-dimensional layered transition metal dichalcogenide nanosheets. Nat. Chem. 2013, 5, 263–275. [Google Scholar] [CrossRef]

- Kang, K.; Xie, S.; Huang, L.; Han, Y.; Huang, P.Y.; Mak, K.F.; Kim, C.-J.; Muller, D.; Park, J. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 2015, 520, 656–660. [Google Scholar] [CrossRef]

- Duan, X.; Wang, C.; Pan, A.; Yu, R.; Duan, X. Two-dimensional transition metal dichalcogenides as atomically thin semiconductors: Opportunities and challenges. Chem. Soc. Rev. 2015, 44, 8859–8876. [Google Scholar] [CrossRef] [PubMed]

- Schmidt, H.; Giustiniano, F.; Eda, G. Electronic transport properties of transition metal dichalcogenide field-effect devices: Surface and interface effects. Chem. Soc. Rev. 2015, 44, 7715–7736. [Google Scholar] [CrossRef]

- Wang, Q.H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J.N.; Strano, M.S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 2012, 7, 699–712. [Google Scholar] [CrossRef]

- Huang, X.; Tan, C.; Yin, Z.; Zhang, H. 25th Anniversary article: Hybrid nanostructures based on two-dimensional nanomaterials. Adv. Mater. 2014, 26, 2185–2204. [Google Scholar] [CrossRef]

- Tong, L.; Wan, J.; Xiao, K.; Liu, J.; Ma, J.; Guo, X.; Zhou, L.; Chen, X.; Xia, Y.; Dai, S. Heterogeneous complementary field-effect transistors based on silicon and molybdenum disulfide. Nat. Electron. 2023, 6, 37–44. [Google Scholar] [CrossRef]

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 2011, 6, 147–150. [Google Scholar] [CrossRef] [PubMed]

- Jariwala, D.; Sangwan, V.K.; Lauhon, L.J.; Marks, T.J.; Hersam, M.C. Emerging device applications for semiconducting two-dimensional transition metal dichalcogenides. ACS Nano 2014, 8, 1102–1120. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Kumar, A.; Durante, O.; Sessa, A.; Faella, E.; Viscardi, L.; Intonti, K.; Giubileo, F.; Martucciello, N.; Romano, P.; et al. Temperature-dependent photoconductivity in two-dimensional MoS2 transistors. Mater. Today Nano 2023, 24, 100382. [Google Scholar] [CrossRef]

- Kumar, A.; Faella, E.; Durante, O.; Giubileo, F.; Pelella, A.; Viscardi, L.; Intonti, K.; Sleziona, S.; Schleberger, M.; Di Bartolomeo, A.; et al. Optoelectronic memory in 2D MoS2 field effect transistor. J. Phys. Chem. Solids 2023, 179, 111406. [Google Scholar] [CrossRef]

- Ni, P.; Dieng, M.; Vanel, J.-C.; Florea, I.; Bouanis, F.Z.; Yassar, A. Liquid Shear Exfoliation of MoS2: Preparation, Characterization, and NO2-Sensing Properties. Nanomaterials 2023, 13, 2502. [Google Scholar] [CrossRef]

- Li, N.; Wang, Q.; Shen, C.; Wei, Z.; Yu, H.; Zhao, J.; Lu, X.; Wang, G.; He, C.; Xie, L.; et al. Large-scale flexible and transparent electronics based on monolayer molybdenum disulfide field-effect transistors. Nat. Electron. 2020, 3, 711–717. [Google Scholar] [CrossRef]

- Liao, F.; Deng, J.; Chen, X.; Wang, Y.; Zhang, X.; Liu, J.; Zhu, H.; Chen, L.; Sun, Q.; Hu, W.; et al. A Dual-Gate MoS2 Photodetector Based on Interface Coupling Effect. Small 2020, 16, 1904369. [Google Scholar] [CrossRef]

- Lin, Z.; Liu, Y.; Halim, U.; Ding, M.; Liu, Y.; Wang, Y.; Jia, C.; Chen, P.; Duan, X.; Wang, C.; et al. Solution-processable 2D semiconductors for high-performance large-area electronics. Nature 2018, 562, 254–258. [Google Scholar] [CrossRef]

- Liu, W.; Sarkar, D.; Kang, J.; Cao, W.; Banerjee, K. Impact of contact on the operation and performance of back-gated monolayer MoS2 field-effect-transistors. Acs Nano 2015, 9, 7904–7912. [Google Scholar] [CrossRef]

- Wang, H.; Yu, L.; Lee, Y.-H.; Shi, Y.; Hsu, A.; Chin, M.L.; Li, L.-J.; Dubey, M.; Kong, J.; Palacios, T.; et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 2012, 12, 4674–4680. [Google Scholar] [CrossRef] [PubMed]

- Das, S.; Chen, H.-Y.; Penumatcha, A.V.; Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 2013, 13, 100–105. [Google Scholar] [CrossRef] [PubMed]

- Hoang, A.T.; Hu, L.; Kim, B.J.; Van, T.T.N.; Park, K.D.; Jeong, Y.; Lee, K.; Ji, S.; Hong, J.; Katiyar, A.K.; et al. Low-temperature growth of MoS2 on polymer and thin glass substrates for flexible electronics. Nat. Nanotechnol. 2023, in press. [CrossRef]

- Liu, Y.; Duan, X.; Shin, H.-J.; Park, S.; Huang, Y.; Duan, X. Promises and prospects of two-dimensional transistors. Nature 2021, 591, 43–53. [Google Scholar] [CrossRef] [PubMed]

- Lemme, M.C.; Daus, A. Low-temperature MoS2 growth on CMOS wafers. Nat. Nanotechnol. 2023, 18, 446–447. [Google Scholar] [CrossRef] [PubMed]

- Xia, Y.; Chen, X.; Wei, J.; Wang, S.; Chen, S.; Wu, S.; Ji, M.; Sun, Z.; Xu, Z.; Bao, W.; et al. 12-inch growth of uniform MoS2 monolayer for integrated circuit manufacture. Nat. Mater. 2023, in press. [CrossRef]

- Liu, M.; Niu, J.; Yang, G.; Chen, K.; Lu, W.; Liao, F.; Lu, C.; Lu, N.; Li, L. Large-Scale Ultrathin Channel Nanosheet-Stacked CFET Based on CVD 1L MoS2/WSe2. Adv. Electron. Mater. 2023, 9, 2200722. [Google Scholar] [CrossRef]

- Sebastian, A.; Pendurthi, R.; Choudhury, T.H.; Redwing, J.M.; Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 2021, 12, 693. [Google Scholar] [CrossRef]

- Lee, S.K.; Kim, Y.J.; Heo, S.; Park, W.; Yoo, T.J.; Cho, C.; Hwang, H.J.; Lee, B.H. Advantages of a buried-gate structure for graphene field-effect transistor. Semicond. Sci. Technol. 2019, 34, 055010. [Google Scholar] [CrossRef]

- Müller, M.; Salazar, R.; Fathipour, S.; Xu, H.; Kallis, K.; Künzelmann, U.; Seabaugh, A.; Appenzeller, J.; Knoch, J. Gate-controlled WSe 2 transistors using a buried triple-gate structure. Nanoscale Res. Lett. 2016, 11, 1–6. [Google Scholar] [CrossRef]

- Chang, K.E.; Yoo, T.J.; Kim, C.; Kim, Y.J.; Lee, S.K.; Kim, S.Y.; Heo, S.; Kwon, M.G.; Lee, B.H. Gate-Controlled graphene–silicon Schottky junction photodetector. Small 2018, 14, 1801182. [Google Scholar] [CrossRef]

- Lee, S.; Lee, S.K.; Kang, C.G.; Cho, C.; Lee, Y.G.; Jung, U.; Lee, B.H. Graphene transfer in vacuum yielding a high quality graphene. Carbon 2015, 93, 286–294. [Google Scholar] [CrossRef]

- Romanov, R.; Kozodaev, M.; Myakota, D.; Chernikova, A.; Novikov, S.; Volkov, V.; Slavich, A.; Zarubin, S.; Chizhov, P.S.; Khakimov, R.; et al. Synthesis of large area two-dimensional MoS2 films by sulfurization of atomic layer deposited MoO3 thin film for nanoelectronic applications. ACS Appl. Nano Mater. 2019, 2, 7521–7531. [Google Scholar] [CrossRef]

- Glavin, N.R.; Rao, R.; Varshney, V.; Bianco, E.; Apte, A.; Roy, A.; Ringe, E.; Ajayan, P.M. Emerging applications of elemental 2D materials. Adv. Mater. 2020, 32, 1904302. [Google Scholar] [CrossRef] [PubMed]

- Paillet, M.; Parret, R.; Sauvajol, J.L.; Colomban, P. Graphene and related 2D materials: An overview of the Raman studies. J. Raman Spectrosc. 2018, 49, 8–12. [Google Scholar] [CrossRef]

- Cong, X.; Liu, X.-L.; Lin, M.-L.; Tan, P.-H. Application of Raman spectroscopy to probe fundamental properties of two-dimensional materials. Npj 2D Mater. Appl. 2020, 4, 13. [Google Scholar] [CrossRef]

- Li, H.; Zhang, Q.; Yap, C.C.R.; Tay, B.K.; Edwin, T.H.T.; Olivier, A.; Baillargeat, D. From bulk to monolayer MoS2: Evolution of Raman scattering. Adv. Funct. Mater. 2012, 22, 1385–1390. [Google Scholar] [CrossRef]

- Shen, Y.C.; Wu, Y.T.; Lee, L.; Chen, J.H.; Wani, S.S.; Yang, T.Y.; Luo, C.W.; Siao, M.D.; Yu, Y.J.; Chiu, P.W.; et al. Rational design on wrinkle-less transfer of transition metal dichalcogenide monolayer by adjustable wettability-assisted transfer method. Adv. Funct. Mater. 2021, 31, 2104978. [Google Scholar] [CrossRef]

- Kondekar, N.P.; Boebinger, M.G.; Woods, E.V.; McDowell, M.T. In situ XPS investigation of transformations at crystallographically oriented MoS2 interfaces. ACS Appl. Mater. Interfaces 2017, 9, 32394–32404. [Google Scholar] [CrossRef]

- Hwang, S.; Hwang, Y.; Park, B.; Lee, J.A.; Choi, D.-H.; Kim, A.R.; Lee, S.-K.; Kwon, J.-D.; Kwon, S.-H.; Kim, Y.; et al. A facile approach towards Wrinkle-Free transfer of 2D-MoS2 films via hydrophilic Si3N4 substrate. Appl. Surf. Sci. 2022, 604, 154523. [Google Scholar] [CrossRef]

- Kim, Y.; Kim, A.R.; Zhao, G.; Choi, S.Y.; Kang, S.C.; Lim, S.K.; Lee, K.E.; Park, J.; Lee, B.H.; Hahm, M.G.; et al. Wafer-scale integration of highly uniform and scalable MoS2 transistors. ACS Appl. Mater. Interfaces 2017, 9, 37146–37153. [Google Scholar] [CrossRef] [PubMed]

- Lee, C.; Yan, H.; Brus, L.E.; Heinz, T.F.; Hone, J.; Ryu, S. Anomalous lattice vibrations of single-and few-layer MoS2. ACS Nano 2010, 4, 2695–2700. [Google Scholar] [CrossRef] [PubMed]

- Poon, C.Y.; Bhushan, B. Comparison of surface roughness measurements by stylus profiler, AFM and non-contact optical profiler. Wear 1995, 190, 76–88. [Google Scholar] [CrossRef]

- Lee, Y.H.; Zhang, X.Q.; Zhang, W.; Chang, M.T.; Lin, C.T.; Chang, K.D.; Yu, Y.C.; Wang, J.T.W.; Chang, C.S.; Li, L.J.; et al. Synthesis of large-area MoS2 atomic layers with chemical vapor deposition. Adv. Mater. 2012, 24, 2320–2325. [Google Scholar] [CrossRef]

- Bartzsch, H.; Glöß, D.; Böcher, B.; Frach, P.; Goedicke, K. Properties of SiO2 and Al2O3 films for electrical insulation applications deposited by reactive pulse magnetron sputtering. Surf. Coat. Technol. 2003, 174, 774–778. [Google Scholar] [CrossRef]

- Lin, H.; Ye, P.; Wilk, G. Leakage current and breakdown electric-field studies on ultrathin atomic-layer-deposited Al2O3 on GaAs. Appl. Phys. Lett. 2005, 87, 182904. [Google Scholar] [CrossRef]

- Hodgson, E. Radiation enhanced electrical breakdown in Al2O3: Field effect. Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. At. 1992, 65, 298–300. [Google Scholar] [CrossRef]

- Zhang, H.; Guo, X.; Niu, W.; Xu, H.; Wu, Q.; Liao, F.; Chen, J.; Tang, H.; Liu, H.; Xu, Z.; et al. Multilayer Si shadow mask processing of wafer-scale MoS2 devices. 2D Mater. 2020, 7, 025019. [Google Scholar] [CrossRef]

- Xu, H.; Zhang, H.; Guo, Z.; Shan, Y.; Wu, S.; Wang, J.; Hu, W.; Liu, H.; Sun, Z.; Luo, C.; et al. High-performance wafer-scale MoS2 transistors toward practical application. Small 2018, 14, 1803465. [Google Scholar] [CrossRef]

- Zhang, S.; Xu, H.; Liao, F.; Sun, Y.; Ba, K.; Sun, Z.; Qiu, Z.-J.; Xu, Z.; Zhu, H.; Chen, L.; et al. Wafer-scale transferred multilayer MoS2 for high performance field effect transistors. Nanotechnology 2019, 30, 174002. [Google Scholar] [CrossRef]

- Frank, M.M.; Wilk, G.D.; Starodub, D.; Gustafsson, T.; Garfunkel, E.; Chabal, Y.J.; Grazul, J.; Muller, D.A. HfO2 and Al2O3 gate dielectrics on GaAs grown by atomic layer deposition. Appl. Phys. Lett. 2005, 86, 152904. [Google Scholar] [CrossRef]

- Tsai, J.-H.; Huang, C.-H.; Ou-Yang, J.-J.; Chao, Y.-T.; Jhou, J.-C.; Wu, Y.-R. Performance and direct-coupled FET logic applications of InAlAs/InGaAs co-integrated field-effect transistors by 2-D simulation. Thin Solid Film. 2013, 547, 267–271. [Google Scholar] [CrossRef]

- Zhang, H.; Wang, H. Two-Dimensional Materials for Electronic Applications. In Advanced Nanoelectronics: Post-Silicon Materials and Devices; John Wiley & Sons: Hoboken, NJ, USA, 2018; pp. 55–90. [Google Scholar]

- Ma, J.; Chen, X.; Wang, X.; Bian, J.; Tong, L.; Chen, H.; Guo, X.; Xia, Y.; Zhang, X.; Xu, Z.; et al. Engineering top gate stack for wafer-scale integrated circuit fabrication based on two-dimensional semiconductors. ACS Appl. Mater. Interfaces 2022, 14, 11610–11618. [Google Scholar] [CrossRef] [PubMed]

- Wang, X.; Chen, X.; Ma, J.; Gou, S.; Guo, X.; Tong, L.; Zhu, J.; Xia, Y.; Wang, D.; Sheng, C.; et al. Pass-Transistor Logic Circuits Based on Wafer-Scale 2D Semiconductors. Adv. Mater. 2022, 34, 2202472. [Google Scholar] [CrossRef]

- Yu, L.; El-Damak, D.; Radhakrishna, U.; Ling, X.; Zubair, A.; Lin, Y.; Zhang, Y.; Chuang, M.-H.; Lee, Y.-H.; Antoniadis, D.; et al. Design, modeling, and fabrication of chemical vapor deposition grown MoS2 circuits with E-mode FETs for large-area electronics. Nano Lett. 2016, 16, 6349–6356. [Google Scholar] [CrossRef]

- Liao, F.; Guo, Z.; Wang, Y.; Xie, Y.; Zhang, S.; Sheng, Y.; Tang, H.; Xu, Z.; Riaud, A.; Zhou, P.; et al. High-performance logic and memory devices based on a dual-gated MoS2 architecture. ACS Appl. Electron. Mater. 2019, 2, 111–119. [Google Scholar] [CrossRef]

- Liu, H.; Chen, L.; Zhu, H.; Sun, Q.-Q.; Ding, S.-J.; Zhou, P.; Zhang, D.W. Atomic layer deposited 2D MoS2 atomic crystals: From material to circuit. Nano Res. 2020, 13, 1644–1650. [Google Scholar] [CrossRef]

- Dathbun, A.; Kim, Y.; Choi, Y.; Sun, J.; Kim, S.; Kang, B.; Kang, M.S.; Hwang, D.K.; Lee, S.; Lee, C.; et al. Selectively metallized 2D materials for simple logic devices. ACS Appl. Mater. Interfaces 2019, 11, 18571–18579. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).