High-Performance Non-Volatile InGaZnO Based Flash Memory Device Embedded with a Monolayer Au Nanoparticles

Abstract

1. Introduction

2. Materials and Methods

2.1. Fabrication of the Proposed NVM Device

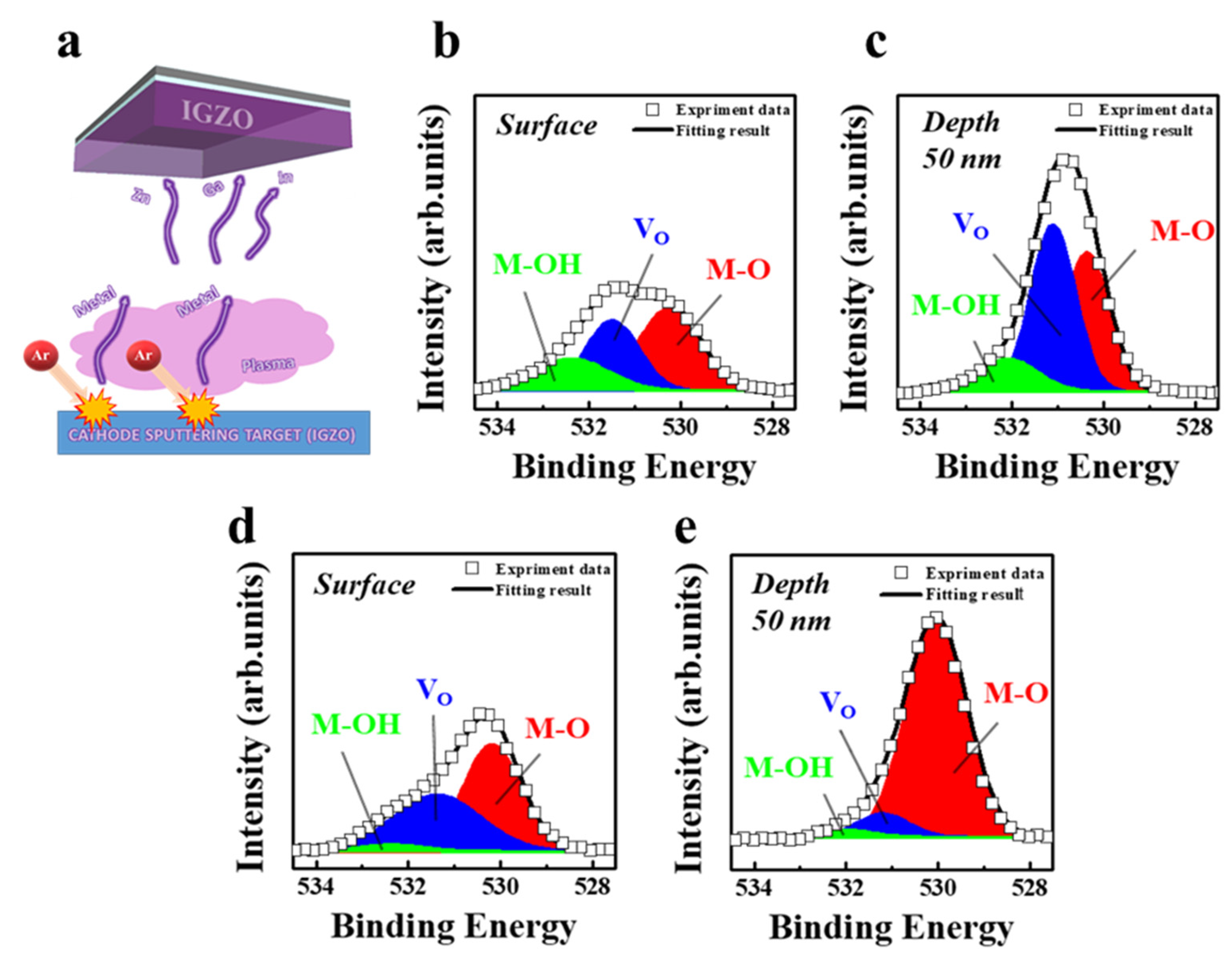

2.2. Material Characterizations

2.3. Memory Characterizations

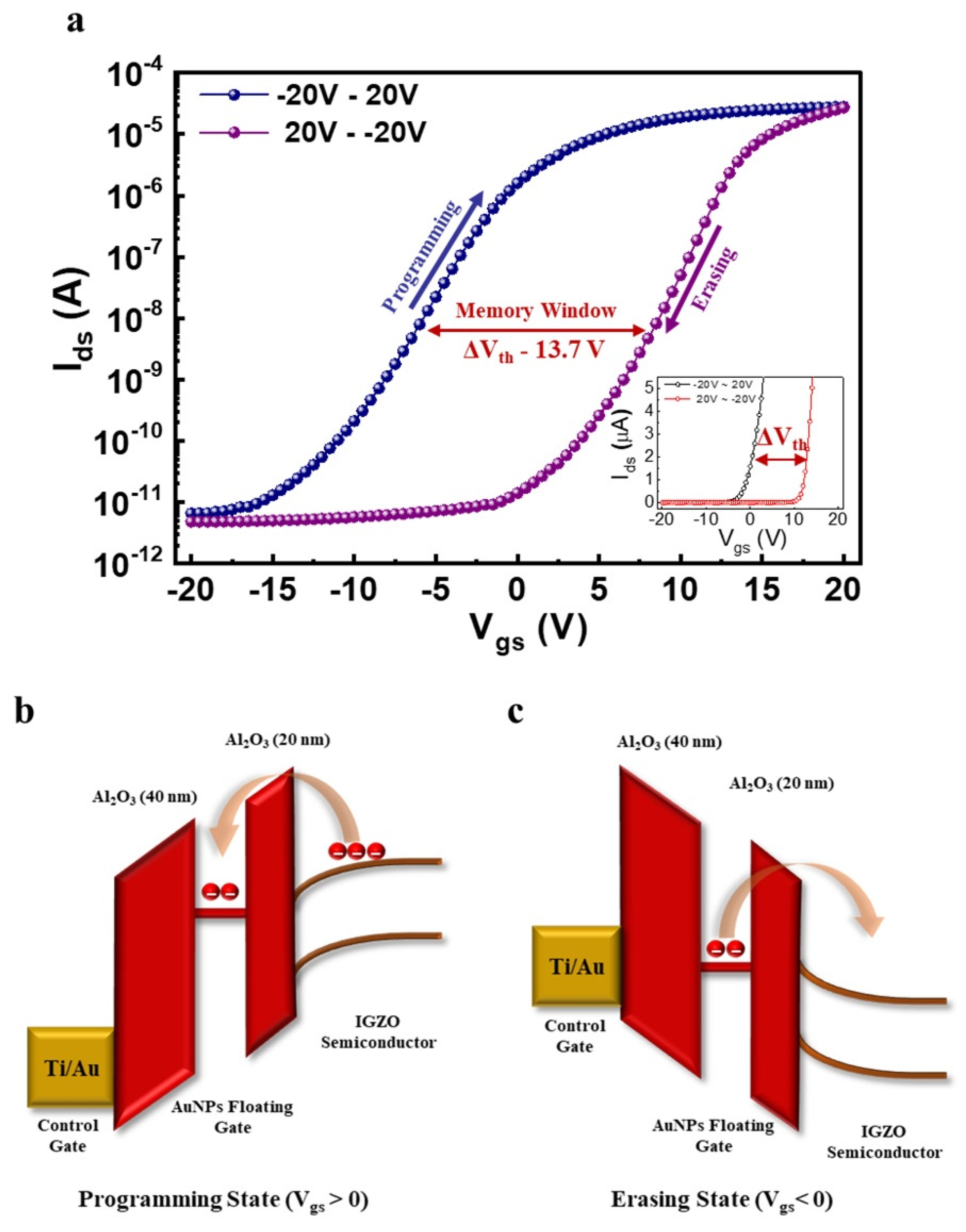

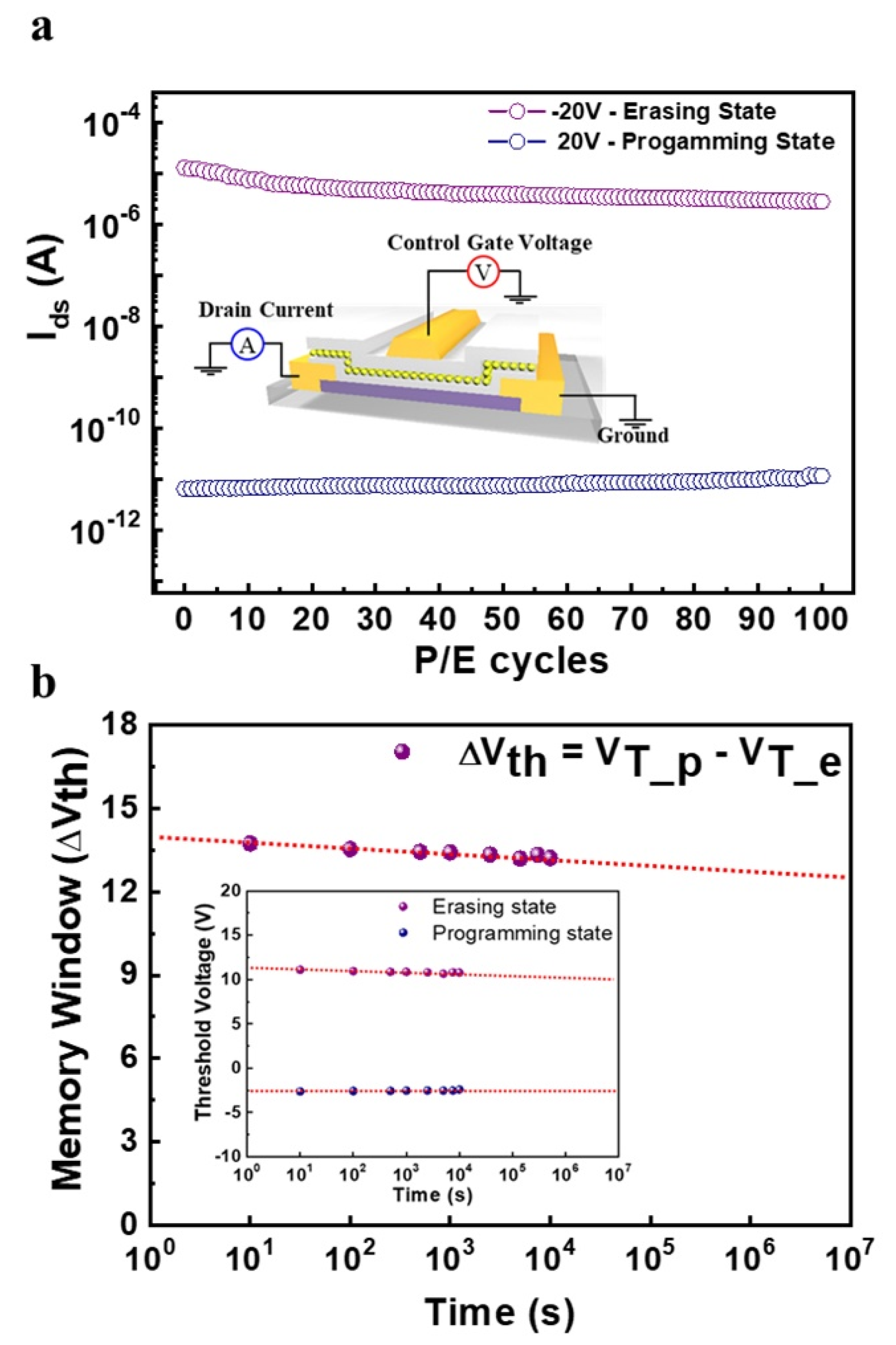

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Ni, Y.; Wang, Y.; Xu, W. Recent Process of Flexible Transistor-Structured Memory. Small 2020, 2, 1–23. [Google Scholar] [CrossRef]

- Tizno, O.; Marshall, A.R.J.; Fernández-Delgado, N.; Herrera, M.; Molina, S.I.; Hayne, M. Room-temperature Operation of Low-voltage, Non-volatile, Compound-semiconductor Memory Cells. Sci. Rep. 2019, 9, 1–8. [Google Scholar] [CrossRef]

- Rodder, M.A.; Vasishta, S.; Dodabalapur, A. Double-Gate MoS2Field-Effect Transistor with a Multilayer Graphene Floating Gate: A Versatile Device for Logic, Memory, and Synaptic Applications. ACS Appl. Mater. Interfaces 2020, 12, 33926–33933. [Google Scholar] [CrossRef]

- Wang, S.; He, C.; Tang, J.; Lu, X.; Shen, C.; Yu, H.; Du, L.; Li, J.; Yang, R.; Shi, D.; et al. New Floating Gate Memory with Excellent Retention Characteristics. Adv. Electron. Mater. 2019, 5, 1–7. [Google Scholar] [CrossRef]

- Wang, X.; Liu, C.; Chen, Y.; Wu, G.; Yan, X.; Huang, H.; Wang, P.; Tian, B.; Hong, Z.; Wang, Y.; et al. Ferroelectric FET for nonvolatile memory application with two-dimensional MoSe2 channels. 2D Mater. 2017, 4. [Google Scholar] [CrossRef]

- Liu, C.; Yan, X.; Song, X.; Ding, S.; Zhang, D.W.; Zhou, P. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nat. Nanotechnol. 2018, 13, 404–410. [Google Scholar] [CrossRef]

- Kahng, D.; Sze, S.M. A Floating Gate and Its Application to Memory Devices. Bell Syst. Tech. J. 1967, 46, 1288–1295. [Google Scholar] [CrossRef]

- Wang, J.; Zou, X.; Xiao, X.; Xu, L.; Wang, C.; Jiang, C.; Ho, J.C.; Wang, T.; Li, J.; Liao, L. Floating gate memory-based monolayer MoS2 transistor with metal nanocrystals embedded in the gate dielectrics. Small 2015, 11, 208–213. [Google Scholar] [CrossRef]

- Park, Y.S.; Lee, S.Y.; Lee, J.S. Nanofloating gate memory devices based on controlled metallic nanoparticle-embedded InGaZnO TFTs. IEEE Electron Device Lett. 2010, 31, 1134–1136. [Google Scholar] [CrossRef]

- Zhang, E.; Wang, W.; Zhang, C.; Jin, Y.; Zhu, G.; Sun, Q.; Zhang, D.W.; Zhou, P.; Xiu, F. Tunable charge-trap memory based on few-layer MoS2. ACS Nano 2015, 9, 612–619. [Google Scholar] [CrossRef] [PubMed]

- Hou, X.; Yan, X.; Liu, C.; Ding, S.; Zhang, D.W.; Zhou, P. Operation mode switchable charge-trap memory based on few-layer MoS2. Semicond. Sci. Technol. 2018, 33. [Google Scholar] [CrossRef]

- Qiu, D.; Lee, D.U.; Lee, K.S.; Pak, S.W.; Kim, E.K. Toward negligible charge loss in charge injection memories based on vertically integrated 2D heterostructures. Nano Res. 2016, 9, 2319–2326. [Google Scholar] [CrossRef]

- Chen, R.; Liu, Q.; Liu, J.; Zhao, X.; Liu, J.; He, L.; Wang, J.; Li, W.; Xiao, X.; Jiang, C. Design of high performance MoS2-based non-volatile memory via ion beam defect engineering. 2D Mater. 2019, 6. [Google Scholar] [CrossRef]

- Qian, S.B.; Zhang, W.P.; Liu, W.J.; Ding, S.J. Electrically programmable-erasable In-Ga-Zn-O thin-film transistor memory with atomic-layer-deposited Al2O3/Pt nanocrystals/Al2O3 gate stack. AIP Adv. 2015, 5. [Google Scholar] [CrossRef]

- Woo, M.H.; Jang, B.C.; Choi, J.; Shin, G.H.; Seong, H.; Im, S.G.; Choi, S.Y. Floating gate memory based on MoS2 channel and iCVD polymer tunneling dielectric. In Proceedings of the 2016 46th European Solid-State Device Research Conference (ESSDERC), Lausanne, Switzerland, 12–15 September 2016; pp. 295–298. [Google Scholar] [CrossRef]

- Suresh, A.; Novak, S.; Wellenius, P.; Misra, V.; Muth, J.F. Transparent indium gallium zinc oxide transistor based floating gate memory with platinum nanoparticles in the gate dielectric. Appl. Phys. Lett. 2009, 94. [Google Scholar] [CrossRef]

- Ahn, M.J.; Cho, W.J. Transparent multi-level-cell nonvolatile memory with dual-gate amorphous indium-gallium-zinc oxide thin-film transistors. Appl. Phys. Lett. 2016, 109. [Google Scholar] [CrossRef]

- Cui, X.M.; Chen, S.; Ding, S.J.; Sun, Q.Q.; Nyberg, T.; Zhang, S.L.; Zhang, W. Unique UV-erasable in-Ga-Zn-O TFT memory with self-assembled pt nanocrystals. IEEE Electron Device Lett. 2013, 34, 1011–1013. [Google Scholar] [CrossRef]

- Park, B.; Cho, K.; Kim, S.; Kim, S. Nano-floating gate memory based on ZnO thin-film transistors and Al nanoparticles. Solid State Sci. 2010, 12, 1966–1969. [Google Scholar] [CrossRef]

- Park, B.; Cho, K.; Kim, S.; Kim, S. Nano-floating gate memory devices composed of ZnO thin-film transistors on flexible plastics. Nanoscale Res. Lett. 2012, 7, 1–4. [Google Scholar] [CrossRef] [PubMed]

- Chang, H.C.; Liu, C.L.; Chen, W.C. Flexible nonvolatile transistor memory devices based on one-dimensional electrospun P3HT:Au hybrid nanofibers. Adv. Funct. Mater. 2013, 23, 4960–4968. [Google Scholar] [CrossRef]

- Shih, C.C.; Lee, W.Y.; Chiu, Y.C.; Hsu, H.W.; Chang, H.C.; Liu, C.L.; Chen, W.C. High Performance Transparent Transistor Memory Devices Using Nano-Floating Gate of Polymer/ZnO Nanocomposites. Sci. Rep. 2016, 6, 1–10. [Google Scholar] [CrossRef]

- Chen, C.M.; Liu, C.M.; Wei, K.H.; Jeng, U.S.; Su, C.H. Non-volatile organic field-effect transistor memory comprising sequestered metal nanoparticles in a diblock copolymer film. J. Mater. Chem. 2012, 22, 454–461. [Google Scholar] [CrossRef]

- Ren, X.; Chan, P.K.L. 23 Bits Optical Sensor Based on Nonvolatile Organic Memory Transistor. Appl. Phys. Lett. 2014, 104. [Google Scholar] [CrossRef]

- Zhu, Z.; Guo, Y.; Liu, Y. Application of organic field-effect transistors in memory. Mater. Chem. Front. 2020, 4, 2845–2862. [Google Scholar] [CrossRef]

- Van Tho, L.; Baeg, K.-J.; Noh, Y.-Y. Organic nano-floating-gate transistor memory with metal nanoparticles. Nano Converg. 2016, 3, 4210. [Google Scholar] [CrossRef]

- Spassov, D.; Paskaleva, A.; Krajewski, T.A.; Guziewicz, E.; Luka, G. Hole and electron trapping in HfO2/Al2O3 nanolaminated stacks for emerging non-volatile flash memories. Nanotechnology 2018, 29. [Google Scholar] [CrossRef] [PubMed]

- Li, J.; Zhang, H.; Ding, Y.; Li, J.; Wang, S.; Zhang, D.W.; Zhou, P. A non-volatile AND gate based on Al2O3/HfO2/Al2O3 charge-trap stack for in-situ storage applications. Sci. Bull. 2019, 64, 1518–1524. [Google Scholar] [CrossRef]

- Choi, S.; Yang, H.; Chang, M.; Baek, S.; Hwang, H.; Jeon, S.; Kim, J.; Kim, C. Memory characteristics of silicon nitride with silicon nanocrystals as a charge trapping layer of nonvolatile memory devices. Appl. Phys. Lett. 2005, 86, 1–3. [Google Scholar] [CrossRef]

- Pookpanratana, S.; Zhu, H.; Bittle, E.G.; Natoli, S.N.; Ren, T.; Richter, C.A.; Li, Q.; Hacker, C.A. Non-volatile memory devices with redox-active diruthenium molecular compound. J. Phys. Condens. Matter 2016, 28. [Google Scholar] [CrossRef] [PubMed]

- Lee, J.H.; Yew, S.C.; Cho, J.; Kim, Y.S. Effect of redox proteins on the behavior of non-volatile memory. Chem. Commun. 2012, 48, 12008–12010. [Google Scholar] [CrossRef]

- Chen, H.; Zhou, Y.; Han, S. Recent advances in metal nanoparticle-based floating gate memory. Nano Sel. 2021, 1–21. [Google Scholar] [CrossRef]

- Lee, J.S. Review paper: Nano-floating gate memory devices. Electron. Mater. Lett. 2011, 7, 175–183. [Google Scholar] [CrossRef]

- Kim, S.J.; Park, Y.S.; Lyu, S.H.; Lee, J.S. Nonvolatile nano-floating gate memory devices based on pentacene semiconductors and organic tunneling insulator layers. Appl. Phys. Lett. 2010, 96, 1–4. [Google Scholar] [CrossRef]

- Kuruoǧlu, F.; Çalişkan, M.; Serin, M.; Erol, A. Well-ordered nanoparticle arrays for floating gate memory applications. Nanotechnology 2020, 31. [Google Scholar] [CrossRef]

- Han, J.; Wang, W.; Ying, J.; Xie, W. Ambipolar organic thin-film transistor-based nano-floating-gate nonvolatile memory. Appl. Phys. Lett. 2014, 104. [Google Scholar] [CrossRef]

- Lee, J.S. Recent progress in gold nanoparticle-based non-volatile memory devices. Gold Bull. 2010, 43, 189–199. [Google Scholar] [CrossRef]

- Kang, M.; Baeg, K.J.; Khim, D.; Noh, Y.Y.; Kim, D.Y. Printed, flexible, organic nano-floating-gate memory: Effects of metal nanoparticles and blocking dielectrics on memory characteristics. Adv. Funct. Mater. 2013, 23, 3503–3512. [Google Scholar] [CrossRef]

- Koliopoulou, S.; Dimitrakis, P.; Goustouridis, D.; Normand, P.; Pearson, C.; Petty, M.C.; Radamson, H.; Tsoukalas, D. Metal nano-floating gate memory devices fabricated at low temperature. Microelectron. Eng. 2006, 83, 1563–1566. [Google Scholar] [CrossRef]

- Vanheusden, K.; Warren, W.L.; Devine, R.A.B.; Fleetwood, D.M. A non-volatile MOSFET memory device based on mobileprotons in SiO2 thin films. Journal of Non-Crystalline Solids. 1999, 254, 1–10. [Google Scholar] [CrossRef]

- Park, C.; Lee, T.; Xia, Y.; Shin, T.J.; Myoung, J.; Jeong, U. Quick, large-area assembly of a single-crystal monolayer of spherical particles by unidirectional rubbing. Adv. Mater. 2014, 26, 4633–4638. [Google Scholar] [CrossRef]

- Hossain, N.M.; Hossain, M.B.; Chowdhury, M.H. Multilayer layer graphene nanoribbon flash memory: Analysis of programming and erasing operation. In Proceedings of the 2014 27th IEEE International System-on-Chip Conference (SOCC), Las vegas, NV, USA, 2–5 September 2014; pp. 24–28. [Google Scholar] [CrossRef]

- Lenzlinger, M.; Snow, E.H. Fowler-nordheim tunneling into thermally grown SiO2. J. Appl. Phys. 1969, 40, 278–283. [Google Scholar] [CrossRef]

- Jang, J.; Park, J.C.; Kong, D.; Kim, D.M.; Lee, J.S.; Sohn, B.H.; Cho, I.H.; Kim, D.H. Endurance characteristics of amorphous-InGaZnO transparent flash memory with gold nanocrystal storage layer. IEEE Trans. Electron Devices 2011, 58, 3940–3947. [Google Scholar] [CrossRef]

- Koo, J.; Yang, J.; Cho, B.; Jo, H.; Lee, K.H.; Kang, M.S. Nonvolatile Electric Double-Layer Transistor Memory Devices Embedded with Au Nanoparticles. ACS Appl. Mater. Interfaces 2018, 10, 9563–9570. [Google Scholar] [CrossRef] [PubMed]

| Gate Stacks | Channel Deposition Method | Memory Window (ΔVth) | Voltage Range | Reference |

|---|---|---|---|---|

| Al2O3/Au-NPs/Al2O3/IGZO | RF Sputtering | ~13.7 | −20 V–20 V | This work |

| Al2O3/Pt-NCs/Al2O3/IGZO | Magnetron Sputtering | ~4.04 | −10 V–10 V | [18] |

| SiO2/Au-NCs/SiO2/IGZO | RF Magnetron Sputtering | ~4.7 | −15 V–15 V | [44] |

| Ion-gel/AuNPs/IGZO | Sol-gel Process | ~0.88 | −9 V–9 V | [45] |

| SiO2/AuNPs/PE/HfO2/IGZO | RF Magnetron Sputtering | ~15 | −50 V–50 V | [9] |

| Al2O3/HfO2/Al2O3/IGZO | RF Sputtering | ~11 | −10 V–30 V | [17] |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Naqi, M.; Kwon, N.; Jung, S.H.; Pujar, P.; Cho, H.W.; Cho, Y.I.; Cho, H.K.; Lim, B.; Kim, S. High-Performance Non-Volatile InGaZnO Based Flash Memory Device Embedded with a Monolayer Au Nanoparticles. Nanomaterials 2021, 11, 1101. https://doi.org/10.3390/nano11051101

Naqi M, Kwon N, Jung SH, Pujar P, Cho HW, Cho YI, Cho HK, Lim B, Kim S. High-Performance Non-Volatile InGaZnO Based Flash Memory Device Embedded with a Monolayer Au Nanoparticles. Nanomaterials. 2021; 11(5):1101. https://doi.org/10.3390/nano11051101

Chicago/Turabian StyleNaqi, Muhammad, Nayoung Kwon, Sung Hyeon Jung, Pavan Pujar, Hae Won Cho, Yong In Cho, Hyung Koun Cho, Byungkwon Lim, and Sunkook Kim. 2021. "High-Performance Non-Volatile InGaZnO Based Flash Memory Device Embedded with a Monolayer Au Nanoparticles" Nanomaterials 11, no. 5: 1101. https://doi.org/10.3390/nano11051101

APA StyleNaqi, M., Kwon, N., Jung, S. H., Pujar, P., Cho, H. W., Cho, Y. I., Cho, H. K., Lim, B., & Kim, S. (2021). High-Performance Non-Volatile InGaZnO Based Flash Memory Device Embedded with a Monolayer Au Nanoparticles. Nanomaterials, 11(5), 1101. https://doi.org/10.3390/nano11051101