Field Programmable Gate Array Applications—A Scientometric Review

Abstract

1. Introduction

2. Materials and Methods

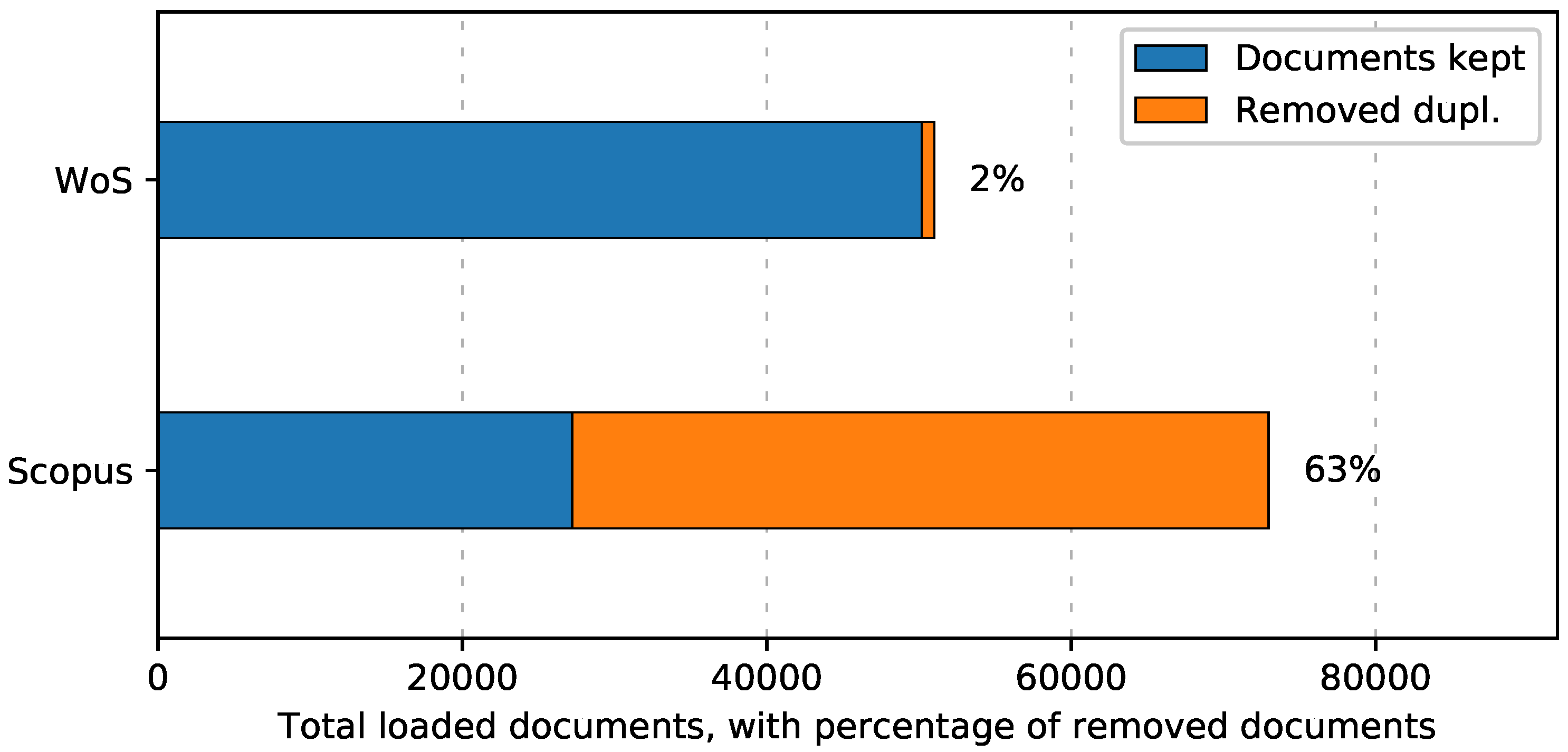

2.1. Dataset Collection

2.2. Review Methodology

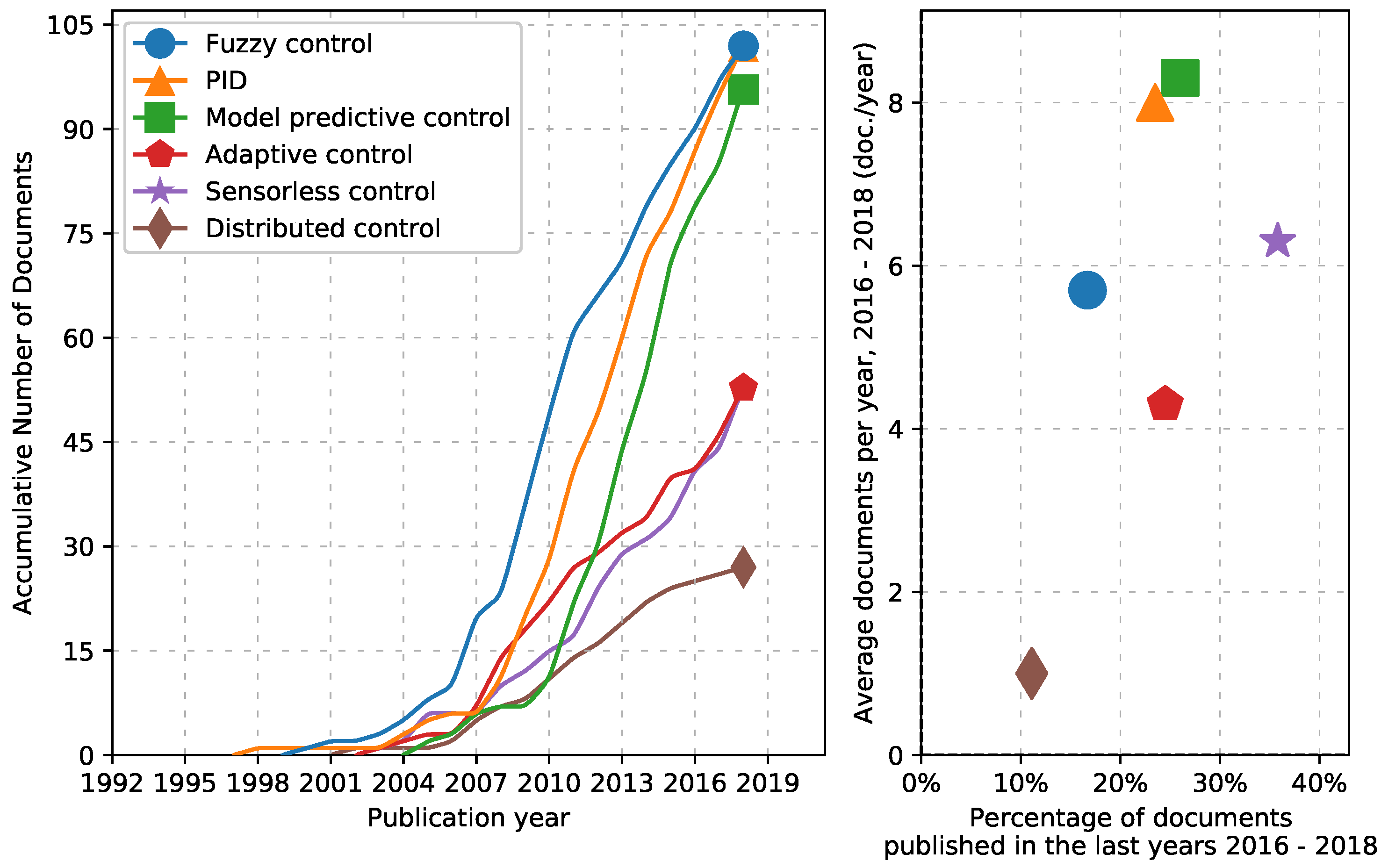

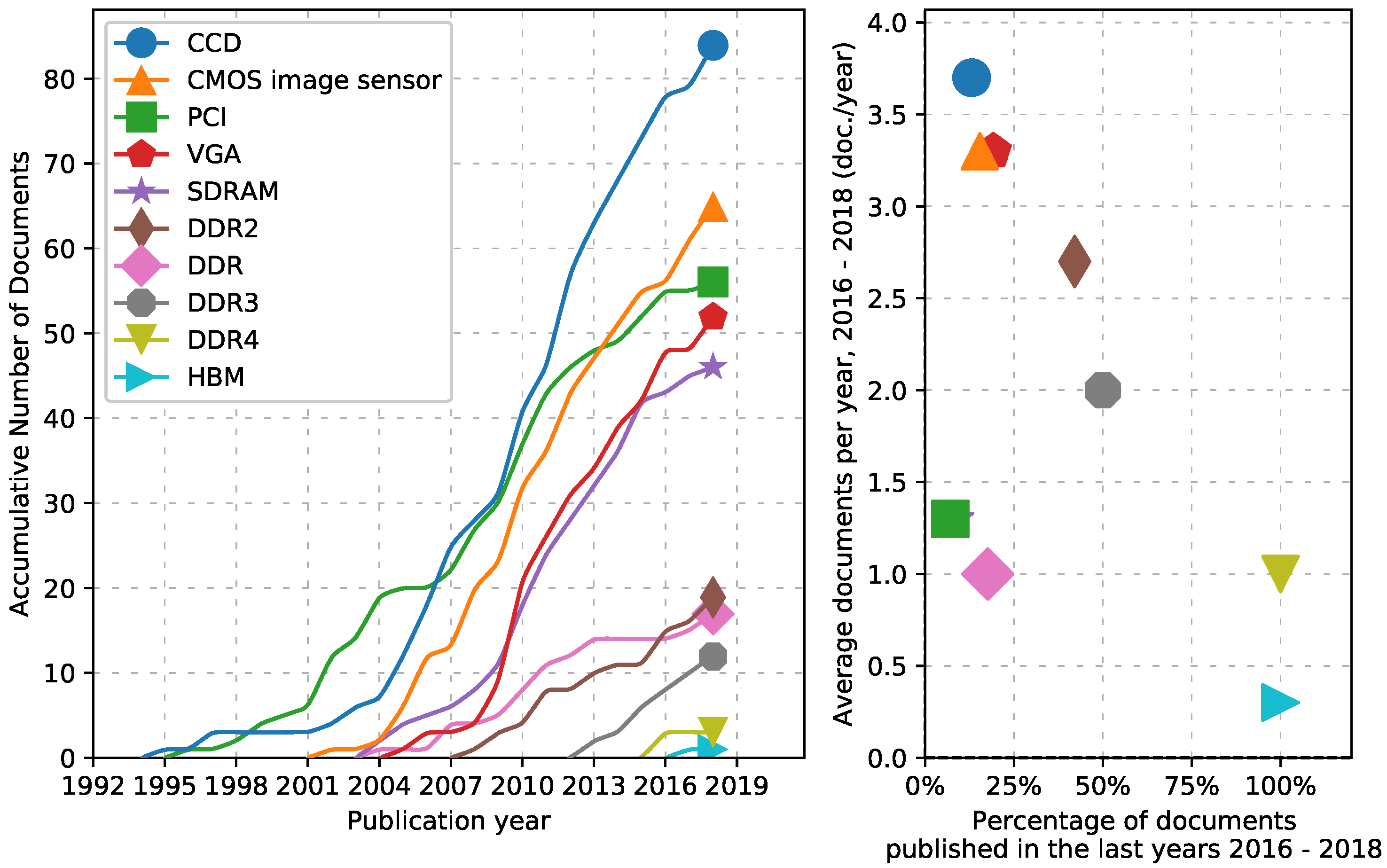

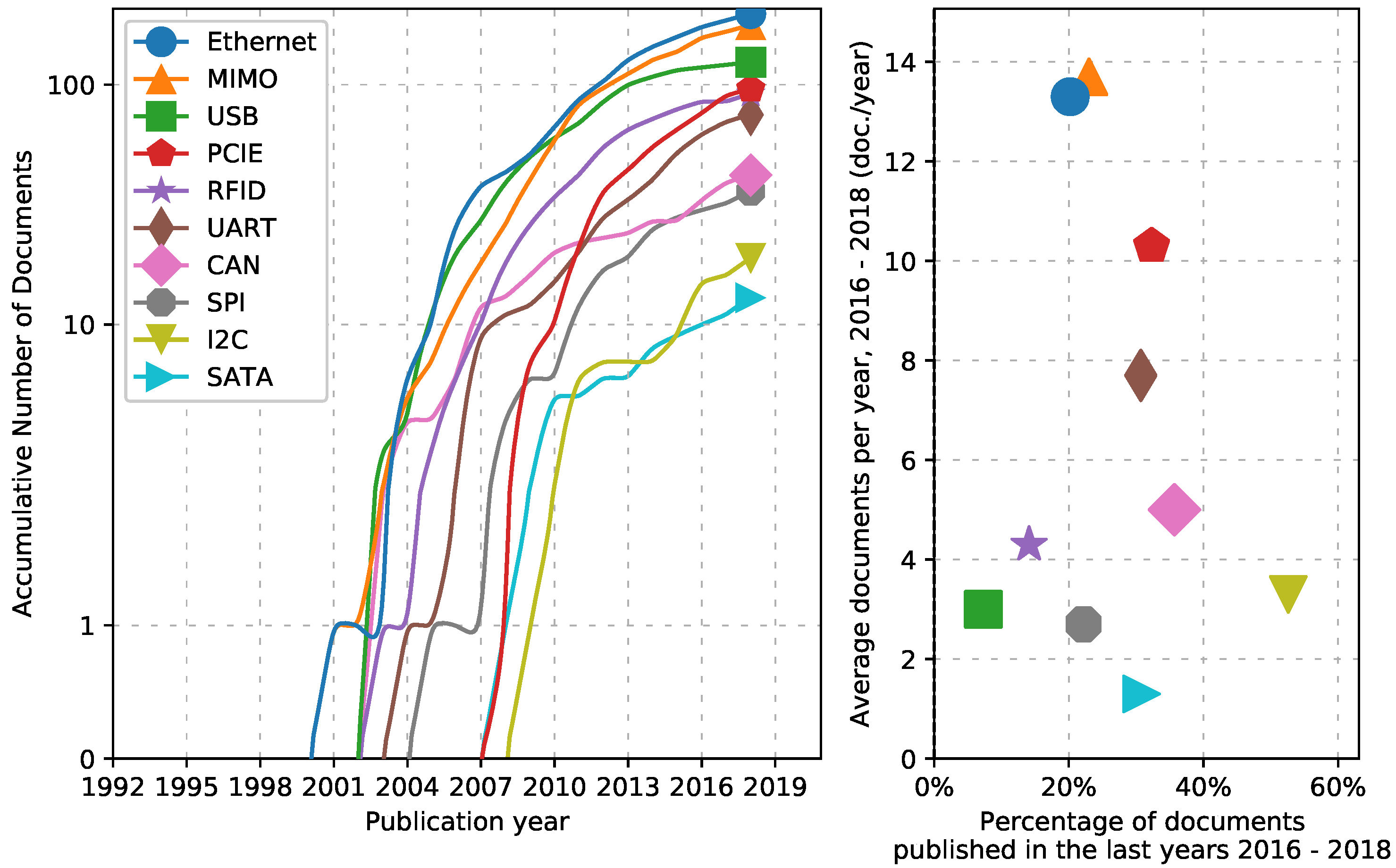

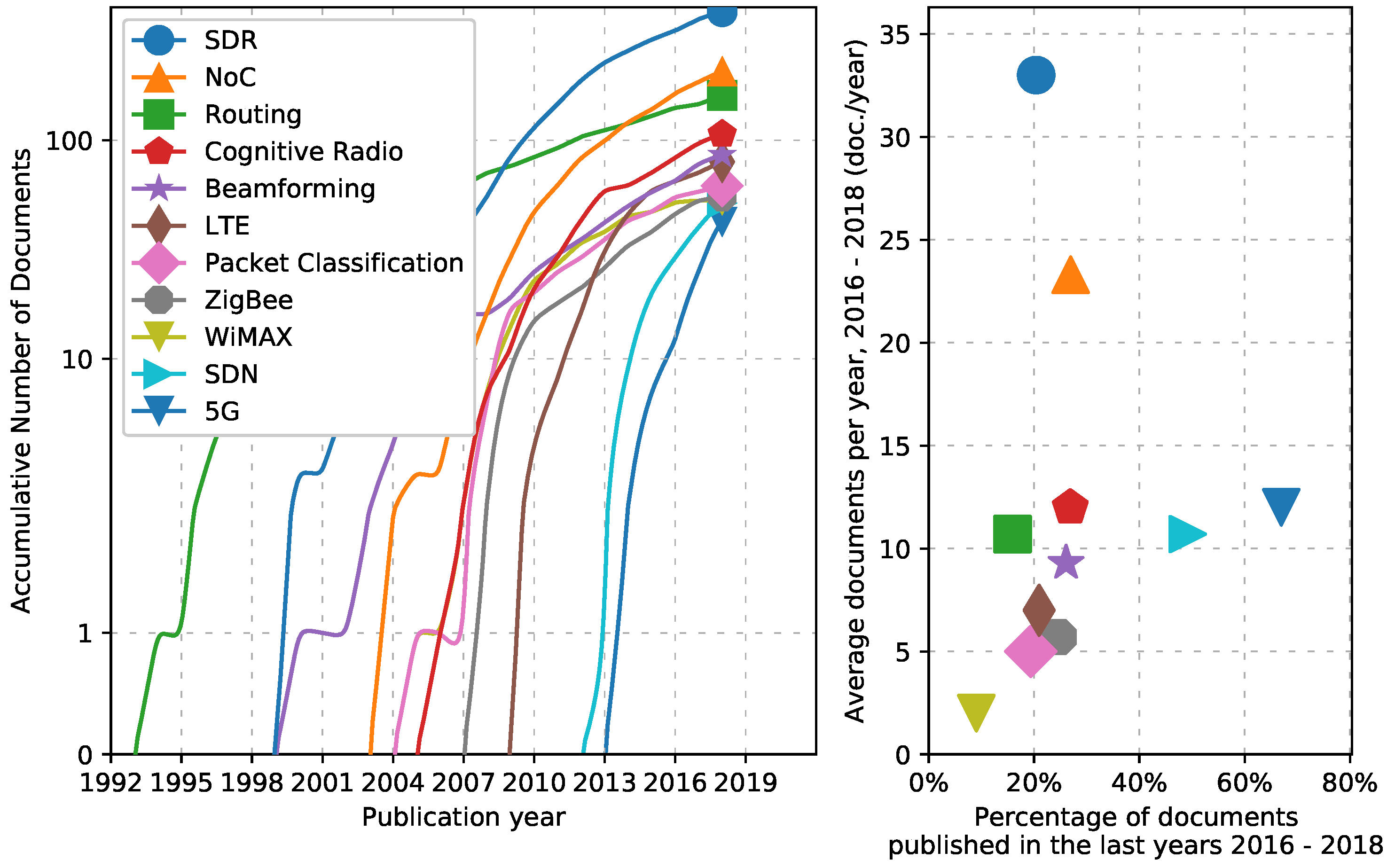

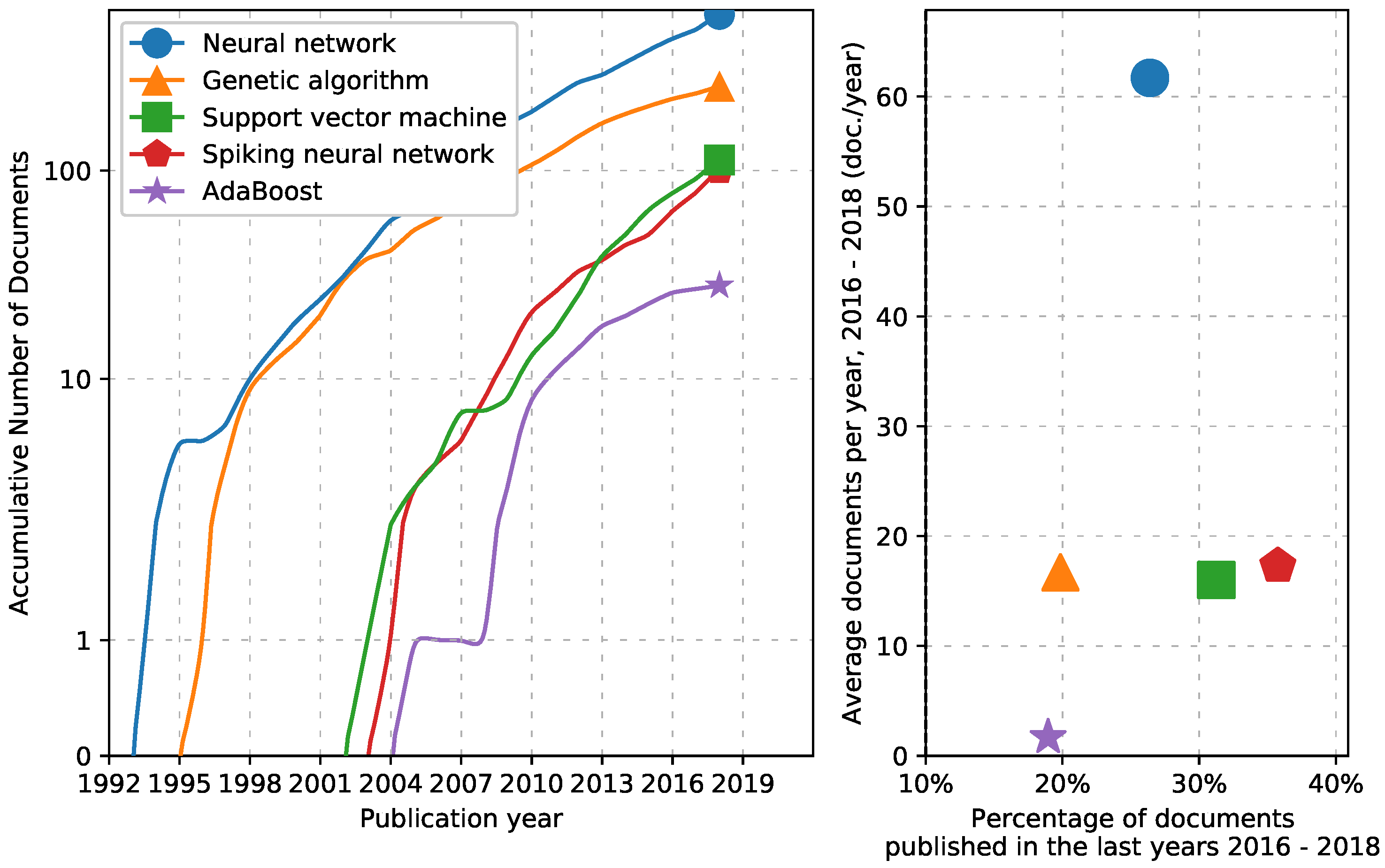

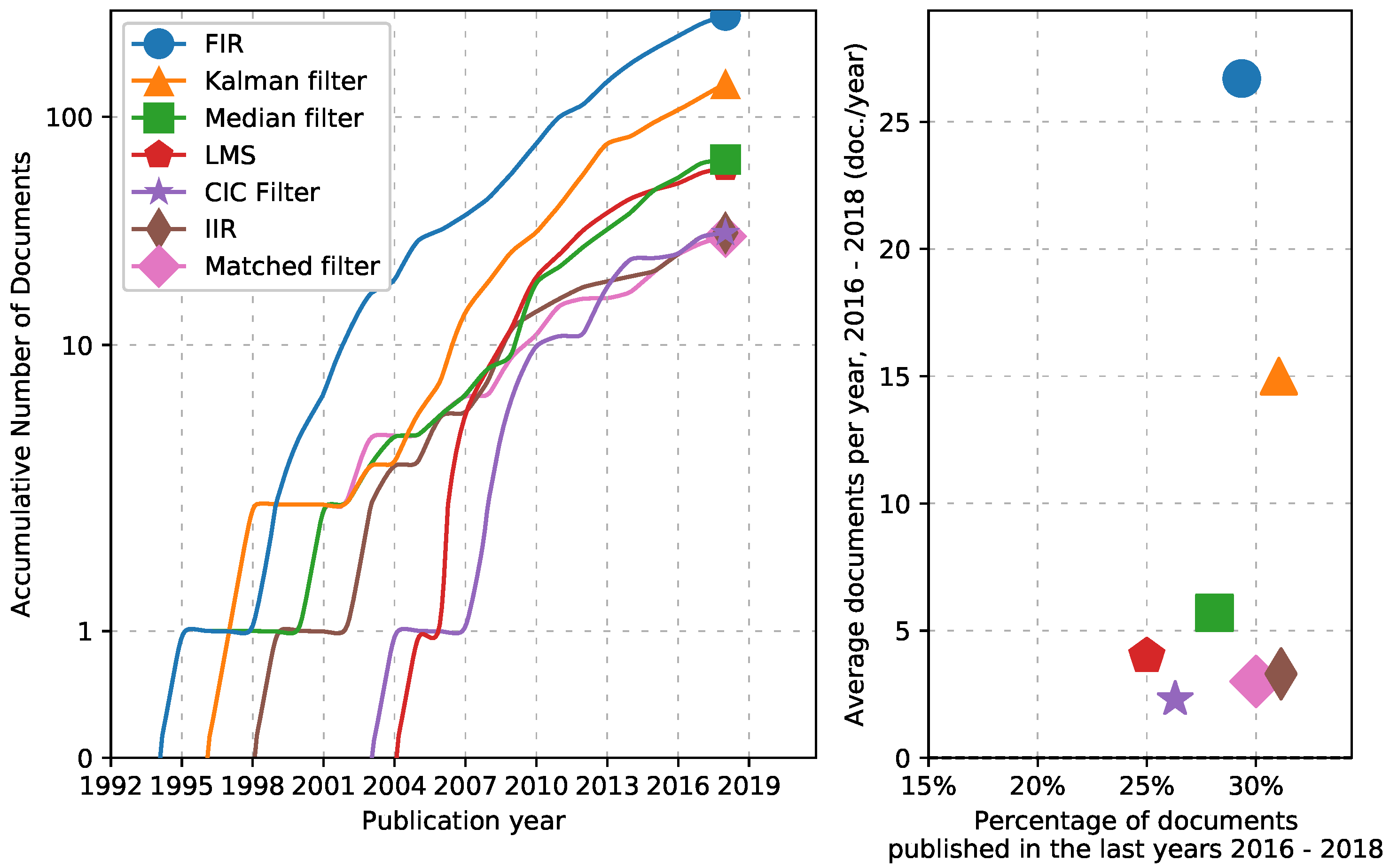

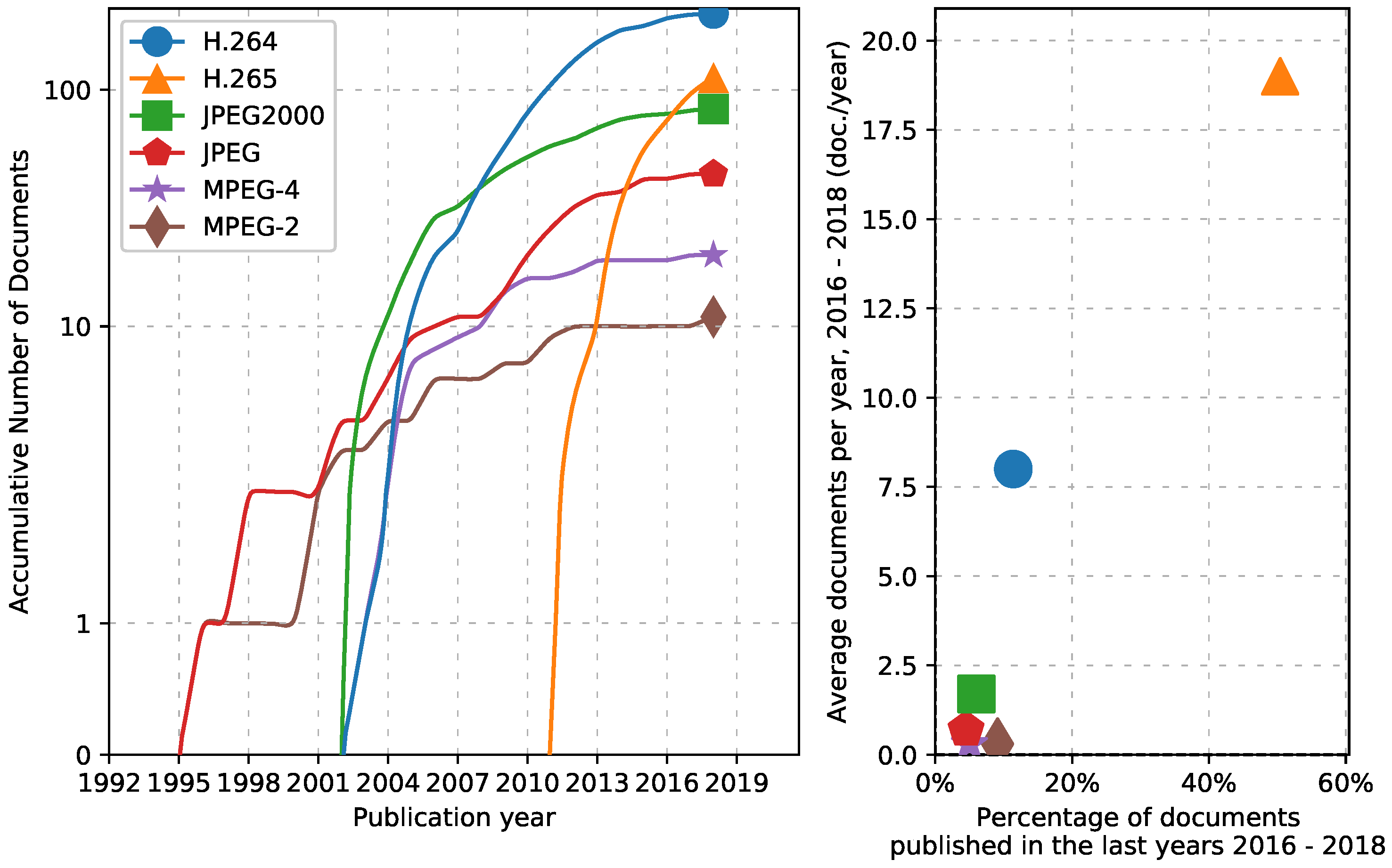

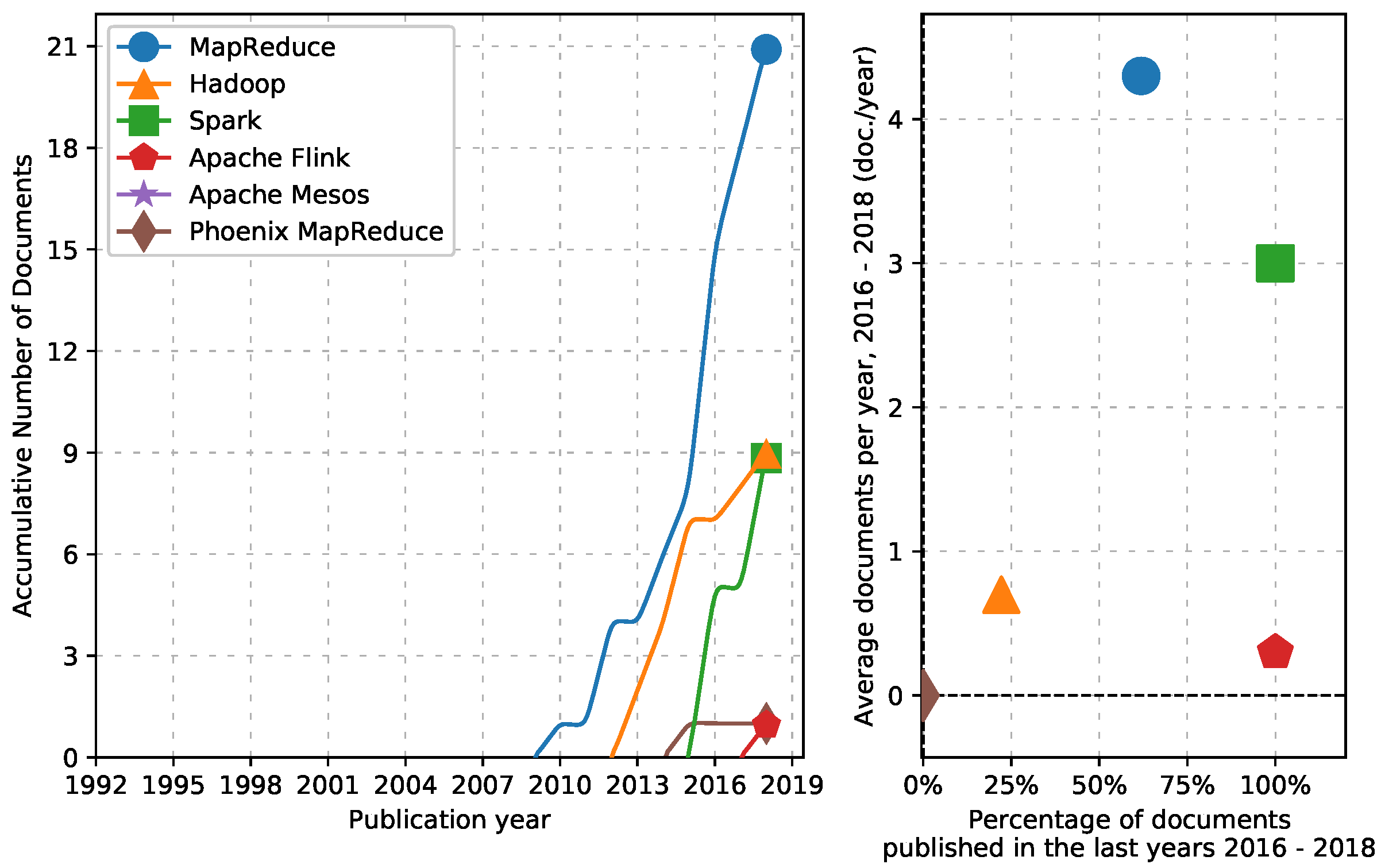

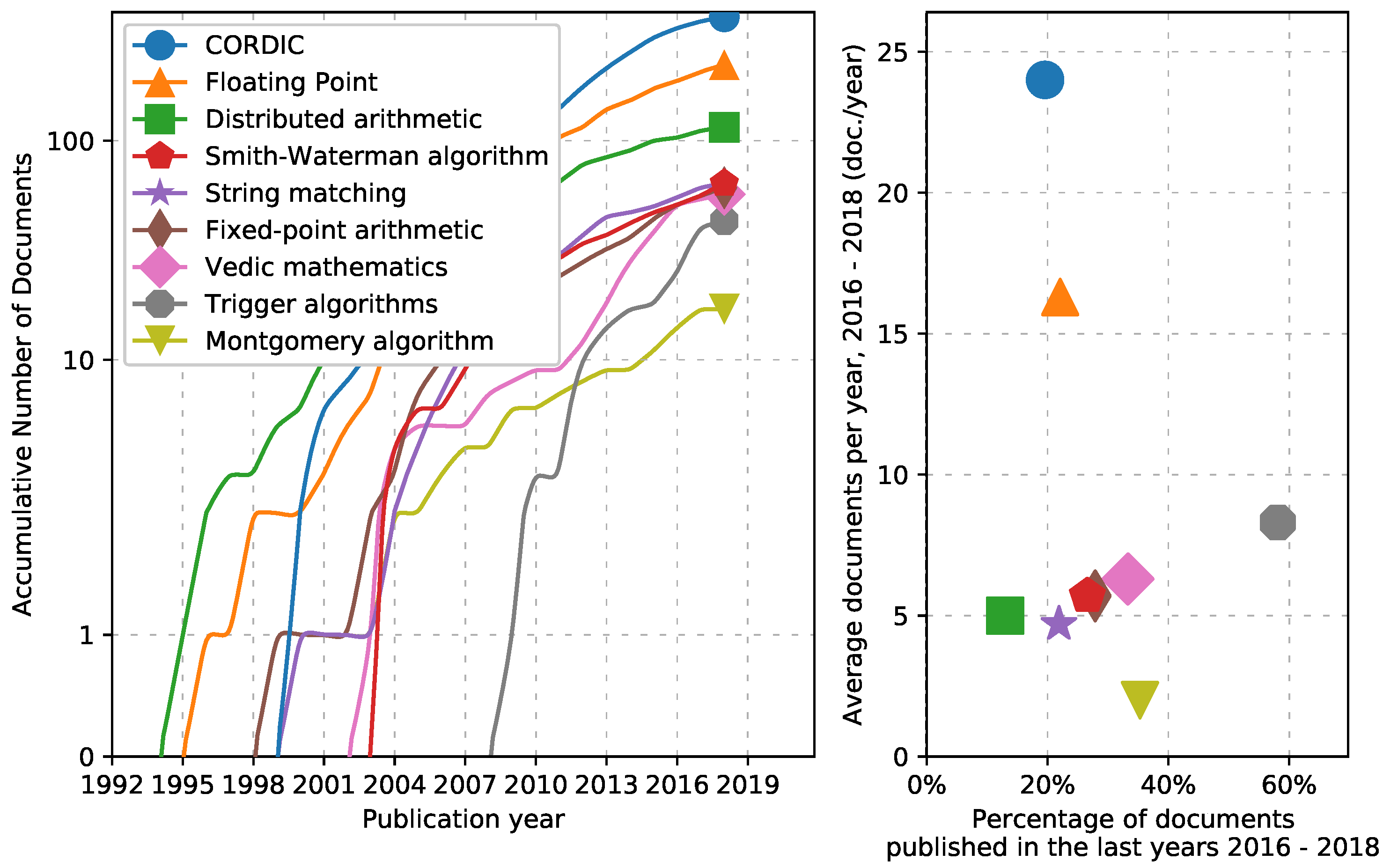

- Parametric evolution graph: this graph has two parts. The first part (left side) presents the accumulative number of documents (or papers) versus the publication year of each topic (in this case author’s keywords). With this graph, we can observe the starting year at the line’s start and the total number of documents at the line’s end. In some graphs, we put the Y-axes on a logarithmic scale to note the starting year of each topic easily. On the right side, we get the parametric plot. Here, we present the ADY and PDLY of each topic, to show the growth of the total number of documents (ADY) and the relative growth (PDLY) in the last years.

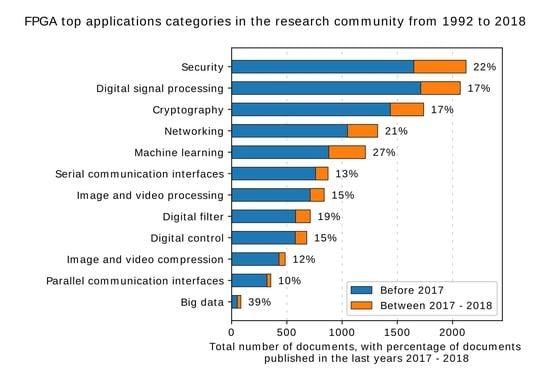

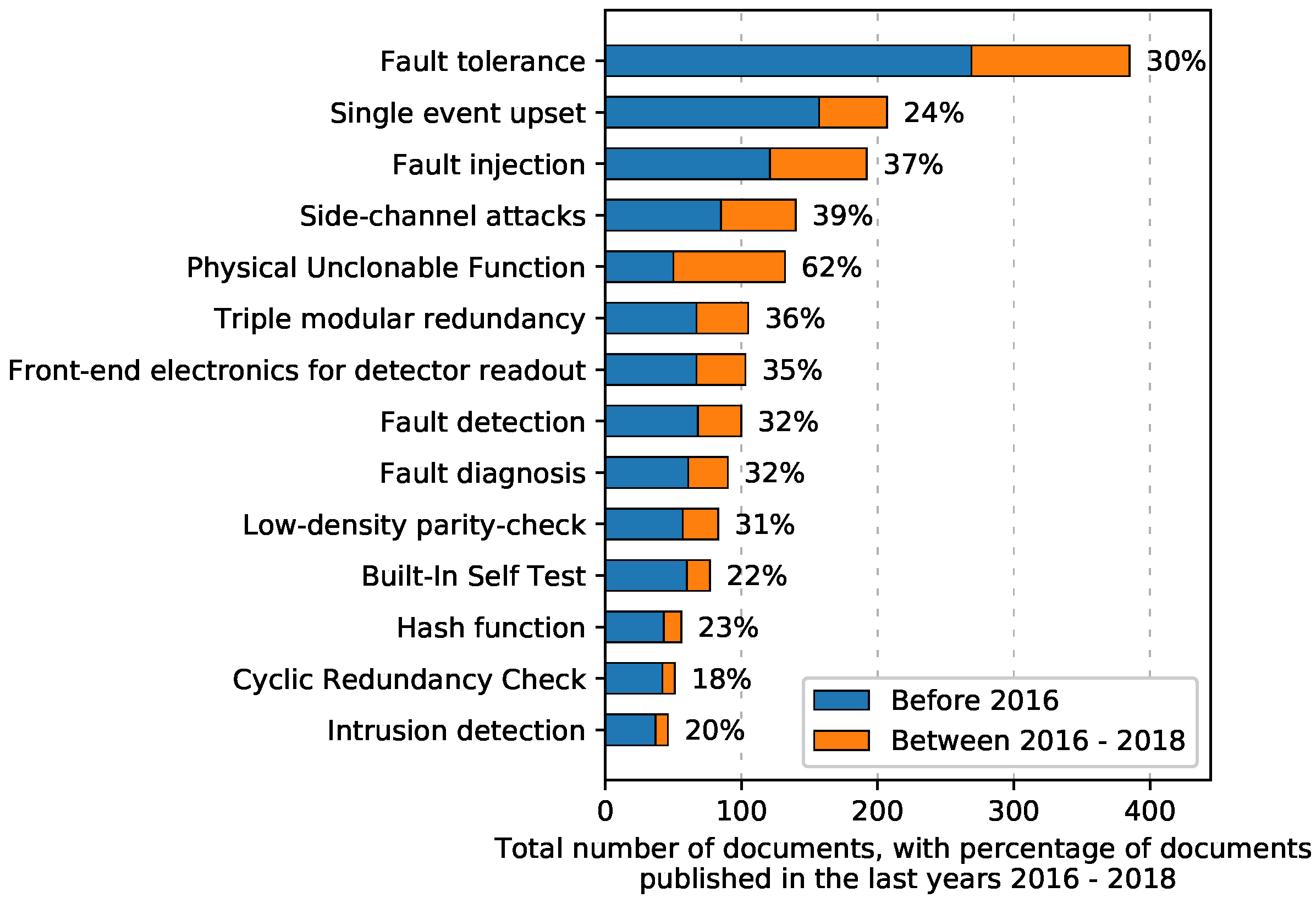

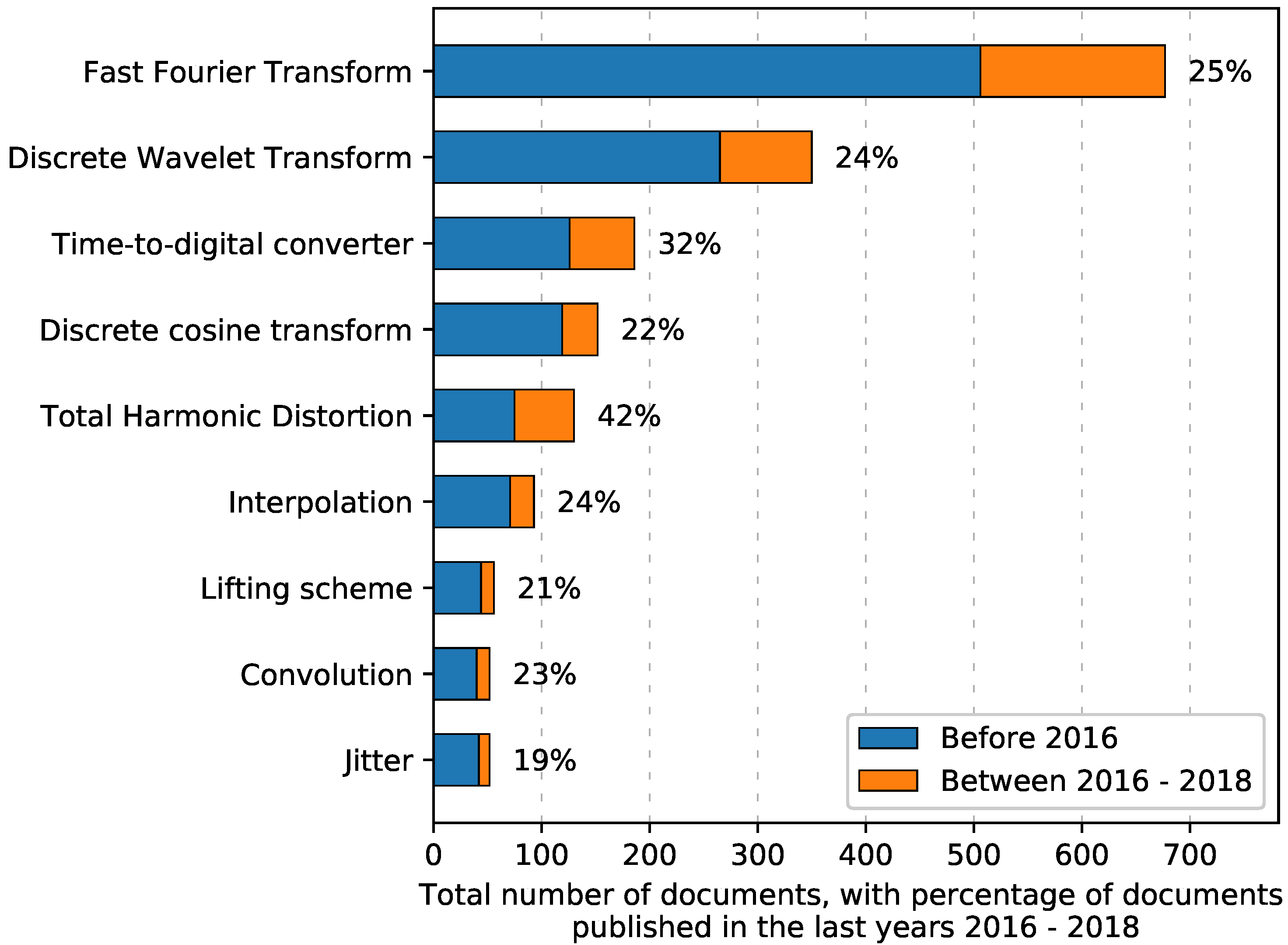

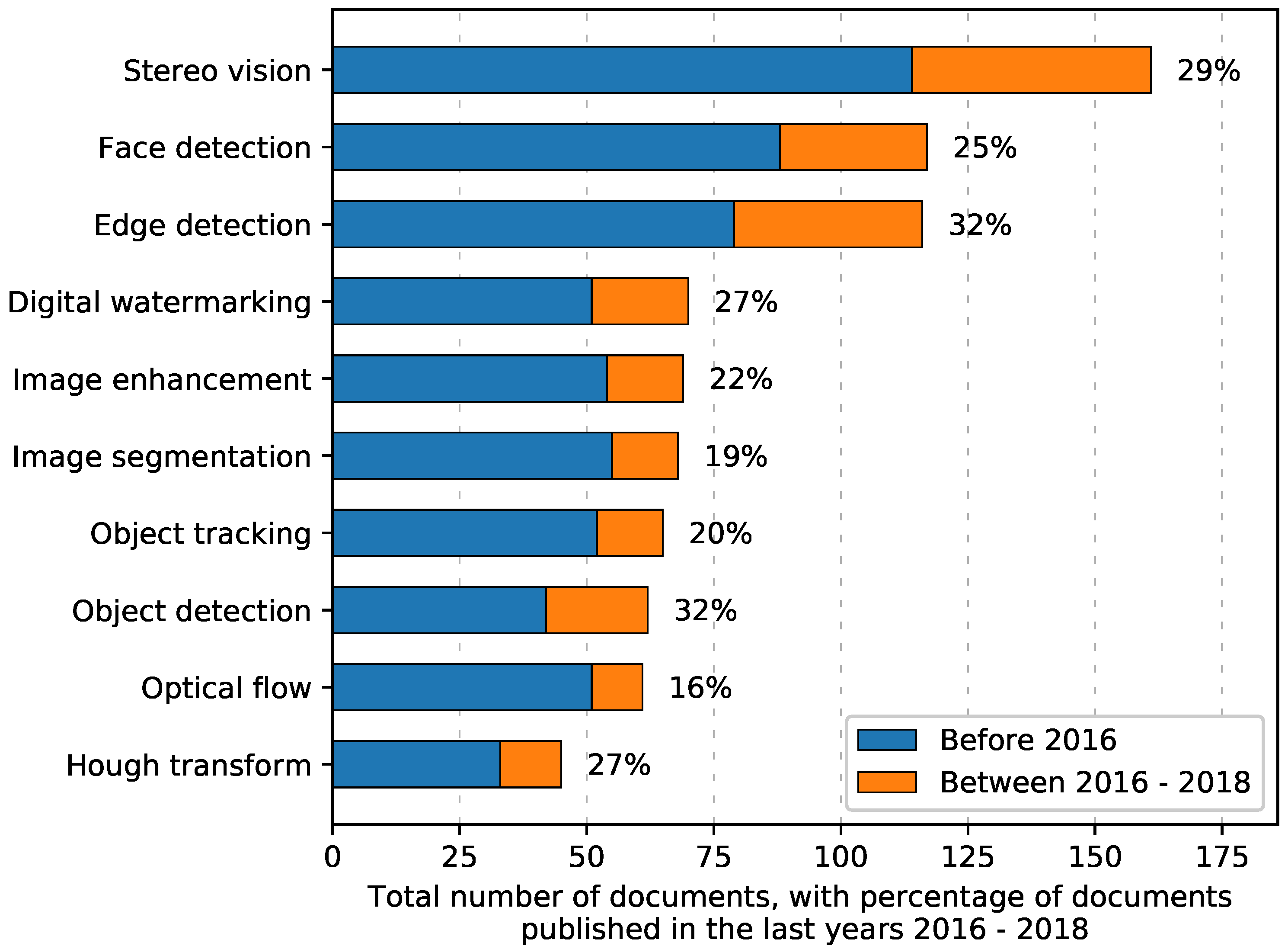

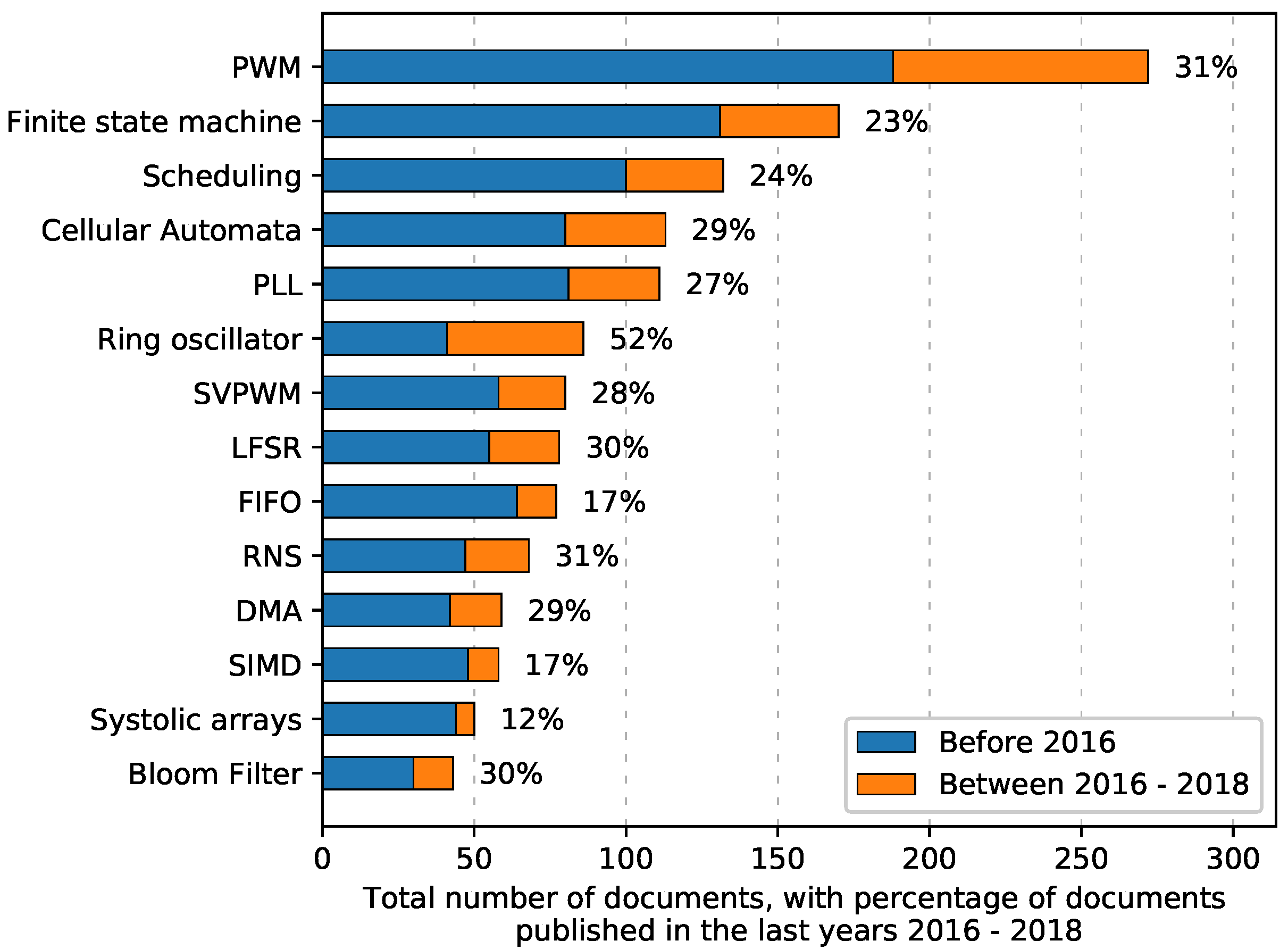

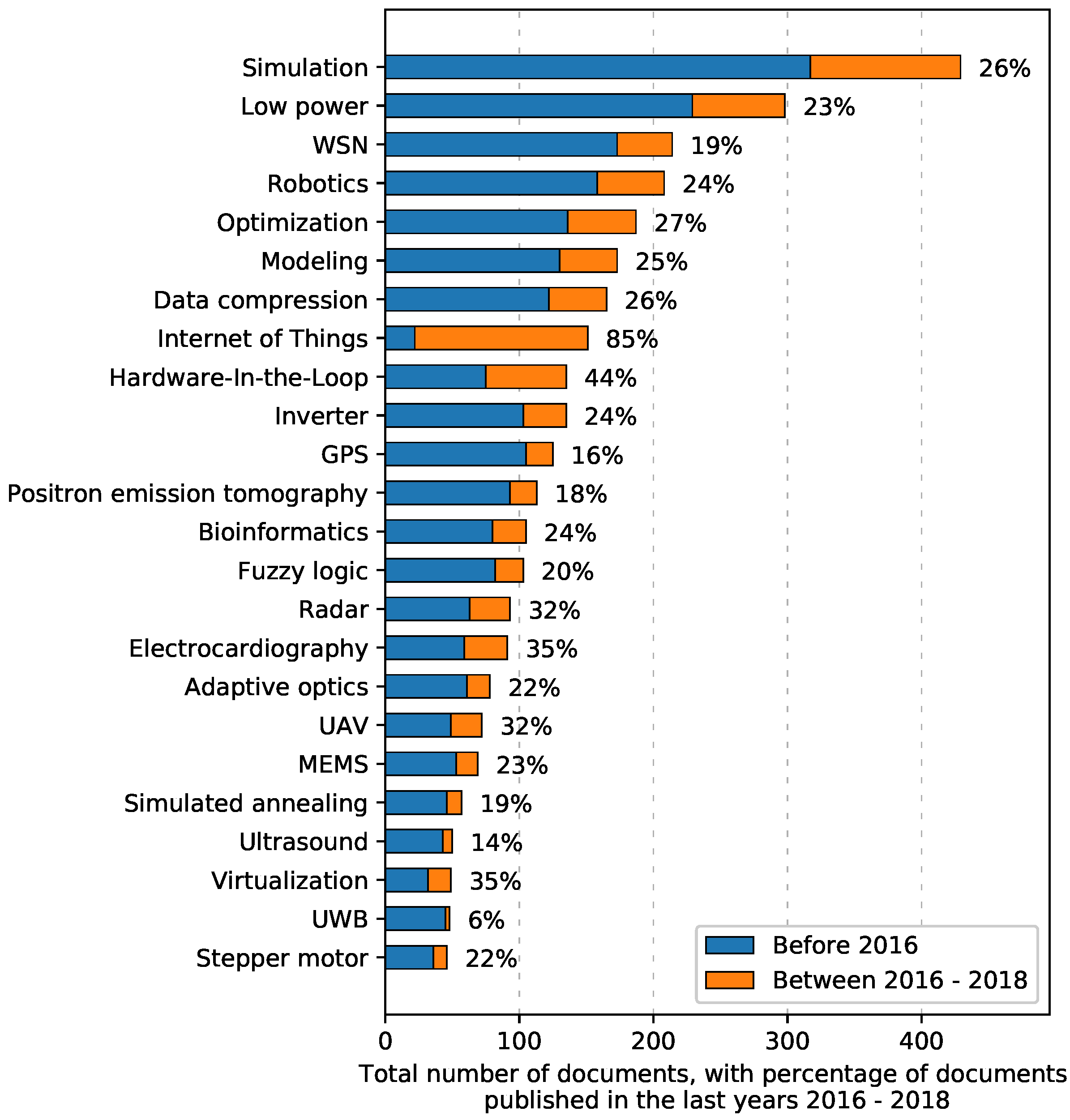

- Trending bar graph: if we need to analyze many topics in a specific section (usually more than ten topics), we use this kind of graph. Here we present the different topics in the Y-axis related to the total number of documents per topic in the X-axis with bars. Also, here we highlight in orange in the bar the documents published in the last three years (in this case 2016 to 2018), including the PDLY value.

3. Digital Control

4. Communication Interfaces

4.1. Parallel

4.2. Serial

5. Networking

6. Computer Security

Cryptography Techniques

7. Machine Learning

8. Digital Signal Processing

Digital Filters

9. Image and Video Processing

Compression Standards

10. Big Data

11. Computer Algorithms

12. Other Implementations

13. Other Applications

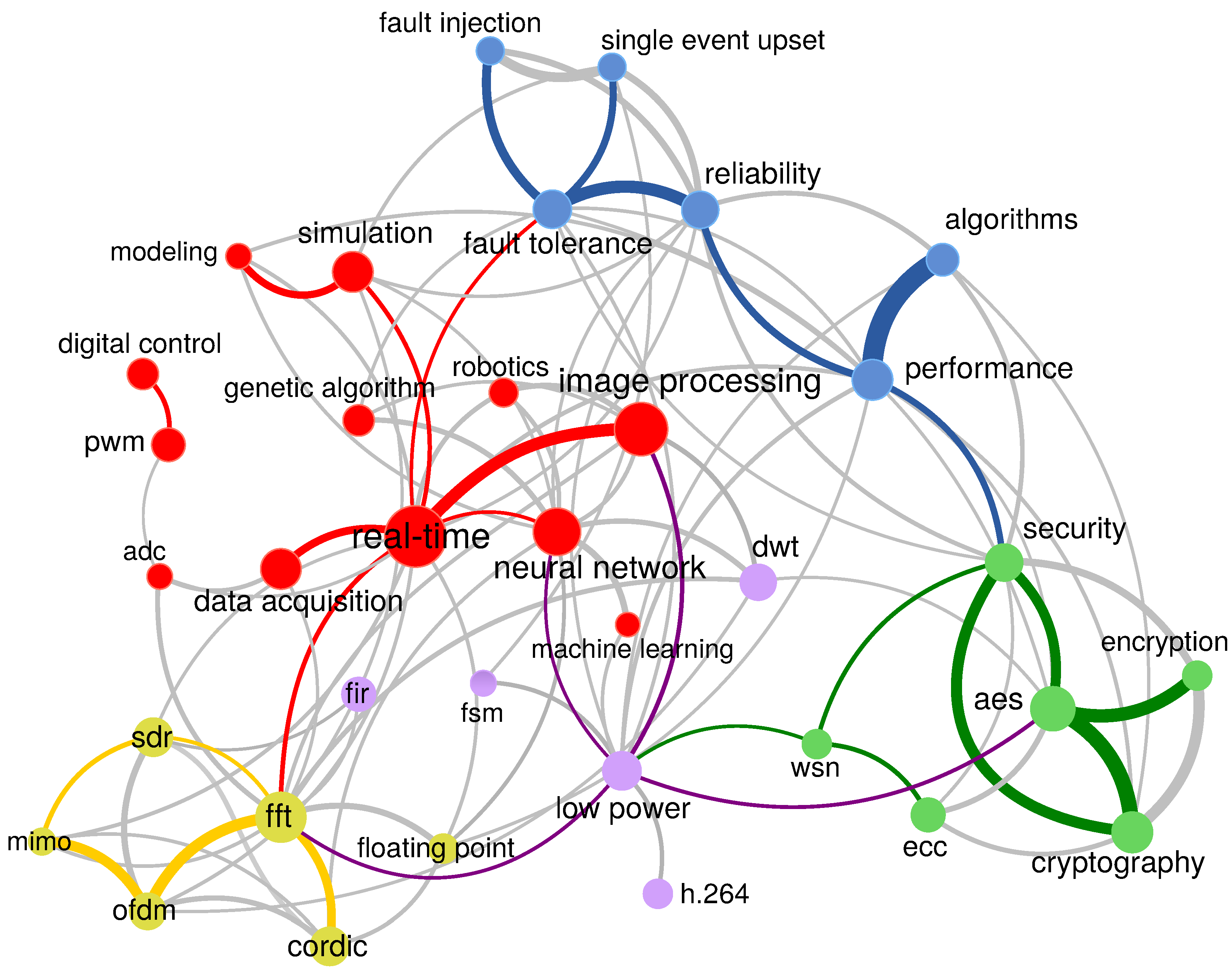

14. Applications Mapping

15. Discussion

Author Contributions

Funding

Conflicts of Interest

References

- Trimberger, S. Field-Programmable Gate Array Technology; Springer US: New York, NY, USA, 2012. [Google Scholar]

- Hamouda, M.; Blanchette, H.F.; Al-Haddad, K.; Fnaiech, F. An Efficient DSP-FPGA-Based Real-Time Implementation Method of SVM Algorithms for an Indirect Matrix Converter. IEEE Trans. Ind. Electron. 2011, 58, 5024–5031. [Google Scholar] [CrossRef]

- Pozniak, K.; Czarski, T.; Romaniuk, R. Functional analysis of DSP blocks in FPGA chips for application in TESLA LLRF system. In Proceedings of the 12th IEEE-SPIE Symposium on Photonics and Web Engineering, Wilga, Poland, 21–25 May 2003. [Google Scholar]

- Huang, J.B.; Xie, Z.W.; Liu, H.; Sun, K.; Liu, Y.C.; Jiang, Z.N. DSP/FPGA-based controller architecture for flexible joint robot with enhanced impedance performance. J. Intell. Robot. Syst. 2008, 53, 247–261. [Google Scholar] [CrossRef]

- Diaz, J.; Ros, E.; Pelayo, F.; Ortigosa, E.; Mota, S. FPGA-based real-time optical-flow system. IEEE Trans. Circuits Syst. Video Technol. 2006, 16, 274–279. [Google Scholar] [CrossRef]

- Kalomiros, J.A.; Lygouras, J. Design and evaluation of a hardware/software FPGA-based system for fast image processing. Microprocess. Microsyst. 2008, 32, 95–106. [Google Scholar] [CrossRef]

- Hegarty, J.; Brunhaver, J.; DeVito, Z.; Ragan-Kelley, J.; Cohen, N.; Bell, S.; Vasilyev, A.; Horowitz, M.; Hanrahan, P. Darkroom: Compiling High-Level Image Processing Code into Hardware Pipelines. ACM Trans. Graph. 2014, 33. [Google Scholar] [CrossRef]

- Rajagopalan, S.; Amirtharajan, R.; Upadhyay, H.; Rayappan, J. Survey and analysis of hardware cryptographic and steganographic systems on FPGA. J. Appl. Sci. 2012, 12, 201–210. [Google Scholar] [CrossRef][Green Version]

- Kean, T. Cryptographic rights management of FPGA intellectual property cores. In Proceedings of the FPGA 2002: Tenth ACM International Symposium on Field-Programmable Gate Arrays, Monterey, CA, USA, 24–26 February 2002. [Google Scholar]

- Chen, D.D.; Mentes, N.; Vercauteren, F.; Roy, S.S.; Cheung, R.C.C.; Pao, D.; Verbauwhede, I. High-Speed Polynomial Multiplication Architecture for Ring-LWE and SHE Cryptosystems. IEEE Trans. Circuits Syst. Regul. Pap. 2015, 62, 157–166. [Google Scholar] [CrossRef]

- Tsai, C.C.; Huang, H.C.; Chan, C.K. Parallel Elite Genetic Algorithm and Its Application to Global Path Planning for Autonomous Robot Navigation. IEEE Trans. Ind. Electron. 2011, 58, 4813–4821. [Google Scholar] [CrossRef]

- Jarvinen, K.; Skytta, J. On parallelization of high-speed processors for elliptic curve cryptography. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2008, 16, 1162–1175. [Google Scholar] [CrossRef]

- Keymeulen, D.; Zebulum, R.; Jin, Y.; Stoica, A. Fault-tolerant evolvable hardware using field-programmable transistor arrays. IEEE Trans. Reliab. 2000, 49, 305–316. [Google Scholar] [CrossRef]

- Cheatham, J.A.; Emmert, J.M.; Baumgart, S. A survey of fault tolerant methodologies for FPGAs. ACM Trans. Des. Autom. Electron. Syst. 2006, 11, 501–533. [Google Scholar] [CrossRef]

- Emmert, J.M.; Stroud, C.E.; Abramovici, M. Online fault tolerance for FPGA logic blocks. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2007, 15, 216–226. [Google Scholar] [CrossRef]

- Li, F.; Lin, Y.; He, L.; Cong, J. Low-power FPGA using pre-defined dual-Vdd/dual-Vt fabrics. In Proceedings of the ACM/SIGDA Twelfth ACM International Symposium on Field-Programmable Gate Arrays—FPGA 2004, Monterey, CA, USA, 22–24 February 2004. [Google Scholar]

- Zhou, Y.; Thekkel, S.; Bhunia, S. Low Power FPGA Design Using Hybrid CMOS-NEMS Approach. In Proceedings of the 12th International Symposium on Low Power Electronics and Design, Portland, OR, USA, 27–29 August 2007. [Google Scholar]

- Lee, D.; Luk, W.; Villasenor, J.; Cheung, P. A Gaussian noise generator for hardware-based simulations. IEEE Trans. Comput. 2004, 53, 1523–1534. [Google Scholar] [CrossRef]

- Tan, Z.; Waterman, A.; Avizienis, R.; Lee, Y.; Cook, H.; Patterson, D.; Asanovic, K. RAMP Gold: An FPGA-based Architecture Simulator for Multiprocessors. In Proceedings of the 47th Design Automation Conference (DAC), Anaheim, CA, USA, 13–18 June 2010. [Google Scholar]

- Hasanzadeh, A.; Edrington, C.S.; Stroupe, N.; Bevis, T. Real-Time Emulation of a High-Speed Microturbine Permanent-Magnet Synchronous Generator Using Multiplatform Hardware-in-the-Loop Realization. IEEE Trans. Ind. Electron. 2014, 61, 3109–3118. [Google Scholar] [CrossRef]

- Buccella, C.; Cecati, C.; Latafat, H. Digital Control of Power Converters-A Survey. IEEE Trans. Ind. Inform. 2012, 8, 437–447. [Google Scholar] [CrossRef]

- De Castro, A.; Zumel, P.; Garcia, O.; Riesgo, T.; Uceda, J. Concurrent and simple digital controller of an AC/DC converter with power factor correction based on an FPGA. IEEE Trans. Power Electron. 2003, 18, 334–343. [Google Scholar] [CrossRef]

- Shu, Z.; Guo, Y.; Lian, J. Steady-state and dynamic study of active power filter with efficient FPGA-based control algorithm. IEEE Trans. Ind. Electron. 2008, 55, 1527–1536. [Google Scholar] [CrossRef]

- Mellit, A.; Kalogirou, S.A. Artificial intelligence techniques for photovoltaic applications: A review. Prog. Energy Combust. Sci. 2008, 34, 574–632. [Google Scholar] [CrossRef]

- Punitha, K.; Devaraj, D.; Sakthivel, S. Artificial neural network based modified incremental conductance algorithm for maximum power point tracking in photovoltaic system under partial shading conditions. Energy 2013, 62, 330–340. [Google Scholar] [CrossRef]

- Juang, C.; Chen, J. Water bath temperature control by a recurrent fuzzy controller and its FPGA implementation. IEEE Trans. Ind. Electron. 2006, 53, 941–949. [Google Scholar] [CrossRef]

- Uchida, T. Hardware-based TCP processor for Gigabit Ethernet. In Proceedings of the IEEE Nuclear Science Symposium/Medical Imaging Conference, Honolulu, HI, USA, 26 October–3 November 2007. [Google Scholar]

- Bomel, P.; Crenne, J.; Ye, L.; Diguet, J.P.; Gogniat, G. Ultra-Fast Downloading of Partial Bitstreams through Ethernet. In Proceedings of the 22nd International Conference on Architecture of Computing Systems, Delft, The Netherlands, 10–13 March 2009. [Google Scholar]

- Wang, C.; Li, X.; Zhou, X. SODA: Software Defined FPGA based Accelerators for Big Data. In Proceedings of the 2015 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 9–13 March 2015. [Google Scholar]

- Rouhani, B.D.; Songhori, E.M.; Mirhoseini, A.; Koushanfar, F. SSketch: An Automated Framework for Streaming Sketch-based Analysis of Big Data on FPGA. In Proceedings of the 2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), Vancouver, BC, Canada, 3–5 May 2015. [Google Scholar]

- Ghasemi, E.; Chow, P. Accelerating Apache Spark with FPGAs. Concurr.-Comput.-Pract. Exp. 2019, 31. [Google Scholar] [CrossRef]

- Ghasemi, E.; Chow, P. Accelerating Apache Spark Big Data Analysis with FPGAs. In Proceedings of the 2016 Intl IEEE Conferences on Ubiquitous Intelligence & Computing, Advanced and Trusted Computing, Scalable Computing and Communications, Cloud and Big Data Computing, Internet of People, and Smart World Congress (UIC/ATC/ScalCom/CBDCom/IoP/SmartWorld), Toulouse, France, 18–21 July 2016. [Google Scholar]

- Monmasson, E.; Cirstea, M.N. FPGA design methodology for industrial control systems—A review. IEEE Trans. Ind. Electron. 2007, 54, 1824–1842. [Google Scholar] [CrossRef]

- Rodriguez-Andina, J.J.; Valdes-Pena, M.D.; Moure, M.J. Advanced Features and Industrial Applications of FPGAs-A Review. IEEE Trans. Ind. Inform. 2015, 11, 853–864. [Google Scholar] [CrossRef]

- Ahmed, S.; Sassatelli, G.; Torres, L.; Rouge, L. Survey of new trends in industry for programmable hardware: FPGAs, MPPAs, MPSoCs, structured ASICs, eFPGAs and new wave of innovation in FPGAs. In Proceedings of the 20th International Conference on Field Programmable Logic and Applications, Milano, Italy, 31 August–2 September 2010. [Google Scholar] [CrossRef]

- Naouar, M.W.; Monmasson, E.; Naassani, A.A.; Slama-Belkhodja, I.; Patin, N. FPGA-based current controllers for AC machine drives—A review. IEEE Trans. Ind. Electron. 2007, 54, 1907–1925. [Google Scholar] [CrossRef]

- Doumar, A.; Ito, H. Detecting, diagnosing, and tolerating faults in SRAM-based field programmable gate arrays: A survey. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2003, 11, 386–405. [Google Scholar] [CrossRef]

- Harikrishna, B.; Ravi, S. A Survey on Fault Tolerance in FPGAs. In Proceedings of the 7th International Conference on Intelligent Systems and Control (ISCO), Coimbatore, India, 4–5 January 2013. [Google Scholar]

- Nidhin, T.S.; Bhattacharyya, A.; Behera, R.P.; Jayanthi, T. A Review on SEU Mitigation Techniques for FPGA Configuration Memory. IETE Tech. Rev. 2018, 35, 157–168. [Google Scholar] [CrossRef]

- Papadimitriou, K.; Dollas, A.; Hauck, S. Performance of Partial Reconfiguration in FPGA Systems: A Survey and a Cost Model. ACM Trans. Reconfigurable Technol. Syst. 2011, 4. [Google Scholar] [CrossRef]

- Mellit, A.; Kalogirou, S.A. MPPT-based artificial intelligence techniques for photovoltaic systems and its implementation into field programmable gate array chips: Review of current status and future perspectives. Energy 2014, 70, 1–21. [Google Scholar] [CrossRef]

- De la Piedra, A.; Braeken, A.; Touhafi, A. Sensor Systems Based on FPGAs and Their Applications: A Survey. Sensors 2012, 12, 12235–12264. [Google Scholar] [CrossRef]

- Garcia, G.J.; Jara, C.A.; Pomares, J.; Alabdo, A.; Poggi, L.M.; Torres, F. A Survey on FPGA-Based Sensor Systems: Towards Intelligent and Reconfigurable Low-Power Sensors for Computer Vision, Control and Signal Processing. Sensors 2014, 14, 6247–6278. [Google Scholar] [CrossRef] [PubMed]

- Chen, H.; Chen, Y.; Summerville, D.H. A Survey on the Application of FPGAs for Network Infrastructure Security. IEEE Commun. Surv. Tutor. 2011, 13, 541–561. [Google Scholar] [CrossRef]

- Hailes, P.; Xu, L.; Maunder, R.G.; Al-Hashimi, B.M.; Hanzo, L. A Survey of FPGA-Based LDPC Decoders. IEEE Commun. Surv. Tutor. 2016, 18, 1098–1122. [Google Scholar] [CrossRef]

- Andraka, R. Survey of CORDIC algorithms for FPGA based computers. In Proceedings of the 1998 ACM/SIGDA 6th International Symposium on Field Programmable Gate Arrays, FPGA, New York, NY, USA, 22–24 February 1998. [Google Scholar]

- Singh, A.; Prasad, A.; Talwar, Y. SCADA Security Issues and FPGA implementation of AES - A Review. In Proceedings of the 2nd IEEE International Conference on Next Generation Computing Technologies (NGCT), Dehradun, India, 14–16 October 2016. [Google Scholar]

- Venieris, S.I.; Kouris, A.; Bouganis, C.S. Toolflows for Mapping Convolutional Neural Netw. on FPGAs: A Survey and Future Directions. ACM Comput. Surv. 2018, 51. [Google Scholar] [CrossRef]

- Mittal, S. A survey of FPGA-based accelerators for convolutional neural networks. Neural Comput. Appl. 2018. [Google Scholar] [CrossRef]

- Blaiech, A.G.; Khalifa, K.B.; Valderrama, C.; Fernandes, M.A.; Bedoui, M.H. A Survey and Taxonomy of FPGA-based Deep Learning Accelerators. J. Syst. Archit. 2019. [Google Scholar] [CrossRef]

- Shawahna, A.; Sait, S.M.; El-Maleh, A. FPGA-Based Accelerators of Deep Learning Networks for Learning and Classification: A Review. IEEE Access 2019, 7, 7823–7859. [Google Scholar] [CrossRef]

- Popescu, S.; Budura, G.; Gontean, A. Review of PSK and QAM—Digital modulation techniques on FPGA. In Proceedings of the 2010 International Joint Conferences on Computational Cybernetics and Technical Informatics, Timisoara, Romania, 27–29 May 2010. [Google Scholar] [CrossRef]

- Sun, F.; Wang, H.; Fu, F.; Li, X. Survey of FPGA low power design. In Proceedings of the 2010 International Conference on Intelligent Control and Information Processing, Dalian, China, 13–15 August 2010. [Google Scholar] [CrossRef]

- Alkhafaji, F.; Hasan, W.; Isa, M.; Sulaiman, N. Robotic controller: ASIC versus FPGA—A review. J. Comput. Theor. Nanosci. 2018, 15, 1–25. [Google Scholar] [CrossRef]

- Muralidar, D.; Silambarasan, R. A review about different automotive safety system using FPGA. J. Chem. Pharm. Sci. 2016, 9, 3353–3355. [Google Scholar]

- Jyoti; Kumar, A.; Sangwan, A. Designing of FIR filter using FPGA: A review. In Proceedings of the 3rd International Conference on Nanoelectronics, Circuits and Communication Systems, NCCS 2017, 11–12 November 2017. [Google Scholar] [CrossRef]

- Amulya, K.; Sadashivappa, G. Design and Implementation of a Reconfigurable Digital Down Converter for 4G Systems Using MATLAB and FPGA- A Review. In Proceedings of the 2018 IEEE Conference on Emerging Devices and Smart Systems, ICEDSS 2018, Tamilnadu, India, 2–3 March 2018. [Google Scholar] [CrossRef]

- Bouhali, M.; Shamani, F.; Dahmane, Z.E.; Belaidi, A.; Nurmi, J. FPGA Applications in Unmanned Aerial Vehicles - A Review. In Proceedings of the 13th International Symposium on Applied Reconfigurable Computing (ARC), Delft, The Netherlands, 3–7 April 2017. [Google Scholar] [CrossRef]

- Sharma, B.L.; Khatri, N.; Sharma, A. An Analytical Review on FPGA Based Autonomous Flight Control System for Small UAVs. In Proceedings of the International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), Palnchur, India, 3–5 March 2016. [Google Scholar]

- Bakiri, M.; Guyeux, C.; Couchot, J.F.; Oudjida, A.K. Survey on hardware implementation of random number generators on FPGA: Theory and experimental analyses. Comput. Sci. Rev. 2018, 27, 135–153. [Google Scholar] [CrossRef]

- Sadrozinski, H.F.W.; Wu, J. Applications of Field-Programmable Gate Arrays in Scientific Research, 1st ed.; Taylor & Francis, Inc.: Bristol, PA, USA, 2010. [Google Scholar]

- Rao, S. Field Programmable Gate Array and Applications. Available online: https://patents.google.com/patent/US5208491A/en (accessed on 8 November 2019).

- Ruiz-Rosero, J.; Ramirez-Gonzalez, G.; Viveros-Delgado, J. Software survey: ScientoPy, a scientometric tool for topics trend analysis in scientific publications. Scientometrics 2019, 121, 1165–1188. [Google Scholar] [CrossRef]

- Bakshi, U.; Bakshi, V. Control Systems Engineering. Available online: https://www.researchgate.net/publication/265168969_Control_Systems_Engineering (accessed on 8 November 2019).

- Kung, Y.S.; Fung, R.F.; Tai, T.Y. Realization of a Motion Control IC for X-Y Table Based on Novel FPGA Technology. IEEE Trans. Ind. Electron. 2009, 56, 43–53. [Google Scholar] [CrossRef]

- Del Campo, I.; Echanobe, J.; Basterretxea, K.; Bosque, G. Scalable architecture for high-speed multidimensional fuzzy inference systems. J. Circuits Syst. Comput. 2011, 20, 375–400. [Google Scholar] [CrossRef]

- Qin, W.; Zhou, J.; Li, C. Research of Continuous Variable Camshaft Timing system based on fuzzy-PID control method. In Proceedings of the 2011 2nd International Conference on Mechanic Automation and Control Engineering, Hohhot, China, 15–17 July 2011. [Google Scholar]

- Hwu, K.I.; Yau, Y.T. Performance Enhancement of Boost Converter Based on PID Controller Plus Linear-to-Nonlinear Translator. IEEE Trans. Power Electron. 2010, 25, 1351–1361. [Google Scholar] [CrossRef]

- Chander, S.; Agarwal, P.; Gupta, I. FPGA-based PID controller for DC-DC converter. In Proceedings of the 2010 Joint International Conference on Power Electronics, Drives and Energy Systems & 2010 Power India, New Delhi, India, 20–23 December 2010. [Google Scholar]

- Sivaramakrishna, M.; Upadhyay, C.; Nagaraj, C.; Madhusoodanan, K. Development of pid controller algorithm over FPGA for motor control in failed fuel location module in Indian fast reactors. In Proceedings of the 2011 3rd International Conference on Electronics Computer Technology, ICECT 2011, Kanyakumari, India, 8–10 April 2011. [Google Scholar]

- Stambaugh, C. The control system for the magnetic suspension comparator system for vacuum-to-air mass dissemination. Acta IMEKO 2017, 6, 75–79. [Google Scholar] [CrossRef]

- Camacho, E.; Bordons, C.; Alba, C. Model Predictive Control; Advanced Textbooks in Control and Signal Processing; Springer: London, UK, 2004. [Google Scholar]

- Ling, K.V.; Yue, S.P.; Maciejowski, J.M. A FPGA implementation of model predictive control. In Proceedings of the American Control Conference 2006, Minneapolis, MN, USA, 14–16 June 2006. [Google Scholar]

- Hartley, E.N.; Jerez, J.L.; Suardi, A.; Maciejowski, J.M.; Kerrigan, E.C.; Constantinides, G.A. Predictive Control Using an FPGA With Application to Aircraft Control. IEEE Trans. Control. Syst. Technol. 2014, 22, 1006–1017. [Google Scholar] [CrossRef]

- Morales-Caporal, R.; Pacas, M. Encoderless Predictive Direct Torque Control for Synchronous Reluctance Machines at Very Low and Zero Speed. IEEE Trans. Ind. Electron. 2008, 55, 4408–4416. [Google Scholar] [CrossRef]

- Curkovic, M.; Jezernik, K.; Horvat, R. FPGA-Based Predictive Sliding Mode Controller of a Three-Phase Inverter. IEEE Trans. Ind. Electron. 2013, 60, 637–644. [Google Scholar] [CrossRef]

- Ramirez, R.O.; Espinoza, J.R.; Melin, P.E.; Reyes, M.E.; Espinosa, E.E.; Silva, C.; Maurelia, E. Predictive Controller for a Three-Phase/Single-Phase Voltage Source Converter Cell. IEEE Trans. Ind. Inform. 2014, 10, 1878–1889. [Google Scholar] [CrossRef]

- Hartley, E.N.; Maciejowski, J.M. Field programmable gate array based predictive control system for spacecraft rendezvous in elliptical orbits. Optim. Control. Appl. Methods 2015, 36, 585–607. [Google Scholar] [CrossRef]

- Ioannou, P.A.; Sun, J. Robust Adaptive Control; Prentice-Hall, Inc.: Upper Saddle River, NJ, USA, 1995. [Google Scholar]

- Huang, H.C.; Tsai, C.C. FPGA Implementation of an Embedded Robust Adaptive Controller for Autonomous Omnidirectional Mobile Platform. IEEE Trans. Ind. Electron. 2009, 56, 1604–1616. [Google Scholar] [CrossRef]

- Huang, H.C.; Tsai, C.C.; Lin, S.C. Adaptive Polar-Space Motion Control for Embedded Omnidirectional Mobile Robots with Parameter Variations and Uncertainties. J. Intell. Robot. Syst. 2011, 62, 81–102. [Google Scholar] [CrossRef]

- Wu, T.F.; Huang, H.C.; Tsai, P.S.; Hu, N.T.; Yang, Z.Q. Adaptive Fuzzy CMAC Design for an Omni-Directional Mobile Robot. In Proceedings of the 10th International Conference on Intelligent Information Hiding and Multimedia Signal Processing (IIH-MSP), Kitakyushu, Japan, 27–29 August 2014. [Google Scholar]

- Suzuki, S.; Nonami, K. Nonlinear adaptive control for small-scale helicopter. J. Syst. Des. Dyn. 2011, 5, 866–880. [Google Scholar] [CrossRef]

- Li, L.R.; Wang, Z.H.; Li, Z.; Lu, Q.; Ma, G.X. The Adaptive Control Method of the Energy-efficient Tunnel Lighting System. In Proceedings of the International Conference oInternational Conference on Advances in Management Engineering and Information Technology (AMEIT), Bangkok, Thailand, 28–29 June 2015. [Google Scholar]

- Trivedi, A.; Singh, M. L-1 Adaptive Droop Control for AC Microgrid With Small Mesh Network. IEEE Trans. Ind. Electron. 2018, 65, 4781–4789. [Google Scholar] [CrossRef]

- Rajagopal, K.; Karthikeyan, A.; Srinivasan, A.K. FPGA implementation of novel fractional-order chaotic systems with two equilibriums and no equilibrium and its adaptive sliding mode synchronization. Nonlinear Dyn. 2017, 87, 2281–2304. [Google Scholar] [CrossRef]

- Karthikeyan, R.; Prasina, A.; Babu, R.; Raghavendran, S. FPGA implementation of novel synchronization methodology for a new chaotic system. Indian J. Sci. Technol. 2015, 8. [Google Scholar] [CrossRef]

- Quang, N.K.; Hieu, N.T.; Ha, Q.P. FPGA-Based Sensorless PMSM Speed Control Using Reduced-Order Extended Kalman Filters. IEEE Trans. Ind. Electron. 2014, 61, 6574–6582. [Google Scholar] [CrossRef]

- Idkhajine, L.; Monmasson, E. Optimized FPGA-based Extended Kalman Filter application to an AC drive sensorless speed controller. In Proceedings of the 2010 International Symposium on Power Electronics, Electrical Drives, Automation and Motion, SPEEDAM 2010, Pisa, Italy, 14–16 June 2010. [Google Scholar] [CrossRef]

- Pantea, A.; Aroquiadassou, G.; Mabwe, A.; Martis, C. Real-time sensorless vector control of induction machines using an FPGA board. In Proceedings of the 21st International Symposium on Power Electronics, Electrical Drives, Automation and Motion, SPEEDAM 2012, Sorrento, Italy, 20–22 June 2012. [Google Scholar] [CrossRef]

- Maalouf, A.; Le Ballois, S.; Monmasson, E.; Midy, J.Y.; Bruzy, C. FPGA-based sensorless control of brushless synchronous starter generator at standstill and low speed using high frequency signal injection for an aircraft application. In Proceedings of the ICELIE/IES Industry Forum/37th Annual Conference of the IEEE Industrial-Electronics-Society (IECON), Melbourne, Australia, 7–10 November 2011. [Google Scholar]

- Ma, Z.; Gao, J.; Kennel, R. FPGA Implementation of a Hybrid Sensorless Control of SMPMSM in the Whole Speed Range. IEEE Trans. Ind. Inform. 2013, 9, 1253–1261. [Google Scholar] [CrossRef]

- Ma, Z.; Kennel, R. System-on-Chip sensorless control of PMSM combining signal injection and flux observer. In Proceedings of the 2012 IEEE 7th International Power Electronics and Motion Control Conference - ECCE Asia, IPEMC 2012, Harbin, China, 2–5 June 2012. [Google Scholar] [CrossRef]

- Jezernik, K.; Rodic, M. Torque Sensorless Control of Induction Motor. In Proceedings of the 13th International Power Electronics and Motion Control Conference, Poznan, Poland, 1–3 September 2008; pp. 2283–2288. [Google Scholar] [CrossRef]

- Wolfram, S. Cellular Automata And Complexity: Collected Papers; CRC Press: Boca Raton, FL, USA, 2018. [Google Scholar]

- Chapuis, Y.A.; Zhou, L.; Fukuta, Y.; Mita, Y.; Fujita, H. FPGA-based decentralized control of arrayed MEMS for microrobotic application. IEEE Trans. Ind. Electron. 2007, 54, 1926–1936. [Google Scholar] [CrossRef]

- Li, Y.F.; Chuang, L.L. Controller design for music playing robot - applied to the anthropomorphic piano robot. In Proceedings of the IEEE 10th International Conference on Power Electronics and Drive Systems (PEDS), Kitakyushu, Japan, 22–25 April 2013. [Google Scholar]

- Li, Y.F. FPGA-based module design for PM linear motor control-applied to music playing robot. In Proceedings of the IEEE International Symposium on Industrial Electronics (ISIE), Taipei, Taiwan, 28–31 May 2013. [Google Scholar]

- Li, Y.F. FPGA-Based Distributed Control Module Design for Music Playing Robot - Applied to the Anthropomorphic Piano Robot Control. J. Chin. Soc. Mech. Eng. 2013, 34, 143–150. [Google Scholar]

- Costillo, L.; Ramos, J.; Ibanez, J.; Aparicio, B.; Herranz, M.; Garcia, A. New control system for the 1.5m and 0.9m telescopes at Sierra Nevada Observatory. In Proceedings of the Advanced Software and Control for Astronomy, Orlando, FL, USA, 24–26 May 2006. [Google Scholar] [CrossRef]

- Cherif, S.; Trabelsi, C.; Meftali, S.; Dekeyser, J.L. High level design of adaptive distributed controller for partial dynamic reconfiguration in FPGA. In Proceedings of the 2011 Conference on Design and Architectures for Signal and Image Processing, DASIP 2011, Tampere, Finland, 2–4 November 2011. [Google Scholar] [CrossRef]

- Trabelsi, C.; Meftali, S.; Dekeyser, J.L. Distributed control for reconfigurable FPGA systems: A high-level design approach. In Proceedings of the 7th International Workshop on Reconfigurable Communication-centric Systems-on-Chip (ReCoSoC), York, UK, 9–11 July 2012. [Google Scholar]

- Trabelsi, C.; Meftali, S.; ben Atitallah, R.; Dekeyser, J.L. Model-Driven design flow for distributed control in reconfigurable FPGA systems. In Proceedings of the 8th Conference on Design and Architectures for Signal and Image Processing (DASIP), Madrid, Spain, 8–10 October 2014. [Google Scholar]

- Sarpotdar, M.; Mathew, J.; Safonova, M.; Murthy, J. A generic FPGA-based detector readout and real-time image processing board. In Proceedings of the Conference on High Energy, Optical, and Infrared Detectors for Astronomy VII, Edinburgh, UK, 26–29 June 2016. [Google Scholar] [CrossRef]

- Bendapudi, S.; Kashyap, G.K.; Lithin, M.G.; Subhajit, M.; KrishnamPrasad, B.; Shashikala, T.H. Design of Video Processor for Multi-head Star Sensor. In Proceedings of the 2nd International Symposium on Physics and Technology of Sensors, Pune, India, 8–10 March 2015. [Google Scholar]

- Strauss, M.; Westbrook, E.; Naday, I.; Coleman, T.; Westbrook, M.; Travis, D.; Sweet, R.; Pflugrath, J.; Stanton, M. CCD-based detector for protein crystallography with synchrotron X-rays. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrom. Detect. Assoc. Equip. 1990, 297, 275–295. [Google Scholar] [CrossRef]

- Bredthauer, G. Archon: A modern controller for high performance astronomical CCDs. In Proceedings of the 5th Conference on Ground-Based and Airborne Instrumentation for Astronomy, Montreal, Canada, 22–26 June 2014. [Google Scholar] [CrossRef]

- Liu, S.; Zhao, K.S.; Long, Z.C.; Feng, L. Embedded CCD acquisition system based on ARM and FPGA. Guangdianzi Jiguang/J. Optoelectron. Laser 2007, 18, 1296–1298. [Google Scholar]

- Wang, B.; Bai, Y.L.; Ou-Yang, X.; Liu, B.Y.; Bai, X.H.; Zhao, J.P. Spectrum data acquisition system based on linear CCD. Guangzi Xuebao/Acta Photonica Sin. 2010, 39, 441–445. [Google Scholar] [CrossRef]

- Zhang, Y.; Jin, M.; Zhang, Y.; Liu, H. Development of High-speed and Highly Integrated CCD Laser Range Sensor Based on FPGA. In Proceedings of the 11th World Congress on Intelligent Control and Automation, Shenyang, China, 29 June–4 July 2014. [Google Scholar]

- Kasprowicz, G.; Czyrkowski, H.; Dabrowski, R.; Dominik, W.; Mankiewicz, L.; Pozniak, K.; Romaniuk, R.; Sitek, P.; Sokolowski, M.; Sulej, R.; et al. New low noise CCD cameras for “Pi of the Sky” project. In Proceedings of the Conference on Photonics Applications in Astronomy, Communications, Industry, and High-Energy Physics Experiments 2006, Wilga, Poland, 29 May–4 June 2006. [Google Scholar] [CrossRef]

- Burd, A.; Czyrkowski, H.; Dabrowski, R.; Dominik, W.; Grajda, M.; Kasprowicz, G.; Mankiewicz, L.; Stankiewicz, S.; Wrochna, G. Low noise CCD cameras for wide field astronomy. In Proceedings of the Conference on Photonics, Applications in Astronomy, Communications, Industry, and High-Energy Physics Experiments IV, Wilga, Poland, 30 May–5 June 2005. [Google Scholar] [CrossRef]

- Xu, W.H.; Wu, H.D. Design of ultra-high resolution CCD imaging systems. Guangxue Jingmi Gongcheng/Optics Precis. Eng. 2012, 20, 1603–1610. [Google Scholar] [CrossRef]

- Zhiyong, L.; Weihua, Y.; Xiance, D. The analog front end of ultra-high resolution CCD design based on AD9920A. In Proceedings of the 8th International Conference on Intelligent Computation Technology and Automation (ICICTA), Nanchang, China, 14–15 June 2015. [Google Scholar] [CrossRef]

- Li, F.N.; Wang, Y.J.; Zhang, T.; Sun, H.H. Design of high-speed high-resolution CMOS camera acquisition system based on AM41V4 sensor. Chin. J. Liq. Cryst. Disp. 2015, 30, 492–498. [Google Scholar] [CrossRef]

- Sun, H.; Cai, R.; Wang, Y. Design and implementation of high-speed digital CMOS camera driving control timing and data interface. In Proceedings of the Sixth International Symposium on Instrumentation and Control Technology: Sensors, Automatic Measurement, Control and Computer Simulation, Beijing, China, 13–15 October 2006. [Google Scholar] [CrossRef]

- Ge, Z.W.; Yao, S.Y.; Xu, J.T.; Su, X.H. A fast automatic exposure control method for CMOS image sensor. Tianjin Daxue Xuebao (Ziran Kexue yu Gongcheng Jishu Ban)/J. Tianjin Univ. Sci. Technol. 2010, 43, 854–859. [Google Scholar]

- An, R.; Chen, Y.; Xie, J. Exposure algorithm for CMOS image sensor with adaptive dynamic range. Hongwai yu Jiguang Gongcheng/Infrared Laser Eng. 2013, 42, 88–92. [Google Scholar]

- Liu, Y.; Wu, Z.; Liu, C.; Zhu, X.; Liu, G. Study on an Auto Exposure Algorithm Applied in CMOS Image Sensor for Security Monitoring. Bandaoti Guangdian/Semicond. Optoelectron. 2017, 38, 283–287. [Google Scholar] [CrossRef]

- Yang, W.C.; Wen, D.S.; Chen, S.D.; Wang, H. Spatial transient light detection based on high-speed CMOS image sensor. Guangzi Xuebao/Acta Photonica Sin. 2010, 39, 764–768. [Google Scholar] [CrossRef]

- Yang, D.; Hu, X.; Li, J. Multiple slope integration based on CMOS image sensor. Hongwai Yu Jiguang Gongcheng/Infrared Laser Eng. 2012, 41, 1499–1502. [Google Scholar]

- Fross, B.; Donaldson, R.; Palmer, D. PCI-based WILDFIRE reconfigurable computing engines. In Proceedings of the High-Speed Computing, Digital Signal Processing, and Filtering Using Reconfigurable Logic, Boston, MA, USA, 20–21 November 1996. [Google Scholar] [CrossRef]

- Mizuno, K.; Noguchi, H.; He, G.; Terachi, Y.; Kamino, T.; Kawaguchi, H.; Yoshimoto, M. Fast and low-memory-bandwidth architecture of SIFT descriptor generation with scalability on speed and accuracy for VGA video. In Proceedings of the 20th International Conference on Field Programmable Logic and Applications, FPL 2010, Milano, Italy, 31 August–2 September 2010. [Google Scholar]

- Zhang, J.M.; Jiang, X.Y.; Zhang, Z.L. Gray-scale control of synchronous VGA display by OLED matrix. Guangdianzi Jiguang/J. Optoelectron. Laser 2006, 17, 131–134. [Google Scholar]

- Gao, K.; Cai, J.; Zhang, L.; Sheng, R.n. A SoPC-Based Mini VGA Video Capture and Storage System. In Proceedings of the 2010 3rd International Conference on Biomedical Engineering and Informatics (BMEI 2010), Yantai, China, 16–18 October 2010. [Google Scholar] [CrossRef]

- Sajjanar, S.; Mankani, S.K.; Dongrekar, P.R.; Kumar, N.S.; Mohana; Aradhya, H.V.R. Implementation of Real Time Moving Object Detection and Tracking on FPGA for Video Surveillance Applications. In Proceedings of the IEEE International Conference on Distributed Computing, VLSI, Electrical Circuits and Robotics (DISCOVER), Mangalore, India, 13–14 August 2016. [Google Scholar]

- Murali, K.B.; Tejaswi, P.; Madhumati, G.; Vinay, K.K. Real time delay application for digital circuits with peripheral based digital clock using FPGA. Int. J. Appl. Eng. Res. 2014, 9, 5115–5124. [Google Scholar]

- Bertazzoni, S.; Di, G.D.; Salmeri, M.; Mongiardo, L.; Florean, M.; Salsano, A.; Wyss, J.; Rando, R. TID test for SDRAM based IEEM calibration system. In Proceedings of the 2004 Nuclear Science Symposium, Medical Imaging Conference, Symposium on Nuclear Power Systems and the 14th International Workshop on Room Temperature Semiconductor X- and Gamma- Ray Detectors, Rome, Italy, 16–22 October 2004. [Google Scholar]

- Bunkowski, K.; Kassamakov, I.; Krolikowski, J.; Kierzkowski, K.; Kudla, M.; Maenpaa, T.; Pozniak, K.; Rybka, D.; Tuominen, E.; Ungaro, D.; et al. Irradiation effects in electronic components of the RPC Trigger for the CMS Experiment. In Proceedings of the 12th IEEE-SPIE Symposium on Photonics and Web Engineering, Wilga, Poland, 21–25 May 2003. [Google Scholar] [CrossRef]

- Marek, T.; Novotny, M.; Crha, L. Design and implementation of the memory scheduler for the PC-based router. FIELD-Program. Log. Appl. Proc. 2004, 3203, 1133–1135. [Google Scholar]

- Park, S.H.; An, J.S.; Tae-Seok, O.; Kim, I.H. Design of high speed camera based on cmos technology - art. no. 679414. In Proceedings of the 4th International Conference on Metronics and Information Technology (ICMIT 2007), Gifu, Japan, 5–6 December 2007. [Google Scholar]

- Osmanis, K.; Valters, G.; Osmanis, I. 3D Volumetric Display Design Challenges. In Proceedings of the NORCHIP Conference, Vilnius, Lithuania, 11–12 November 2013. [Google Scholar]

- Singla, D.; Sachdeva, M.; Malhotra, D.; Singh, H. Thermal and energy efficient RAM design on 28 nm for electronic devices. Indian J. Sci. Technol. 2016, 9. [Google Scholar] [CrossRef]

- Kalia, K.; Pandey, B.; Hussain, D.M.A. SSTL Based Thermal and Power Efficient RAM Design on 28nm FPGA for Spacecraft. In Proceedings of the 6th International Conference on Smart Grid and Clean Energy Technologies (ICSGCE), Chengdu, China, 19–22 October 2016. [Google Scholar]

- Gandhi, J.; Ang, B.; Lee, T.; Liu, H.; Kim, M.; Lee, H.; Refai-Ahmed, G.; Shi, H.; Ramalingam, S. 2.5D FPGA-HBM integration challenges. Adv. Microelectron. 2017, 44, 12–16. [Google Scholar] [CrossRef]

- Meixner, A.; Kakizawa, A.; Provost, B.; Bedwani, S. External Loopback Testing Experiences with High Speed Serial Interfaces. In Proceedings of the 2008 IEEE International Test Conference, Santa Clara, CA, USA, 28–30 October 2008. [Google Scholar] [CrossRef]

- Kono, M.; Kanbe, A.; Toyoda, H. A 400-Gb/s and Low-power Physical-layer Architecture for Next-generation Ethernet. In Proceedings of the IEEE International Conference on Communications (ICC), Kyoto, Japan, 5–9 June 2011. [Google Scholar]

- Kono, M.; Kanbe, A.; Toyoda, H.; Nishimura, S. A Novel 400-Gb/s (100-Gb/s x 4) Physical-Layer Architecture Using Low-Power Technology. IEICE Trans. Commun. 2012, E95B, 3437–3444. [Google Scholar] [CrossRef]

- Jansweijer, P.P.M.; Peek, H.Z. Measuring propagation delay over a coded serial communication channel using FPGAs. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2011, 626, S169–S172. [Google Scholar] [CrossRef]

- Exel, R.; Bigler, T.; Sauter, T. Asymmetry Mitigation in IEEE 802.3 Ethernet for High-Accuracy Clock Synchronization. IEEE Trans. Instrum. Meas. 2014, 63, 729–736. [Google Scholar] [CrossRef]

- Freire, I.; Sousa, I.; Klautau, A.; Almeida, I.; Lu, C.; Berg, M. Analysis and Evaluation of End-to-End PTP Synchronization for Ethernet-based Fronthaul. In Proceedings of the 59th Annual IEEE Global Communications Conference (IEEE GLOBECOM), Washington, DC, USA, 4–8 December 2016. [Google Scholar]

- Cho, J.H.; Kim, H.; Yoon, C.H.; Cho, S.; Lee, T.J. Ethernet transport system supporting delay-sensitive real-time traffics. Int. J. Commun. Syst. 2014, 27, 2366–2376. [Google Scholar] [CrossRef]

- Ademaj, A.; Kopetz, H. Time-triggered Ethernet and IEEE 1588 clock synchronization. In Proceedings of the IEEE International Symposium on Precision Clock Synchronization for Measurement, Control and Communication, Vienna, Austria, 1–3 October 2007; pp. 41–43. [Google Scholar] [CrossRef]

- Bai, J.; Wu, L.; Yun, N.; Liu, Y.; Zhang, X. A 10Gbps In-line Network Security Processor with a 32-bit Embedded CPU. In Proceedings of the 22nd Wireless and Optical Communications Conference (WOCC), Chongqing, China, 16–18 May 2013. [Google Scholar]

- Niu, Y.; Wu, L.; Wang, L.; Zhang, X.; Xu, J. A configurable IPSec processor for high performance in-line security network processor. In Proceedings of the 2011 7th International Conference on Computational Intelligence and Security, CIS 2011, Sanya, China, 3–4 December 2011. [Google Scholar] [CrossRef]

- Haene, S.; Perels, D.; Burg, A. A real-time 4-stream MIMO-OFDM transceiver: System design, FPGA implementation, and characterization. IEEE J. Sel. Areas Commun. 2008, 26, 877–889. [Google Scholar] [CrossRef]

- Iacono, D.; Ronchi, M.; Torre, L.; Osnato, F. MIMO OFDM Physical layer real-time prototyping. In Proceedings of the IEEE Wireless Communications and Networking Conference, WCNC 2008, Las Vegas, NV, USA, 31 March–3 April 2008. [Google Scholar]

- Park, J.S.; Ogunfunmi, T. Efficient FPGA-Based Implementations of MIMO-OFDM Physical Layer. Circuits Syst. Signal Process. 2012, 31, 1487–1511. [Google Scholar] [CrossRef]

- Park, J.S.; Ogunfunmi, T. FPGA implementation of Channel Estimation for MIMO-OFDM. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011. [Google Scholar]

- Vincent, H.M.J.; Dahmane, A.; Moussa, S.; D’Amours, C. Rapid prototyping of channel estimation techniques in MIMO-OFDM systems. In Proceedings of the 2013 6th Joint IFIP Wireless and Mobile Networking Conference, WMNC 2013, Dubai, UAE, 23–25 April 2013. [Google Scholar] [CrossRef]

- Sudhakar, R.P.; Ramachandra, R.R. Design and FPGA implementation of channel estimation method and modulation technique for MIMO system. Eur. J. Sci. Res. 2009, 25, 257–265. [Google Scholar]

- Zhang, H.; Zhao, J. The design of RF data acquisition system based on STM32 and FPGA. In Proceedings of the 2nd International Conference on Multimedia Technology, ICMT 2011, Hangzhou, China, 26–28 July 2011. [Google Scholar] [CrossRef]

- Cabrini, A.; Gobbi, L.; Baderna, D.; Torelli, G. A compact low-cost test equipment for thermal and electrical characterization of integrated circuits. Measurement 2009, 42, 281–289. [Google Scholar] [CrossRef]

- Liu, J.; Niu, Y.; Dong, W.; Si, B.; Liu, J. Design and application of video signal generator based on FPGA. Yi Qi Yi Biao Xue Bao/Chin. J. Sci. Instrum. 2008, 29, 654–657. [Google Scholar]

- Wen, F.; Xia, L.; Liang, F.; Dong, J.; Wang, Q.; Jin, G. Development of lidar data acquisition system for visibility measurement. Hongwai Yu Jiguang Gongcheng/Infrared Laser Eng. 2011, 40, 52–56. [Google Scholar]

- Huixin, Z.; Qi, H.; Suhua, L.; Haiguang, Y. The design for LVDS high-speed data acquisition and transmission system based on FPGA. In Proceedings of the 2011 IEEE 3rd International Conference on Communication Software and Networks, ICCSN 2011, Xi’an, China, 27–29 May 2011. [Google Scholar] [CrossRef]

- Wang, A.; Li, Z.; Yang, X.; Feng, B. A new security problem of USB: Monitoring cable attack and countermeasures. In Proceedings of the 2012 International Conference on Information Technology and Software Engineering, ITSE 2012, Beijing, China, 8–10 December 2012. [Google Scholar] [CrossRef]

- Yang, X.; Li, Z.; Wang, A.; Zhang, Y. System design of cryptographic security USB device controller IP core. Huazhong Keji Daxue Xuebao (Ziran Kexue Ban)/J. Huazhong Univ. Sci. Technol. (Nat. Sci. Ed.) 2010, 38, 59–62. [Google Scholar]

- Yang, Y.T.; Zhang, S.T.; Li, Z.C.; Zhang, M.D.; Cao, G.C. Design and Implementation for High Speed Data Transfer Interface of PCI Express Based on Zynq Platform. Dianzi Keji Daxue Xuebao/J. Univ. Electron. Sci. Technol. China 2017, 46, 522–528. [Google Scholar] [CrossRef]

- Byszuka, A.; Pozniak, K.; Zabolotny, W.M.; Kasprowicz, G.; Wojenski, A.; Cieszewski, R.; Juszczyk, B.; Kolasinski, P.; Zienkiewicz, P.; Chernyshova, M.; et al. Fast data transmission in dynamic data acquisition system for plasma diagnostics. In Proceedings of the Conference on Photonics Applications in Astronomy, Communications, Industry, and High-Energy Physics Experiments, Wilga, Poland, 26 May–1 June 2014. [Google Scholar] [CrossRef]

- Bittner, R.; Ruf, E.; Forin, A. Direct GPU/FPGA communication Via PCI express. Clust.-Comput. J. Netw. Softw. Tools Appl. 2014, 17, 339–348. [Google Scholar] [CrossRef]

- Thoma, Y.; Dassatti, A.; Molla, D.; Petraglio, E. FPGA-GPU communicating through PCIe. Microprocess. Microsyst. 2015, 39, 565–575. [Google Scholar] [CrossRef]

- Wu, A.; Jin, X.; Guo, S.; Du, X. A Flexible FPGA-to-FPGA Interconnect Interface Design and Implementation. In Proceedings of the International Conference on Computers, Communications and Systems (ICCCS), Kanyakumari, India, 2–3 November 2015. [Google Scholar]

- An, W.; Jin, X.; Du, X.; Guo, S. A Flexible FPGA-to-FPGA Communication System. In Proceedings of the 18th International Conference on Advanced Communication Technology (ICACT), Pyeongchang, Korea, 31 Janrary–3 February 2016. [Google Scholar]

- Bono, S.; Green, M.; Stubblefield, A.; Juels, A.; Rubin, A.; Szydlo, M. Security analysis of a cryptographically-enabled RFID device. In Proceedings of the 14th USENIX Security Symposium, Baltimore, MD, USA, 31 July–5 August 2005. [Google Scholar]

- Kavun, E.B.; Yalcin, T. A Lightweight Implementation of Keccak Hash Function for Radio-Frequency Identification Applications. In Proceedings of the 6th Workshop on Radio Frequency Identification Security, Istanbul, Turkey, 8–9 June 2010. [Google Scholar]

- Fu, L.; Shen, X.; Zhu, L.; Wang, J. A low-cost UHF RFID tag chip with AES cryptography engine. Secur. Commun. Netw. 2014, 7, 365–375. [Google Scholar] [CrossRef]

- Fang, Y.Y.; Chen, X.J. Design and simulation of UART serial communication module based on VHDL. In Proceedings of the 2011 3rd International Workshop on Intelligent Systems and Applications, ISA 2011, Wuhan, China, 28–29 May 2011. [Google Scholar] [CrossRef]

- Ali, L.; Sidek, R.; Aris, I.; Ali, A.; Suparjo, B. Design of a micro-UART for SoC application. Comput. Electr. Eng. 2004, 30, 257–268. [Google Scholar] [CrossRef]

- Wakhle, G.; Aggarwal, I.; Gaba, S. Synthesis and implementation of UART using VHDL codes. In Proceedings of the 2012 International Symposium on Computer, Consumer and Control, IS3C 2012, Taichung, Taiwan, 4–6 June 2012. [Google Scholar] [CrossRef]

- Kammerer, R.; Obermaisser, R.; Fromel, B. A router for the containment of timing and value failures in CAN. Eurasip J. Embed. Syst. 2012, 2012. [Google Scholar] [CrossRef]

- Lee, T.Y.; Kuo, C.W.; Lin, I.A. High Performance CAN/FlexRay Gateway Design for In-Vehicle Network. In Proceedings of the IEEE Conference on Dependable and Secure Computing, Taipei, Taiwan, 7–10 August 2017. [Google Scholar]

- Mellal, I.; Laghrouche, M.; Bui, H.T. Field Programmable Gate Array (FPGA) Respiratory Monitoring System Using a Flow Microsensor and an Accelerometer. Meas. Sci. Rev. 2017, 17, 61–67. [Google Scholar] [CrossRef][Green Version]

- Kumari, R.S.S.; Gayathri, C. Interfacing of mems motion sensor with fpga using 12c protocol. In Proceedings of the International Conference on Innovations in Information, Embedded and Communication Systems (ICIIECS), Coimbatore, India, 17–18 March 2017. [Google Scholar]

- Feng, Z.; Qinzhang, W.; Guoqiang, R. A High-speed Method of CCD Image Data Storage System. In Proceedings of the 2nd IEEE International Conference on Advanced Computer Control, Shenyang, China, 27–29 March 2010. [Google Scholar] [CrossRef]

- Zhang, F.; Wu, Q.; Ren, G. A high-speed method of CCD image data storage system based on SATA. Bandaoti Guangdian/Semicond. Optoelectron. 2010, 31, 782–786. [Google Scholar]

- Wu, Q.; Song, T.; Li, X. Research on the High-Speed Image Acquisition and Storage Technology based on TMS320C6748. In Proceedings of the 4th National Conference on Electrical, Electronics and Computer Engineering (NCEECE), Xi’an, China, 12–13 December 2015. [Google Scholar]

- Dillinger, M.; Madani, K.; Alonistioti, N. Software Defined Radio: Architectures, Systems and Functions; Wiley Series in Software Radio; Wiley: Hoboken, NJ, USA, 2005. [Google Scholar]

- Garcia, J.; Cumplido, R. On the design of an FPGA-based OFDM modulator for IEEE 802.11a. In Proceedings of the 2nd International Conference on Electrical and Electronics Engineering (ICEEE 2005), Mexico City, Mexico, 7–9 September 2005. [Google Scholar] [CrossRef]

- Garcia, J.; Cumplido, R. On the design of an FPGA-based OFDM modulator for IEEE 802.16-2004. In Proceedings of the International Conference on Reconfigurable Computing and FPGAs, Puebla, Mexico, 28–30 September 2005. [Google Scholar]

- Bluemm, C.; Heller, C.; Weigel, R. SDR OFDM Waveform Design for a UGV/UAV Communication Scenario. J. Signal Process. Syst. Signal Image Video Technol. 2012, 69, 11–21. [Google Scholar] [CrossRef]

- Zhang, B.; Guo, X. A Novel Reconfigurable Architecture for Generic OFDM Modulator Based on FPGA. In Proceedings of the 16th International Conference on Advanced Communication Technology (ICACT), Pyeongchang, Korea, 16–19 February 2014. [Google Scholar]

- Ribeiro, C.; Gameiro, A. A software-defined radio FPGA implementation of OFDM-based PHY transceiver for 5G. Analog. Integr. Circuits Signal Process. 2017, 91, 343–351. [Google Scholar] [CrossRef]

- Al Safi, A.; Bazuin, B. FPGA Based Implementation of BPSK and QPSK Modulators using Address Reverse Accumulators. In Proceedings of the 7th IEEE Annual Ubiquitous Computing, Electronics and Mobile Communication Conference (IEEE UEMCON), New York, NY, USA, 20–22 October 2016. [Google Scholar]

- Nivin, R.; Rani, J.S.; Vidhya, P. Design and Hardware Implementation of Reconfigurable Nano Satellite Communication System Using FPGA Based SDR for FM/ FSK Demodulation and BPSK Modulation. In Proceedings of the International Conference on Communication Systems and Networks (ComNet), Trivandrum, India, 21–23 July 2016. [Google Scholar]

- Kazaz, T.; Kulin, M.; Hadzialic, M. Design and Implementation of SDR Based QPSK Modulator on FPGA. In Proceedings of the 36th International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO), Opatija, Croatia, 20–24 May 2013. [Google Scholar]

- Jakubov, O.; Kovar, P.; Kacmarik, P.; Vejrazka, F. The Witch Navigator - A Low Cost GNSS Software Receiver for Advanced Processing Techniques. Radioengineering 2010, 19, 536–543. [Google Scholar]

- Kovar, P.; Vejrazka, F. Software radio and its applications in GNSS. In Proceedings of the 46th International Symposium Electronics in Marine (ELMAR-2004), Zadar, Croatia, 16–18 June 2004. [Google Scholar]

- Puricer, P.; Kovar, P.; Seidl, L.; Vejrazka, F. GNSS software receiver—A versatile platform for navigation systems signals processing. In Proceedings of the 47th International Symposium ELMAR-2005 on Multimedia Systems and Applications, Zadar, Croatia, 8–10 June 2005. [Google Scholar]

- Raju, K.; Pratap, Y.; Patel, V.; Kumar, G.; Naidu, S.; Patwardhan, A.; Henry, R.; Bhanu, P.P. Implementation of multichannel GPS receiver baseband modules. In Proceedings of the 2nd International Conference on Computer Science, Engineering and Applications, ICCSEA 2012, New Delhi, India, 25–27 May 2012. [Google Scholar] [CrossRef]

- Mohamed, K.E.; Ali, B.M.; Jamuar, S.S.; Khatun, S.; Ismail, A. A software defined radio approach for digital CDMA transmitter. In Proceedings of the 4th International Conference on Cybernetics and Information Technologies, Systems and Applications/5th Int Conf on Computing, Communications and Control Technologies, Orlando, FL, USA, 12–15 July 2007. [Google Scholar]

- Al Safi, A.; Bazuin, B. Toward Digital Transmitters with Amplitude Shift Keying and Quadrature Amplitude Modulators Implementation Examples. In Proceedings of the 7th IEEE Annual Computing and Communication Workshop and Conference (IEEE CCWC), Las Vegas, NV, USA, 9–11 January 2017. [Google Scholar]

- Kumar, A.K.A. FPGA Implementation of QAM Modems Using PR for Reconfigurable Wireless Radios. In Proceedings of the Annual International Conference on Emerging Research Areas (AICERA) / International Conference on Microelectronics, Communication and Renewable Energy (ICMiCR), Kanjirapally, India, 4–6 June 2013. [Google Scholar]

- Khan, M.A.; Ansari, A.Q. Design of 8-Bit Programmable Crossbar Switch for Network-on-Chip Router. In Proceedings of the 4th International Conference on Network Security and Applications (CNSA 2011), Chennai, India, 15–17 July 2011. [Google Scholar]

- Karadeniz, T.; Mhamdi, L.; Goossens, K.; Garcia-Luna-Aceves, J.J. Hardware Design and Implementation of a Network-on-Chip Based Load Balancing Switch Fabric. In Proceedings of the International Conference on Reconfigurable Computing and FPGAs (ReConFig), Cancun, Mexico, 5–7 December 2012. [Google Scholar]

- Sharma, R.; Joshi, V.; Rohokale, V. Performance of router design for Network-on-Chip implementation. In Proceedings of the 2012 International Conference on Communication, Information and Computing Technology, ICCICT 2012, Mumbai, India, 19–20 October 2012. [Google Scholar] [CrossRef]

- Bayar, S.; Yurdakul, A. An Efficient Mapping Algorithm on 2-D Mesh Network-on-Chip with Reconfigurable Switches. In Proceedings of the 11th IEEE International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Istanbul, Turkey, 12–14 April 2016. [Google Scholar]

- Bansal, S.; Sharma, S.; Sharma, N. Design of Configurable Power Efficient 2-Dimensional Crossbar Switch For Network-on-Chip(NoC). In Proceedings of the IEEE International Conference on Recent Trends in Electronics, Information and Communication Technology (RTEICT), Bengaluru, India, 20–21 May 2016. [Google Scholar]

- Bansal, S.; Sharma, S.; Sharma, N. Design of Configurable Power Efficient 3-Dimensional Crossbar Switch For Network-on-Chip(NoC). In Proceedings of the 2nd International Conference on Advances in Computing, Communication, and Automation (ICACCA) (Fall), Bareilly, India, 30 September–1 October 2016. [Google Scholar]

- Khan, M.; Ansari, A. N-Bit multiple read and write FIFO memory model for network-on-chip. In Proceedings of the 2011 World Congress on Information and Communication Technologies, WICT 2011, Mumbai, India, 11–14 December 2011. [Google Scholar] [CrossRef]

- Ortega-Cisneros, S.; Cabrera-Villasenor, H.J.; Raygoza-Panduro, J.J.; Sandoval, F.; Loo-Yau, R. Hardware and Software Co-design: An Architecture Proposal for a Network-on-Chip Switch based on Buffer less Data Flow. J. Appl. Res. Technol. 2014, 12, 153–163. [Google Scholar] [CrossRef]

- Elhajji, M.; Attia, B.; Zitouni, A.; Tourki, R.; Meftali, S.; Dekeyser, J.L. FeRoNoC: Flexible and extensible router implementation for diagonal mesh topology. In Proceedings of the 2011 Conference on Design and Architectures for Signal and Image Processing, DASIP 2011, Tampere, Finland, 2–4 November 2011. [Google Scholar] [CrossRef]

- Zakaria, F.F.; Latif, N.A.A.; Hashim, S.J.; Ehkan, P.; Rokhani, F.Z. Cooperative Virtual Channel Router for Adaptive Hardwired FPGA Network-on-Chip. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Jeju, Korea, 25–28 October 2016. [Google Scholar]

- Kamal, R.; Moreno Arostegui, J.M. Design and Analysis of DMA based Network Interface for NoC’s Router. In Proceedings of the IEEE International Conference on Recent Trends in Electronics, Information and Communication Technology (RTEICT), Bengaluru, India, 20–21 May 2016. [Google Scholar]

- Jayan, G.; Pavitha, P.P. FPGA Implementation of an Efficient Router Architecture Based on DMC. In Proceedings of the IEEE International Conference on Emerging Technological Trends in Computing, Communications and Electrical Engineering (ICETT), Sasthancotta, India, 21–22 October 2016. [Google Scholar]

- Kashwan, K.R.; Selvaraj, G. Implementation and Performance Analyses of a Novel Optimized NoC Router. In Proceedings of the International Conference for Convergence of Technology (I2CT), Pune, India, 6–8 April 2014. [Google Scholar]

- Shahane, P.; Pisharoty, N. Implementation of input block of minimally buffered deflection NoC Router. Int. J. Eng. Technol. 2016, 8, 1796–1800. [Google Scholar] [CrossRef][Green Version]

- Kamali, H.M.; Hessabi, S. AdapNoC: A Fast and Flexible FPGA-based NoC Simulator. In Proceedings of the 26th International Conference on Field-Programmable Logic and Applications (FPL), Lausanne, Switzerland, 29 August–2 September 2016. [Google Scholar] [CrossRef]

- Sanju, V.; Koushika, C.; Sharmili, R.; Chiplunkar, N.; Khalid, M. Design and implementation of a network on chip-based simulator: A performance study. Int. J. Comput. Sci. Eng. 2014, 9, 95–105. [Google Scholar] [CrossRef]

- Killian, C.; Tanougast, C.; Monteiro, M.; Diou, C.; Dandache, A.; Jovanovic, S. Behavioral modeling and C-VHDL co-simulation of network on chip on FPGA for education. In Proceedings of the 5th International Workshop on Reconfigurable Communication-Centric Systems on Chip 2010, ReCoSoC 2010, Karlsruhe, Germany, 17–19 May 2010. [Google Scholar]

- Venkateswaran, R.; Mazumder, P. A survey of da techniques for pld and fpga based systems. Integr. VLSI J. 1994, 17, 191–240. [Google Scholar] [CrossRef][Green Version]

- Lockwood, J.; Naufel, N.; Turner, J.; Taylor, D. Reprogrammable network packet processing on the Field Programmabl Port Extender (FPX). In Proceedings of the 2001 ACM/SIGDA 9th International Sysmposium on Field Programmable Gate Arrays (FPGA 2001), Monterrey, CA, USA, 11–13 February 2001. [Google Scholar]

- Braun, F.; Lockwood, J.; Waldvogel, M. Layered protocol wrappers for Internet packet processing in reconfigurable hardware. In Proceedings of the HOT 9 Interconnects. Symposium on High Performance Interconnects, Stanford, CA, USA, 22–24 August 2001. [Google Scholar] [CrossRef]

- Zhang, Y.; Lan, J.L.; Hu, Y.X.; Wang, P.; Duan, T. A polymorphic routing system providing flexible customization for service. Tien Tzu Hsueh Pao/Acta Electron. Sin. 2016, 44, 988–994. [Google Scholar] [CrossRef]

- Kwon, A.; Zhang, K.; Lim, P.; Pan, Y.; Smith, J.; Dehon, A. RotoRouter: Router support for endpoint-authorized decentralized traffic filtering to prevent DoS attacks. In Proceedings of the 2014 International Conference on Field-Programmable Technology (FPT), Shanghai, China, 10–12 December 2014. [Google Scholar] [CrossRef]

- Gibb, G.; Lockwood, J.W.; Naous, J.; Hartke, P.; McKeown, N. NetFPGA—An open platform for teaching how to build gigabit-rate network switches and routers. IEEE Trans. Educ. 2008, 51, 364–369. [Google Scholar] [CrossRef]

- Chan, P.; Schlag, M.; Ebeling, C.; McMurchie, L. Distributed-memory parallel routing for field-programmable gate arrays. IEEE Trans.-Comput.-Aided Des. Integr. Circuits Syst. 2000, 19, 850–862. [Google Scholar] [CrossRef]

- Moctar, Y.O.M.; Brisk, P. Parallel FPGA Routing based on the Operator Formulation. 51st ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 1–5 June 2014. [Google Scholar] [CrossRef]

- Gort, M.; Anderson, J.H. Accelerating FPGA Routing Through Parallelization and Engineering Enhancements Special Section on PAR-CAD 2010. IEEE Trans.-Comput.-Aided Des. Integr. Circuits Syst. 2012, 31, 61–74. [Google Scholar] [CrossRef]

- Muthukaruppan, A.; Suresh, S.; Kamakoti, V. A novel three phase parallel genetic approach to routing for field programmable gate arrays. In Proceedings of the IEEE International Conference on Field-Programmable Technology (FPT), Hong Kong, China, 16–18 December 2002. [Google Scholar] [CrossRef]

- Fatima, K.; Rao, R. FPGA Implementation of a New Parallel Routing Algorithm. In Proceedings of the IEEE Region 10 Conference (TENCON 2008), Hyderabad, India, 19–21 November 2008. [Google Scholar]

- D’Hollander, E.H.; Stroobandt, D.; Touhafi, A. ParaFPGA 2013: Harnessing Programs, Power and Performance in Parallel FPGA applications. In Proceedings of the International Conference on Parallel Programming (ParCo), Garching, Germany, 10–13 September 2013. [Google Scholar] [CrossRef]

- Mitola, J.; Maguire, G.Q. Cognitive radio: making software radios more personal. IEEE Pers. Commun. 1999, 6, 13–18. [Google Scholar] [CrossRef]

- Kosunen, M.; Turunen, V.; Kokkinen, K.; Ryynanen, J. Survey and Analysis of Cyclostationary Signal Detector Implementations on FPGA. IEEE J. Emerg. Sel. Top. Circuits Syst. 2013, 3, 541–551. [Google Scholar] [CrossRef]

- Srinu, S.; Sabat, S. FPGA implementation of spectrum sensing based on energy detection for cognitive radio. In Proceedings of the 2010 IEEE International Conference on Communication Control and Computing Technologies, ICCCCT 2010, Tamil Nadu, India, 7–9 October 2010. [Google Scholar] [CrossRef]

- Chaitanya, G.; Rajalakshmi, P.; Desai, U. Real time hardware implementable spectrum sensor for cognitive radio applications. In Proceedings of the 2012 9th International Conference on Signal Processing and Communications, SPCOM 2012, Bangalore, India, 22–25 July 2012. [Google Scholar] [CrossRef]

- Nguyen, T.T.; Dang, K.L.; Nguyen, H.V.; Nguyen, P.H. A Real-Time FPGA Implementation of Spectrum Sensing Applying for DVB-T Primary Signal. In Proceedings of the International Conference on Advanced Technologies for Communications (ATC), Ho Chi Minh City, Vietnam, 16–18 October 2013. [Google Scholar]

- Wen, Z.; Meng, Z.; Wang, Q.; Liu, L.; Zou, J.; Wang, L. An FPGA real-time spectrum sensing for cognitive radio in very high throughput WLAN. In Proceedings of the Joint International Conference on Pervasive Computing and the Networked World, ICPCA/SWS 2012, Istanbul, Turkey, 28–30 November 2012. [Google Scholar] [CrossRef]

- Hanninen, T.; Vartiainen, J.; Juntti, M.; Raustia, M. Implementation of spectrum sensing on wireless open-access research platform. In Proceedings of the 2010 3rd International Symposium on Applied Sciences in Biomedical and Communication Technologies, ISABEL 2010, Roma, Italy, 7–10 November 2010. [Google Scholar] [CrossRef]

- Kyperountas, S.; Shi, Q.; Vallejo, A.; Correal, N. A MultiTaper Hardware Core for Spectrum Sensing. In Proceedings of the IEEE International Symposium on Dynamic Spectrum Access Networks, Bellevue, WA, USA, 16–19 October 2012. [Google Scholar]

- Recio, A.; Athanas, P. Physical Layer for Spectrum-Aware Reconfigurable OFDM on an FPGA. In Proceedings of the 13th Euromicro Conference on Digital System Design on Architectures, Methods and Tools, Lille, France, 1–3 September 2010. [Google Scholar] [CrossRef]

- Ishwerya, P.; Geethu, S.; Lakshminarayanan, G. An Efficient Hybrid Spectrum Sensing Architecture on FPGA. In Proceedings of the 2nd IEEE International Conference on Wireless Communications, Signal Processing and Networking (WiSPNET), Chennai, India, 22–24 March 2017. [Google Scholar]

- Omara, M.O.S.; Suratman, F.Y.; Astuti, R.P. An FPGA Testbed for Spectrum Sensing in Cognitive Radio. In Proceedings of the IEEE Asia Pacific Conference on Wireless and Mobile (APWiMob), Bandung, Indonesia, 28–29 November 2017. [Google Scholar]

- Shreejith, S.; Mathew, L.K.; Prasad, V.A.; Fahmy, S.A. Efficient Spectrum Sensing for Aeronautical LDACS Using Low-Power Correlators. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 1183–1191. [Google Scholar] [CrossRef]

- Sramek, P.; Povalac, K.; Marsalek, R. Experimental evaluation of radio frequency spectrum sensing detectors in tv bands. In Proceedings of the International Conference on Signal Processing and Multimedia Application (SIGMAP 2010), Athens, Greece, 26–28 July 2010. [Google Scholar]

- Sunil, D.; Sabat, S. Spectrum sensing using envelope tracking and signal moment. In Proceedings of the 2016 International Conference on Signal Processing and Communication, ICSC 2016, Noida, India, 26–28 December 2016. [Google Scholar] [CrossRef]

- Murty, M.S.; Shrestha, R. Hardware-Efficient and Wide-Band Frequency-Domain Energy Detector for Cognitive-Radio Wireless Network. In Proceedings of the 31st International Conference on VLSI Design/17th International Conference on Embedded Systems (VLSID & ES), Pune, India, 6–10 January 2018; pp. 277–282. [Google Scholar] [CrossRef]

- Costantine, J.; Tawk, Y.; Barbin, S.E.; Christodoulou, C.G. Reconfigurable Antennas: Design and Applications. Proc. IEEE 2015, 103, 424–437. [Google Scholar] [CrossRef]

- Manoj, S.; Kothari, A. Reconfigurable planar inverted F antenna for cognitive radio & mobile systems. In Proceedings of the 2015 5th International Workshop on Computer Science and Engineering: Information Processing and Control Engineering, Moscow, Russia, 15–17 April 2015. [Google Scholar]

- Raut, R.; Kulat, K. Software defined adaptive codec for cognitive radio. WSEAS Trans. Commun. 2009, 8, 1243–1252. [Google Scholar]

- Golbon-Haghighi, M.H. Beamforming in Wireless Networks. In Towards 5G Wireless Networks; Bizaki, H.K., Ed.; IntechOpen: Rijeka, Croatia, 2016; Chapter 8. [Google Scholar] [CrossRef]

- Sengupta, A.; Madanayake, A.; Gomez-Garcia, R.; Engeberg, E.D. Wideband Aperture Array using RF Channelizers and Massively-Parallel Digital 2-D IIR Filterbank. In Proceedings of the Conference on Radar Sensor Technology XVIII, Baltimore, MD, USA, 5–7 May 2014. [Google Scholar] [CrossRef]

- Seneviratne, V.; Madanayake, A.; Bruton, L.T. A 480MHz ROACH-2 FPGA Realization of 2-Phase 2-D IIR Beam Filters for Digital RF Apertures. In Proceedings of the Moratuwa Engineering Research Conference (MERCon), Moratuwa, Sri Lanka, 5–6 April 2016. [Google Scholar]

- Thiripurasundari, C.; Sumathy, V.; Thiruvengadam, C. An FPGA implementation of novel smart antenna algorithm in tracking systems for smart cities. Comput. Electr. Eng. 2018, 65, 59–66. [Google Scholar] [CrossRef]

- Kee, H.; Bhattacharyya, S.S.; Wong, I.; Rao, Y. FPGA-based design and implementation of the 3gpp-lte physical layer using parameterized synchronous dataflow techniques. In Proceedings of the 2010 IEEE International Conference on Acoustics, Speech, and Signal Processing, Dallas, TX, USA, 10–19 March 2010. [Google Scholar] [CrossRef]

- Sleiman, S.; Ismail, M. Multimode Reconfigurable digital sd modulator architecture for fractional-N PLLs. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 592–596. [Google Scholar] [CrossRef]

- Abbas, S.; Sheeba, P.; Thiruvengadam, S. Design of downlink PDSCH architecture for LTE using FPGA. In Proceedings of the International Conference on Recent Trends in Information Technology, ICRTIT 2011, Chennai, India, 3–5 June 2011. [Google Scholar] [CrossRef]

- Abbas, S.S.A.; Thiruvengadam, S.J.; Punitha, M. Realization of PDSCH Transmitter and Receiver Architecture for 3GPP-LTE Advanced. In Proceedings of the IEEE International Conference on Wireless Communications, Signal Processing and Networking (WiSPNET), Chennai, India, 23–25 March 2016. [Google Scholar]

- Syed, A.A.S.; Geethu, K.; Thiruvengadam, S. Implementation of Physical Downlink Control Channel (PDCCH) for LTE using FPGA. In Proceedings of the 2012 International Conference on Devices, Circuits and Systems, ICDCS 2012, Coimbatore, India, 15–16 March 2012. [Google Scholar] [CrossRef]

- Chen, F.; Zheng, W.; Lv, N. FPGA implementation of PDCCH blind detection algorithm in TD-LTE. In Proceedings of the 2014 International Conference on Materials Science and Computational Engineering, ICMSCE 2014, Qingdao, China, 20–21 May 2014. [Google Scholar] [CrossRef]

- Adiono, T.; Mareta, R. Low Latency Parallel-Pipelined Configurable FFT-IFFT 128/256/512/1024/2048 for LTE. In Proceedings of the 4th International Conference on Intelligent and Advanced Systems (ICIAS) and A Conference of World Engineering, Science and Technology Congress (ESTCON), Kuala Lumpur, Malaysia, 12–14 June 2012. [Google Scholar]

- Nash, J.G. Distributed-Memory-Based FFT Architecture and FPGA Implementations. Electronics 2018, 7, 116. [Google Scholar] [CrossRef]

- Ayhan, T.; Dehaene, W.; Verhelst, M. A 128 similar to 2048/1536 point fft hardware implementation with output pruning. In Proceedings of the 22nd European Signal Processing Conference (EUSIPCO), Lisbon, Portugal, 1–5 September 2014. [Google Scholar]

- Tran, M.T.; Casseau, E.; Gautier, M. Demo abstract: FPGA-based implementation of a flexible FFT dedicated to LTE standard. In Proceedings of the Conference on Design and Architectures for Signal and Image Processing (DASIP), Rennes, France, 12–14 October 2016. [Google Scholar]

- Jiang, W.; Prasanna, V.K. Scalable Packet Classification on FPGA. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2012, 20, 1668–1680. [Google Scholar] [CrossRef]

- Fong, J.; Wang, X.; Qi, Y.; Li, J.; Jiang, W. ParaSplit: A scalable architecture on FPGA for Terabit packet classification. In Proceedings of the 2012 IEEE 20th Annual Symposium on High-Performance Interconnects, HOTI 2012, Santa Clara, CA, USA, 22–24 August 2012. [Google Scholar] [CrossRef]

- Qi, Y.; Fong, J.; Jiang, W.; Xu, B.; Li, J.; Prasanna, V. Multi-dimensional packet classification on FPGA: 100 Gbps and beyond. In Proceedings of the 2010 International Conference on Field-Programmable Technology, FPT’10, Beijing, China, 8–10 December 2010. [Google Scholar] [CrossRef]

- Qu, Y.R.; Prasanna, V.K. High-Performance and Dynamically Updatable Packet Classification Engine on FPGA. IEEE Trans. Parallel Distrib. Syst. 2016, 27, 197–209. [Google Scholar] [CrossRef]

- Jiang, W.; Prasanna, V.K. A FPGA-based Parallel Architecture for Scalable High-Speed Packet Classification. In Proceedings of the 20th IEEE International Conference on Application-Specific Systems, Architectures and Processors, Boston, MA, USA, 7–9 July 2009. [Google Scholar] [CrossRef]

- Fiesslert, A.; Hager, S.; Scheuermannt, B.; Moore, A.W. HyPaFilter—A Versatile Hybrid FPGA Packet Filter. In Proceedings of the 12th ACM/IEEE Symposium on Architectures for Networking and Communications Systems (ANCS), Santa Clara, CA, USA, 17–18 March 2016. [Google Scholar] [CrossRef]

- Fiessler, A.; Lorenz, C.; Hager, S.; Scheuermann, B.; Moore, A. HyPaFilter: Enhanced Hybrid Packet Filtering Using Hardware Assisted Classification and Header Space Analysis. IEEE/ACM Trans. Netw. 2017, 25, 3655–3669. [Google Scholar] [CrossRef]

- Antichi, G.; Di Pietro, A.; Giordano, S.; Procissi, G.; Ficara, D. Design and Development of an OpenFlow Compliant Smart Gigabit Switch. In Proceedings of the 54th Annual IEEE Global Telecommunications Conference (GLOBECOM), Houston, TX, USA, 5–9 December 2011. [Google Scholar]

- Farahani, S. ZigBee Wireless Networks and Transceivers; Elsevier Science: New York, NY, USA, 2011. [Google Scholar]

- Deep, V.; Elarabi, T. Efficient IEEE 802.15.4 ZigBee standard hardware design for IoT applications. In Proceedings of the 1st IEEE International Conference on Signals and Systems, ICSigSys 2017, Sanur, Indonesia, 16–18 May 2017. [Google Scholar] [CrossRef]

- Supare, V.P.; Sayankar, B.B.; Agrawal, P. Design & Implementation of MQAM based IEEE 802.15.4/ZigBee Tranceiver using HDL. In Proceedings of the International Conference on Smart Technologies and Management for Computing, Communication, Controls, Energy and Materials (ICSTM), Chennai, India, 6–8 May 2015. [Google Scholar]

- Li, S.; Li, W.; Zhu, J. A novel zigbee based high speed ad hoc communication network. In Proceedings of the IEEE International Conference on Network Infrastructure and Digital Content, Beijing, China, 6–8 November 2009. [Google Scholar]

- Ahmad, R.; Sidek, O.; Kunhi, M.S. Implementation of a Verilog-based digital receiver for 2.4 GHZ Zigbee applications on FPGA. J. Eng. Sci. Technol. 2014, 9, 135–152. [Google Scholar]

- Mohana, P.; Radha, S. Realization of MAC Layer Functions of ZigBee Protocol Stack in FPGA. In Proceedings of the International Conference on Control, Automation, Communication and Energy Conservation, Perundurai, India, 4–6 June 2009. [Google Scholar]

- Ottoy, G.; Hamelinckx, T.; Preneel, B.; De, S.L.; Goemaere, J.P. AES data encryption in a ZigBee network: Software or hardware? In Proceedings of the 2nd International ICST Conference on Security and Privacy in Mobile Information and Communication Systems, MobiSec 2010, Catania, Italy, 27–28 May 2010. [Google Scholar] [CrossRef]

- Ottoy, G.; Hamelinckx, T.; Preneel, B.; De Strycker, L.; Goemaere, J.P. On the choice of the appropriate AES data encryption method for ZigBee nodes. Secur. Commun. Netw. 2016, 9, 87–93. [Google Scholar] [CrossRef]

- Ahmad, R.; Kho, D.; Abd Manaf, A.; Ismail, W. Parallel-Pipelined-Memory-Based Blowfish Design with Reduced FPGA Utilization for Secure ZigBee Real-Time Transmission. Wirel. Pers. Commun. 2019, 104, 471–489. [Google Scholar] [CrossRef]

- Asif, S. 5G Mobile Communications: Concepts and Technologies; CRC Press: New York, NY, USA, 2018. [Google Scholar]

- Andrews, J.; Ghosh, A.; Muhamed, R. Fundamentals of WiMAX: Understanding Broadband Wireless Networking; Prentice Hall Press: Upper Saddle River, NJ, USA, 2011. [Google Scholar]

- Abba, S.; Khan, W.A.; Khan, T.A.; Ahmed, S. Implementation of OFDM Baseband Transmitter Compliant IEEE Std 802.16d on FPGA. In Proceedings of the 2nd International Conference on Communication Software and Networks, Singapore, 26–28 Feburary 2010. [Google Scholar] [CrossRef]

- Hadiyoso, S.; Astuti, R.P.; Hidayat, I. Design of an FPGA-Based OFDM-STBC Transceiver for WiMAX 802.16e Standard. In Proceedings of the 2nd International Conference on Information and Communication Technology (ICoICT), Bandung, Indonesia, 28–30 May 2014. [Google Scholar]

- Ahn, C.; Kim, J.; Ju, J.; Choi, J.; Choi, B.; Choi, S. Implementation of an SDR platform using GPU and its application to a 2 x 2 MIMO WiMAX system. Analog. Integr. Circuits Signal Process. 2011, 69, 107–117. [Google Scholar] [CrossRef]

- Suarez-Casal, P.; Carro-Lagoa, A.; Garcia-Naya, J.A.; Castedo, L. A Multicore SDR Architecture for Reconfigurable WiMAX Downlink. In Proceedings of the 13th Euromicro Conference on Digital System Design on Architectures, Methods and Tools, Lille, France, 1–3 September 2010. [Google Scholar] [CrossRef]

- Suarez-Casal, P.; Carro-Lagoa, A.; Garcia-Naya, J.A.; Fraga-Lamas, P.; Castedo, L.; Morales-Mendez, A. A Real-Time Implementation of the Mobile WiMAX ARQ and Physical Layer. J. Signal Process. Syst. Signal Image Video Technol. 2015, 78, 283–297. [Google Scholar] [CrossRef]

- Shaker, S.; Elramly, S.; Shehata, K. FPGA implementation of a reconfigurable Viterbi decoder for WiMAX receiver. In Proceedings of the 21th International Conference on Microelectronics, ICM 2009, Marrakech, Morocco, 19–22 December 2009. [Google Scholar] [CrossRef]

- Nandula, S.; Rao, Y.S.; Embanath, S.P. High speed area efficient configurable Viterbi decoder for WiFi and WiMAX systems. In Proceedings of the International Conference on Intelligent and Advanced Systems, Kuala Lumpur, Malaysia, 25–28 November 2007. [Google Scholar]

- Junjie, L.; June, T.; Yingning, P.; Jianwen, C. High Performance Viterbi Decoder on Cell/BE. China Commun. 2009, 6, 150–156. [Google Scholar]

- Benzekki, K.; El Fergougui, A.; Elbelrhiti Elalaoui, A. Software-defined networking (SDN): a survey. Secur. Commun. Netw. 2016, 9, 5803–5833. [Google Scholar] [CrossRef]

- Lockwood, J.W.; Monga, M. Implementing ultra-low-latency datacenter services with programmable logic. In Proceedings of the 2015 IEEE 23rd Annual Symposium on High-Performance Interconnects, Santa Clara, CA, USA, 26–28 August 2015. [Google Scholar]

- Zhao, T.; Li, T.; Han, B.; Sun, Z.; Huang, J. Design and implementation of Software Defined Hardware Counters for SDN. Comput. Netw. 2016, 102, 129–144. [Google Scholar] [CrossRef]

- Antichi, G.; Rotsos, C.; Moore, A. Enabling performance evaluation beyond 10 Gbps. In Proceedings of the ACM Conference on Special Interest Group on Data Communication, SIGCOMM 2015, New York, NY, USA, 17–21 August 2015. [Google Scholar] [CrossRef]

- Pacifico, R.; Goulart, P.; Vieira, A.; Vieira, M.; Nacif, J. Hardware Modules for Packet Interarrival Time Monitoring for Software Defined Measurements. In Proceedings of the 41st IEEE Conference on Local Computer Networks, LCN 2016, Dubai, United Arab Emirates, 7–10 November 2016. [Google Scholar] [CrossRef]

- Van, T.N.; Bao, H.; Thinh, T. An anomaly-based intrusion detection architecture integrated on openflow switch. In Proceedings of the 6th International Conference on Communication and Network Security, ICCNS 2016, New York, NY, USA, 12–14 November 2016. [Google Scholar] [CrossRef]

- Arap, O.; Brown, G.; Himebaugh, B.; Swany, M. Software Defined Multicasting for MPI Collective Operation Offloading with the NetFPGA. In Proceedings of the 20th International Euro-Par Conference on Parallel Processing (Euro-Par), Porto, Portugal, 25–29 August 2014. [Google Scholar]

- Rotsos, C.; Antichi, G.; Bruyere, M.; Owezarski, P.; Moore, A. An open testing framework for next-generation openflow switches. In Proceedings of the 3rd European Workshop on Software-Defined Networks, EWSDN 2014, Washington, DC, USA, 1–3 September 2014. [Google Scholar] [CrossRef]

- Park, T.; Xu, Z.; Shin, S. HEX switch: Hardware-assisted security extensions of OpenFlow. In Proceedings of the 1st Workshop on Security in Softwarized Networks: Prospects and Challenges, Budapest, Hungary, 20–24 August 2018. [Google Scholar] [CrossRef]

- Paolucci, F.; Civerchia, F.; Sgambelluri, A.; Giorgetti, A.; Cugini, F.; Castoldi, P. P4 Edge Node Enabling Stateful Traffic Engineering and Cyber Security. J. Opt. Commun. Netw. 2019, 11, A84–A95. [Google Scholar] [CrossRef]

- Yu, Y.; Liang, M.; Wang, Z. Research on data center network data plane model based on vector address. Sichuan Daxue Xuebao (Gongcheng Kexue Ban)/J. Sichuan Univ. (Eng. Sci. Ed.) 2016, 48, 129–135. [Google Scholar] [CrossRef]

- Duan, T.; Lan, J.; Hu, Y.; Sun, P. Separating VNF and network control for hardware-acceleration of SDN/NFV architecture. ETRI J. 2017, 39, 525–534. [Google Scholar] [CrossRef]

- Vieira, J.; Malkowsky, S.; Nieman, K.; Miers, Z.; Kundargi, N.; Liu, L.; Wong, I.; Owall, V.; Edfors, O.; Tufvesson, F. A flexible 100-antenna testbed for Massive MIMO. In Proceedings of the IEEE Global Communications Conference (GLOBECOM), Austin, TX, USA, 8–12 December 2014; pp. 287–293. [Google Scholar]

- Malkowsky, S.; Vieira, J.; Liu, L.; Harris, P.; Nieman, K.; Kundargi, N.; Wong, I.C.; Tufvesson, F.; Owall, V.; Edfors, O. The World’s First Real-Time Testbed for Massive MIMO: Design, Implementation, and Validation. IEEE Access 2017, 5, 9073–9088. [Google Scholar] [CrossRef]

- Nadal, J.; Nour, C.A.; Baghdadi, A. Low-Complexity Pipelined Architecture for FBMC/OQAM Transmitter. IEEE Trans. Circuits Syst. -Express Briefs 2016, 63, 19–23. [Google Scholar] [CrossRef]

- Danneberg, M.; Michailow, N.; Gaspar, I.; Matthe, M.; Zhang, D.; Mendes, L.L.; Fettweis, G. Implementation of a 2 by 2 MIMO-GFDM Transceiver for Robust 5G Networks. In Proceedings of the 12th International Symposium on Wireless Communication Systems (ISWCS), Brussels, Belgium, 25–28 August 2015. [Google Scholar]

- Ferreira, M.; Ferreira, J.; Huebner, M. A parallel-pipelined OFDM baseband modulator with dynamic frequency scaling for 5G systems. In Proceedings of the 14th International Symposium on Applied Reconfigurable Computing, ARC 2018, Santorini, Greece, 2–4 May 2018. [Google Scholar] [CrossRef]

- Medjkouh, S.; Nadal, J.; Nour, C.A.; Baghdadi, A. Reduced Complexity FPGA Implementation for UF-OFDM Frequency Domain Transmitter. In Proceedings of the IEEE International Workshop on Signal Processing Systems (SiPS), Lorient, France, 3–5 October 2017. [Google Scholar]

- Haggui, H.; Bellili, F.; Affes, S. FPGA Prototyping of a STAR-Based Time-Delay Estimator for 5G Radio Access. In Proceedings of the IEEE 28th Annual International Symposium on Personal, Indoor, and Mobile Radio Communications (PIMRC), Montreal, QC, Canada, 8–13 October 2017. [Google Scholar]

- Chitimalla, D.; Kondepu, K.; Valcarenghi, L.; Tornatore, M.; Mukherjee, B. 5G Fronthaul-Latency and Jitter Studies of CPRI Over Ethernet. J. Opt. Commun. Netw. 2017, 9, 172–182. [Google Scholar] [CrossRef]

- Haroun, M.H.; Cabedo-Fabres, M.; Ayad, H.; Jomaah, J.; Ferrando-Bataller, M. Direction of Arrival Estimation for LTE-Advanced and 5G in the Uplink. In Proceedings of the IEEE Middle East and North Africa Communications Conference (MENACOMM), Jounieh, Lebanon, 18–20 April 2018. [Google Scholar]

- Schatz, D.; Bashroush, R.; Wall, J. Towards a more representative definition of cyber security. J. Digit. Forensics, Secur. Law 2017, 12, 8. [Google Scholar] [CrossRef]

- Lee, P.; Anderson, T. Fault Tolerance: Principles and Practice; Dependable Computing and Fault-Tolerant Systems; Springer: Vienna, Austria, 2012. [Google Scholar]

- Perez, A.; Suriano, L.; Otero, A.; de la Torre, E. Dynamic Reconfiguration under RTEMS for Fault Mitigation and Functional Adaptation in SRAM-based SoPCs for Space Systems. In Proceedings of the NASA/ESA Conference on Adaptive Hardware and Systems (AHS), Pasadena, CA, USA, 24–27 July 2017. [Google Scholar]

- Perez Celis, J.A.; de la Rosa Nieves, S.; Romo Fuentes, C.; Santillan Gutierrez, S.D.; Saenz-Otero, A. Methodology for designing highly reliable Fault Tolerance Space Systems based on COTS devices. In Proceedings of the 7th Annual IEEE International Systems Conference (SysCon), Orlando, FL, USA, 15–18 April 2013; pp. 591–594. [Google Scholar]

- Andres Perez-Celis, J.; Ferrer-Perez, J.A.; Santillan-Gutierrez, S.D.; de la Rosa Nieves, S. Simulation of Fault-Tolerant Space Systems Based on COTS Devices With GPSS. IEEE Syst. J. 2016, 10, 53–58. [Google Scholar] [CrossRef]

- Van Harten, L.; Jordans, R.; Pourshaghaghi, H. Necessity of Fault Tolerance Techniques in Xilinx Kintex 7 FPGA Devices for Space Missions: A Case Study. In Proceedings of the 20th Euromicro Conference on Digital System Design (DSD), Vienna, Austria, 30 August–1 September 2017. [Google Scholar] [CrossRef]

- Van Harten, L.D.; Mousavi, M.; Jordans, R.; Pourshaghaghi, H.R. Determining the necessity of fault tolerance techniques in FPGA devices for space missions. Microprocess. Microsyst. 2018, 63, 1–10. [Google Scholar] [CrossRef]