Improving the Lot Fabrication Stability and Performance of Silica Optical Films during PECVD

Abstract

:1. Introduction

2. Lot Fabrication

3. Results and Discussion

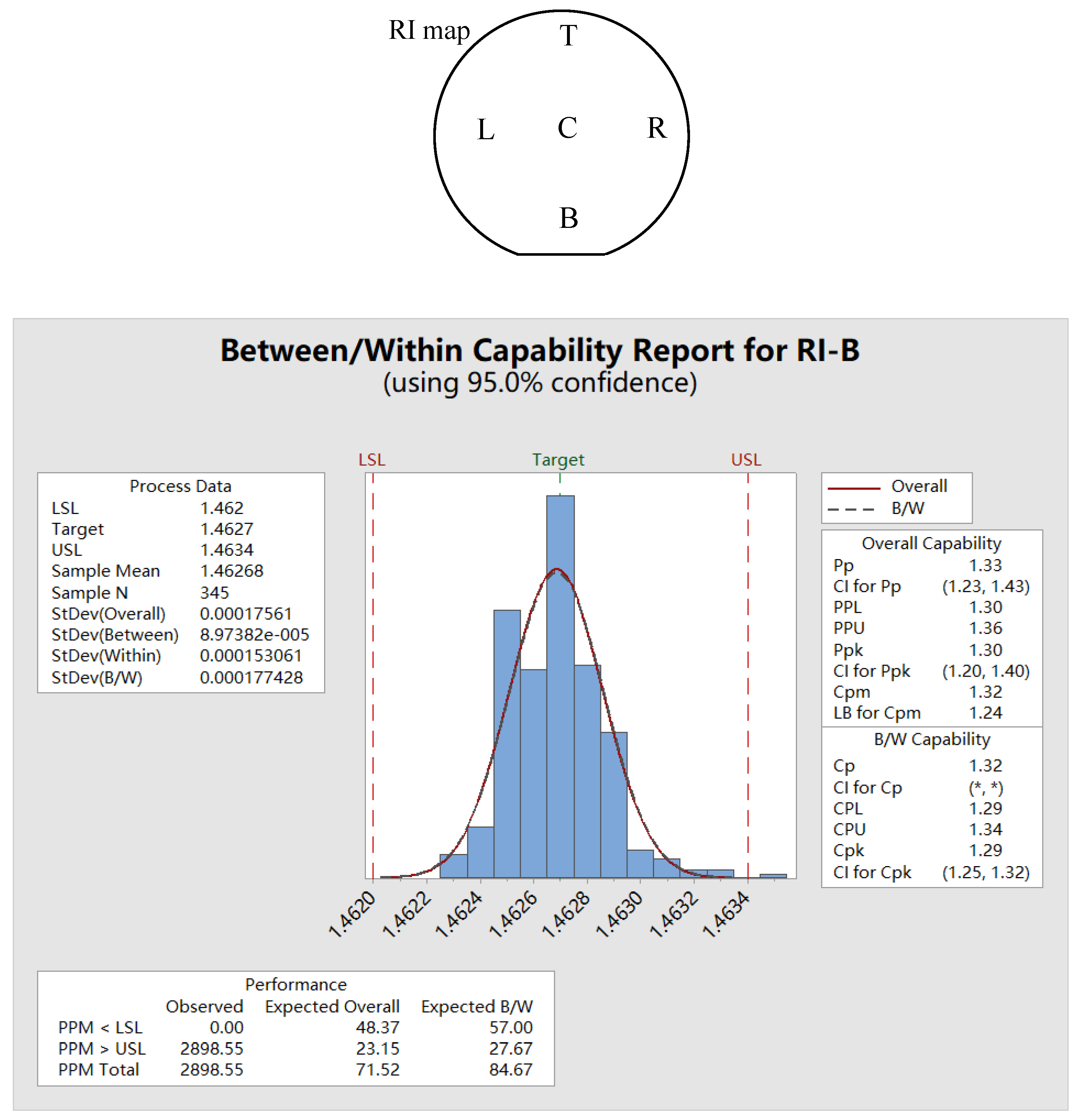

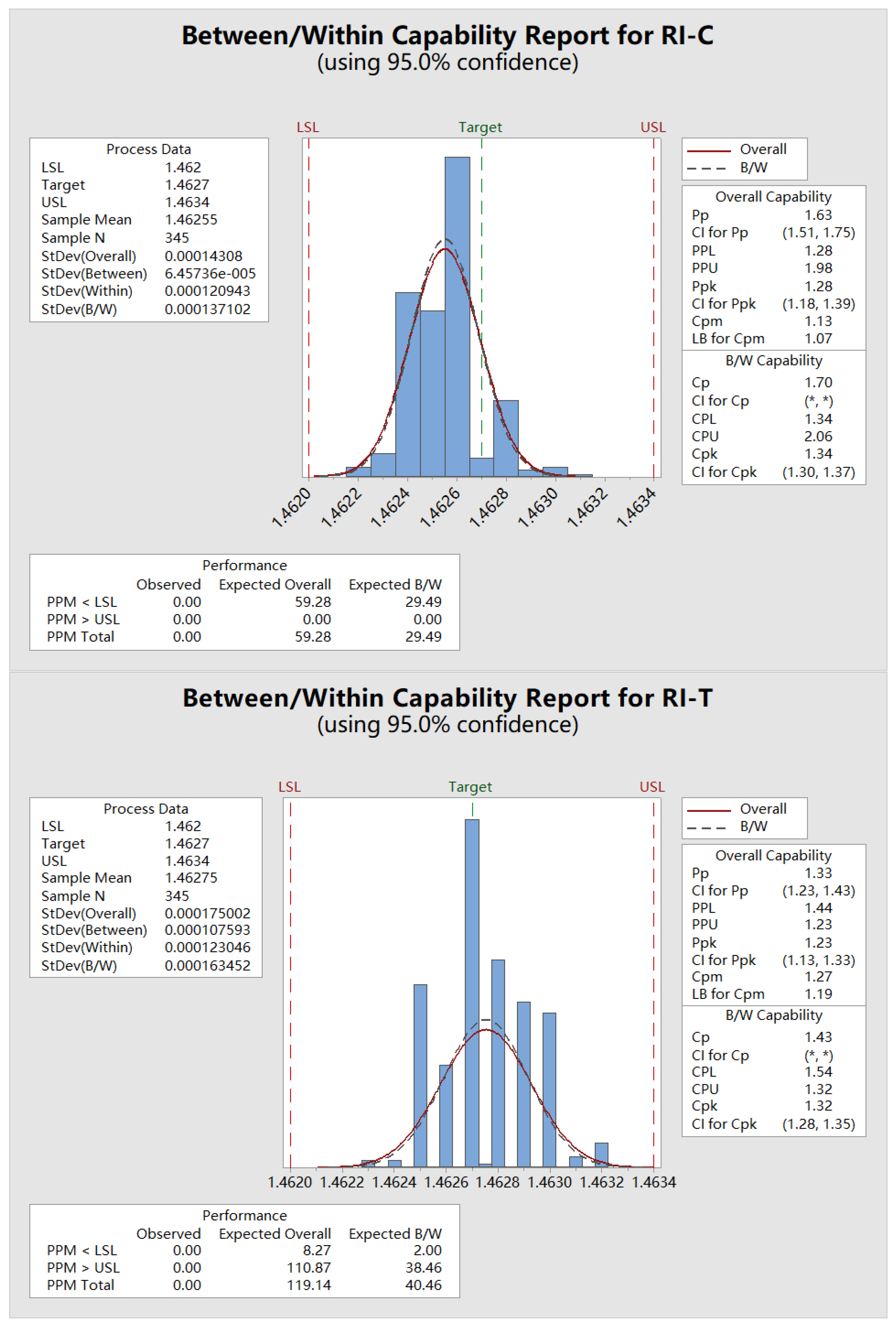

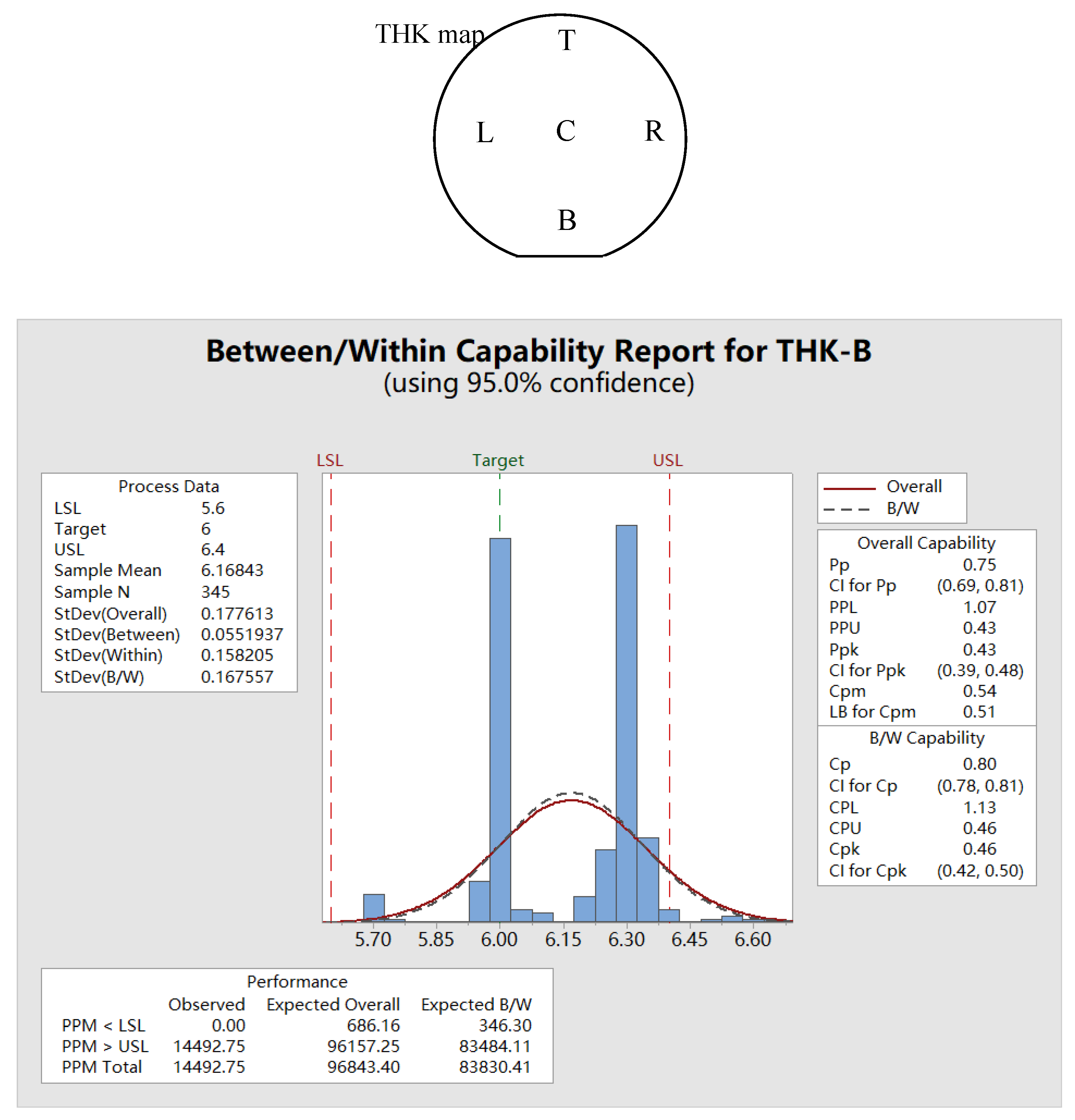

3.1. RI of the GeO2-SiO2 Optical Film

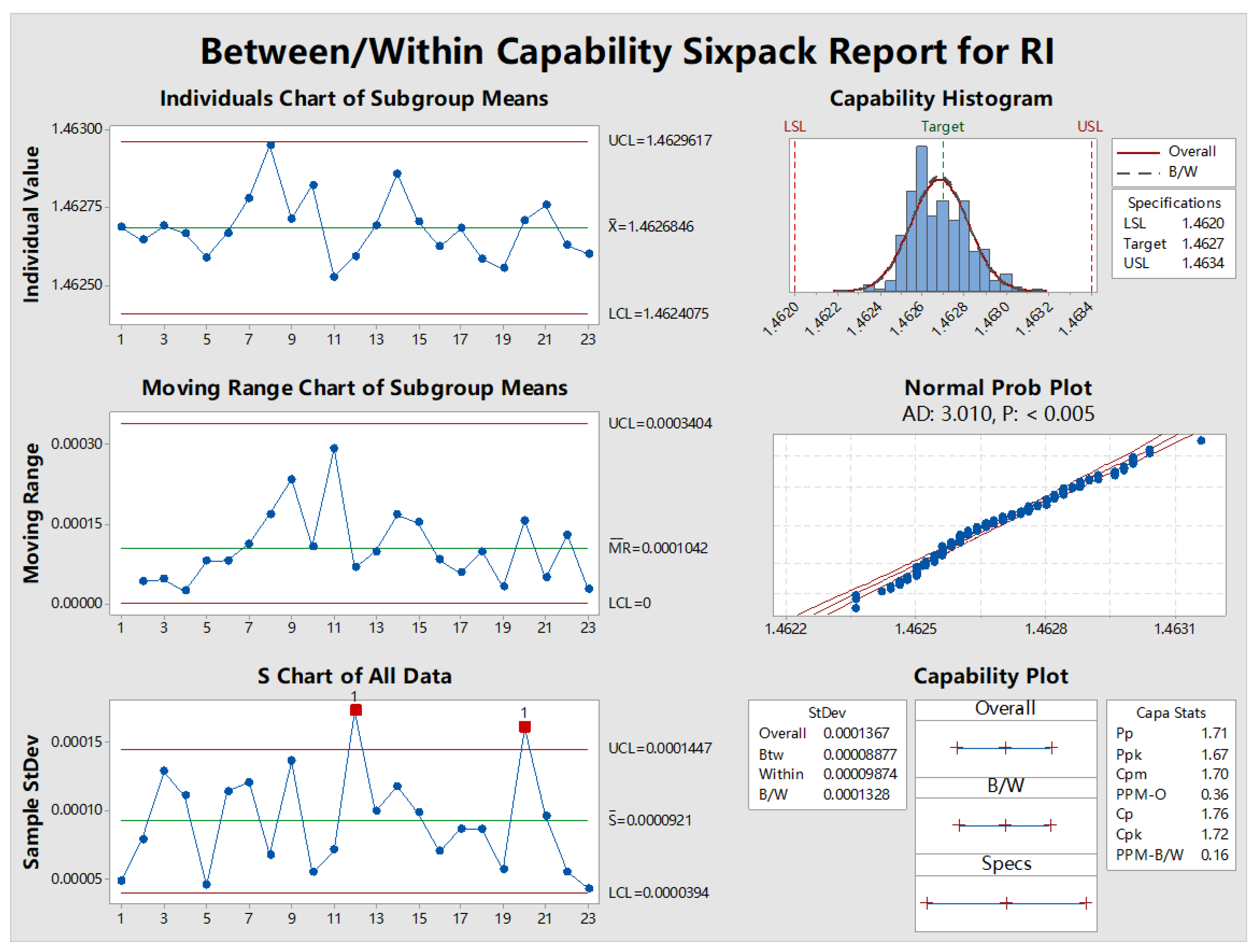

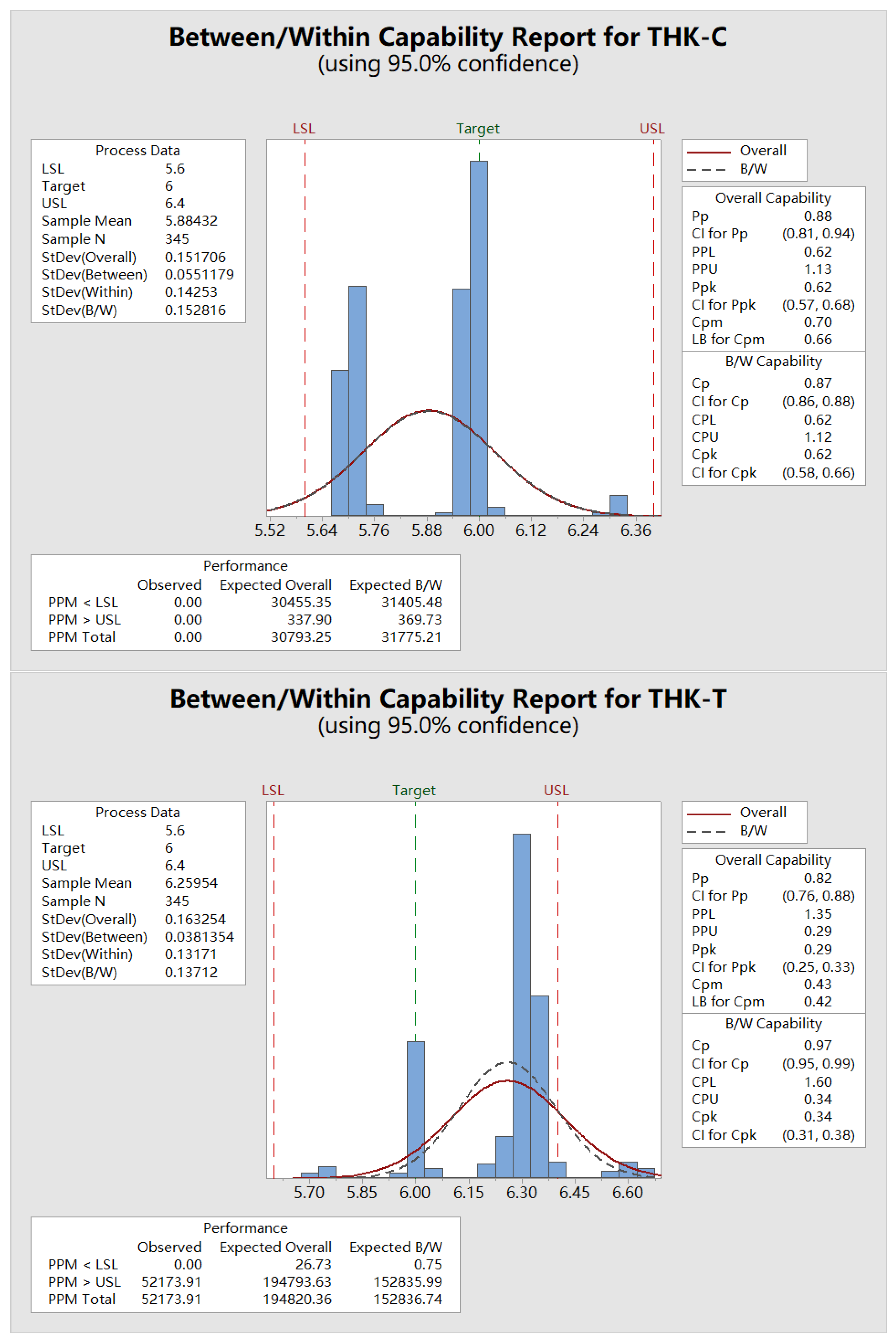

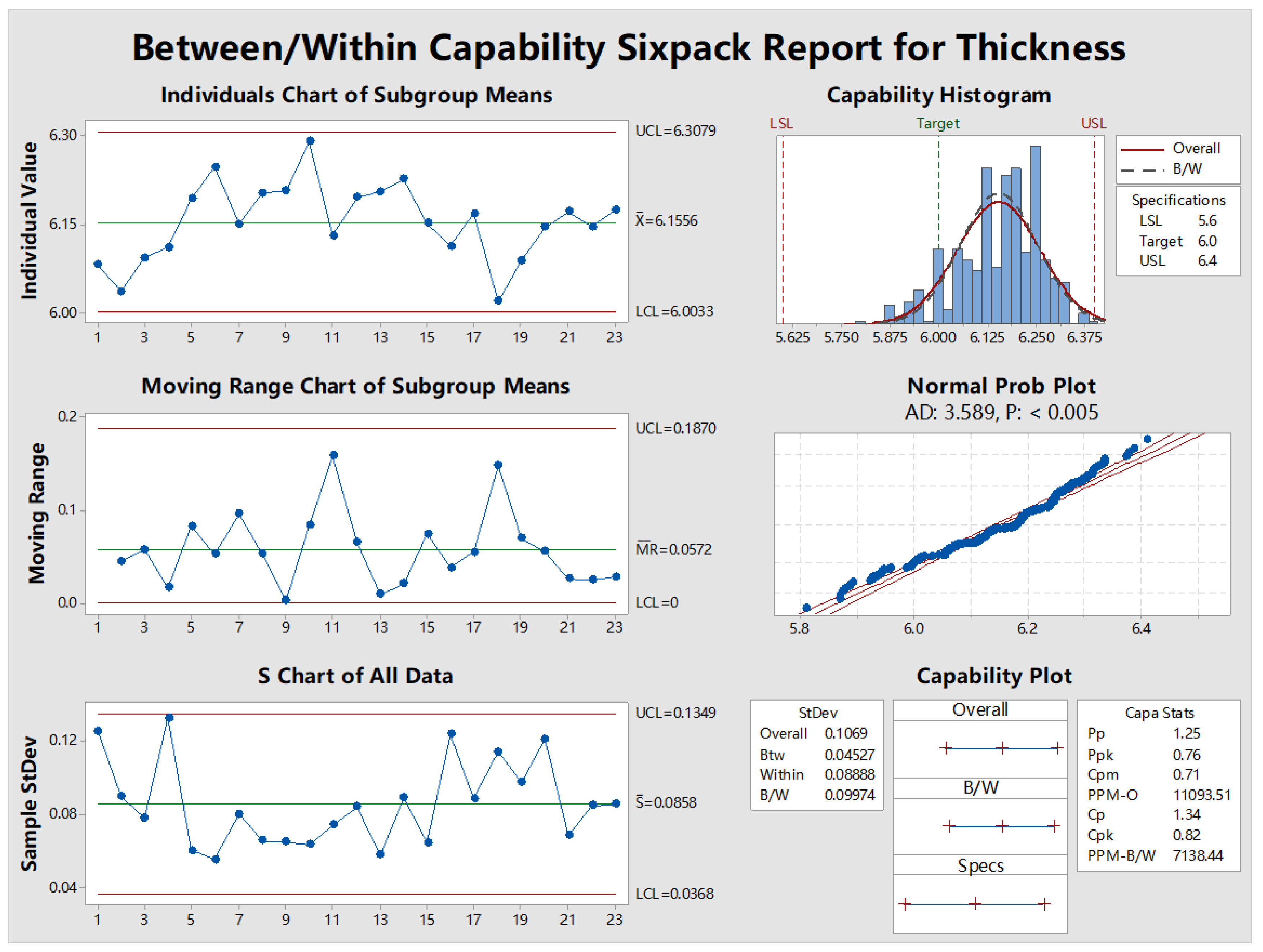

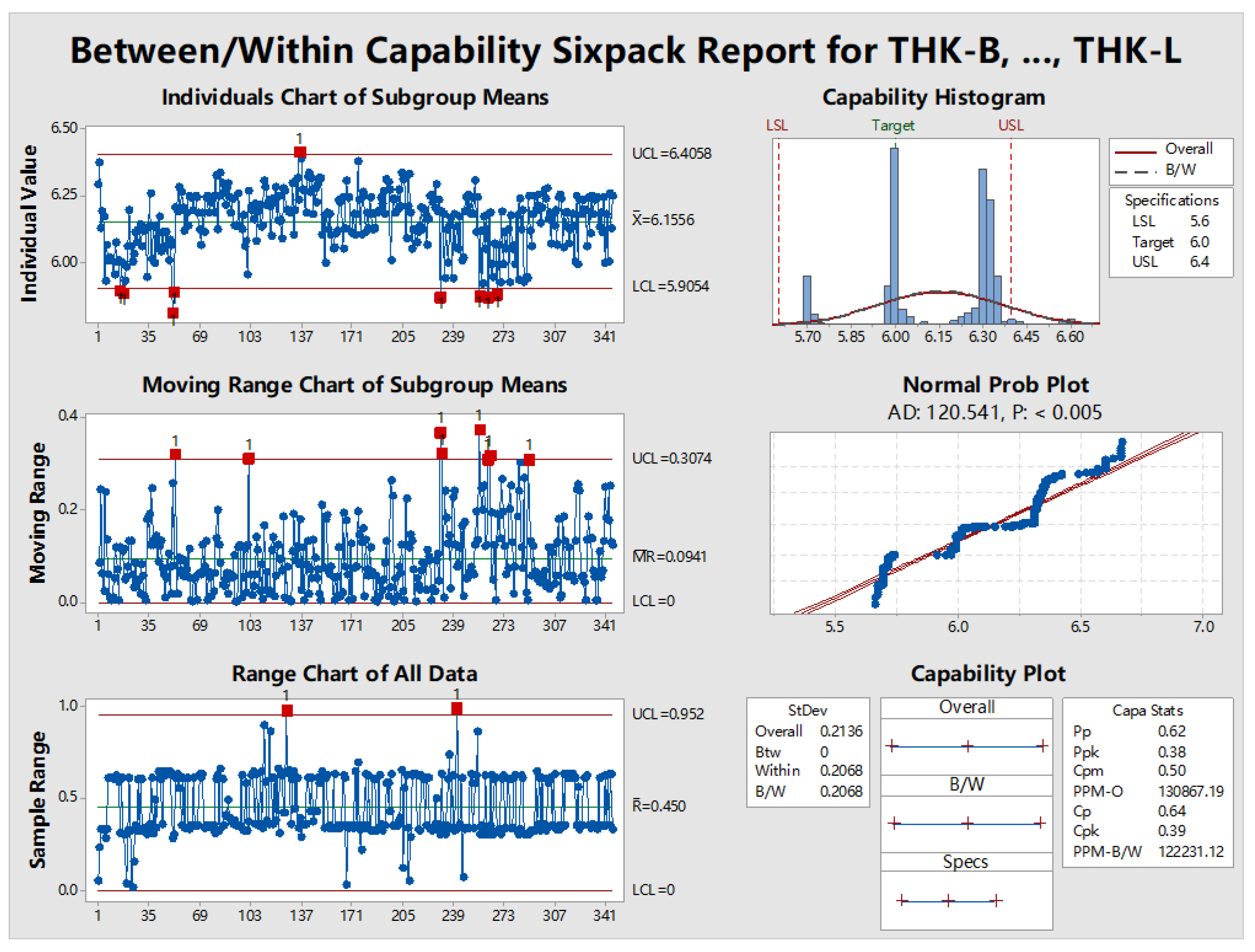

3.2. Thickness of the GeO2-SiO2 Optical Film

3.3. Process Control Strategy

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Choe, J.S.; Ko, H.; Choi, B.S.; Kim, K.J.; Youn, C.J. Silica planar lightwave circuit based integrated 1×4 polarization beam splitter module for three-space BB84 quantum key distribution. IEEE Photonics J. 2018, 10, 7600108. [Google Scholar] [CrossRef]

- Fujisawa, T.; Yamashita, Y.; Sakamoto, T.; Matsui, T.; Tsujikawa, K.; Nakajima, K.; Saitoh, K. Scrambling-type three-mode PLC Multiplexer based on cascaded Y-branch waveguide with integrated mode rotator. J. Lighwave Technol. 2018, 36, 1985–1992. [Google Scholar] [CrossRef]

- Himeno, A.; Kato, K.; Miya, T. Silica-based planar lightwave circuits. IEEE J. Sel. Top. Quantum Electron. 1998, 4, 913–924. [Google Scholar] [CrossRef]

- Doerr, C.R.; Okamoto, K. Advances in silica planar lightwave circuits. J. Lighwave Technol. 2006, 24, 4763–4789. [Google Scholar] [CrossRef]

- Watanabe, K.; Hashizume, Y.; Nasu, Y.; Kohtoku, M.; Itoh, M.; Inoue, Y. Ultralow power consumption silica-based PLC-VOA/switches. J. Lighwave Technol. 2008, 26, 2235–2244. [Google Scholar] [CrossRef]

- Dai, D.X. Subwavelength silica-based optical waveguide with a multilayered buffer for sharp bending. J. Lighwave Technol. 2009, 27, 2489–2499. [Google Scholar]

- Parks, J.W.; Wall, T.A.; Cai, H.; Hawkins, A.R.; Schmidt, H. Enhancement of ARROW photonic device performance via thermal annealing of PECVD-based SiO2 waveguides. IEEE J. Sel. Top. Quantum Electron. 2016, 22, 249–254. [Google Scholar] [CrossRef] [PubMed]

- Kim, Y.; Cho, S.; Seo, Y.; Yoon, H.; Im, Y.; Suh, S.; Yoon, D. Refractive index control of core layer using PECVD and FHD for Silica optical waveguide. Surf. Coat. Technol. 2003, 171, 34–38. [Google Scholar] [CrossRef]

- Liang, H.; Gordon, R.G. Atmospheric pressure chemical vapor deposition of transparent conducting films of fluorine doped zinc oxide and their application to amorphous silicon solar cells. J. Mater. Sci. 2010, 42, 6388–6399. [Google Scholar] [CrossRef]

- Shareef, I.A.; Rubloff, G.W.; Anderle, M.; Gill, W.N.; Cotte, J.; Kim, D.H. Subatmospheric chemical vapor deposition ozone/TEOS process for SiO2 trench filling. J. Vac. Sci. Technol. 1995, 13, 1888–1892. [Google Scholar] [CrossRef]

- Zhang, J.; Ren, Z.; Liang, R.; Sui, Y.; Liu, W. Planar optical waveguide thin films grown by microwave ECR PECVD. Surf. Coat. Technol. 2000, 131, 116–120. [Google Scholar] [CrossRef]

- Kilian, A.; Kirchof, J.; Przyrembel, G.; Wischmann, W. Birefringence free planar optical waveguide made by flame hydrolysis deposition (FHD) through tailoring of the overcladding. J. Lighwave Techol. 2000, 18, 193–198. [Google Scholar] [CrossRef]

- Enami, Y.; Derose, C.T.; Mathine, D.; Loychik, C.; Greenlee, C.; Norwood, R.A.; Kim, T.D.; Luo, J.; Tian, Y.; Jen, A.K.-Y.; et al. Hybrid polymer/sol-gel waveguide modulators with exceptionally large electro-optic coefficients. Nat. Photonics 2007, 1, 180–185. [Google Scholar] [CrossRef]

- Kim, Y.T.; Kim, D.S.; Yoon, D.H. PECVD SiO2 and SiON films dependent on the RF bias power for low-loss silica waveguide. Thin Solid Films 2005, 475, 271–274. [Google Scholar] [CrossRef]

- Bellman, R.A.; Bourdon, G.; Alibert, G.; Beguin, A.; Guiot, E.; Simpson, L.B.; Lehuede, P.; Guiziou, L.; LeGuen, E. Ultrlow loss high delta silica germania planar waveguides. J. Electrochem. Soc. 2004, 151, G541–G547. [Google Scholar] [CrossRef]

- Oakland, J.S. Statistical Process Control; Elsevier Ltd.: Oxford, UK, 2007. [Google Scholar]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zheng, Y.; Gao, P.; Xiao, Z.; Zhou, J.; Duan, J.; Chen, B. Improving the Lot Fabrication Stability and Performance of Silica Optical Films during PECVD. Appl. Sci. 2019, 9, 785. https://doi.org/10.3390/app9040785

Zheng Y, Gao P, Xiao Z, Zhou J, Duan J, Chen B. Improving the Lot Fabrication Stability and Performance of Silica Optical Films during PECVD. Applied Sciences. 2019; 9(4):785. https://doi.org/10.3390/app9040785

Chicago/Turabian StyleZheng, Yu, Piaopiao Gao, Zhixin Xiao, Jianying Zhou, Ji’an Duan, and Bo Chen. 2019. "Improving the Lot Fabrication Stability and Performance of Silica Optical Films during PECVD" Applied Sciences 9, no. 4: 785. https://doi.org/10.3390/app9040785

APA StyleZheng, Y., Gao, P., Xiao, Z., Zhou, J., Duan, J., & Chen, B. (2019). Improving the Lot Fabrication Stability and Performance of Silica Optical Films during PECVD. Applied Sciences, 9(4), 785. https://doi.org/10.3390/app9040785