Nonvolatile Organic Floating-Gate Memory Using N2200 as Charge-Trapping Layer

Abstract

1. Introduction

2. Device Structure and Physical Models

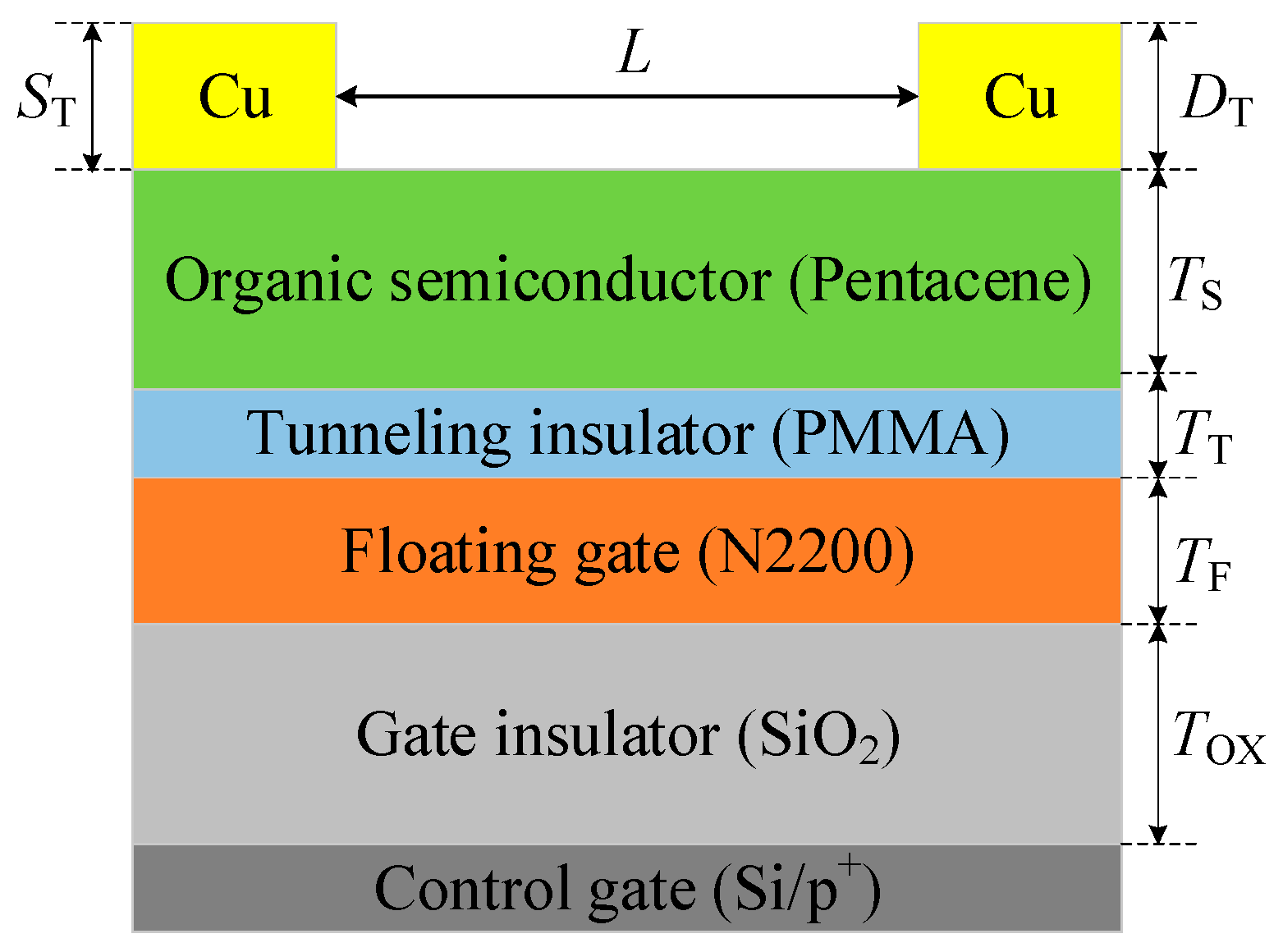

2.1. Device Structure

2.2. Physical Models

3. Results and Discussion

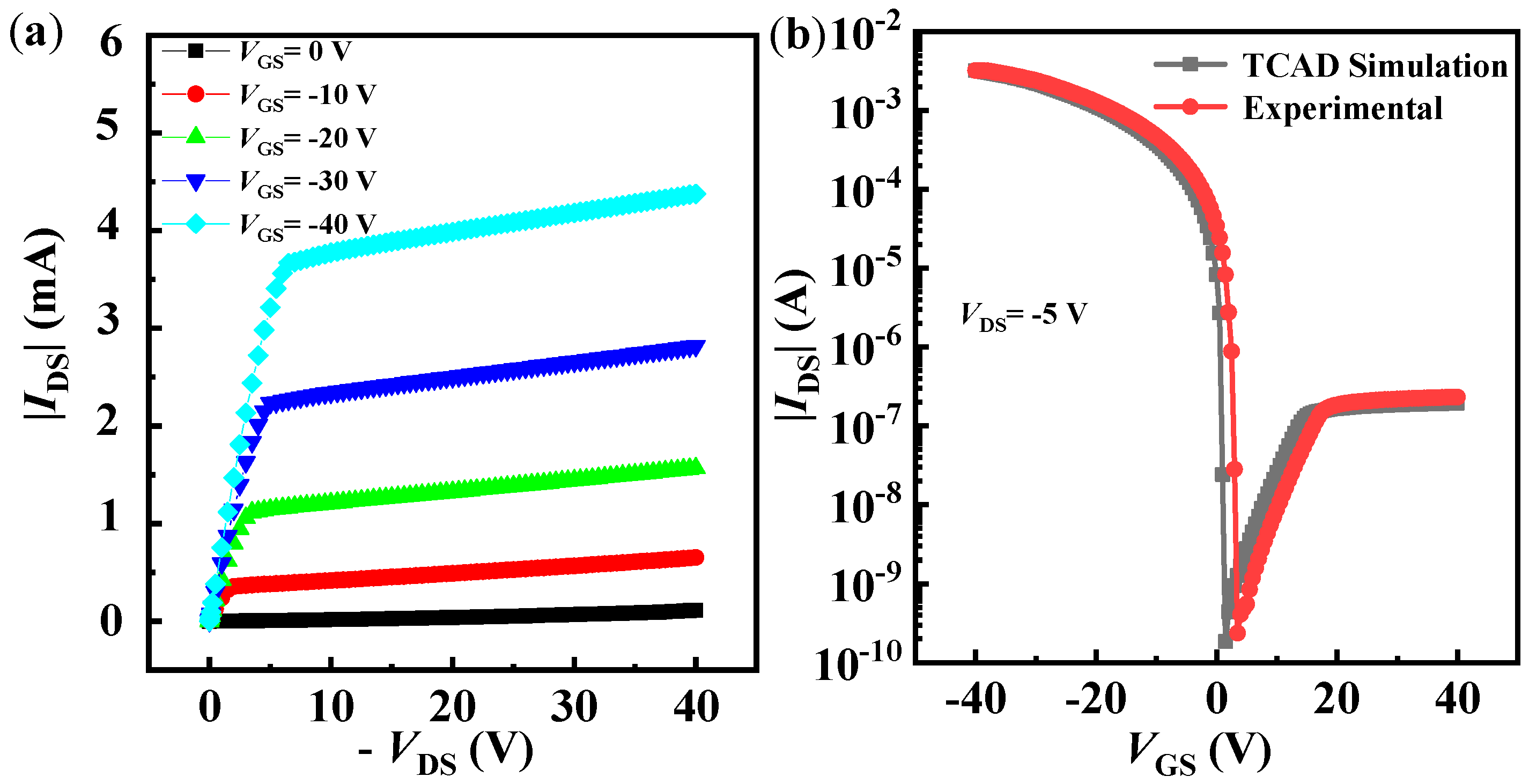

3.1. Output and Transfer Characteristics

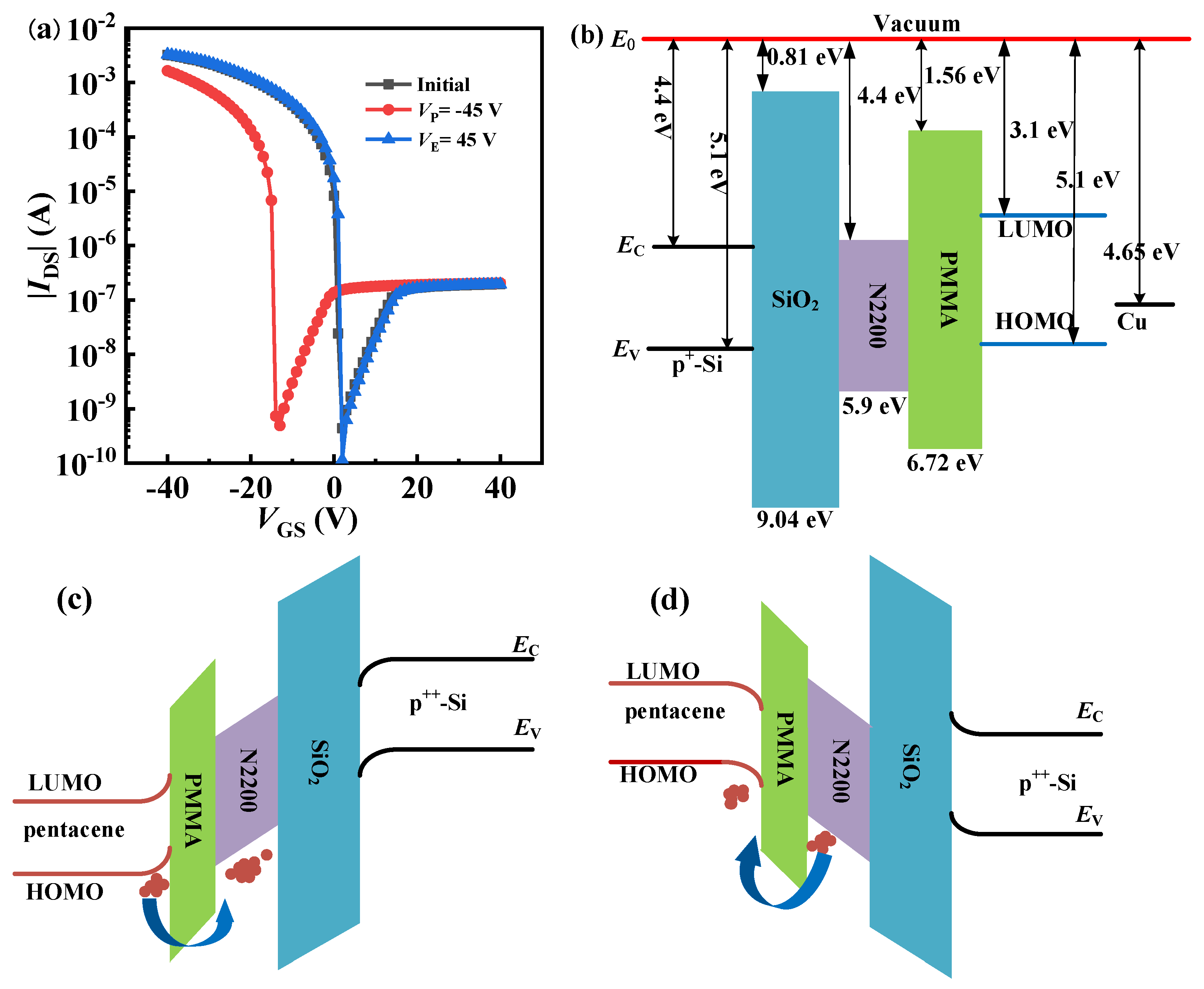

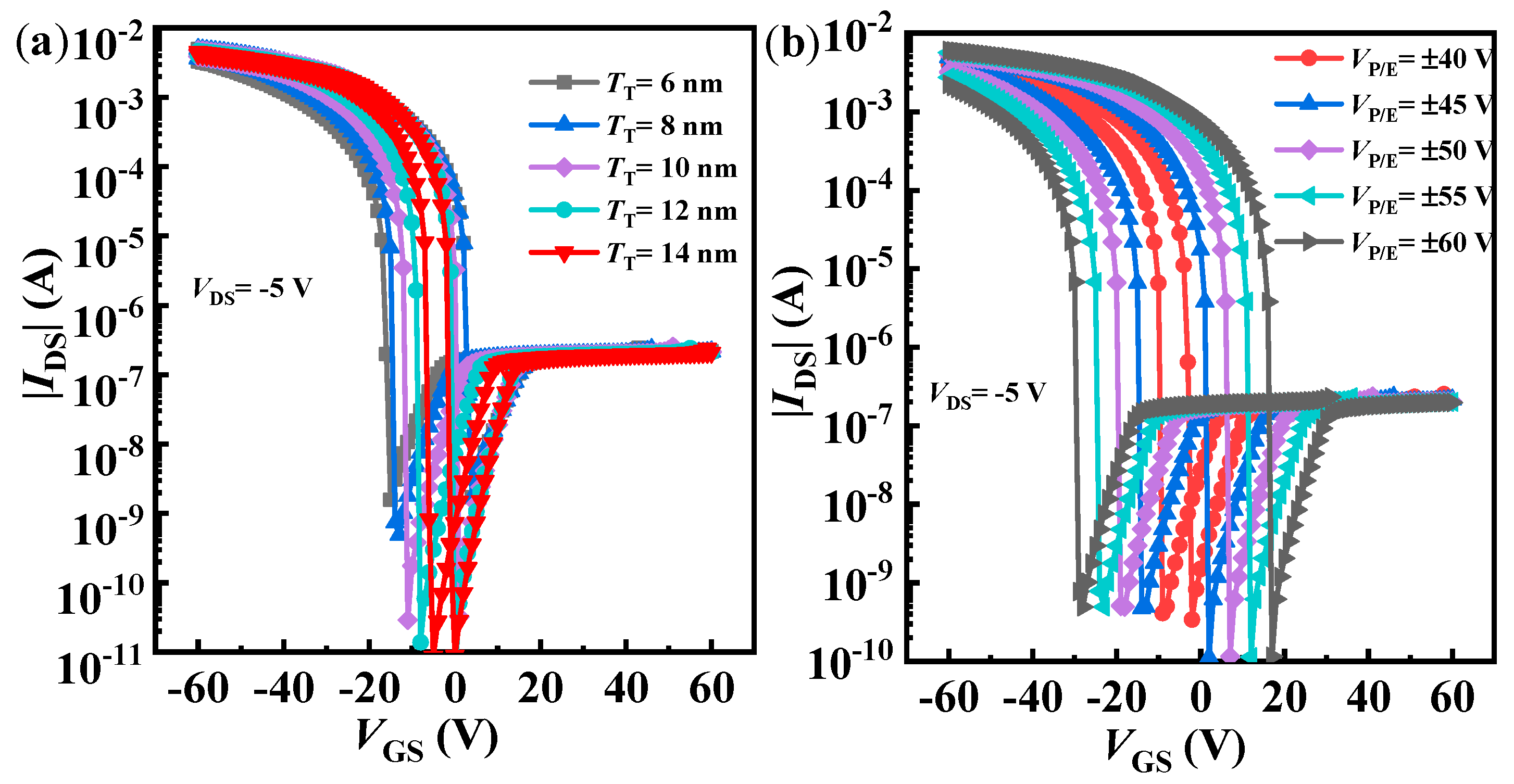

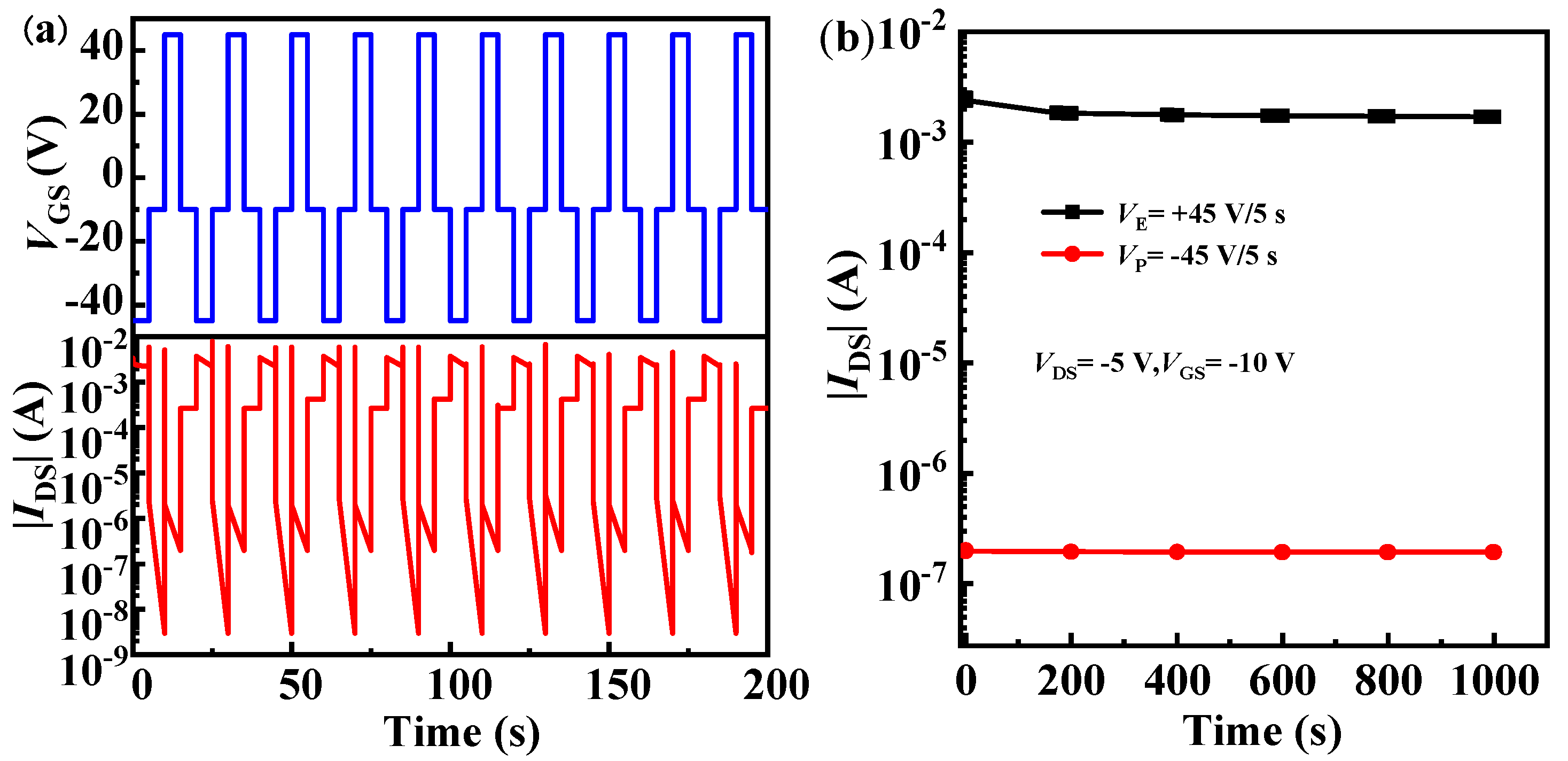

3.2. Storage Characteristics

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Hu, D.; Wang, X.; Chen, H.; Guo, T. High performance flexible nonvolatile memory based on vertical organic thin film transistor. Adv. Funct. Mater. 2017, 27, 1703541. [Google Scholar] [CrossRef]

- Jeong, Y.J.; Yun, D.J.; Kim, S.H.; Jang, J.; Park, C.E. Photoinduced recovery of organic transistor memories with photoactive floating-gate interlayers. ACS Appl. Mater. 2017, 9, 11759–11769. [Google Scholar] [CrossRef]

- Zhao, Y.; Wang, W.; He, Z.; Peng, B.; Di, C.A.; Li, H. High-performance and multifunctional organic field-effect transistors. Chin. Chem. Lett. 2023, 34, 108094. [Google Scholar] [CrossRef]

- Chen, H.; Zhou, Y.; Han, S.T. Recent advances in metal nanoparticle-based floating gate memory. Nano Select 2021, 2, 1245–1265. [Google Scholar] [CrossRef]

- Kumar, S.; Kumar, A.; Mishra, R.D.; Babu, P.; Pandey, S.K.; Devi, S.; Kumar, M. Multilevel Nanophotonic Resistive Switching in Ag-ITO-SiO 2 on Silicon with Enhanced Optical Storage Density. J. Light. Technol. 2024, 43, 1299–1305. [Google Scholar] [CrossRef]

- Nguyen, T.H.; Imran, M.; Choi, J.; Yang, J.S. HYDRA: A Hybrid Resistance Drift Resilient Architecture for Phase Change Memory-Based Neural Network Accelerators. IEEE Trans. Comput. 2024, 73, 2123–2135. [Google Scholar] [CrossRef]

- Wu, H.; Chen, A.; Zhang, P.; He, H.; Nance, J.; Guo, C.; Wang, K.L. Magnetic memory driven by topological insulators. Nat. Commun. 2021, 12, 6251. [Google Scholar] [CrossRef] [PubMed]

- Yoo, J.; Song, H.; Lee, H.; Lim, S.; Kim, S.; Heo, K.; Bae, H. Recent research for HZO-based ferroelectric memory towards in-memory computing applications. Electronics 2023, 12, 2297. [Google Scholar] [CrossRef]

- Leydecker, T.; Herder, M.; Pavlica, E.; Bratina, G.; Hecht, S.; Orgiu, E.; Samorì, P. Flexible non-volatile optical memory thin-film transistor device with over 256 distinct levels based on an organic bicomponent blend. Nat. Nanotechnol. 2016, 11, 769–775. [Google Scholar] [CrossRef]

- Heshami, K.; England, D.G.; Humphreys, P.C.; Bustard, P.J.; Acosta, V.M.; Nunn, J.; Sussman, B.J. Quantum memories: Emerging applications and recent advances. J. Mod. Opt. 2016, 63, 2005–2028. [Google Scholar] [CrossRef]

- Xie, S.; Tu, L.; Han, Y.; Huang, L.; Kang, K.; Lao, K.U.; Poddar, P.; Park, C.; Muller, D.A.; Park, J. Coherent, atomically thin transition-metal dichalcogenide superlattices with engineered strain. Science 2018, 359, 1131–1136. [Google Scholar] [CrossRef] [PubMed]

- Chen, Y.; Yu, H.; Gong, J.; Ma, M.; Han, H.; Wei, H.; Xu, W. Artificial synapses based on nanomaterials. Nanotechnology 2018, 30, 012001. [Google Scholar] [CrossRef]

- Zhu, Z.; Guo, Y.; Liu, Y. Application of organic field-effect transistors in memory. Mater. Chem. Front. 2020, 4, 2845–2862. [Google Scholar] [CrossRef]

- Wang, S.; He, C.; Tang, J.; Lu, X.; Shen, C.; Yu, H.; Du, L.; Li, J.; Yang, R.; Shi, D.; et al. New floating gate memory with excellent retention characteristics. Adv. Electron. Mater. 2019, 5, 1800726. [Google Scholar] [CrossRef]

- Khan, A.I.; Keshavarzi, A.; Datta, S. The future of ferroelectric field-effect transistor technology. Nat. Electron. 2020, 3, 588–597. [Google Scholar] [CrossRef]

- Kim, J.; Ho, D.; Kim, I.S.; Kim, M.G.; Baeg, K.J.; Kim, C. Solution-processed flexible nonvolatile organic field-effect transistor memory using polymer electret. Org. Electron. 2021, 99, 106331. [Google Scholar] [CrossRef]

- He, L.; Li, E.; He, W.; Yan, Y.; Lan, S.; Yu, R.; Cheng, H.; Guo, T. Complementary of ferroelectric and floating gate structure for high performance organic nonvolatile memory. Adv. Electron. Mater. 2021, 7, 2100599. [Google Scholar] [CrossRef]

- Chen, Z.; Chen, S.; Jiang, T.; Chen, S.; Jia, R.; Xiao, Y.; Pan, J.; Jie, J.; Zhang, X. A floating-gate field-effect transistor memory device based on organic crystals with a built-in tunneling dielectric by a one-step growth strategy. Nanoscale 2024, 16, 3721–3728. [Google Scholar] [CrossRef]

- Jeong, Y.J.; Yun, D.J.; Noh, S.H.; Park, C.E.; Jang, J. Surface modification of CdSe quantum-dot floating gates for advancing light-erasable organic field-effect transistor memories. ACS Nano 2018, 12, 7701–7709. [Google Scholar] [CrossRef]

- Xu, T.; Fan, S.; Cao, M.; Liu, T.; Su, J. Flexible organic field-effect transistor nonvolatile memory enabling bipolar charge storage by small-molecule floating gate. Appl. Phys. Lett. 2022, 120, 073301. [Google Scholar] [CrossRef]

- Yu, Y.; Ma, Q.; Ling, H.; Li, W.; Ju, R.; Bian, L.; Shi, N.; Qian, Y.; Yi, M.; Xie, L.; et al. Small-molecule-based organic field-effect transistor for nonvolatile memory and artificial synapse. Adv. Funct. Mater. 2019, 29, 1904602. [Google Scholar] [CrossRef]

- Liu, Y.; Shao, Z.; Yu, X.; Guo, D.; Wang, S.; Bian, L.; Chen, Y.; Liu, H.; Ling, H.; Xie, L. Graphdiyne particles as nano-floating gates for high-performance nonvolatile organic field-effect transistor memory. Org. Electron. 2024, 128, 107027. [Google Scholar] [CrossRef]

- Gao, X.; Liu, C.H.; She, X.J.; Li, Q.L.; Liu, J.; Wang, S.D. Photon-energy-dependent light effects in organic nano-floating-gate nonvolatile memories. Org. Electron. 2014, 15, 2486–2491. [Google Scholar] [CrossRef]

- Che, Y.; Zhang, Y.; Cao, X.; Song, X.; Cao, M.; Dai, H.; Yang, J.; Zhang, G.; Yao, J. Low operating voltage ambipolar graphene oxide-floating-gate memory devices based on quantum dots. J. Mater. Chem. C 2016, 4, 1420–1424. [Google Scholar] [CrossRef]

- Li, Q.; Zhang, Y.; Yu, Y.; Chen, Z.; Jin, L.; Li, Y.; Li, T.; Yang, Y.; Zhao, H.; Li, J. Light enhanced low-voltage nonvolatile memory based on all-inorganic perovskite quantum dots. Nanotechnology 2019, 30, 37LT01. [Google Scholar] [CrossRef] [PubMed]

- Li, W.; Guo, F.; Ling, H.; Liu, H.; Yi, M.; Zhang, P.; Wang, W.; Xie, L.; Huang, W. Solution-processed wide-bandgap organic semiconductor nanostructures arrays for nonvolatile organic field-effect transistor memory. Small 2018, 14, 1701437. [Google Scholar] [CrossRef] [PubMed]

- Xu, T.; Guo, S.; Qi, W.; Li, S.; Xu, M.; Xie, W.; Wang, W. High-performance flexible organic thin-film transistor nonvolatile memory based on molecular floating-gate and pn-heterojunction channel layer. Appl. Phys. Lett. 2020, 116, 023301. [Google Scholar] [CrossRef]

- Shu, S.; Xu, T.; Su, J. A flexible floating-gate based organic field-effect transistor non-volatile memory based on F8BT/PMMA integrated floating-gate/tunneling layer. Phys. Scr. 2023, 98, 045402. [Google Scholar] [CrossRef]

- Wang, G.; Liu, X.; Wang, W. Solution processed organic transistor nonvolatile memory with a floating-gate of carbon nanotubes. IEEE Electron Device Lett. 2017, 39, 111–114. [Google Scholar] [CrossRef]

- Yan, Z.W.; Wang, J.; Qiao, J.L.; Chen, W.J.; Yang, P.; Xiao, T.; Yang, J.H. Numerical simulation study of organic nonvolatile memory with polysilicon floating gate. Chin. Phys. B 2016, 25, 067102. [Google Scholar] [CrossRef]

- Liu, L.; Su, Y.; Xu, J.P.; Zhang, Y.X. Fabrication and Characteristics of Nano-Floating Gate Memories with ZnO Nano-Crystals as Charge-Storage Layer. Chin. Phys. Lett. 2018, 35, 068101. [Google Scholar] [CrossRef]

- Kim, H.R.; Kang, C.S.; Kim, S.K.; Byun, C.W.; Yoon, S.M. Characterization on the operation stability of mechanically flexible memory thin-film transistors using engineered ZnO charge-trap layers. J. Phys. D Appl. Phys. 2019, 52, 325106. [Google Scholar] [CrossRef]

- Yu, T.; Hou, S.; Liu, Z.; Wang, Y.; Yin, J.; Gao, X.; Liu, N.; Yuan, G.; Wu, L.; Xia, Y.; et al. Enhanced Performance of Organic Field-Effect Transistor with Bi-Functional N-Type Organic Semiconductor Layer. Adv. Electron. Mater. 2024, 10, 2300651. [Google Scholar] [CrossRef]

- Li, W.; Yi, M.; Ling, H.; Guo, F.; Wang, T.; Yang, T.; Xie, L.H.; Huang, W. Analysis of temperature-dependent electrical transport properties of nonvolatile organic field-effect transistor memories based on PMMA film as charge trapping layer. J. Phys. D Appl. Phys. 2016, 49, 125104. [Google Scholar] [CrossRef]

- Wang, W.; Han, J.; Ying, J.; Xiang, L.; Xie, W. Effect of tunneling layers on the performances of floating-gate based organic thin-film transistor nonvolatile memories. Appl. Phys. Lett. 2014, 105, 123303. [Google Scholar] [CrossRef]

- Mittal, P.; Yadav, S.; Negi, S. Advancements for organic thin film transistors: Structures, materials, performance parameters, influencing factors, models, fabrication, reliability and applications. Mater. Sci. Semicond. Process. 2021, 133, 105975. [Google Scholar] [CrossRef]

- Delavari, N.; Tybrandt, K.; Berggren, M.; Piro, B.; Noël, V.; Mattana, G.; Zozoulenko, I. Nernst–Planck–Poisson analysis of electrolyte-gated organic field-effect transistors. J. Phys. D Appl. Phys. 2021, 54, 415101. [Google Scholar] [CrossRef]

- Jung, S.; Bonnassieux, Y.; Horowitz, G.; Jung, S.; Iñiguez, B.; Kim, C.H. Advances in compact modeling of organic field-effect transistors. IEEE J. Electron Devices Soc. 2020, 8, 1404–1415. [Google Scholar] [CrossRef]

- Gill, W.D. Drift mobilities in amorphous charge-transfer complexes of trinitrofluorenone and poly-n-vinylcarbazole. J. Appl. Phys. 1972, 43, 5033–5040. [Google Scholar] [CrossRef]

- Matsumura, M.; Akai, T.; Saito, M.; Kimura, T. Height of the energy barrier existing between cathodes and hydroxyquinoline–aluminum complex of organic electroluminescence devices. J. Appl. phys. 1996, 79, 264–268. [Google Scholar] [CrossRef]

- Parker, I.D. Carrier tunneling and device characteristics in polymer light-emitting diodes. J. Appl. Phys. 1994, 75, 1656–1666. [Google Scholar] [CrossRef]

- Li, W.; Zhang, P.; Li, H.; Sheng, X.; Li, Y.; Xu, X.; Yi, M.; Shi, N.; Shi, W.; Xie, L.; et al. A tricolour photodetecting memory device based on lead sulfide colloidal quantum dots floating gate. Org. Electron. 2019, 75, 105111. [Google Scholar] [CrossRef]

- Zhang, P.; Chen, X.; Li, W.; Ling, H.; Wang, W.; Zhang, G.; Yi, M.; Xie, L.; Shi, W.; Shi, N.; et al. Organic non-volatile memory based on pentacene/tris (8-hydroxy quinoline) aluminum heterojunction transistor. Org. Electron. 2018, 57, 335–340. [Google Scholar] [CrossRef]

- Lamport, Z.A.; Haneef, H.F.; Anand, S.; Waldrip, M.; Jurchescu, O.D. Tutorial: Organic field-effect transistors: Materials, structure and operation. J. Appl. Phys. 2018, 124, 071101. [Google Scholar] [CrossRef]

- Yi, M.; Shu, J.; Wang, Y.; Ling, H.; Song, C.; Li, W.; Xie, L.; Huang, W. The effect of porous structure of PMMA tunneling dielectric layer on the performance of nonvolatile floating-gate organic field-effect transistor memory devices. Org. Electron. 2016, 33, 95–101. [Google Scholar] [CrossRef]

- Zhang, W.T.; Wang, F.X.; Li, Y.M.; Guo, X.X.; Yang, J.H. Organic field-effect transistor floating-gate memory using polysilicon as charge trapping layer. Chin. Phys. B 2019, 28, 086801. [Google Scholar] [CrossRef]

- Xu, T.; Guo, S.; Xu, M.; Li, S.; Xie, W.; Wang, W. Organic transistor nonvolatile memory with an integrated molecular floating-gate/tunneling layer. Appl. Phys. Lett. 2018, 113, 243301. [Google Scholar] [CrossRef]

- Wang, Y.; Kang, L.; Liu, Z.; Wan, Z.; Yin, J.; Gao, X.; Xia, Y.; Liu, Z. Enhancement of memory properties of pentacene field-effect transistor by the reconstruction of an inner vertical electric field with an n-type semiconductor interlayer. ACS Appl. Mater. Interfaces 2021, 13, 13452–13458. [Google Scholar] [CrossRef]

| Parameter | Symbol | Value |

|---|---|---|

| Channel length | L/μm | 80 |

| Channel width | W/μm | 1000 |

| Thickness of source and drain electrodes | ST, DT/nm | 50 |

| Thickness of organic semiconductor | TS/nm | 40 |

| Thickness of tunneling insulator | TT/nm | 6, 8, 10, 12, 14 |

| Thickness of FG | TF/nm | 18 |

| Thickness of gate insulator | TOX/nm | 90 |

| Dielectric constant of gate insulator (PMMA) | εS | 3.0 |

| Dielectric constant of FG layer (N2200) | εS | 3.5 |

| Work function (Cu) | WF/eV | 4.65~4.70 |

| Active layer band gap width (pentacene) | Eg/eV | 1.8~2.2 |

| Band gap width of FG layer (N2200) | Eg/eV | 3.3~3.6 |

| FG Layer | Tunneling Layer | VP/VE (V) | Memory Window (V) | Reference |

|---|---|---|---|---|

| Gold nanoparticles | PMMA | +80/−150 | 43 | [45] |

| Single-walled carbon nanotubes | PMMA | +60/−60 | 26.7 | [29] |

| Polysilicon | PMMA | +60/−60 | 9.28 | [46] |

| F8BT | PMMA | +40/−40 | 9.28 | [28] |

| C60 | TTC | +40/−40 | 8.0 | [47] |

| N2200 | PMMA | +45/−45 | 16.1 | This work |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, W.; Shang, J.; Li, S.; Liu, H.; Ma, M.; Ma, D. Nonvolatile Organic Floating-Gate Memory Using N2200 as Charge-Trapping Layer. Appl. Sci. 2025, 15, 2278. https://doi.org/10.3390/app15052278

Zhang W, Shang J, Li S, Liu H, Ma M, Ma D. Nonvolatile Organic Floating-Gate Memory Using N2200 as Charge-Trapping Layer. Applied Sciences. 2025; 15(5):2278. https://doi.org/10.3390/app15052278

Chicago/Turabian StyleZhang, Wenting, Junliang Shang, Shuang Li, Hu Liu, Mengqi Ma, and Dongping Ma. 2025. "Nonvolatile Organic Floating-Gate Memory Using N2200 as Charge-Trapping Layer" Applied Sciences 15, no. 5: 2278. https://doi.org/10.3390/app15052278

APA StyleZhang, W., Shang, J., Li, S., Liu, H., Ma, M., & Ma, D. (2025). Nonvolatile Organic Floating-Gate Memory Using N2200 as Charge-Trapping Layer. Applied Sciences, 15(5), 2278. https://doi.org/10.3390/app15052278