An Electronically Adjustable Floating Memcapacitor Emulator Circuit Using CDBA

Abstract

1. Introduction

- In our work, the CDBA element, which has important advantages such as wide dynamic range, high slope speed, differential structure at the input port and which has not been used in the design of memcapacitor emulators in the literature to the best of our knowledge, was used.

- The memcapacitor emulator analyzed both in simulation and experimentally has the advantages of not having ground restriction, not having a memristor in its structure, being electronically adjustable and being able to operate in decreasing and increasing modes.

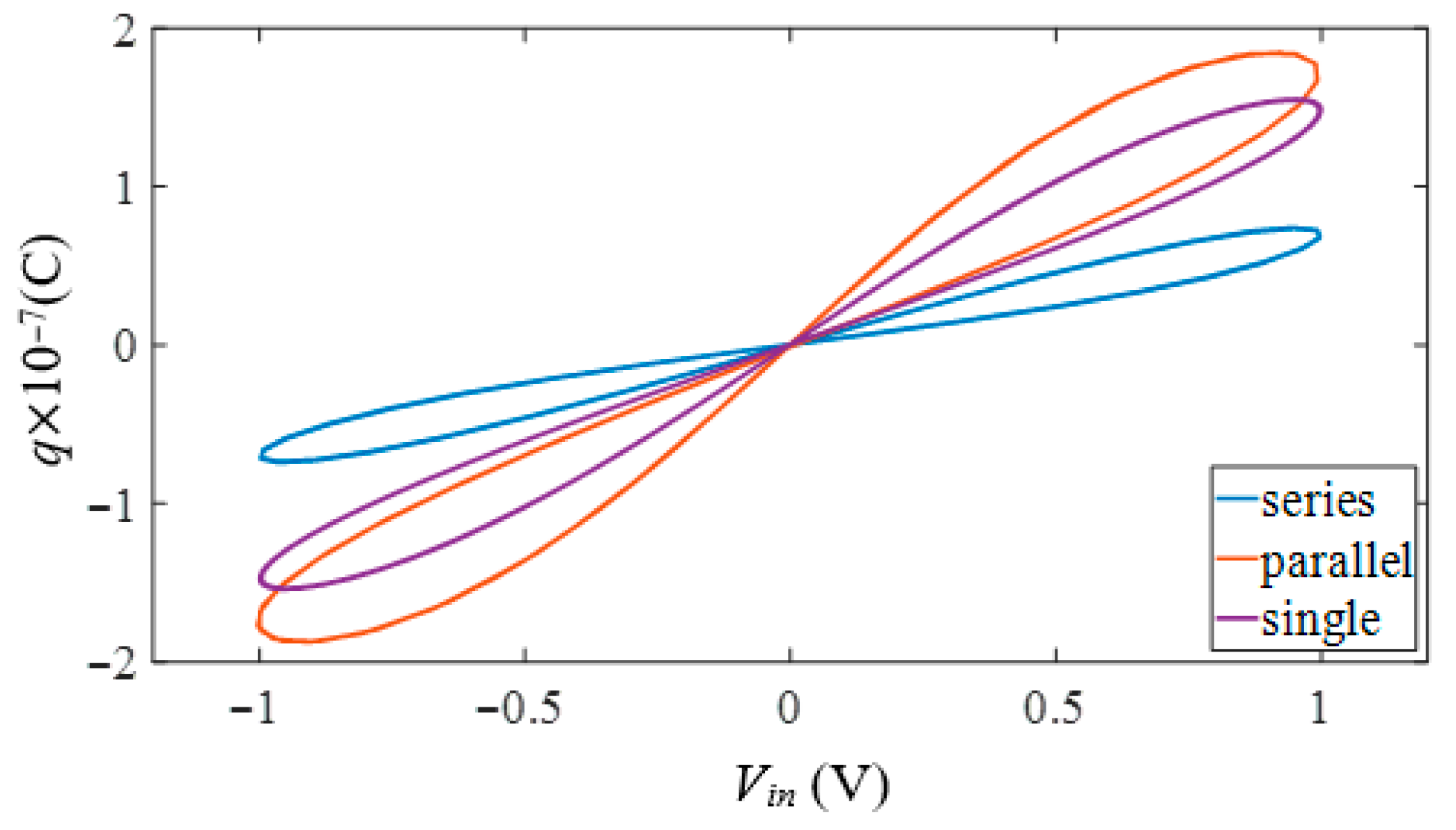

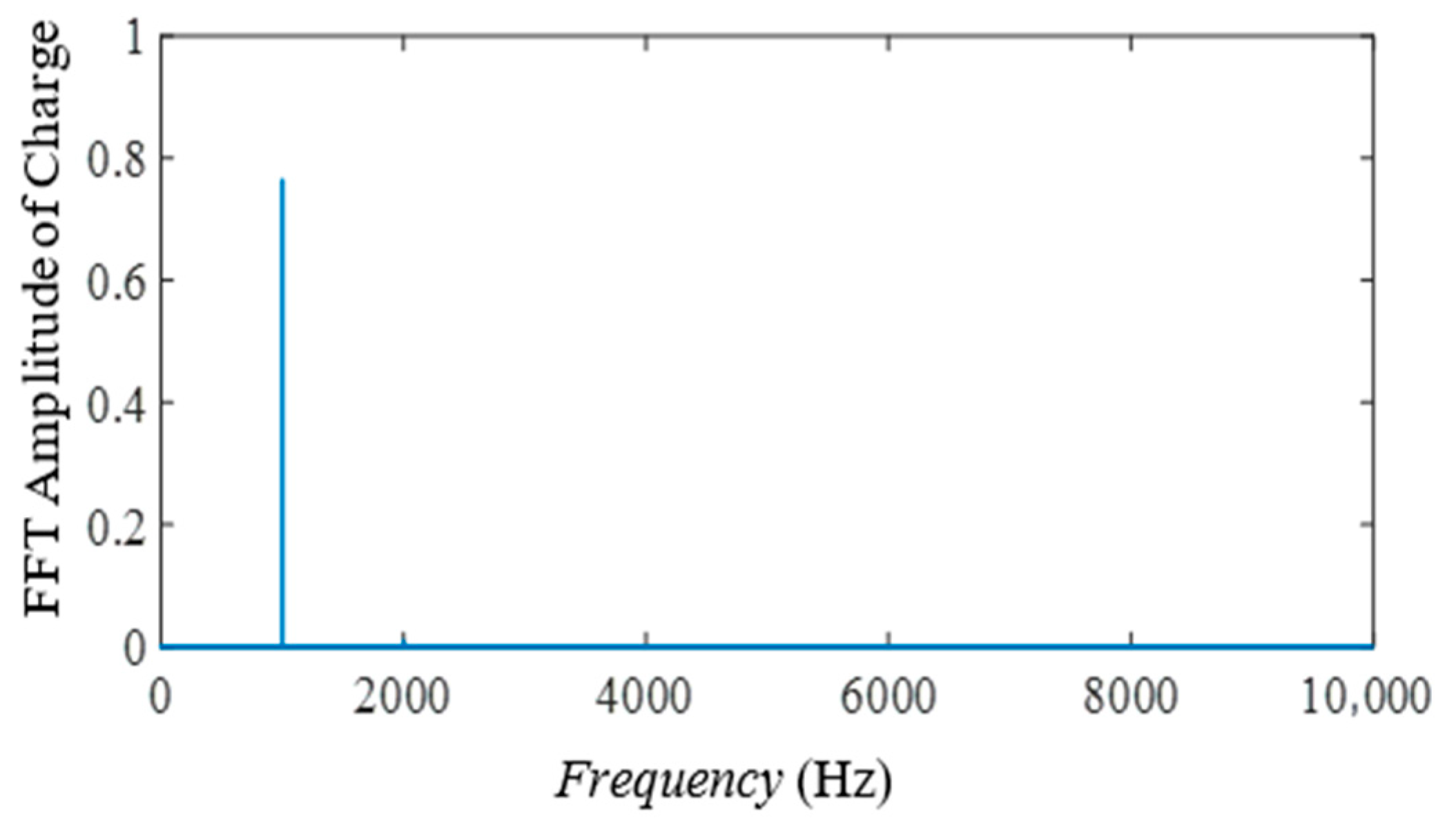

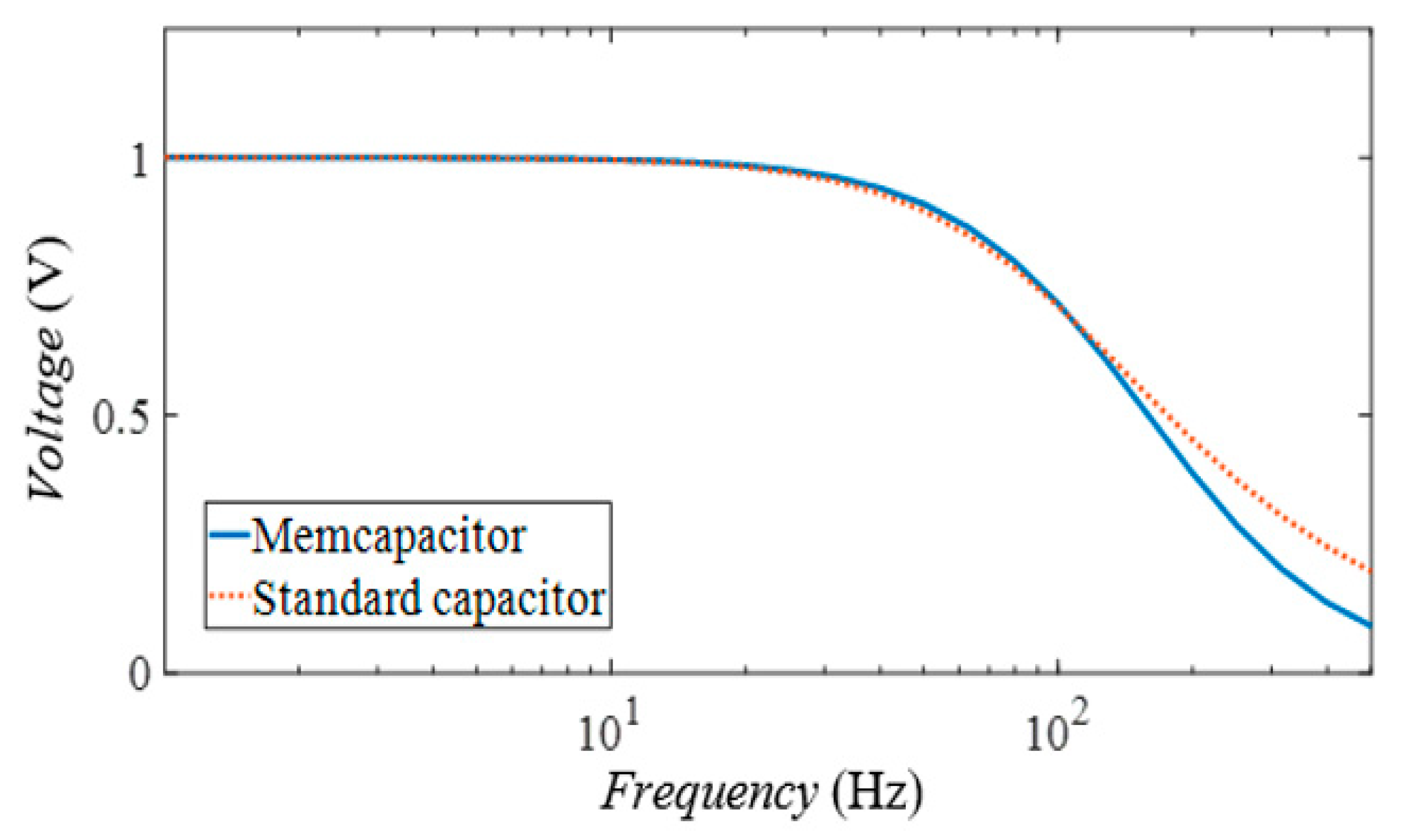

- The designed memcapacitor emulator successfully passed the tests of non-volatility, frequency-dependent variable characteristics, series-parallel connection characteristics and Fourier analysis.

- The proposed memcapacitor emulator circuit was implemented in a second-order active low-pass filter circuit and was found to be more efficient in both filtering performance and power consumption compared to the standard capacitor.

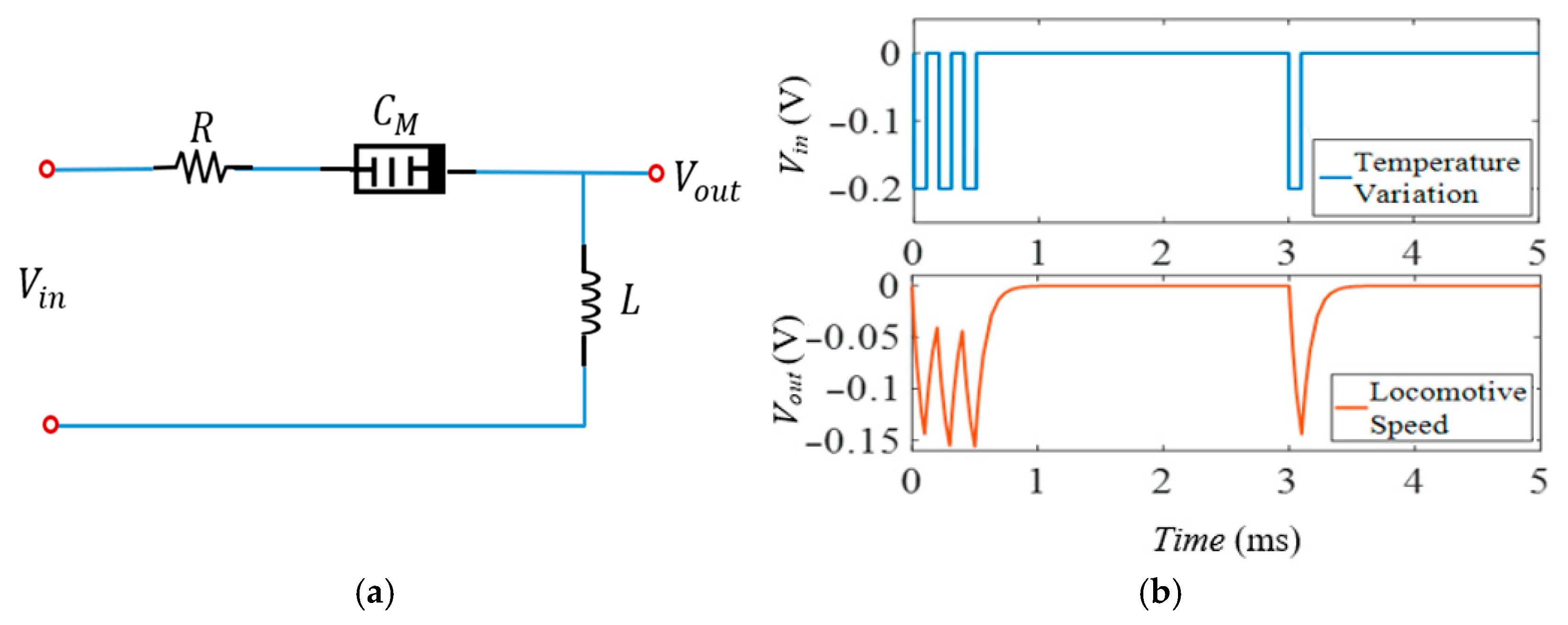

- The proposed memcapacitor emulator also successfully completed the learning and data storage tasks in the amoeba learning circuit.

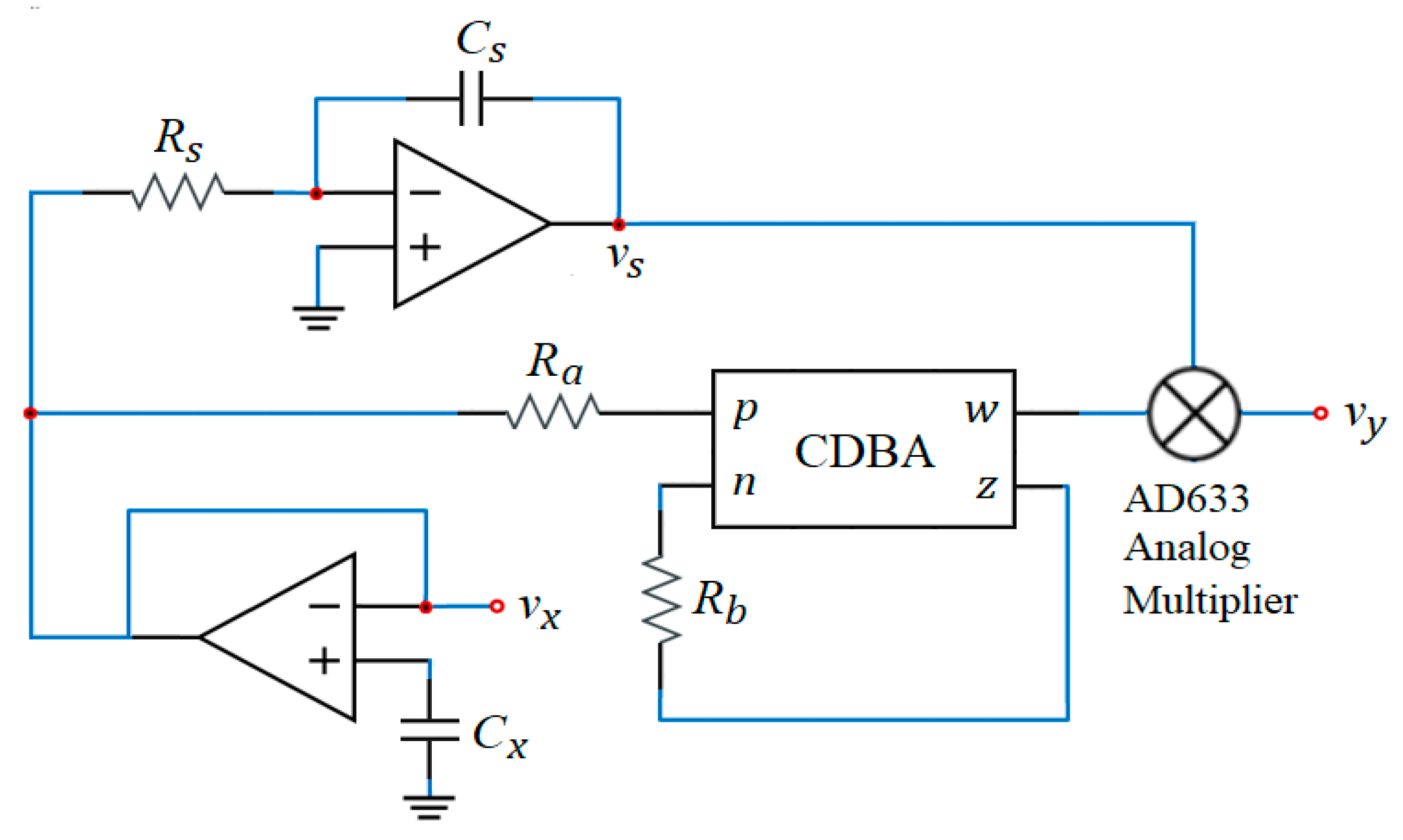

2. Proposed Memcapacitor Emulator Circuit

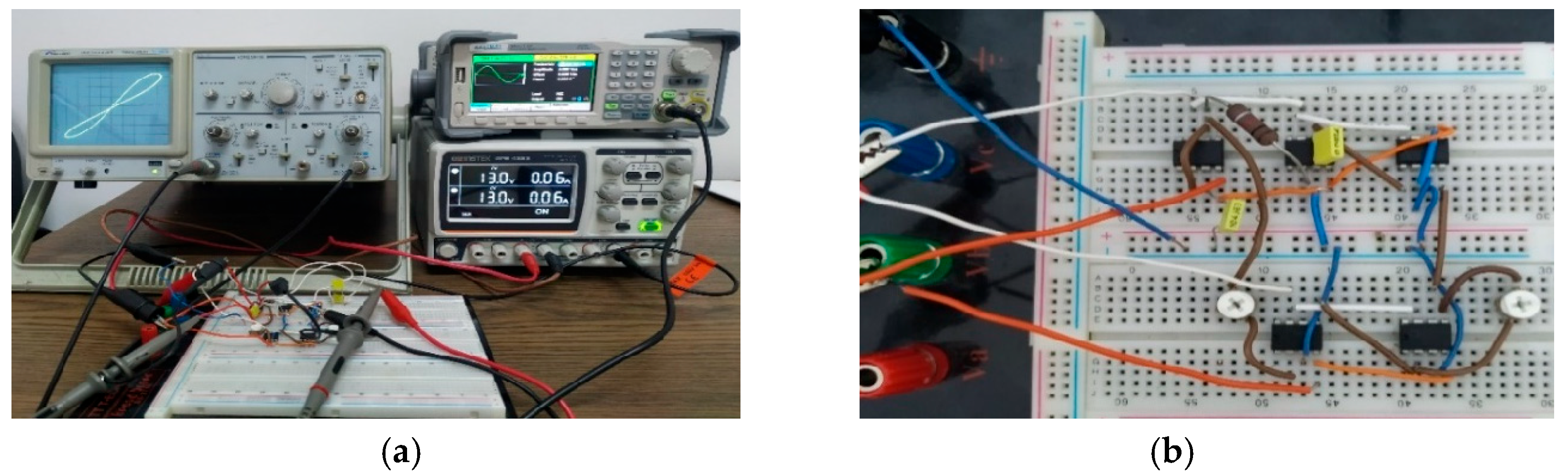

3. Simulation and Experimental Results

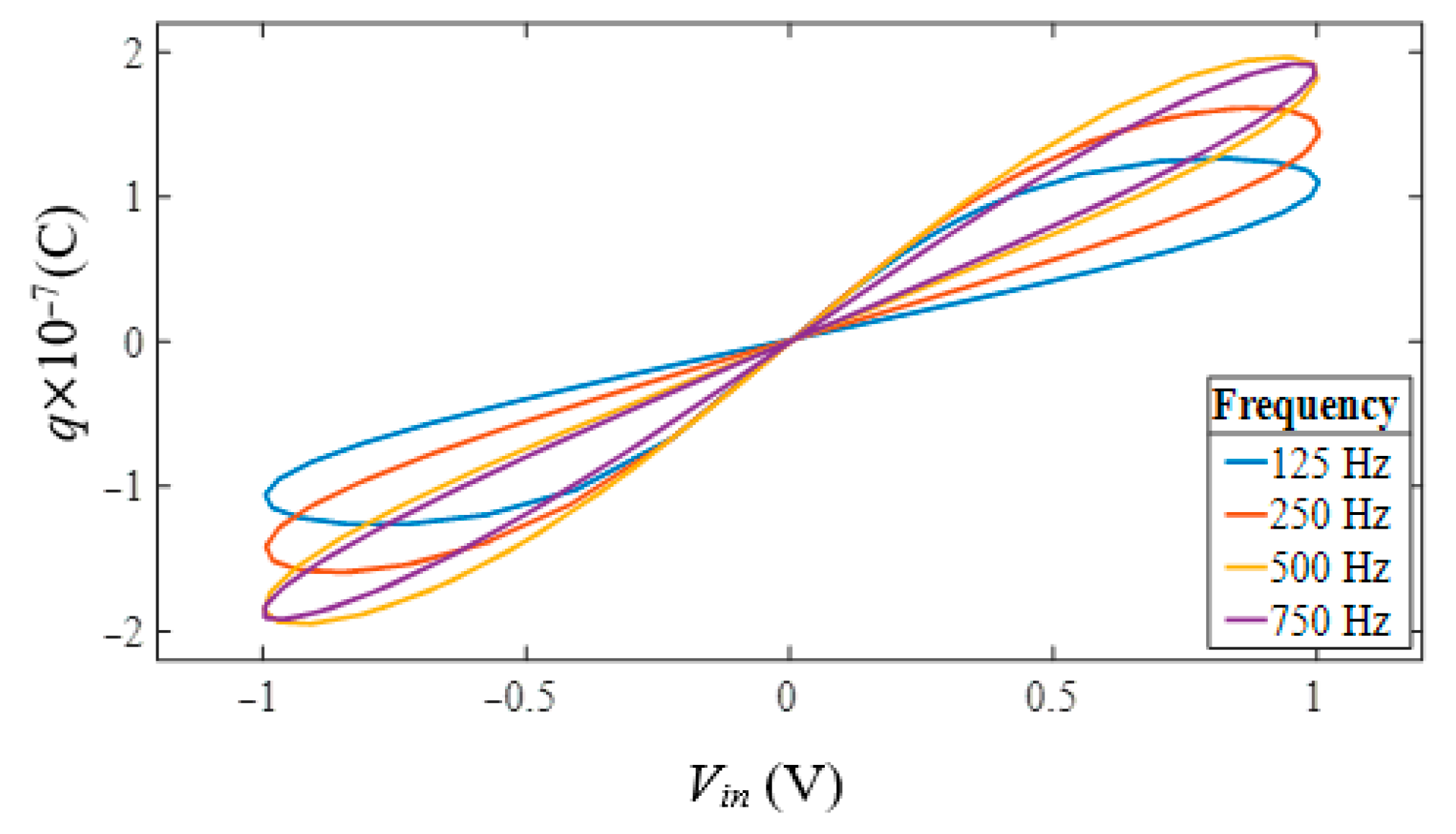

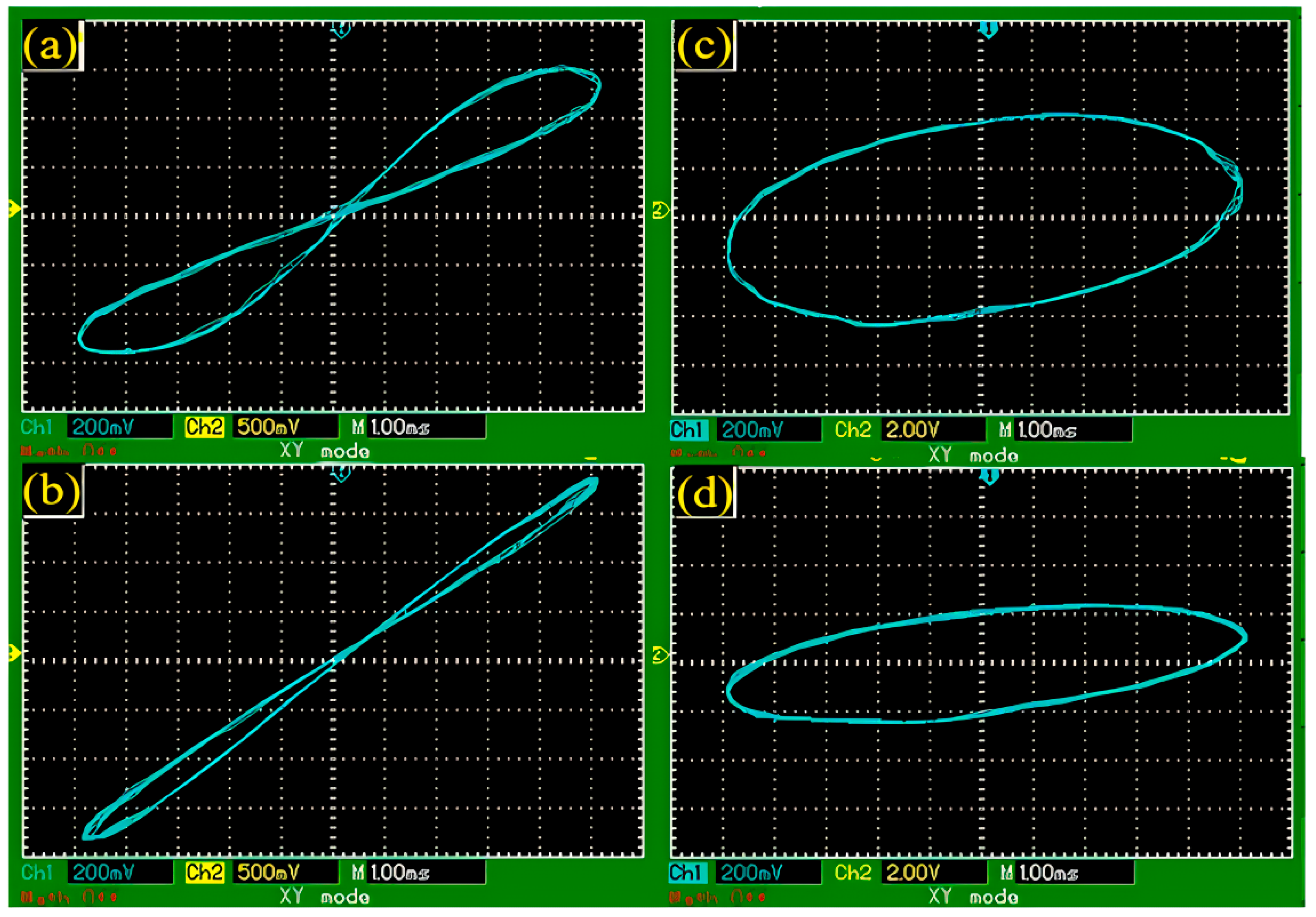

3.1. Voltage–Charge Characteristics

3.2. Non-Volatile Memory Property

3.3. Electronic Adjustability

3.4. Sensitivity Analysis

3.5. Fourier Analysis

4. Application Examples

4.1. Second-Order Active Low Pass Filter

4.2. Amoeba Learning Circuit

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Xiao, P.; Fang, J.; Wei, Z.; Dong, Y.; Du, S.; Wen, N.; Hong, Q. A Riccati Matrix Equation Solver Design Based Neurodynamics Method and Its Application. IEEE Trans. Autom. Sci. Eng. 2025, 99, 15163–15176. [Google Scholar] [CrossRef]

- Di Ventra, M.; Pershin, Y.V.; Chua, L.O. Circuit Elements with Memory: Memristors, Memcapacitors, and Meminductors. Proc. IEEE 2009, 97, 1717–1724. [Google Scholar] [CrossRef]

- Chua, L.O. Memristor—The Missing Circuit Element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- Solovyeva, E.; Schulze, S.; Harchuk, H. Behavioral Modeling of Memristor-Based Rectifier Bridge. Appl. Sci. 2021, 11, 2908. [Google Scholar] [CrossRef]

- Xia, Z.; Sun, X.; Wang, Z.; Meng, J.; Jin, B.; Wang, T. Low-Power Memristor for Neuromorphic Computing: From Materials to Applications. Nano-Micro Lett. 2025, 17, 217. [Google Scholar] [CrossRef]

- Park, S.O.; Jeong, H.; Park, J.; Bae, J.; Choi, S. Experimental Demonstration of Highly Reliable Dynamic Memristor for Artificial Neuron and Neuromorphic Computing. Nat. Commun. 2022, 13, 2888. [Google Scholar] [CrossRef]

- Nirmal, K.A.; Kumbhar, D.D.; Kesavan, A.V.; Dongale, T.D.; Kim, T.G. Advancements in 2D Layered Material Memristors: Unleashing Their Potential Beyond Memory. npj 2D Mater. Appl. 2024, 8, 83. [Google Scholar] [CrossRef]

- Chen, Y.; Zhang, T.; Li, X.; Wang, Y.; Liu, J. Hardware Implementation of Memristor-Based Artificial Neural Networks. Nat. Commun. 2024, 15, 1234. [Google Scholar] [CrossRef]

- Sangwan, V.; Lee, H.S.; Bergeron, H.; Balla, I.; Beech, H.A.; Campbell, G.P.; Gong, Y.; Ajayan, P.M.; Lauhon, L.J.; Hersam, M.C. Multi-Terminal Memtransistors from Polycrystalline Monolayer Molybdenum Disulfide. Nature 2018, 554, 500–504. [Google Scholar] [CrossRef]

- Yu, F.; Zhang, S.; Su, D.; Wu, Y.; Gracia, Y.M.; Yin, H. Dynamic Analysis and Implementation of FPGA for a New 4D Fractional-Order Memristive Hopfield Neural Network. Fractal Fract. 2025, 9, 115. [Google Scholar] [CrossRef]

- Shooshtari, M.; Jiménez Través, M.; Pahlavan, S.; Serrano-Gotarredona, T.; Linares-Barranco, B. Applying Hodgkin–Huxley Neuron Model for Perovskite Memristor in Circuit Simulation. In Proceedings of the IEEE International Conference on Metrology for eXtended Reality, Artificial Intelligence and Neural Engineering (MetroXRAINE), Benevento, Italy, 5–7 June 2024; pp. 1077–1082. [Google Scholar] [CrossRef]

- Barraj, I.; Mestiri, H.; Masmoudi, M. Overview of Memristor-Based Design for Analog Applications. Micromachines 2024, 15, 505. [Google Scholar] [CrossRef]

- Dakheel, M.M.; Hassanein, A.M.; Fouad, R.A.; Radwan, A.G. Memristor-Based Data Converter Circuits. Electronics 2023, 12, 1654. [Google Scholar]

- Fahmy, G.A.; Zorkany, M. Design of a Memristor-Based Digital to Analog Converter (DAC). Electronics 2021, 10, 622. [Google Scholar] [CrossRef]

- Minati, L.; Gambuzza, L.V.; Thio, W.J.; Sprott, J.C.; Frasca, M. A Chaotic Circuit Based on a Physical Memristor. Chaos Solitons Fractals 2020, 138, 109990. [Google Scholar] [CrossRef]

- Duan, Z.; Chen, J.; He, S.; Yu, X.; Wang, Q.; Zhang, X.; Xiong, P. A Fully Integrated Memristive Chaotic Circuit Based on Memristor Emulator with Voltage Controlled Oscillator. Micromachines 2025, 16, 246. [Google Scholar] [CrossRef] [PubMed]

- Dong, C.; Yang, M. Extreme Homogeneous and Heterogeneous Multistability in a Novel 5D Memristor-Based Chaotic System with Hidden Attractors. Fractal Fract. 2024, 8, 266. [Google Scholar] [CrossRef]

- Qian, K.; Xiao, Y.; Wei, Y.; Liu, D.; Wang, Q.; Feng, W. A Robust Memristor-Enhanced Polynomial Hyper-Chaotic Map and Its Multi-Channel Image Encryption Application. Micromachines 2023, 14, 2090. [Google Scholar] [CrossRef]

- Hong, Q.; Jiang, H.; Xiao, P.; Du, S.; Li, T. A Parallel Computing Scheme Utilizing Memristor Crossbars for Fast Corner Detection and Rotation Invariance in the ORB Algorithm. IEEE Trans. Comput. 2025, 74, 996–1010. [Google Scholar] [CrossRef]

- Reynolds, J.; Lenz, G.; Tarigopula, A.; Green, D. A Scalable, Multi Core, Multi Function, Integrated CMOS/Memristor Sensor Interface for Neural Sensing Applications. Electronics 2025, 14, 30. [Google Scholar] [CrossRef]

- Chae, M.; Lee, D.; Kim, H.-D. Low-Power Consumption IGZO Memristor-Based Gas Sensor Embedded in an Internet of Things Monitoring System for Isopropanol Alcohol Gas. Micromachines 2024, 15, 77. [Google Scholar] [CrossRef]

- Odebowale, A.A.; Berhe, A.M.; Hattori, H.T.; Miroshnichenko, A.E. Modeling and Analysis of a Radiative Thermal Memristor. Appl. Sci. 2024, 14, 2633. [Google Scholar] [CrossRef]

- Biolek, D.; Biolek, Z.; Biolková, V. Coupled Memristors, Memcapacitors, and Meminductors and Their Fingerprints. AEÜ Int. J. Electron. Commun. 2018, 97, 263–266. [Google Scholar] [CrossRef]

- Biolek, D.; Biolek, Z.; Biolková, V. SPICE Modeling of Memristive, Memcapacitative and Meminductive Systems. In Proceedings of the European Conference on Circuit Theory and Design (ECCTD), Antalya, Turkey, 23–27 August 2009; pp. 249–252. [Google Scholar] [CrossRef]

- Di Ventra, M.; Pershin, Y.V. The Parallel Approach. Nat. Phys. 2013, 9, 200–202. [Google Scholar] [CrossRef]

- Wang, F.; Wang, F. Floating Memcapacitor Based on Knowm Memristor and Its Dynamic Behaviors. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 5134–5138. [Google Scholar] [CrossRef]

- Liu, X.; Mou, J.; Wang, J.; Banerjee, S.; Li, P. Dynamical Analysis of a Novel Fractional-Order Chaotic System Based on Memcapacitor and Meminductor. Fractal Fract. 2022, 6, 671. [Google Scholar] [CrossRef]

- Wang, X.; Cao, Y.; Li, H.; Li, B. A Chaos-Enhanced Fractional-Order Chaotic System with Self-Reproduction Based on Memcapacitor and Meminductor. Fractal Fract. 2023, 7, 582. [Google Scholar] [CrossRef]

- Guo, M.; Yang, R.; Zhang, M.; Dou, G. A Novel Memcapacitor and Its Application in a Chaotic Circuit. Nonlinear Dyn. 2021, 105, 123–138. [Google Scholar] [CrossRef]

- Chen, G.; Yuan, F.; Dou, G.; Li, Y.; Wang, G. Complex Dynamics in a Memcapacitor-Based Chaotic Circuit. Entropy 2019, 21, 188. [Google Scholar] [CrossRef]

- Ishisaki, Y.; Oshio, R.; Kuwahara, T.; Shintani, M.; Tokumitsu, E.; Matsuda, T.; Kawanishi, H.; Nakashima, Y.; Kimura, M. Analog Memcapacitor by Ferroelectric Capacitor and Its Application to Spiking Neuromorphic System. IEEE Trans. Electron Devices 2024, 71, 4626–4630. [Google Scholar] [CrossRef]

- Van De Burgt, Y.; Melianas, A.; Keene, S.T.; Malliaras, G.G.; Salleo, A.; Tiberj, A.; Gerstner, W.; Zampieri, G.; Zenobi, G. Energy-Efficient Memcapacitor Devices for Neuromorphic Computing. Nat. Electron. 2021, 4, 740–747. [Google Scholar] [CrossRef]

- Hossain, R.; Mohamed, A.S.; Armendarez, N.X.; Najem, J.S.; Hasan, M.S. Biomembrane-Based Memcapacitive Reservoir Computing System for Energy Efficient Temporal Data Processing. arXiv 2023, arXiv:2305.12025. [Google Scholar] [CrossRef]

- Singh, A.; Kim, D.; Lee, B.-G. Analysis of a Memcapacitor-Based Neural Network Accelerator Framework. arXiv 2025, arXiv:2502.00027. [Google Scholar] [CrossRef]

- Zhang, Z.; Pershin, Y.V.; Martin, I. Electromechanical Memcapacitive Neurons for Energy-Efficient Spiking Neural Networks. arXiv 2023, arXiv:2304.10899. [Google Scholar] [CrossRef]

- Min, J.; Kang, S.; Kim, S. Memcapacitor-Based Minimum and Maximum Logic Gate Design. In Proceedings of the 2021 18th International SoC Design Conference (ISOCC), Jeju Island, Republic of Korea, 6–9 October 2021; pp. 1–4. [Google Scholar]

- Tran, D.; Teuscher, C. Memcapacitive Devices in Logic and Crossbar Applications. arXiv 2017, arXiv:1704.05921. [Google Scholar] [CrossRef]

- Cam Taskiran, Z.G.; Sagbas, M.; Ayten, U.E.; Sedef, H. A New Universal Mutator Circuit for Memcapacitor and Meminductor Elements. AEÜ Int. J. Electron. Commun. 2020, 119, 153180. [Google Scholar] [CrossRef]

- Sharma, P.K.; Ranjan, R.K.; Khateb, F.; Kumngern, M. Charge Controlled MEM-Element Emulator and Its Application in a Chaotic System. IEEE Access 2020, 8, 171397–171407. [Google Scholar] [CrossRef]

- Yesil, A.; Babacan, Y. Electronically Controllable Memcapacitor Circuit with Experimental Results. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 1443–1447. [Google Scholar] [CrossRef]

- Ananda, R.Y.; Satyanarayan, G.S.; Trivedi, G. A High Frequency MOS-Based Floating Charge-Controlled Memcapacitor Emulator. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 1189–1193. [Google Scholar] [CrossRef]

- Vista, J.; Ranjan, A. Simple Charge Controlled Floating Memcapacitor Emulator Using DXCCDITA. Analog Integr. Circuits Signal Process. 2020, 104, 37–46. [Google Scholar] [CrossRef]

- Corinto, F.; Civalleri, P.P.; Chua, L.O. A Theoretical Approach to Memristor Devices. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 123–132. [Google Scholar] [CrossRef]

- Korkmaz, M.O.; Babacan, Y.; Yesil, Y. A New Floating Memcapacitor Emulator Circuit without Using Passive Elements. Int. J. Circuit Theory Appl. 2024, 52, 3650–3663. [Google Scholar] [CrossRef]

- Acar, C.; Ozoguz, S. A New Versatile Building Block: Current Differencing Buffered Amplifier Suitable for Analog Signal Processing Filters. Microelectron. J. 1999, 30, 157–160. [Google Scholar] [CrossRef]

- Ozoguz, S.; Toker, A.; Ibrahim, M.A. A New Versatile Building Block: Current Differencing Buffered Amplifier and Its Applications. In Proceedings of the 1999 European Conference on Circuit Theory and Design (ECCTD’99), Stresa, Italy, 29 August–2 September 1999; pp. 1187–1190. [Google Scholar]

- Biolek, D.; Senani, R.; Biolková, V.; Kolka, Z. Active Elements for Analog Signal Processing: Classification, Review, and New Proposals. Radioengineering 2008, 17, 15–32. [Google Scholar]

- Wilson, B. Recent Developments in Current Conveyors and Current-Mode Circuits. IEE Proc. G Circ. Devices Syst. 1990, 137, 63–77. [Google Scholar] [CrossRef]

- Ayten, U.E.; Sagbas, M.; Sedef, H. Current Mode Leapfrog Ladder Filters Using a New Active Block. Int. J. Electron. Commun. (AEÜ) 2010, 64, 503–511. [Google Scholar] [CrossRef]

- Sedra, A.S.; Smith, K.C. A Second-Generation Current Conveyor and Its Applications. IEEE Trans. Circ. Theory 1970, 17, 132–134. [Google Scholar] [CrossRef]

- Oner, S.E. Design of Active Filters Using a New Active Device CDBA. Master’s Thesis, Council of Higher Education, Ankara, Turkey, 2007. [Google Scholar]

- Ozcan, S.; Toker, A.; Acar, C.; Kuntman, H.; Cicekoglu, O. Single Resistance-Controlled Sinusoidal Oscillators Employing Current Differencing Buffered Amplifier. Microelectron. J. 2000, 31, 169–174. [Google Scholar] [CrossRef]

- Kaewpoonsuk, A.; Petchmaneelumka, W.; Kamsri, T.; Riewruja, V. Realization of OTA-Based CDBA. In Proceedings of the International Conference on Control, Automation and Systems (ICCAS), KINTEX, Bucheon, Republic of Korea, 2–5 June 2005. [Google Scholar]

- Borah, S.S.; Sundaravadivel, P. A Review of Current Differencing Buffered Amplifiers: Performance Metrics and Technological Advances. Electronics 2024, 13, 3623. [Google Scholar] [CrossRef]

- Babacan, Y. Ultra-Low Voltage and Low-Power Voltage-Mode DTMOS-Based Four-Quadrant Analog Multiplier. Analog Integr. Circuits Signal Process. 2019, 99, 39–45. [Google Scholar] [CrossRef]

- Kaya, Z. Implementation of Fast Fourier Transform on Programmable Gate Arrays. Ph.D. Thesis, Council of Higher Education, Ankara, Turkey, 2021. [Google Scholar]

- Yu, D.; Zhao, X.; Sun, T.; Iu, H.H.C.; Fernando, T. A Simple Floating Mutator for Emulating Memristor, Memcapacitor, and Meminductor. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1334–1338. [Google Scholar] [CrossRef]

- Korkmaz, M.O.; Yeşil, A. FDCCII Tabanlı, Elektronik Olarak Ayarlanabilir Yeni Bir Memkapasitör Emülatör Devresi. Mühendis. Bilim. Ve Araştırmaları Derg. 2023, 5, 127–134. [Google Scholar] [CrossRef]

- Pershin, Y.V.; Di Ventra, M. Emulation of Floating Memcapacitors and Meminductors Using Current Conveyors. Electron. Lett. 2011, 47, 243–244. [Google Scholar] [CrossRef]

- Korkmaz, M.O.; Babacan, Y.; Yesil, A. Mutator Circuit for Memcapacitor Emulator Using Operational Transconductance Amplifiers. Elektron. Ir Elektrotechnika 2024, 30, 38402. [Google Scholar] [CrossRef]

| Frequency | Cm Range | |

|---|---|---|

| With Simulation | With Experiment | |

| Parameters | Range Simulation | Range Experimental | |

|---|---|---|---|

| Parameters | Range Simuation | Range Experimental | |

|---|---|---|---|

| Parameters | Upper Frequency Limit | |

|---|---|---|

| Sensitivity Analysis | |

|---|---|

| −1 | |

| 1 | |

| −1 | |

| −1 | |

| −2 |

| Ref. | Components | Complexity | Frequency Performance | Floating/Grounded | Sim/Exp. | Electronic Control | Cost |

|---|---|---|---|---|---|---|---|

| [40] | 2 CCII, 1 AM 1 R, 3 C | Medium | Grounded | Simulation Experimental | Yes | Medium | |

| [41] | 1 VDTA,1 OTA,1 buffer, 1 R, 2 C | Medium | Floating | Simulation Experimental | No | Medium | |

| [57] | 4 CCII, 1 Opamp, 1 Varactor Diode, 6 R, 2 C | High | Floating | Simulation Experimental | No | High | |

| [58] | 1 FDCCII, 1 AM, 2 MOSFETs, 3 C | Medium | Grounded | Simulation Only | Yes | Medium | |

| [59] | 4 CCII, 1 Memristor, 1 L1 R | High | Not specified | Floating | Simulation Only | No | High |

| This study | 1 CDBA, 2 opamp, 1 AM, 3 R, 2 C | Medium | Floating | Simulation Experimental | Yes | Medium |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gursul Kalac, S.; Cam Taskiran, Z.G.; Hamamci, S.E. An Electronically Adjustable Floating Memcapacitor Emulator Circuit Using CDBA. Appl. Sci. 2025, 15, 7506. https://doi.org/10.3390/app15137506

Gursul Kalac S, Cam Taskiran ZG, Hamamci SE. An Electronically Adjustable Floating Memcapacitor Emulator Circuit Using CDBA. Applied Sciences. 2025; 15(13):7506. https://doi.org/10.3390/app15137506

Chicago/Turabian StyleGursul Kalac, Sevgi, Zehra Gulru Cam Taskiran, and Serdar Ethem Hamamci. 2025. "An Electronically Adjustable Floating Memcapacitor Emulator Circuit Using CDBA" Applied Sciences 15, no. 13: 7506. https://doi.org/10.3390/app15137506

APA StyleGursul Kalac, S., Cam Taskiran, Z. G., & Hamamci, S. E. (2025). An Electronically Adjustable Floating Memcapacitor Emulator Circuit Using CDBA. Applied Sciences, 15(13), 7506. https://doi.org/10.3390/app15137506