Ku-Band CMOS Power Amplifier with Three-Stack Power Stage to Enhance Output Power and Efficiency

Abstract

:1. Introduction

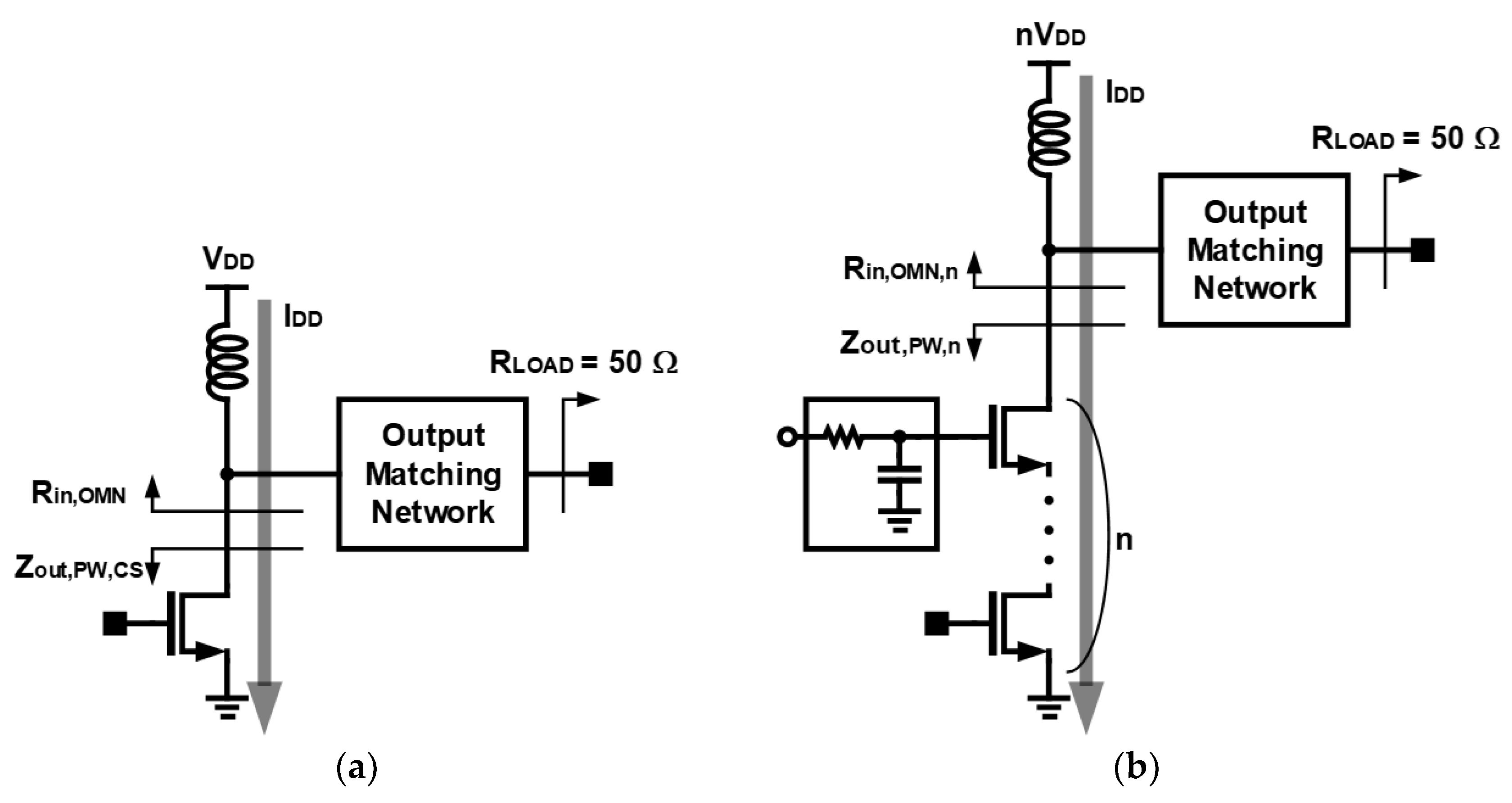

2. Typical CMOS Power Amplifiers

2.1. Common-Source Structure

2.2. Stack Structure

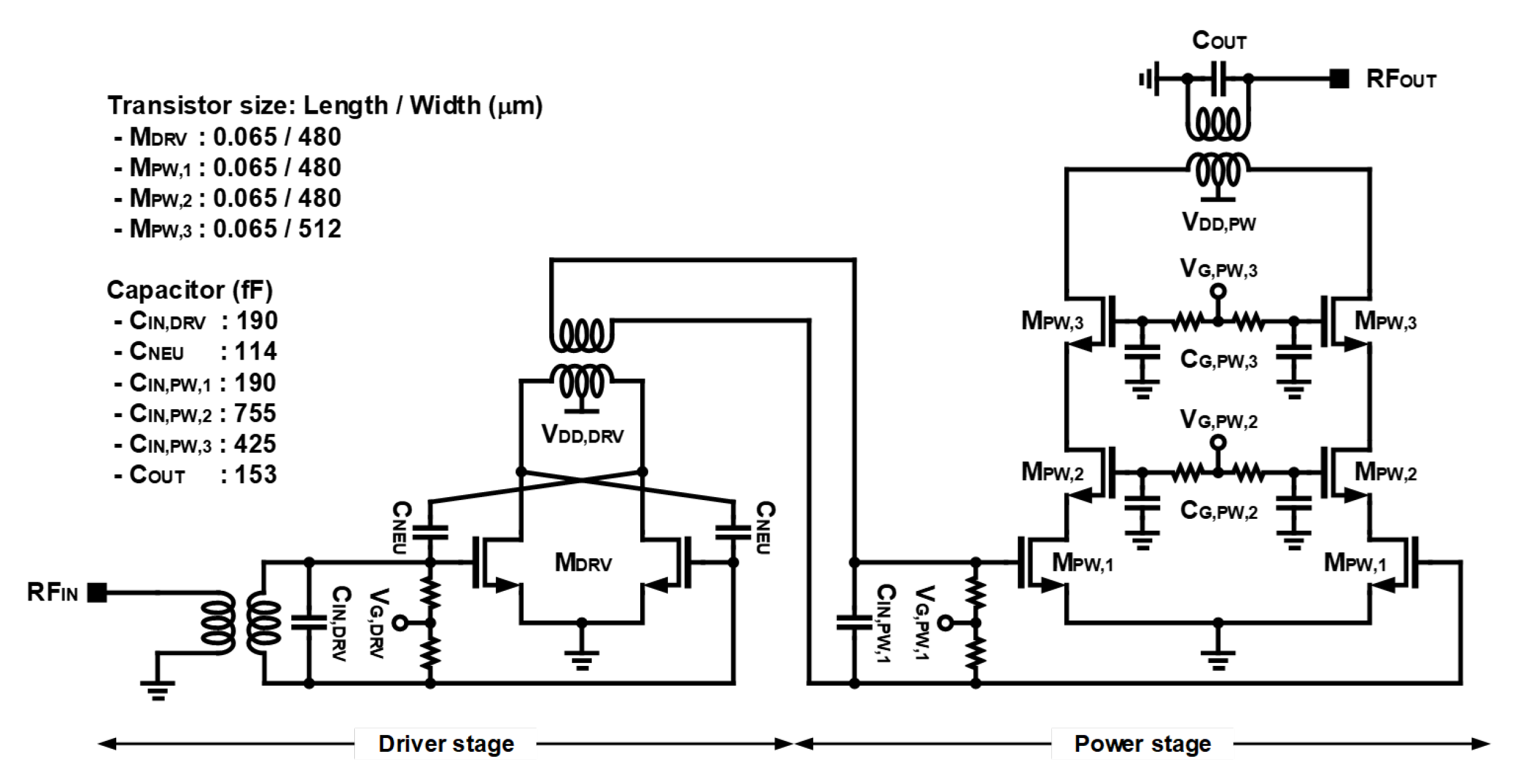

3. Proposed Power Amplifier

4. Design of the Proposed Power Amplifier

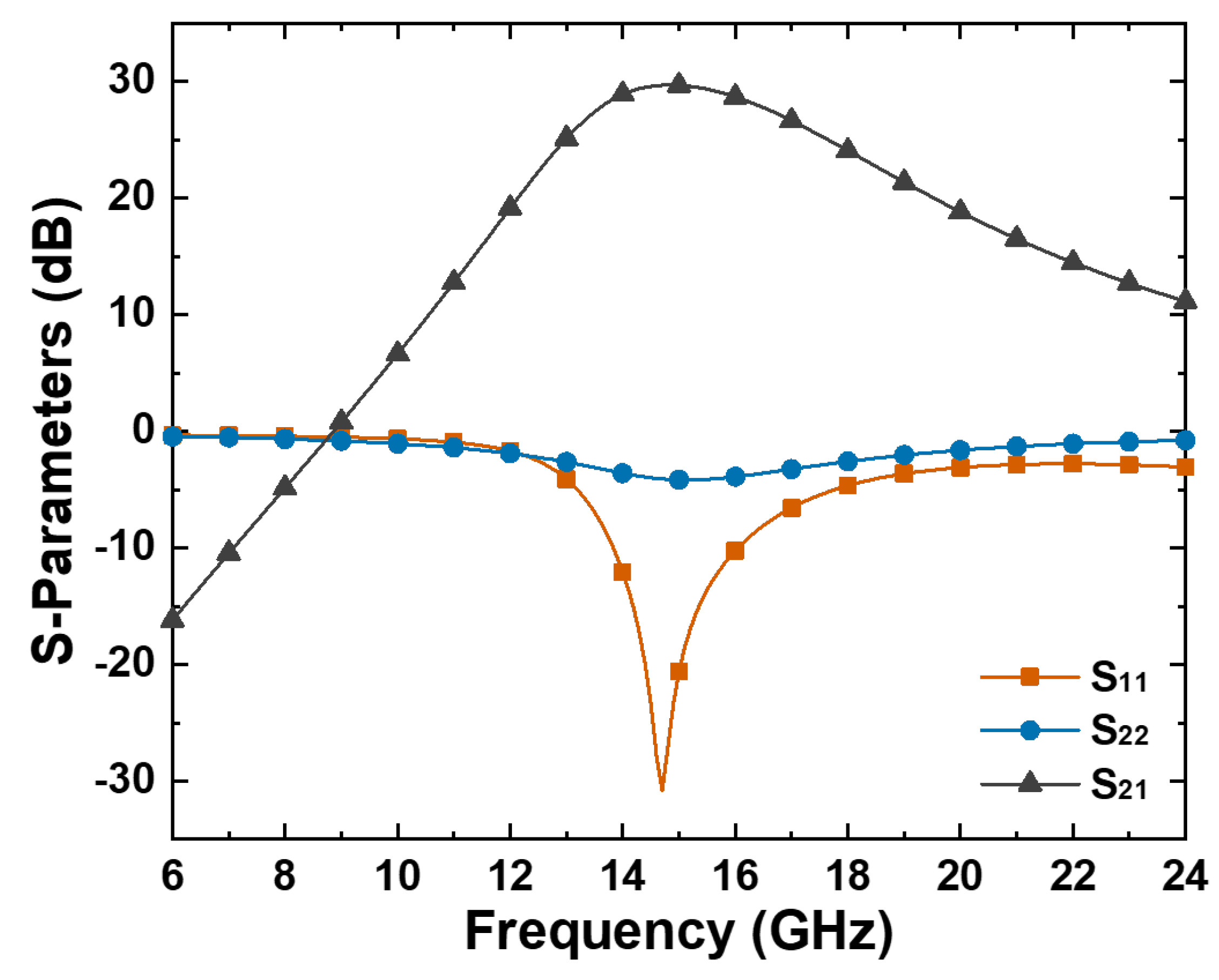

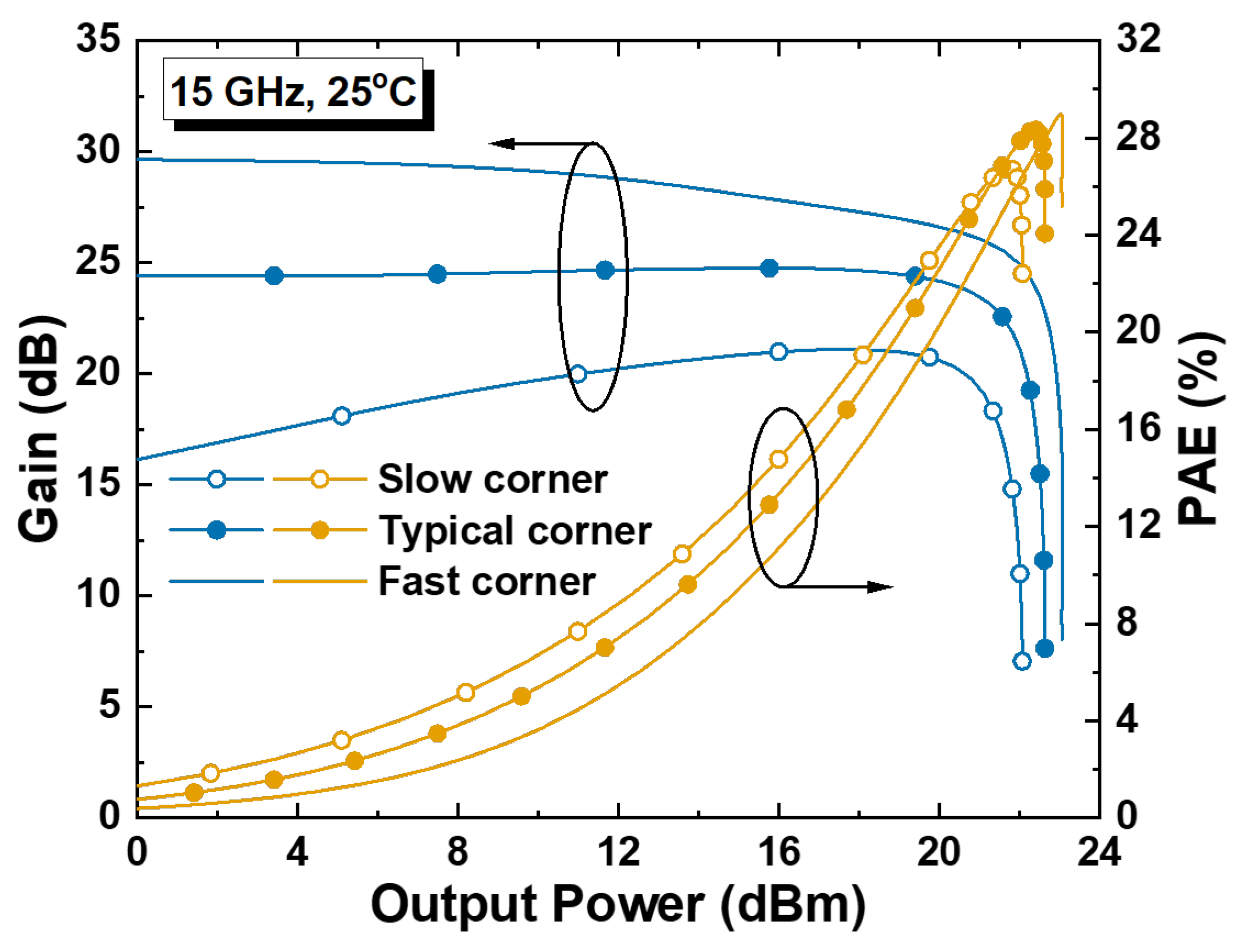

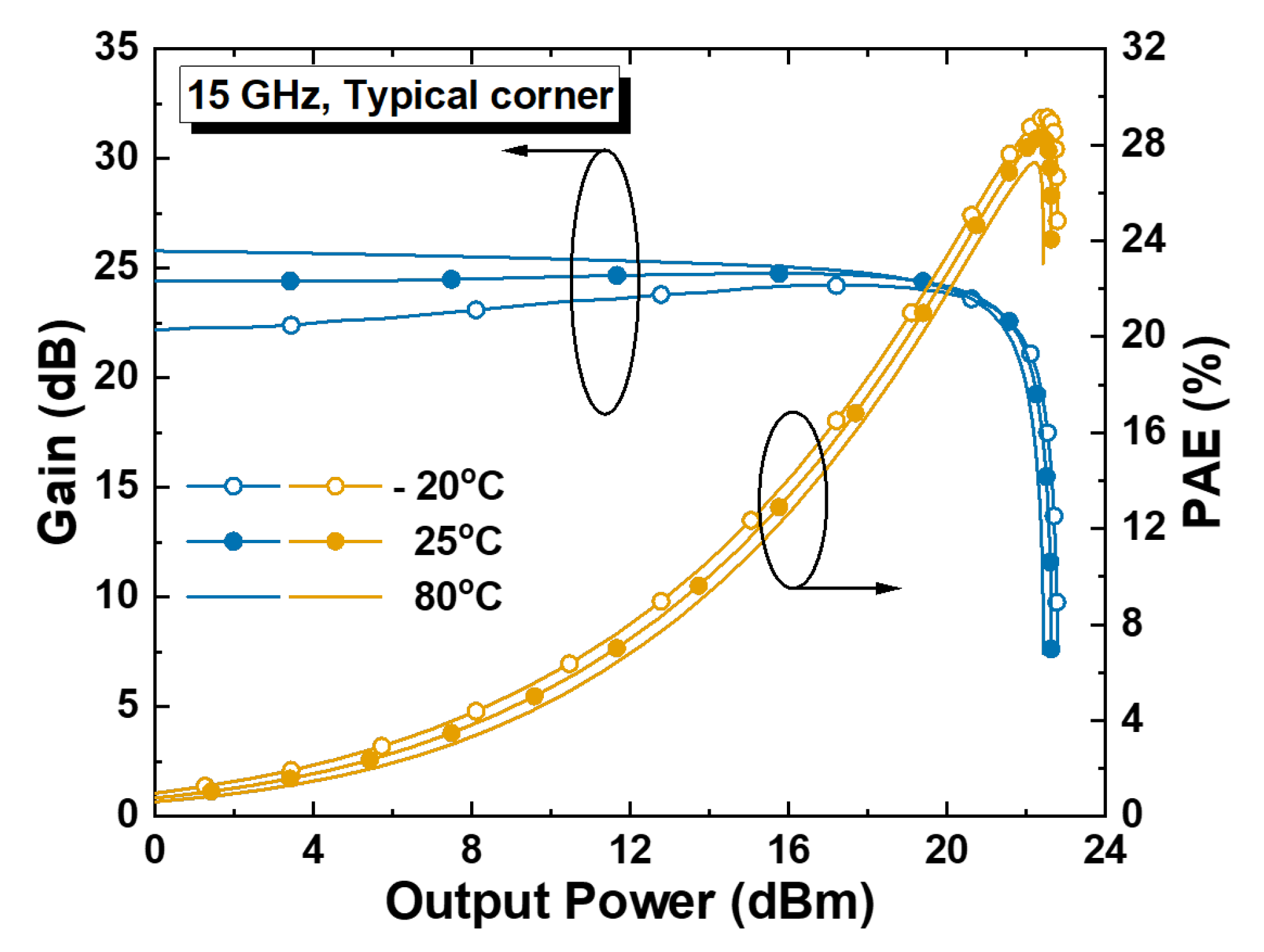

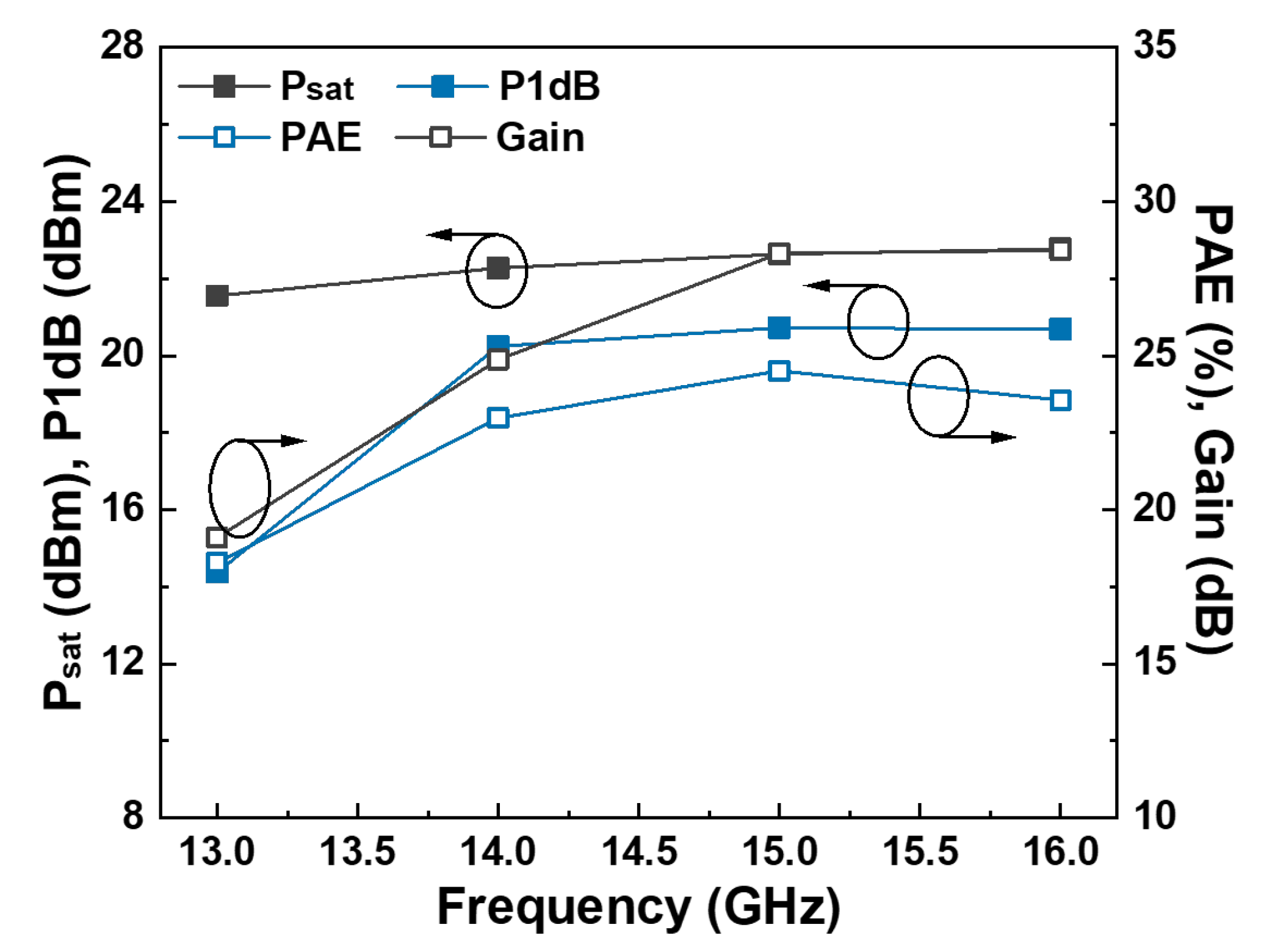

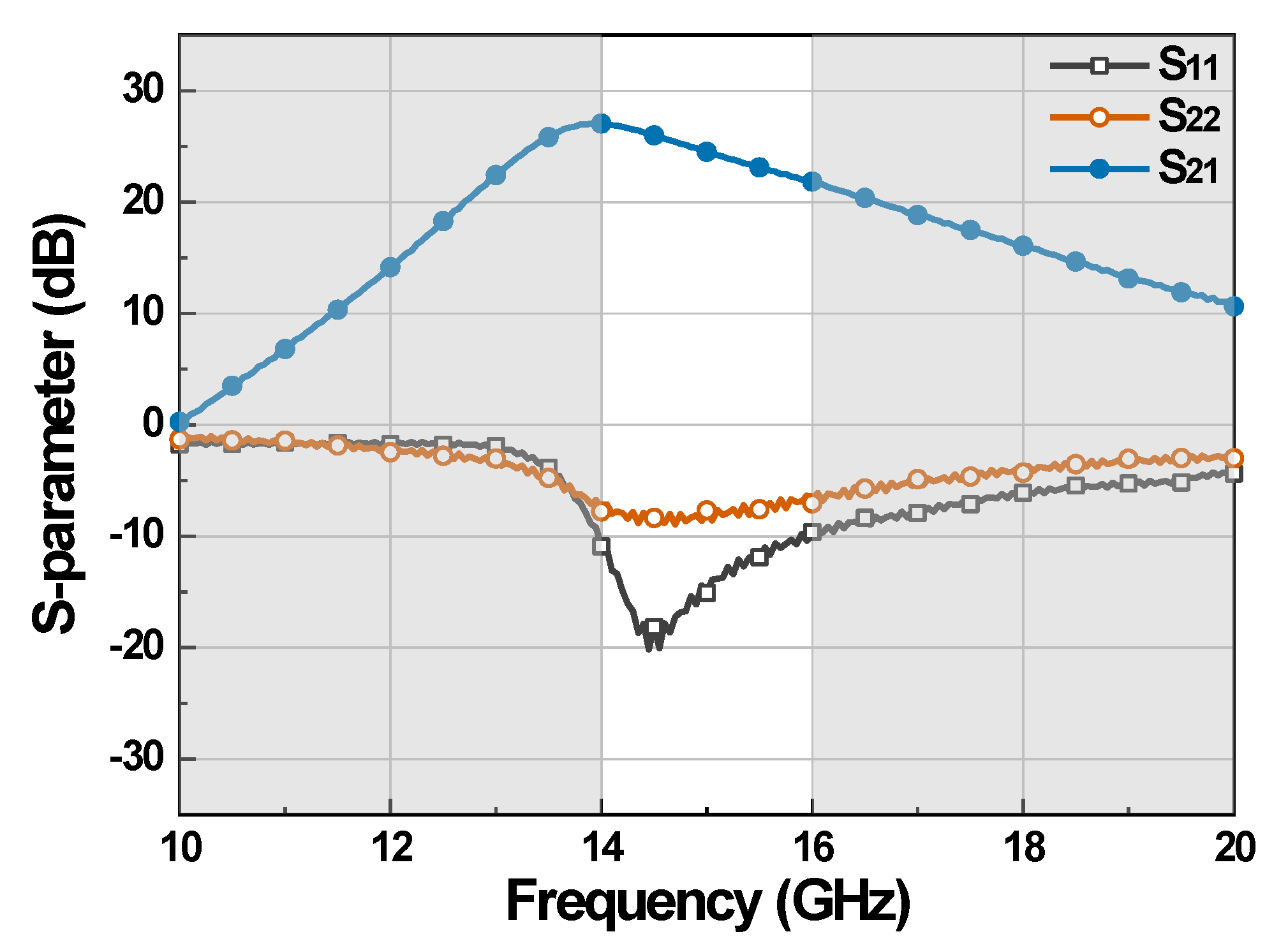

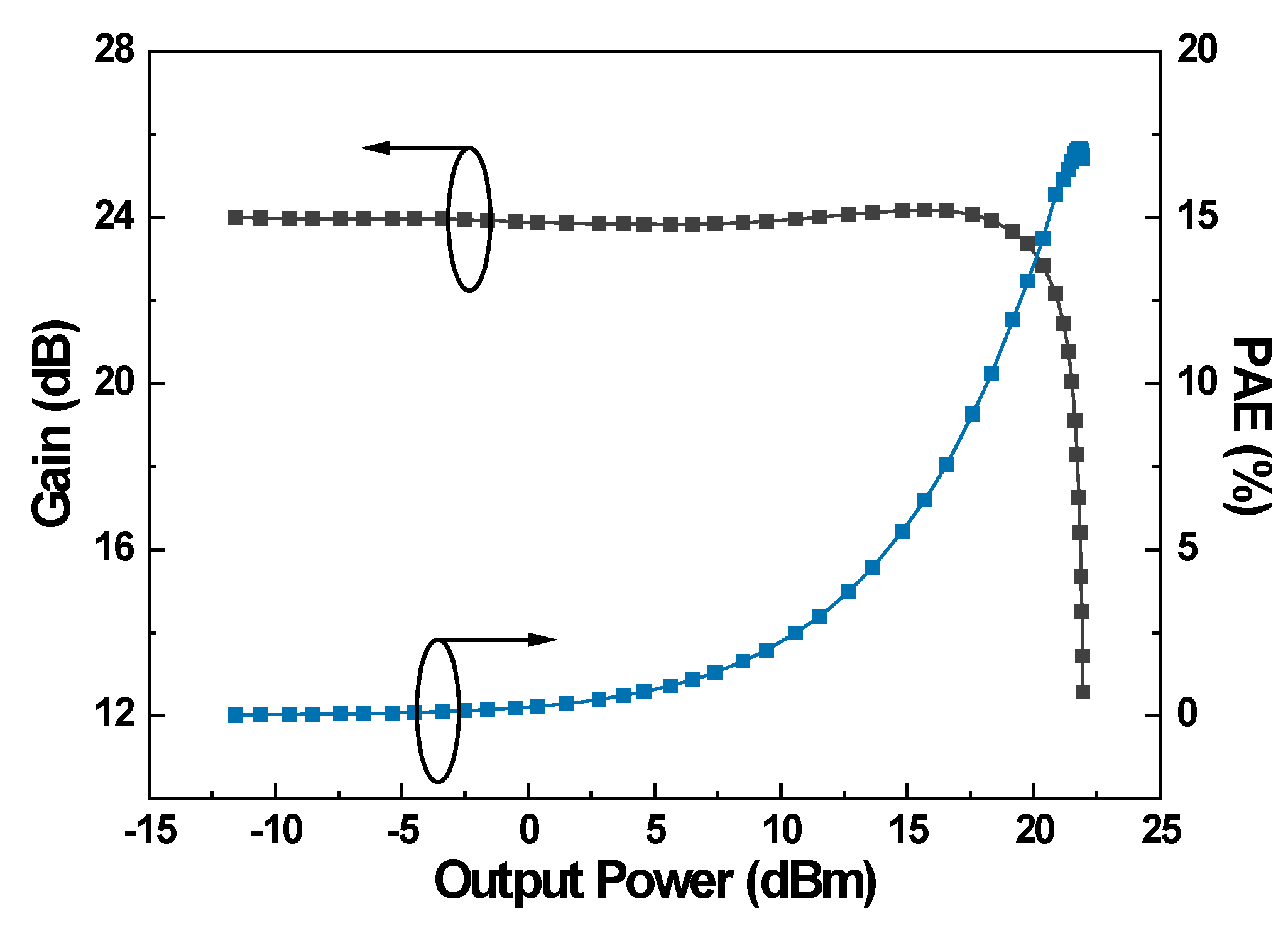

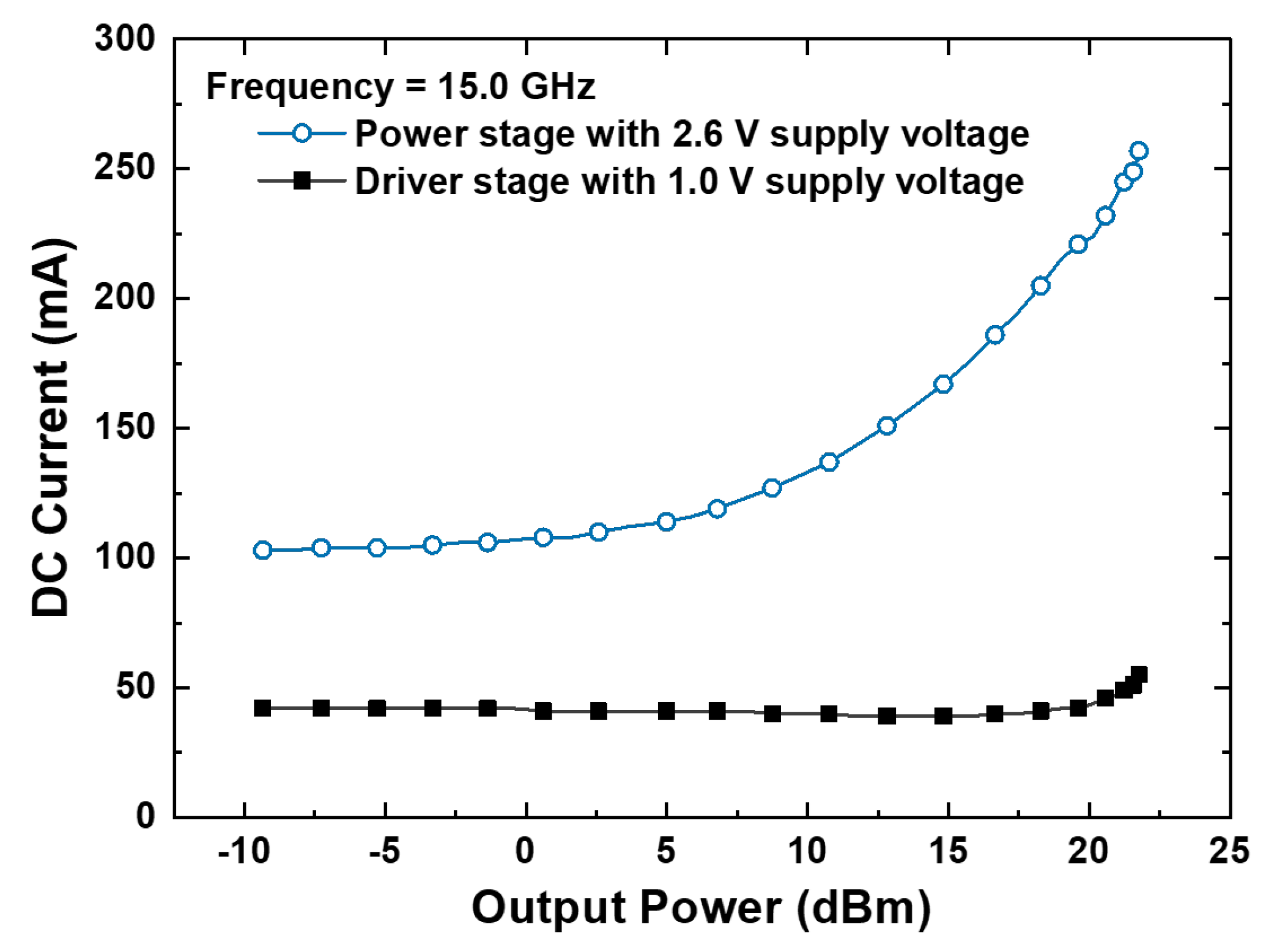

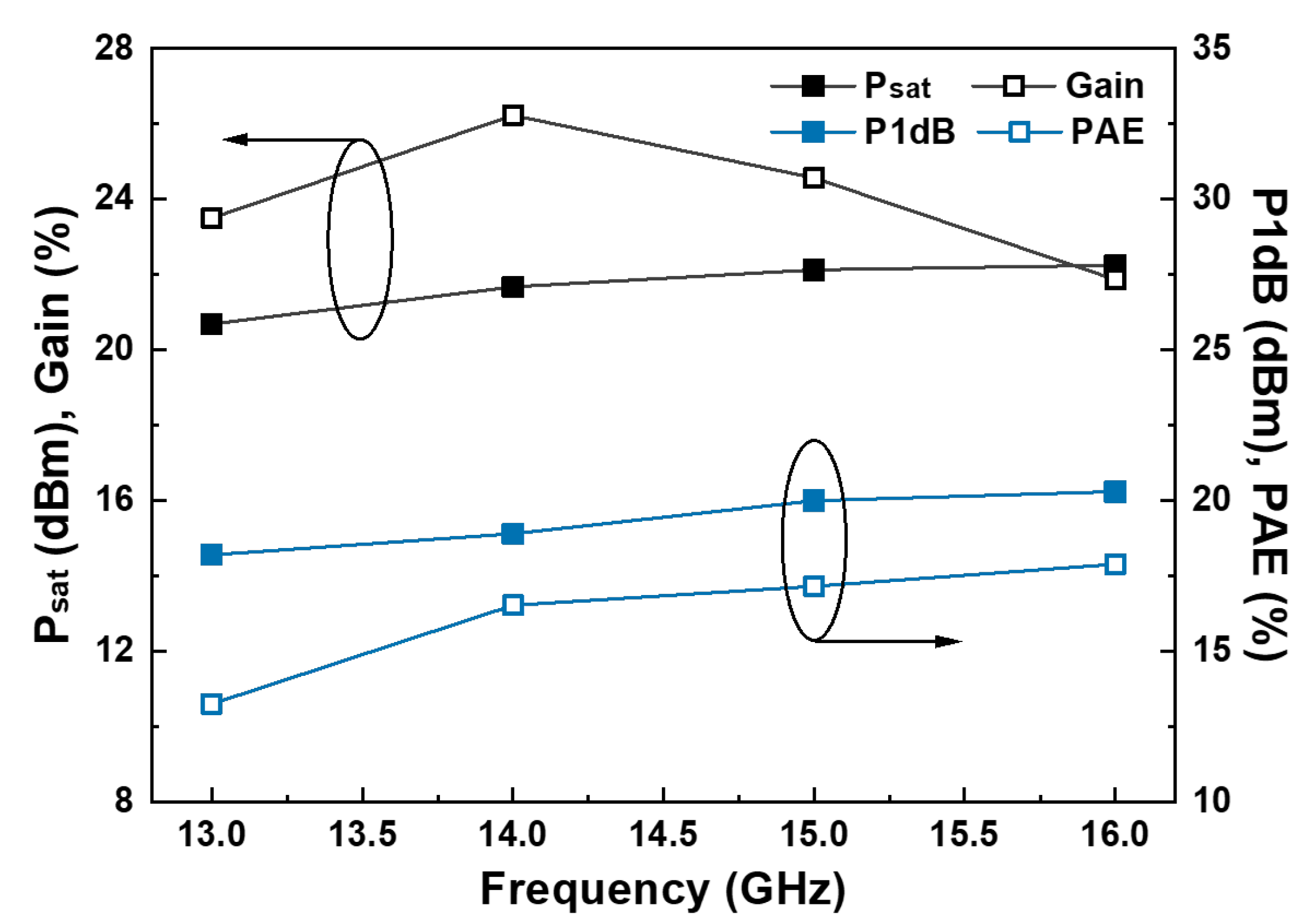

5. Measurement Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Cho, G.; Jeong, G.; Hong, S. 28-GHz CMOS power amplifier linearized with resistive drain-body connection. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 876–879. [Google Scholar] [CrossRef]

- Ding, B.; Yuan, S.; Zhao, C.; Tao, L.; Tian, T. A Ka band FMCW transceiver front-end with 2-GHz bandwidth in 65-nm CMOS. IEEE Trans. Circuits Syst. II-Express Briefs 2019, 66, 212–216. [Google Scholar] [CrossRef]

- Jia, H.; Prawoto, C.C.; Chi, B.; Wang, Z.; Yue, C.P. A full Ka-band power amplifier with 32.9% PAE and 15.3-dBm power in 65-nm CMOS. IEEE Trans. Circuits Syst. I-Regul. Pap. 2018, 65, 2657–2668. [Google Scholar] [CrossRef]

- Jong, G.D.; Leenaerts, D.; van der Heijden, E. A fully integrated down-converter for Ka-band VSAT satellite reception. In Proceedings of the ESSCIRC (ESSCIRC), Bordeaux, France, 17–21 September 2012. [Google Scholar]

- Maassen, D.; Rautschke, F.; Ohnimus, F.; Schenk, L.; Dalisda, U.; Boeck, G. 70 W GaN-HEMT Ku-band power amplifier in MIC technology. IEEE Trans. Microw. Theory Technol. 2017, 65, 1272–1283. [Google Scholar] [CrossRef]

- Zhong, J.; Zhao, D.; You, X. A Ku-Band CMOS Power Amplifier with Series-Shunt LC Notch Filter for Satellite Communications. IEEE Trans. Circuits Syst. I-Regul. Pap. 2021, 68, 1869–1880. [Google Scholar] [CrossRef]

- Aljuhani, A.H.; Kanar, T.; Zihir, S.; Rebeiz, G.M. A scalable dual-polarized 256-element Ku-band SATCOM phased-array transmitter with 36.5 dBW EIRP per polarization. In Proceedings of the European Microwave Conference (EuMC), Madrid, Spain, 23–27 September 2018. [Google Scholar]

- Nasri, A.; Estebsari, M.; Toofan, S.; Piacibello, A.; Pirola, M.; Camarchia, V.; Ramella, C. Design of a Wideband Doherty Power Amplifier with High Efficiency for 5G Application. Electronics 2021, 10, 873. [Google Scholar] [CrossRef]

- Xu, Y.; Pang, J.; Wang, X.; Zhu, A. Enhancing Bandwidth and Back-Off Range of Doherty Power Amplifier With Modified Load Modulation Network. IEEE Trans. Microw. Theory Tech. 2021, 69, 2291–2303. [Google Scholar] [CrossRef]

- Lv, G.; Chen, W.; Chen, X.; Ghannouchi, F.M.; Feng, Z. A Fully Integrated 47.6% Fractional Bandwidth GaN MMIC Distributed Efficient Power Amplifier with Modified Input Matching and Power Splitting Network. IEEE Trans. Microw. Theory Tech. 2021, 69, 3132–3145. [Google Scholar] [CrossRef]

- Jeong, H.; Lee, H.; Park, B.; Jang, S.; Kong, S.; Park, C. Optimization Technique for High-Gain CMOS Power Amplifier for 5G Applications. Appl. Sci. 2021, 11, 11691. [Google Scholar] [CrossRef]

- Park, C.; Kim, Y.; Kim, H.; Hong, S. A 1.9-GHz CMOS Power Amplifier Using Three-Port Asymmetric Transmission Line Transformer for a Polar Transmitter. IEEE Trans. Microw. Theory Tech. 2007, 55, 230–238. [Google Scholar] [CrossRef]

- Li, X.; Lv, W.; Li, Y.; Wang, Y.; Huang, S.; Duan, Z. A Ku-Band High-Integrated CMOS Power Amplifier. In Proceedings of the IEEE 5th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, 23–25 October 2020. [Google Scholar]

- Chen, B.; Lou, L.; Tang, K.; Wang, Y.; Gao, J.; Zheng, Y. A 13.5–19 GHz 20.6-dB Gain CMOS Power Amplifier for FMCW Radar Application. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 377–379. [Google Scholar] [CrossRef]

- Chen, J.; Helmi, S.R.; Jou, A.Y.; Mohammadi, S. A Wideband Power Amplifier in 45 nm CMOS SOI Technology for X Band Applications. IEEE Microw. Wirel. Compon. Lett. 2013, 23, 587–589. [Google Scholar] [CrossRef]

| Ref. | Tech. (CMOS) | Freq. (GHz) | Supply (V) | Psat (dBm) | P1dB (dBm) | Gain (dB) | Peak PAE (%) | Architecture |

|---|---|---|---|---|---|---|---|---|

| This work | 65 nm | 15.0 | 1.0/2.6 | 22.1 | 20.0 | 24.6 | 17.2 | 2-stage/ CS + Stack |

| (2021) T-CAS-1 [6] | 65 nm | 14.2 | 1.0 | 14.5 | - | 21.9 | 24.1 | 2-stage/ CS |

| (2020) ICICM [13] | 65 nm | 14–18 | - | 22.6 | 17.4 | 26.8 | 30 | 2-stage/ CS |

| (2017) MWCL [14] | 65 nm | 15.0 | 1.2 | 13.9 | 11.6 | 20.6 | 20 | 3-stage/ CS |

| (2013) MWCL [15] | 45 nm (SOI) | 9–15 @12 | 4.8 | 22.8 | 21.9 | 9.8 | 21.8 | 1-stage/ Stack |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, J.; Lee, J.; Jang, S.; Jeong, H.; Kim, C.; Park, C. Ku-Band CMOS Power Amplifier with Three-Stack Power Stage to Enhance Output Power and Efficiency. Appl. Sci. 2022, 12, 4432. https://doi.org/10.3390/app12094432

Yang J, Lee J, Jang S, Jeong H, Kim C, Park C. Ku-Band CMOS Power Amplifier with Three-Stack Power Stage to Enhance Output Power and Efficiency. Applied Sciences. 2022; 12(9):4432. https://doi.org/10.3390/app12094432

Chicago/Turabian StyleYang, Junhyuk, Jaeyong Lee, Seongjin Jang, Hayeon Jeong, Choulyoung Kim, and Changkun Park. 2022. "Ku-Band CMOS Power Amplifier with Three-Stack Power Stage to Enhance Output Power and Efficiency" Applied Sciences 12, no. 9: 4432. https://doi.org/10.3390/app12094432

APA StyleYang, J., Lee, J., Jang, S., Jeong, H., Kim, C., & Park, C. (2022). Ku-Band CMOS Power Amplifier with Three-Stack Power Stage to Enhance Output Power and Efficiency. Applied Sciences, 12(9), 4432. https://doi.org/10.3390/app12094432